Изобретение относится к вычислительной технике и может быть использовано для сопряжения магистрали устройств с магистральным параллельным интерфейсом (МПИ) (типа Электроника 60) с внешними устройствами ряда СМ ЭВМ, имеющими интерфейс Общая шина (ОШ).

Целью изобретения является повышение пропускной способности магистрали МПИ за счет организации работы устройства с магистралью МПИ в режиме пословного обмена данными в ПДП при выполнении побайтных операций обмена данными с магистралью ОШ.

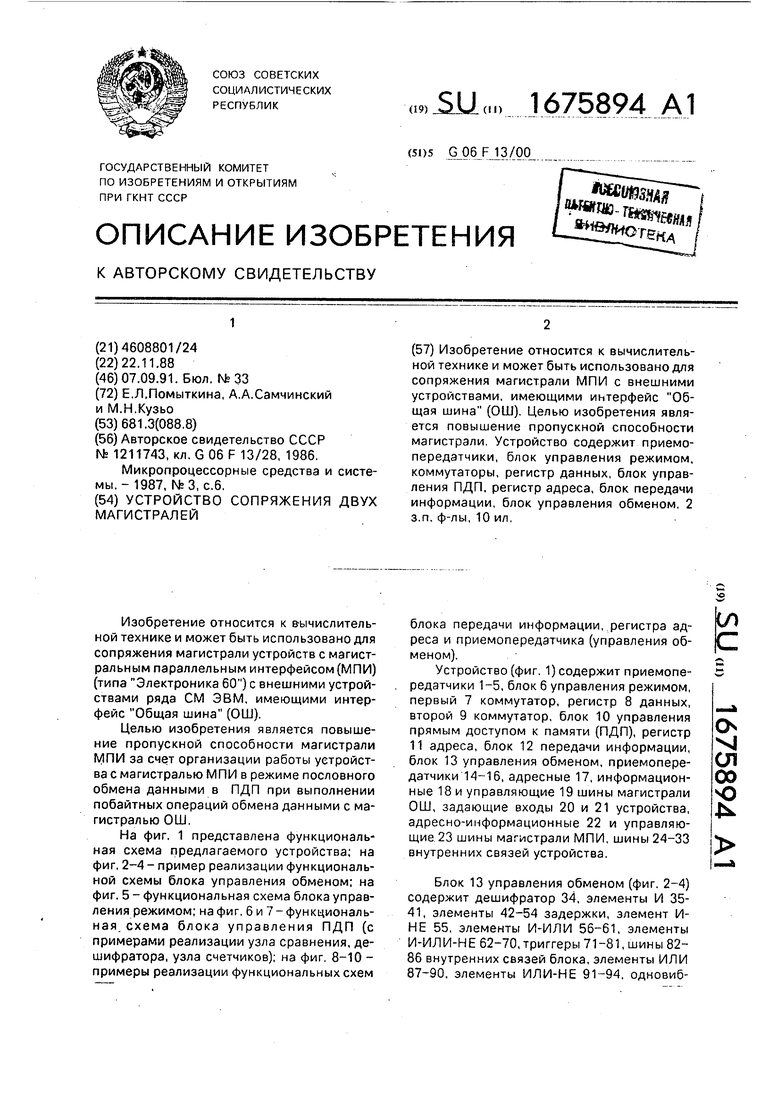

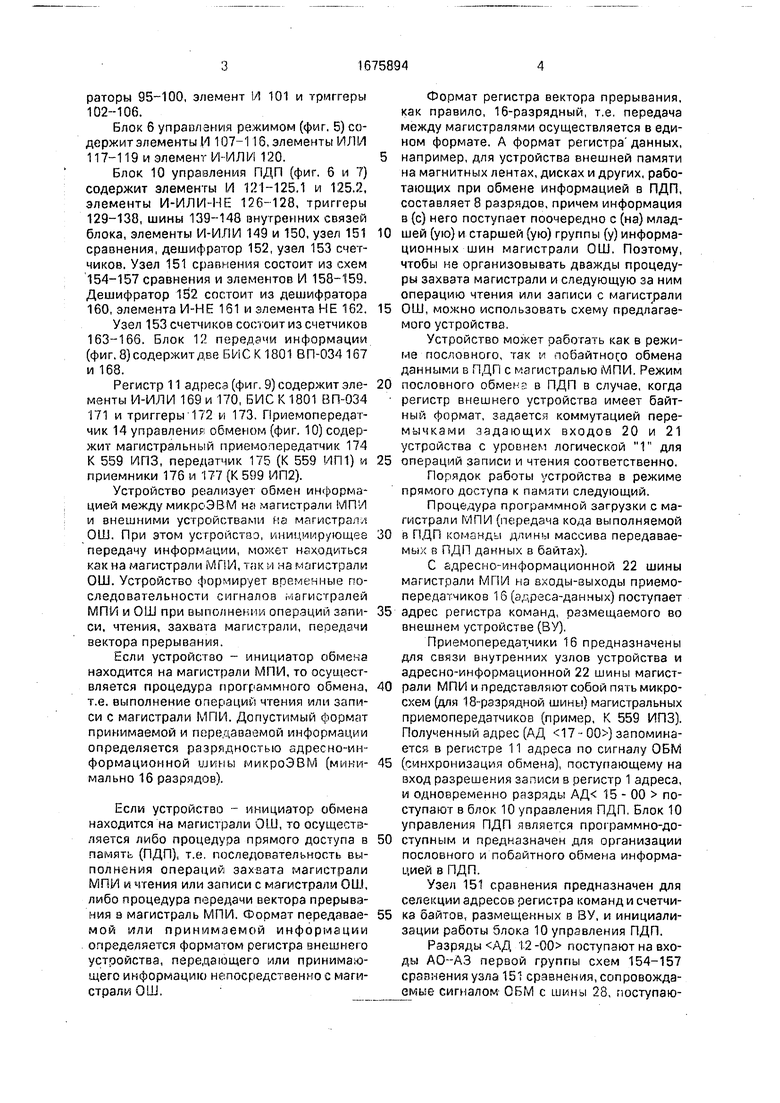

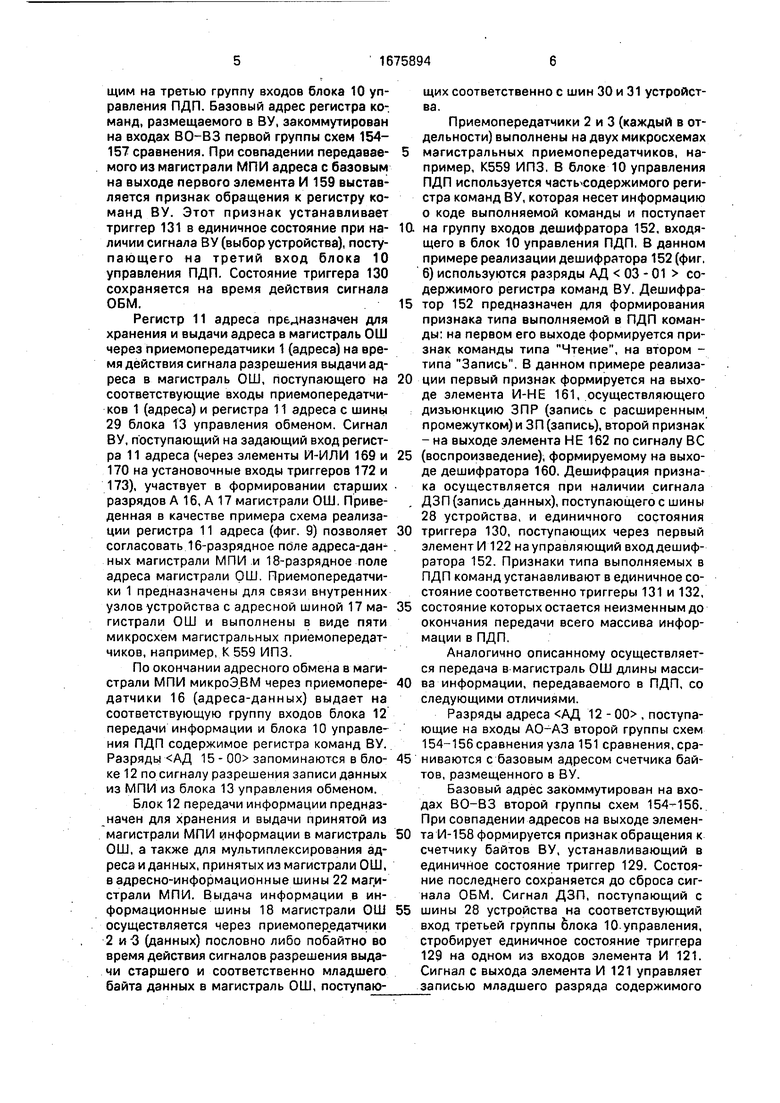

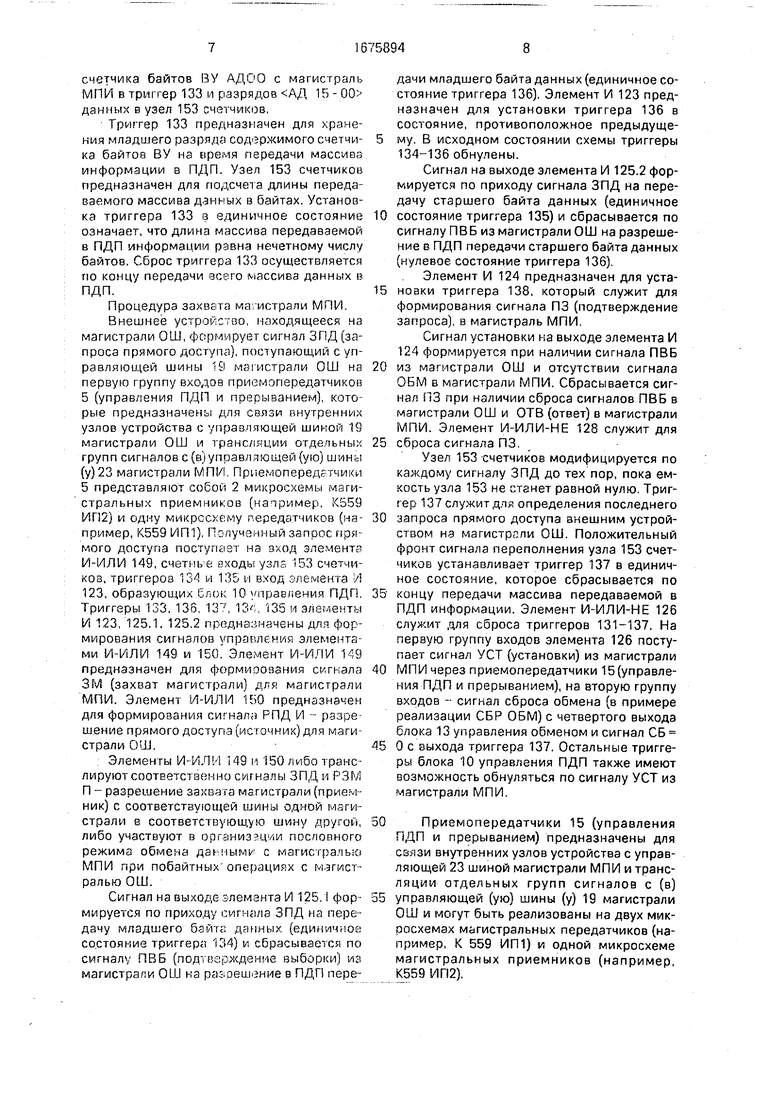

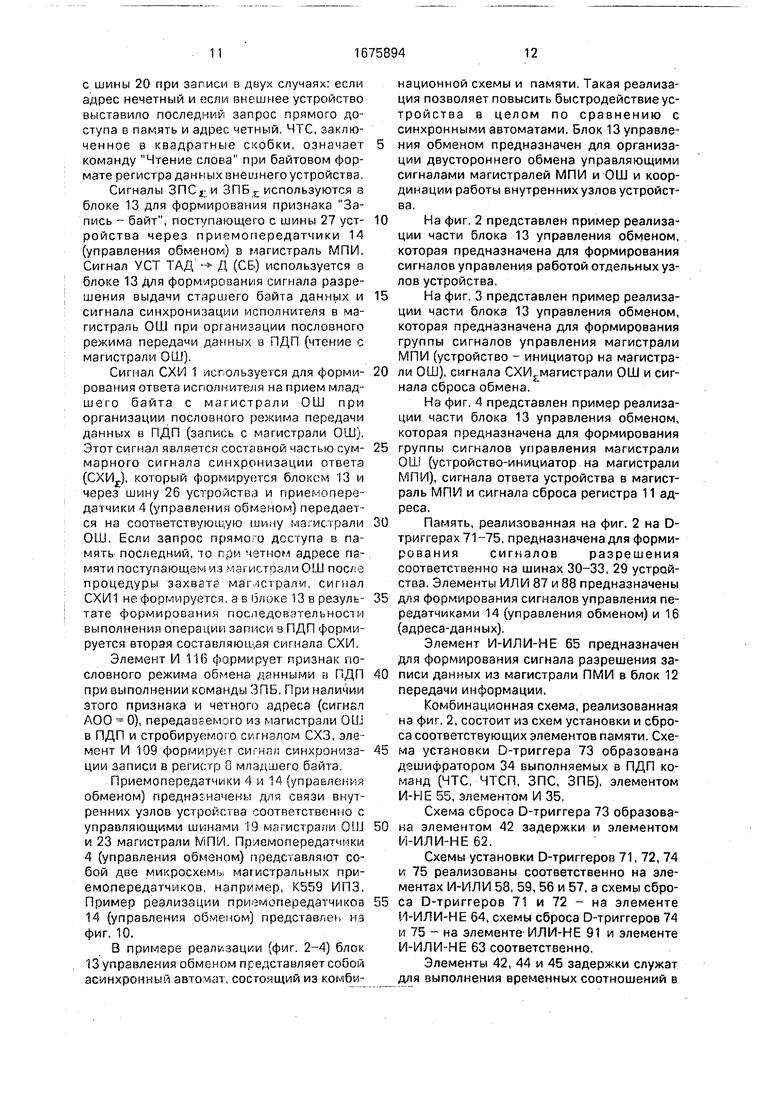

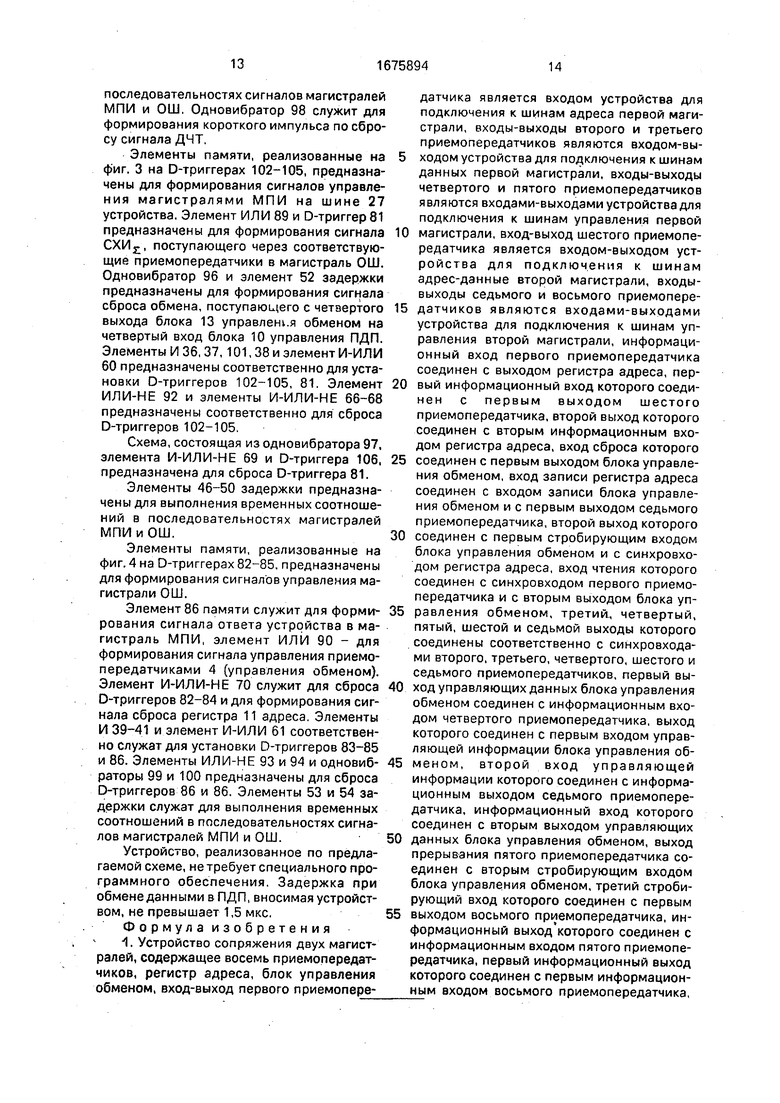

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2-4 - пример реализации функциональной схемы блока управления обменом; на фиг. 5 - функциональная схема блока управления режимом; на фиг. 6 и 7 - функциональ- ная схема блока управления ПДП (с примерами реализации узла сравнения, дешифратора, узла счетчиков); на фиг. 8-10 - примеры реализации функциональных схем

блока передачи информации, регистра адреса и приемопередатчика (управления обменом).

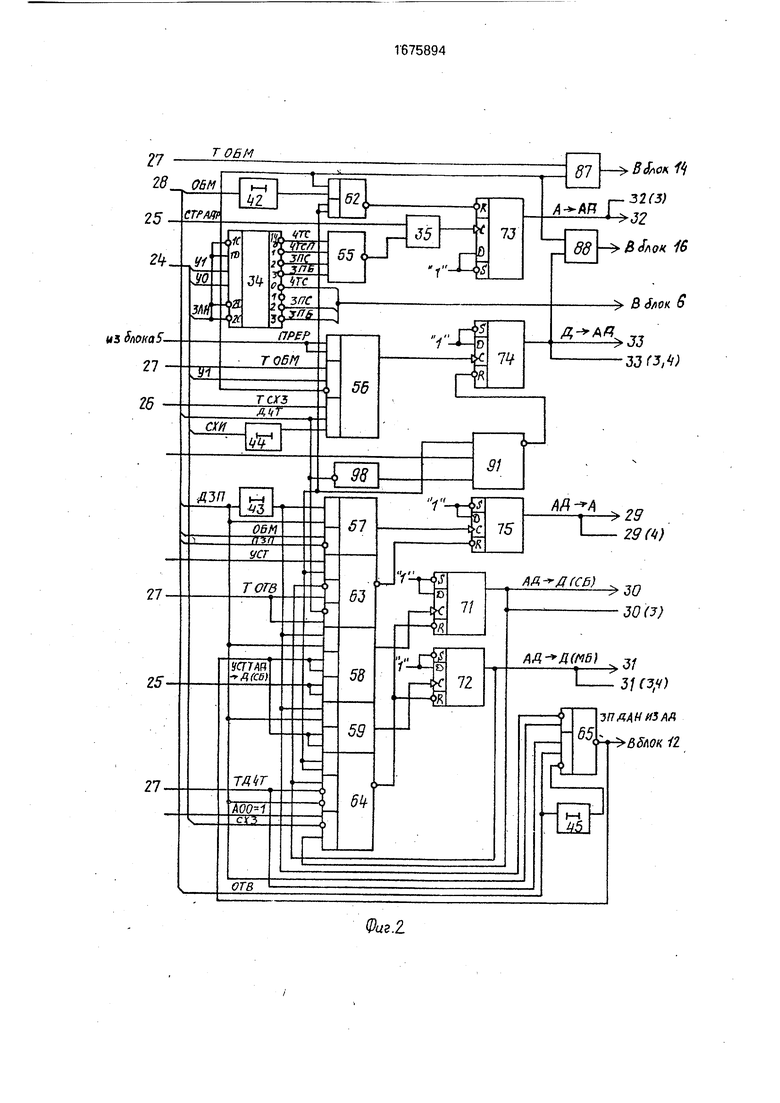

Устройство (фиг. 1) содержит приемопередатчики 1-5, блок 6 управления режимом, первый 7 коммутатор, регистр 8 данных, второй 9 коммутатор, блок 10 управления прямым доступом к памяти (ПДП), регистр 11 адреса, блок 12 передачи информации, блок 13 управления обменом, приемопередатчики 14-16, адресные 17, информационные 18 и управляющие 19 шины магистрали ОШ, задающие входы 20 и 21 устройства, адресно-информационные 22 и управляющие 23 шины магистрали МПИ, шины 24-33 внутренних связей устройства.

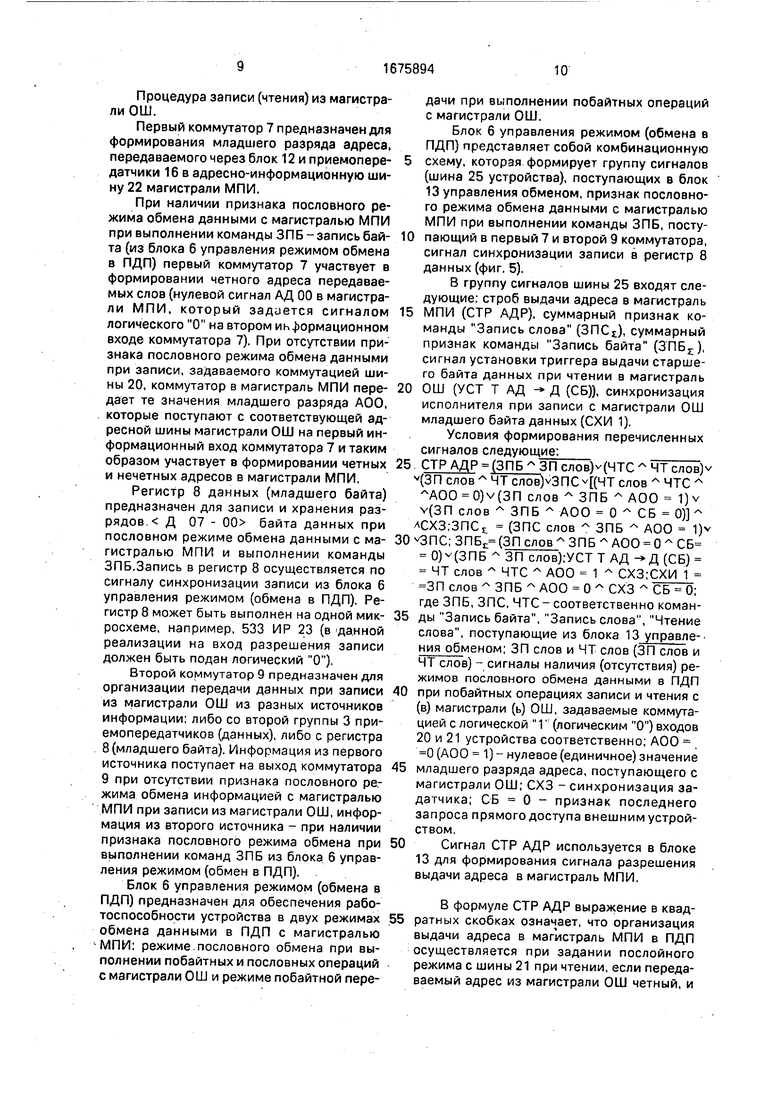

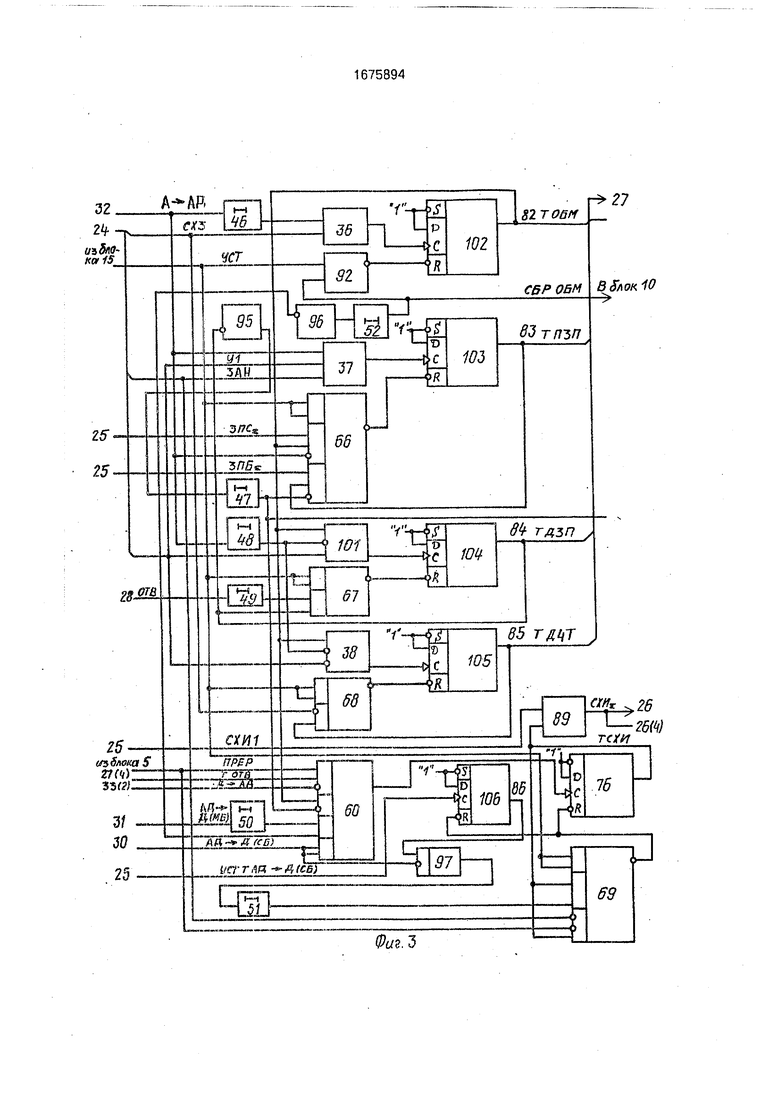

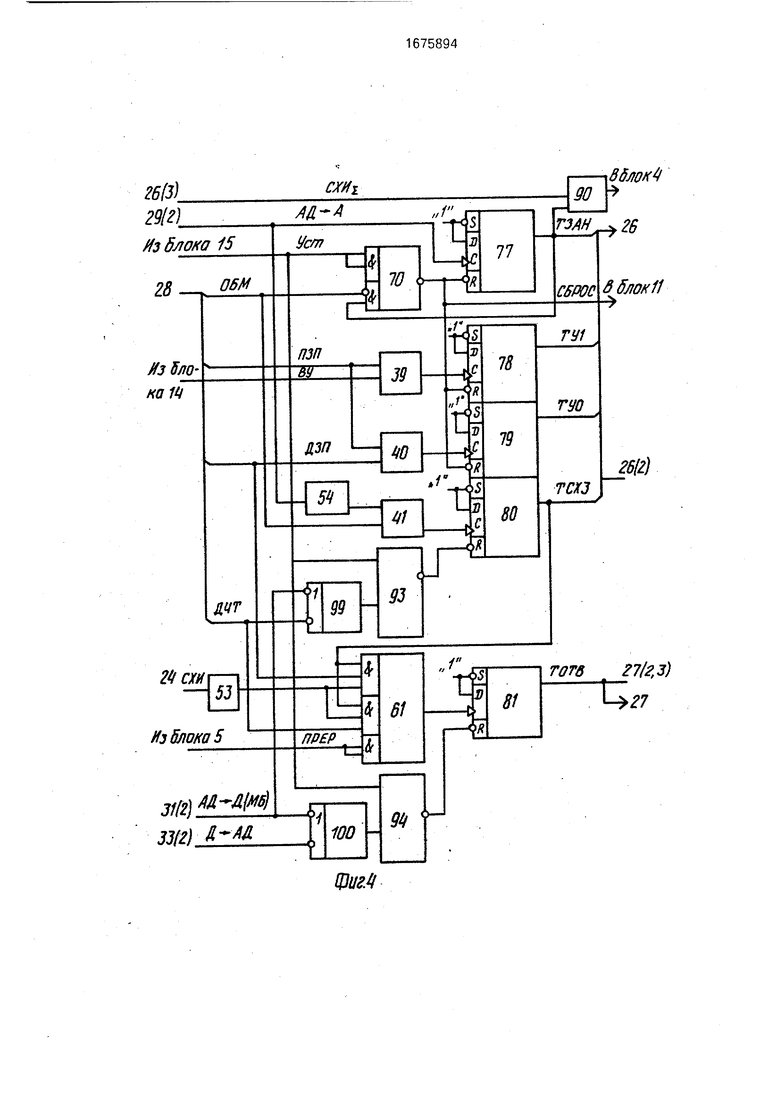

Блок 13 управления обменом (фиг. 2-4) содержит дешифратор 34, элементы И 35- 41, элементы 42-54 задержки, элемент И- НЕ 55, элементы И-ИЛИ 56-61, элементы И-ИЛИ-НЕ 62-70,триггеры 71-81, шины 82- 86 внутренних связей блока, элементы ИЛИ 87-90, элементы ИЛИ-НЕ 91-94. одновибсл

с

о

VI

ел

00

ю J

раторы 95-100, элемент И 101 и триггеры 102-106.

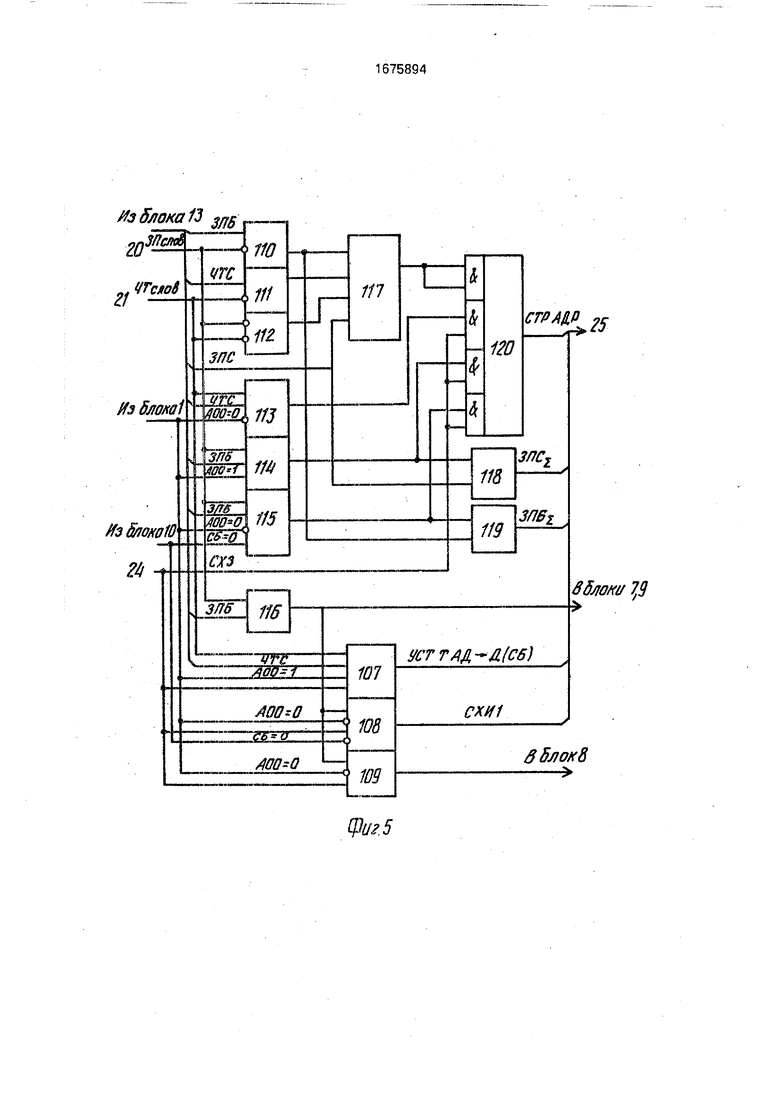

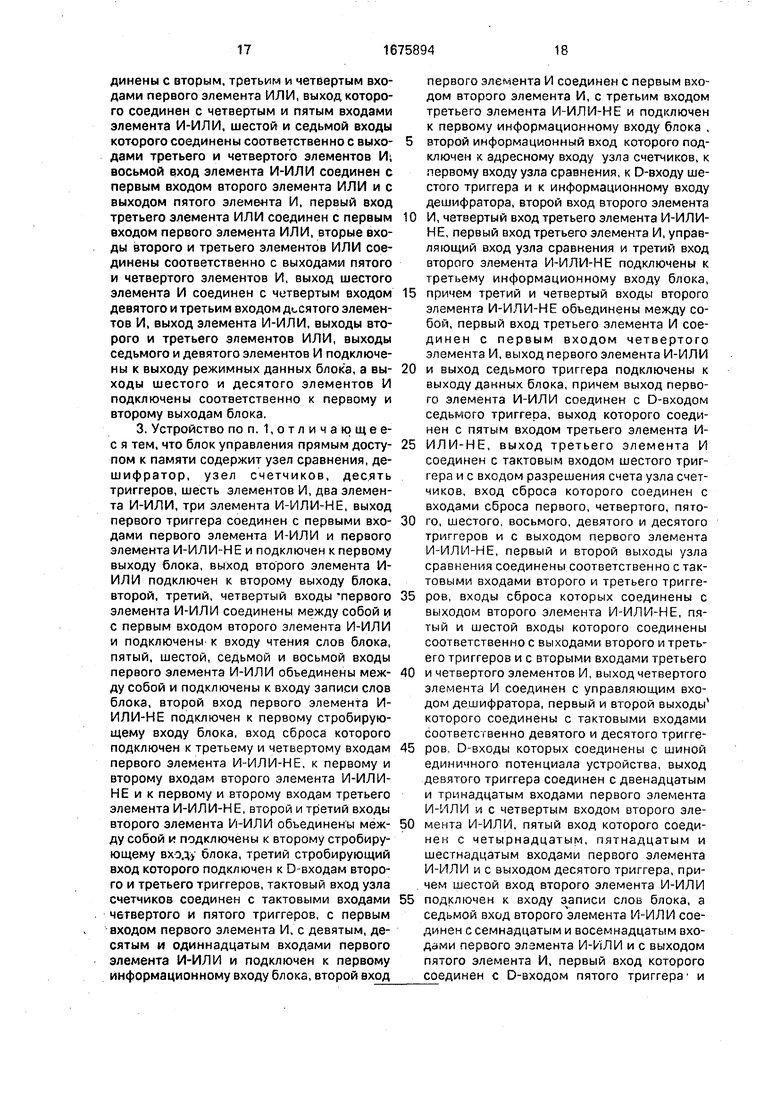

Блок 6 управления режимом (фиг. 5) содержит элементы И 107-116, элементы ИЛИ 117-119 и элемент И-ИЛИ 120.

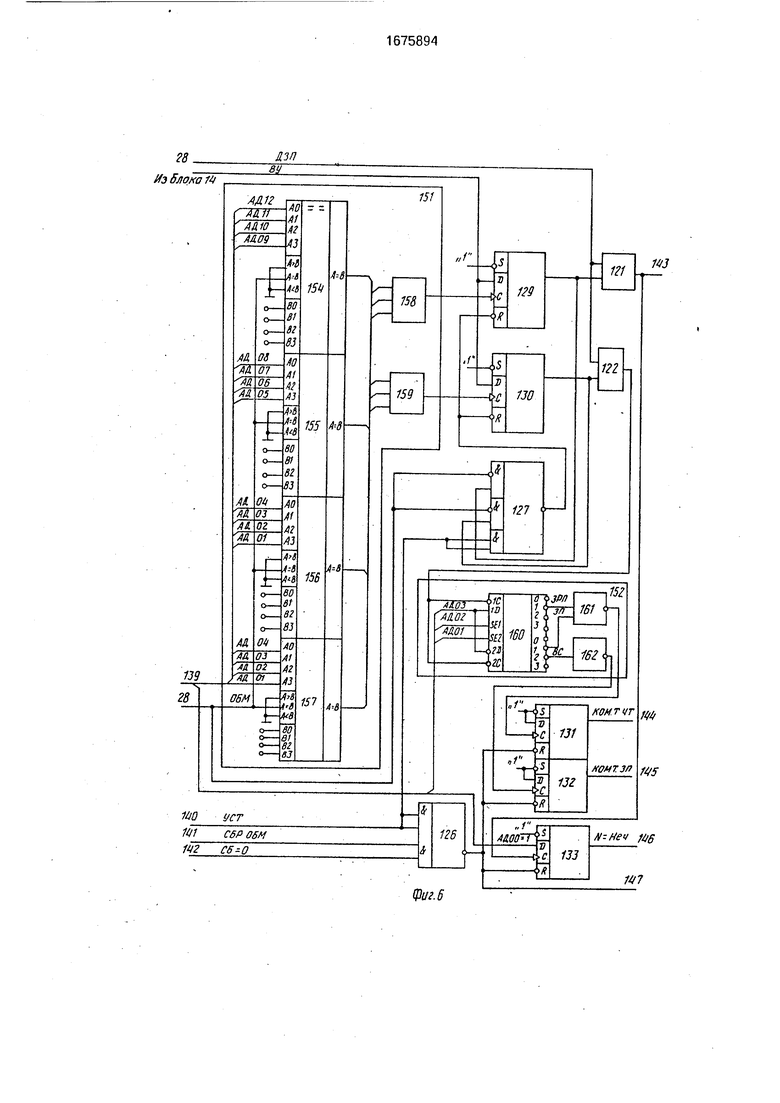

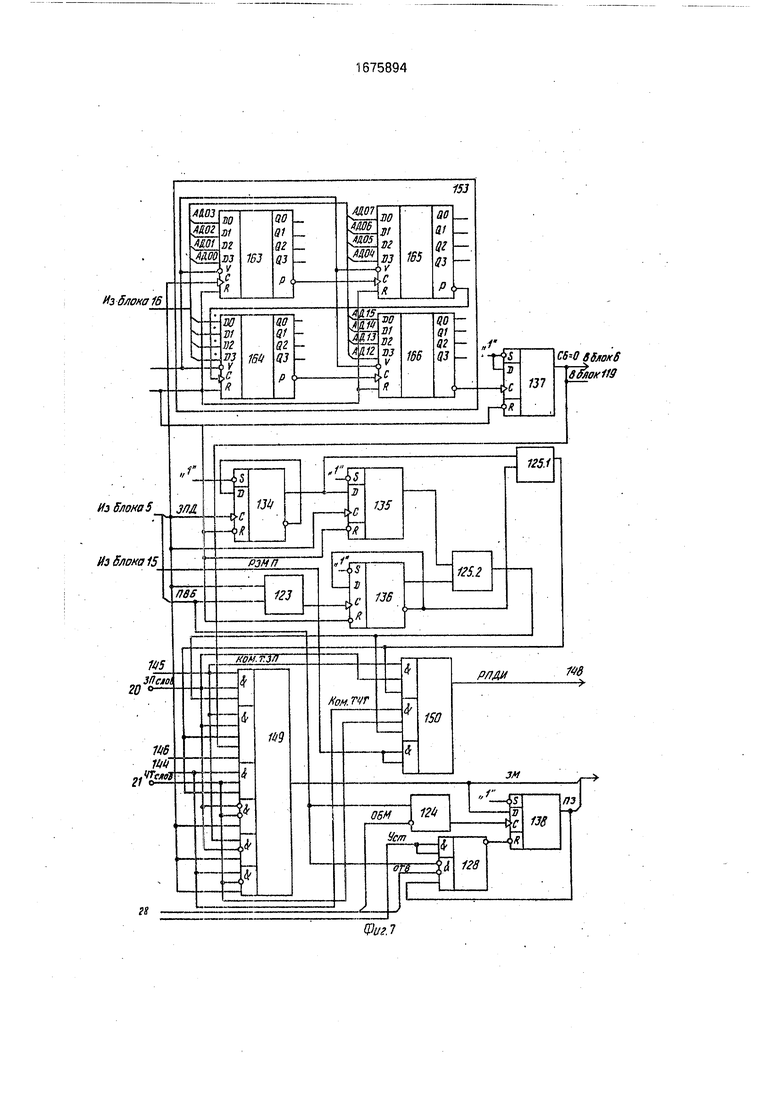

Блок 10 управления ПДП (фиг. 6 и 7) содержит элементы И 121-125.1 и 125.2, элементы И-ИЛИ-НЕ 126-128, триггеры 129-138, шины 139-148 внутренних связей блока, элементы И-ИЛИ 149 и 150, узел 151 сравнения, дешифратор 152, узел 153 счетчиков, Узел 151 сравнения состоит из схем 154-157 сравнения и элементов И 158-159. Дешифратор 1S2 состоит из дешифратора 160, элемента И-НЕ 161 и элемента НЕ 162.

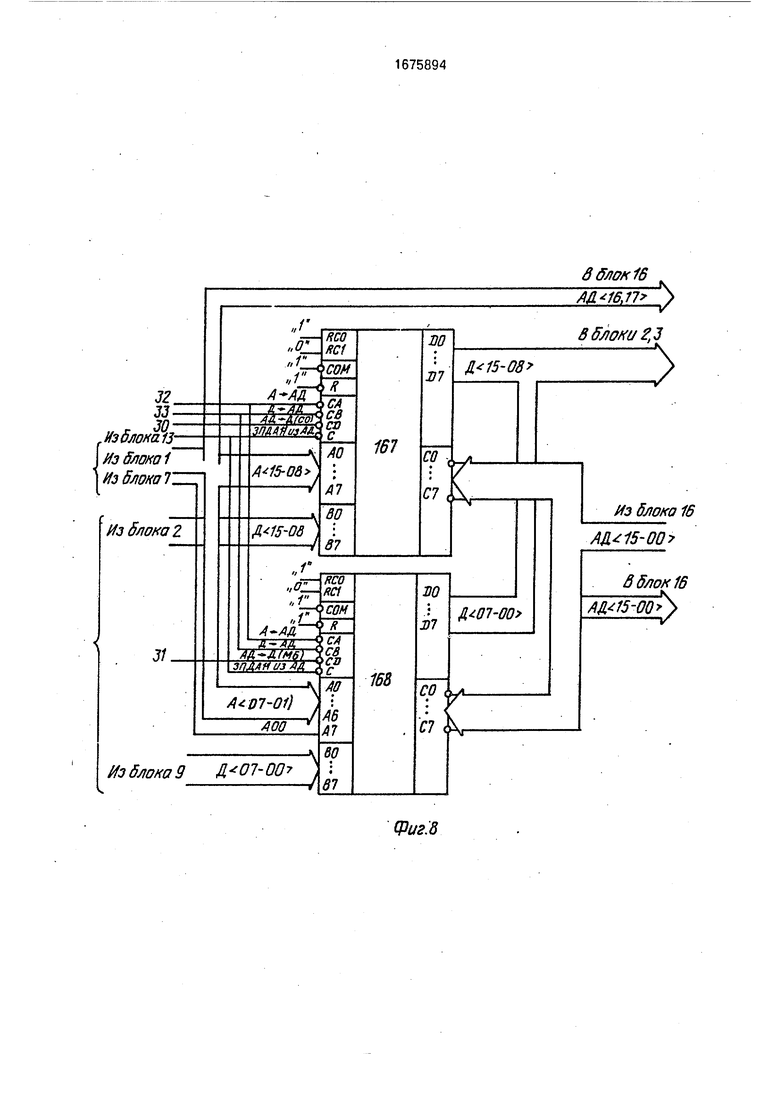

Узел 153 счетчиков состоит из счетчиков 163-166. Блок 12 передачи информации (фиг. 8) содержит две БИС К 1801 ВП-034 167 и 168,

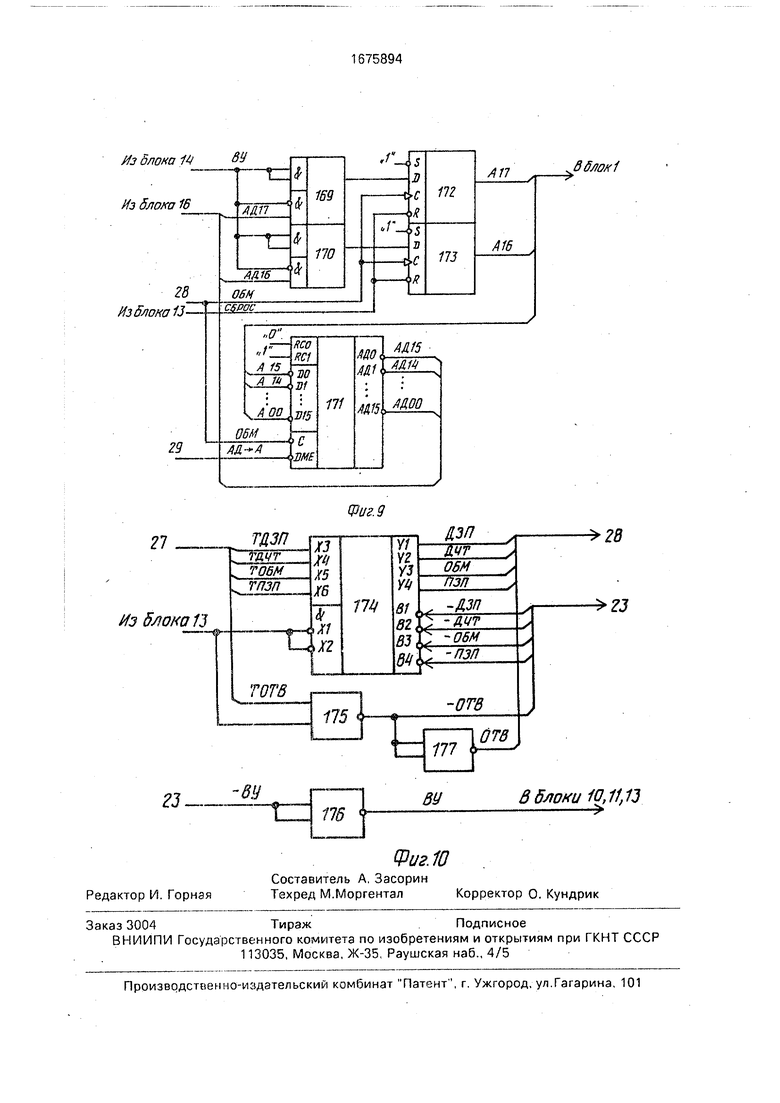

Регистр 11 адреса (фиг. 9) содержит элементы И-ИЛИ 169 и 170, БИС К 1801 ВП-034 171 и триггеры 172 и 173. Приемопередатчик 14 управления обменом (фиг, 10) содержит магистральный приемопередатчик 174 К 559 ИПЗ, передатчик 175 (К 559 ИП1) и приемники 176 и 177 (К 599 ИП2).

Устройство реализует обмен информацией между микроЭВМ на магистрали МПИ и внешними устройствами на магистрали ОШ. При этом устройство, инициирующее передачу информации, может находиться как на магистрали МПИ, так и на магистрали ОШ. Устройство формирует временные последовательности сигналов магистралей МПИ и ОШ при выполнении операций записи, чтения, захвата магистрали, передачи вектора прерывания.

Если устройство - инициатор обмена находится на магистрали МПИ, то осуществляется процедура программного обмена, т.е. выполнение операций чтения или записи с магистрали МПИ. Допустимый формат принимаемой и передаваемой информации определяется разрядностью адресно-информационной шины микроЭВМ (минимально 16 разрядов).

Если устройство - инициатор обмена находится на магистрали ОШ, то осуществляется либо процедура прямого доступа в память (ПДП), т.е. последовательность выполнения операций захвата магистрали МПИ и чтения или записи с магистрали ОШ. либо процедура передачи вектора прерывания в магистраль МПИ. Формат передаваемой или принимаемой информации определяется форматом регистра внешнего устройства, передающего или принимающего информацию непосредственно с магистрали ОШ.

Формат регистра вектора прерывания, как правило, 16-разрядный, т.е. передача между магистралями осуществляется в едином формате, А формат регистра данных,

например, для устройства внешней памяти на магнитных лентах, дисках и других, работающих при обмене информацией в ПДП, составляете разрядов, причем информация в (с) него поступает поочередно с (на) млад0 шей (ую) и старшей (ую) группы (у) информационных шин магистрали ОШ. Поэтому, чтобы не организовывать дважды процедуры захвата магистрали и следующую за ним операцию чтения или записи с магистрали

5 ОШ, можно использовать схему предлагаемого устройства.

Устройство может работать как в режиме пословного, так и побайтного обмена данными в ПДП с магистралью МПИ. Режим

0 пословного обмена в ПДП в случае, когда регистр внешнего устройства имеет байтный формат, задается коммутацией перемычками задающих входов 20 и 21 устройства с уровнем логической 1 для

5 операций записи и чтения соответственно. Порядок работы устройства в режиме прямого доступа к памяти следующий.

Процедура программной загрузки с магистрали МПИ (передача кода выполняемой

0 в ПДП команды длины массива передаваемых в ПДП данных в байтах).

С адресно-информационной 22 шины магистрали МПИ на входы-выходы приемопередатчиков 16 (адреса-данных) поступает

5 адрес регистра команд, размещаемого во внешнем устройстве (ВУ),

Приемопередатчики 16 предназначены для связи внутренних узлов устройства и адресно-информационной 22 шины магист0 рали МПИ и представляют собой пять микросхем (для 18-рззрядной шины) магистральных приемопередатчиков (пример, К 559 ИПЗ). Полученный адрес (АД 17 - 00) запоминается в регистре 11 адреса по сигналу ОБМ

5 (синхронизация обмена), поступающему на вход разрешения записи в регистр 1 адреса, и одновременно разряды АД 15 - 00 поступают в блок 10 управления ПДП, Блок 10 управления ПДП является программно-до0 ступным и предназначен для организации пословного и побайтного обмена информацией в ПДП.

Узел 151 сравнения предназначен для селекции адресов регистра команд и счетчи5 ка байтов, размещенных в ВУ, и инициализации работы блока 10 управления ПДП.

Разряды АД 12 -00 поступают на входы АО-АЗ первой группы схем 154-157 сравнения узла 151 сравнения, сопровождаемые сигналом ОБМ с шины 28, поступающим на третью группу входов блока 10 управления ПДП. Базовый адрес регистра команд, размещаемого в В У, закоммутирован на входах ВО-ВЗ первой группы схем 154- 157 сравнения. При совпадении передаваемого из магистрали МПИ адреса с базовым на выходе первого элемента И 159 выставляется признак обращения к регистру команд ВУ. Этот признак устанавливает триггер 131 в единичное состояние при наличии сигнала ВУ (выбор устройства), поступающего на третий вход блока 10 управления ПДП. Состояние триггера 130 сохраняется на время действия сигнала ОБМ.

Регистр 11 адреса предназначен для хранения и выдачи адреса в магистраль ОШ через приемопередатчики 1 (адреса) на время действия сигнала разрешения выдачи адреса в магистраль ОШ, поступающего на соответствующие входы приемопередатчиков 1 (адреса) и регистра 11 адреса с шины 29 блока 13 управления обменом. Сигнал ВУ, поступающий на задающий вход регистра 11 адреса (через элементы И-ИЛИ 169 и 170 на установочные входы триггеров 172 и 173), участвует в формировании старших разрядов А 16, А 17 магистрали ОШ. Приведенная в качестве примера схема реализации регистра 11 адреса (фиг. 9) позволяет согласовать 16-разрядное поле адреса-дан- ных магистрали МПИ и 18-разрядное поле адреса магистрали ОШ. Приемопередатчики 1 предназначены для связи внутренних узлов устройства с адресной шиной 17 магистрали ОШ и выполнены в виде пяти микросхем магистральных приемопередатчиков, например, К 559 ИПЗ.

По окончании адресного обмена в магистрали МПИ микроЭВМ через приемопередатчики 16 (адреса-данных) выдает на соответствующую группу входов блока 12 передачи информации и блока 10 управления ПДП содержимое регистра команд ВУ. Разряды АД 15 - 00 запоминаются в блоке 12 по сигналу разрешения записи данных из МПИ из блока 13 управления обменом.

Блок 12 передачи информации предназначен для хранения и выдачи принятой из магистрали МПИ информации в магистраль ОШ, а также для мультиплексирования адреса и данных, принятых из магистрали ОШ, в адресно-информационные шины 22 магистрали МПИ. Выдача информации в информационные шины 18 магистрали ОШ осуществляется через приемопередатчики 2 и -3 (данных) пословно либо побайтно во время действия сигналов разрешения выдачи старшего и соответственно младшего байта данных в магистраль ОШ, поступающих соответственно с шин 30 и 31 устройства.

Приемопередатчики 2 и 3 (каждый в отдельности) выполнены на двух микросхемах

магистральных приемопередатчиков, например, К559 ИПЗ. В блоке 10 управления ПДП используется часть содержимого регистра команд ВУ, которая несет информацию о коде выполняемой команды и поступает

0. на группу входов дешифратора 152, входящего в блок 10 управления ПДП, В данном примере реализации дешифратора 152 (фиг. 6) используются разряды АД 03 - 01 содержимого регистра команд ВУ. Дешифра5 тор 152 предназначен для формирования признака типа выполняемой в ПДП команды: на первом его выходе формируется признак команды типа Чтение, на втором - типа Запись. В данном примере реализа0 ции первый признак формируется на выходе элемента И-НЕ 161, осуществляющего дизъюнкцию ЗПР (запись с расширенным промежутком) и ЗП (запись), второй признак - на выходе элемента НЕ 162 по сигналу ВС

5 (воспроизведение), формируемому на выходе дешифратора 160. Дешифрация признака осуществляется при наличии сигнала ДЗП (запись данных), поступающего с шины 28 устройства, и единичного состояния

0 триггера 130, поступающих через первый элемент И 122 на управляющий вход дешифратора 152. Признаки типа выполняемых в ПДП команд устанавливают в единичное состояние соответственно триггеры 131 и 132,

5 состояние которых остается неизменным до окончания передачи всего массива информации в ПДП.

Аналогично описанному осуществляется передача в магистраль ОШ длины масси0 ва информации, передаваемого в ПДП, со следующими отличиями.

Разряды адреса АД 12 - 00 , поступающие на входы АО-АЗ второй группы схем 154-156 сравнения узла 151 сравнения, сра5 ниваются с базовым адресом счетчика байтов, размещенного в ВУ.

Базовый адрес закоммутирован на входах ВО-ВЗ второй группы схем 154-156. При совпадении адресов на выходе элемен0 та И-158 формируется признак обращения к счетчику байтов ВУ, устанавливающий в единичное состояние триггер 129. Состояние последнего сохраняется до сброса сигнала ОБМ. Сигнал ДЗП, поступающий с

5 шины 28 устройства на соответствующий вход третьей группы блока 10 управления, стробирует единичное состояние триггера 129 на одном из входов элемента И 121. Сигнал с выхода элемента И 121 управляет записью младшего разряда содержимого

счетчика байтов ВУ АДОО с магистраль МПЙ в триггер 133 и разрядов АД 15-00 данных в узел 153 счетчиков.

Триггер 133 предназначен для хранения младшего разряда содержимого счетчика байтов ВУ на время передачи массива информации в ПДП. Узел 153 счетчиков предназначен для подсчета длины передаваемого массива данных в байтах. Установка триггера 133 в единичное состояние означает, что длина массива передаваемой в ПДП информации равна нечетному числу байтов. Сброс триггера 133 осуществляется по концу передачи всего массива данных в ПДП.

Процедура захвата магистрали МПИ.

Внешнее устройство, находящееся на магистрали ОШ, формирует сигнал ЗПД (запроса прямого доступа), поступающий с управляющей шины 19 магистрали ОШ на первую группу входов приемопередатчиков 5 (управления ПДП и прерыванием}, которые предназначены для связи внутренних узлов устройства с управляющей шиной 19 магистрали ОШ и трансляции отдельных групп сигналов с (в) управляющей (ую) шины (у) 23 магистрали МПИ. Приемопередатчики 5 представляют собой 2 микросхемы магистральных приемников (например, 559 ИП2) и одну микросхему передатчиков (например, К559 ИП1). Полученный запрос прямого доступа поступает на вход элемента И-ИЛИ 149, счетные входы узла 153 счетчиков, триггеров 134 и 135 и вход элемента И 123, образующих блок 10 управления ПДП. Триггеры 133, 136, 137, 134, 135 и элементы И 123, 125.1, 125.2 предназначены для формирования сигналов управления элементами И-ИЛИ 149 и 150. Элемент И-ИЛИ 149 предназначен для формирования сигнала ЗМ (захват магистрали) для магистрали МПИ. Элемент И-ИЛИ 150 предназначен для формирования сигнала РПД И - разрешение прямого доступа (источник) для магистрали ОШ.

Элементы И-ИЛИ 149 и 150 либо транслируют соответственно сигналы ЗПД и РЗМ П - разрешение захвата магистрали (приемник) с соответствующей шины одной магистрали в соответствующую шину другой, либо участвуют в организации пословного режима обмена данными с магистралью МПИ при побайтных операциях с магистралью ОШ.

Сигнал на выходе элемента И 125.1 формируется по приходу сигнала ЗПД на передачу младшего байта данных (единичное состояние триггера 134) и сбрасывается по сигналу ПВБ (подтверждение выборки) из магистрали ОШ на разрешение в ПДП передачи младшего байта данных (единичное состояние триггера 136). Элемент И 123 предназначен для установки триггера 136 в состояние, противоположное предыдущему. В исходном состоянии схемы триггеры 134-136 обнулены.

Сигнал на выходе элемента И 125.2 формируется по приходу сигнала ЗПД на передачу старшего байта данных (единичное

состояние триггера 135) и сбрасывается по сигналу ПВБ из магистрали ОШ на разрешение в ПДП передачи старшего байта данных (нулевое состояние триггера 136).

Элемент И 124 предназначен для установки триггера 138, который служит для формирования сигнала ПЗ (подтверждение запроса), в магистраль МПИ.

Сигнал установки на выходе элемента И 124 формируется при наличии сигнала ПВБ

из магистрали ОШ и отсутствии сигнала ОБМ в магистрали МПИ. Сбрасывается сигнал ПЗ при наличии сброса сигналов ПВБ в магистрали ОШ и ОТВ (ответ) в магистрали МПИ, Элемент И-ИЛИ-НЕ 128 служит для

сброса сигнала ПЗ.

Узел 153 -счетчиков модифицируется по каждому сигналу ЗПД до тех пор, пока емкость узла 153 не станет равной нулю. Триггер 137 служит для определения последнего

запроса прямого доступа внешним устройством на магистрали ОШ. Положительный фронт сигнала переполнения узла 153 счетчиков устанавливает триггер 137 в единичное состояние, которое сбрасывается по

концу передачи массива передаваемой в ПДП информации, Элемент И-ИЛИ-НЕ 126 служит для сброса триггеров 131-137. На первую группу входов элемента 126 поступает сигнал УСТ (установки) из магистрали

МПИ через приемопередатчики (управления ПДП и прерыванием), на вторую группу входов - сигнал сброса обмена (в примере реализации СБР ОБМ) с четвертого выхода блока 13 управления обменом и сигнал СБ

0 с выхода триггера 137. Остальные триггеры блока 10 управления ПДП также имеют возможность обнуляться по сигналу УСТ из магистрали МПИ.

Приемопередатчики 15 (управления ПДП и прерыванием) предназначены для связи внутренних узлов устройства с управляющей 23 шиной магистрали МПИ и трансляции отдельных групп сигналов с (в)

управляющей (ую) шины (у) 19 магистрали ОШ и могут быть реализованы на двух микросхемах магистральных передатчиков(например, К 559 ИП1) и одной микросхеме магистральных приемников (например, К559 ИП2).

Процедура записи (чтения) из магистрали ОШ.

Первый коммутатор 7 предназначен для формирования младшего разряда адреса, передаваемого через блок 12 и приемопередатчики 16 в адресно-информационную шину 22 магистрали МПИ.

При наличии признака пословного режима обмена данными с магистралью МПИ при выполнении команды ЗПБ - запись байта (из блока 6 управления режимом обмена в ПДП) первый коммутатор 7 участвует в формировании четного адреса передаваемых слов (нулевой сигнал АД 00 в магистрали МПИ, который задается сигналом логического О на втором информационном входе коммутатора 7). При отсутствии признака пословного режима обмена данными при записи, задаваемого коммутацией шины 20, коммутатор в магистраль МПИ передает те значения младшего разряда АОО, которые поступают с соответствующей адресной шины магистрали ОШ на первый информационный вход коммутатора 7 и таким образом участвует в формировании четных и нечетных адресов в магистрали МПИ.

Регистр 8 данных (младшего байта) предназначен для записи и хранения разрядов Д 07 - 00 байта данных при пословном режиме обмена данными с магистралью МПИ и выполнении команды ЗПБ.Запись в регистр 8 осуществляется по сигналу синхронизации записи из блока 6 управления режимом (обмена в ПДП). Регистр 8 может быть выполнен на одной микросхеме, например, 533 ИР 23 (в данной реализации на вход разрешения записи должен быть подан логический О).

Второй коммутатор 9 предназначен для организации передачи данных при записи из магистрали ОШ из разных источников информации: либо со второй группы 3 приемопередатчиков (данных), либо с регистра

8(младшего байта). Информация из первого источника поступает на выход коммутатора

9при отсутствии признака пословного режима обмена информацией с магистралью МПИ при записи из магистрали ОШ, информация из второго источника - при наличии признака пословного режима обмена при выполнении команд ЗПБ из блока 6 управления режимом (обмен в ПДП).

Блок б управления режимом (обмена в ПДП) предназначен для обеспечения работоспособности устройства в двух режимах обмена данными в ПДП с магистралью МПИ: режиме пословного обмена при выполнении побайтных и пословных операций с магистрали ОШ и режиме побайтной передачи при выполнении побайтных операций с магистрали ОШ.

Блок 6 управления режимом (обмена в ПДП) представляет собой комбинационную

схему, которая формирует группу сигналов (шина 25 устройства), поступающих в блок 13 управления обменом, признак пословного режима обмена данными с магистралью МПИ при выполнении команды ЗПБ, постулающий в первый 7 и второй 9 коммутатора, сигнал синхронизации записи в регистр 8 данных (фиг. 5).

В группу сигналов шины 25 входят следующие: строб выдачи адреса в магистраль

МПИ (СТР АДР), суммарный признак команды Запись слова (ЗПСЈ), суммарный признак команды Запись байта (ЗПБГ), сигнал установки триггера выдачи старшего байта данных при чтении в магистраль

ОШ (УСТ Т АД - Д (СБ)), синхронизация исполнителя при записи с магистрали ОШ младшего байта данных (СХИ 1).

Условия формирования перечисленных сигналов следующие:

СТР АДР - (ЗПБ ЗП словНЧТС ЧТ слов)у (ЗП слов л ЧТслов ЗПО(ЧТ слов л ЧТС л ЛАОО ОМЗП слов л ЗПБ л АОО 1)v v(3n слов Л ЗПБ Л АОО О Л СБ 0) Л лСХЗ;ЗПС (ЗПС слов Л ЗПБ Л АОО 1)v

ЗПС; ЗПБС (ЗПслов ЗПБ л АОО О л СБ 0)(ЗПБ л ЗП слов);УСТ Т АД - Д (СБ) ЧТ слов л ЧТС л АОО 1 л СХЗ;СХИ 1 ЗП слов л ЗПБ л АОО О л СХЗ л СБ 0; где ЗПБ, ЗПС, ЧТС - соответственно команды Запись байта, Запись слова, Чтение слова, поступающие из блока 13 управле-- ния обменом: ЗП слов и ЧТ слов (ЗП слов и ЧТ слов) - сигналы наличия (отсутствия) режимов пословного обмена данными в ПДП

при побайтных операциях записи и чтения с (в) магистрали (ь) ОШ, задаваемые коммутацией с логической 1 (логическим О) входов 20 и 21 устройства соответственно; АОО 0 (АОО 1) - нулевое (единичное) значение

младшего разряда адреса, поступающего с магистрали ОШ; СХЗ - синхронизация за- датчика; СБ 0 - признак последнего запроса прямого доступа внешним устройством.

Сигнал СТР АДР используется в блоке 13 для формирования сигнала разрешения выдачи адреса в магистраль МПИ.

В формуле СТР АДР выражение в квад- ратных скобках означает, что организация выдачи адреса в магистраль МПИ в ПДП осуществляется при задании послойного режима с шины 21 при чтении, если передаваемый адрес из магистрали ОШ четный, и

с шины 20 при записи в двух случаях: если адрес нечетный и если внешнее устройство выставило последний запрос прямого доступа в память и адрес четный. ЧТС, заключенное в квадратные скобки, означает команду Чтение слова при байтовом формате регистра данных внешнего устройства.

Сигналы и ЗПБЕ используются в блоке 13 для формирования признака Запись - байт, поступающего с шины 27 устройства через приемопередатчики 14 (управления обменом) в магистраль МПИ. Сигнал УСТ ТАД - Д (СБ) используется в блоке 13 для формирования сигнала разрешения выдачи старшего байта данных и сигнала синхронизации исполнителя в магистраль ОШ при организации пословного режима передачи данных в ПДП (чтение с магистрали ОШ).

Сигнал СХИ 1 используется для формирования ответа исполнителя на прием младшего байта с магистрали ОШ при организации пословного режима передачи данных в ПДП (запись с магистрали ОШ). Этот сигнал является составной частью суммарного сигнала синхронизации ответа (СХИ ), который формируется блоком 13 и через шину 26 устройства и приемопередатчики 4 (управления обменом) передается на соответствующую шину магистрали ОШ. Если запрос прямого доступа в память последний, то при четном адресе памяти поступающем из магистрали ОШ после процедуры захвата магистрали, сигнал СХИ1 не формируется, а в блоке 13 в результате формирования последовательности выполнения операции записи в ПДП формируется вторая составляющая сигнала СХИ,

Элемент И 116 формирует признак пословного режима обмена данными в ПДП при выполнении команды ЗПБ. При наличии этого признака и четного адреса (сигнал АОО 0), передаваемого из магистрали ОШ в ПДП и стробируемого сигналом СХЗ, элемент И 109 формирует сигнал синхронизации записи в регистр 8 младшего байта.

Приемопередатчики 4 и 14 (управления обменом) предназначены для связи внутренних узлов устройства соответственно с управляющими шинами 19 магистрали ОШ и 23 магистрали МПИ. Приемопередатчики 4 (управления обменом) представляют собой две микросхемы магистральных приемопередатчиков, например, К559 ИПЗ. Пример реализации приемопередатчиков 14 (управления обменом) представлен на фиг, 10,

В примере реализации (фиг, 2-4) блок 13 управления обменом представляет собой асинхронный автомат, состоящий из комби

национной схемы и памяти, Такая реализация позволяет повысить быстродействие устройства в целом по сравнению с синхронными автоматами, Блок 13 управления обменом предназначен для организации двустороннего обмена управляющими сигналами магистралей МПИ и ОШ и координации работы внутренних узлов устройства.

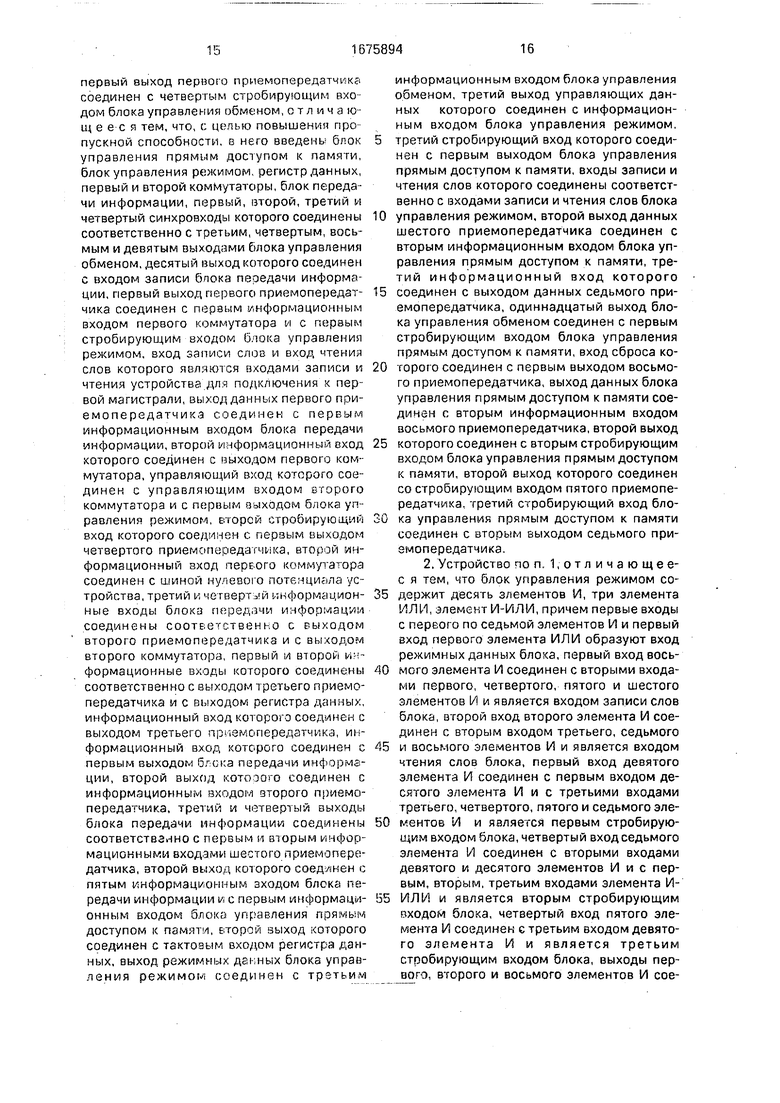

0 На фиг. 2 представлен пример реализации части блока 13 управления обменом, которая предназначена для формирования сигналов управления работой отдельных узлов устройства,

5 На фиг, 3 представлен пример реализации части блока 13 управления обменом, которая предназначена для формирования группы сигналов управления магистрали МПИ (устройство - инициатор на магистра0 ли ОШ), сигнала СХИ магистрали ОШ и сигнала сброса обмена.

На фиг. 4 представлен пример реализации части блока 13 управления обменом, которая предназначена для формирования

5 группы сигналов управления магистрали ОШ (устройство-инициатор на магистрали МПИ), сигнала ответа устройства в магистраль МПИ и сигнала сброса регистра 11 адреса.

0 Память, реализованная на фиг. 2 на D- триггерах 71-75, предназначена для формирования сигналов разрешения соответственно на шинах 30-33, 29 устройства. Элементы ИЛИ 87 и 88 предназначены

5 для формирования сигналов управления передатчиками 14 (управления обменом) и 16 (адреса-данных).

Элемент И-ИЛИ-НЕ 65 предназначен для формирования сигнала разрешения за0 писи данных из магистрали ПМИ в блок 12 передачи информации.

Комбинационная схема, реализованная на фиг. 2, состоит из схем установки и сброса соответствующих элементов памяти. Схе5 ма установки D-триггера 73 образована дешифратором 34 выполняемых в ПДП команд (ЧТС, ЧТСП, ЗПС, ЗПБ), элементом И-НЕ 55, элементом И 35.

Схема сброса D-триггера 73 образова0 на элементом 42 задержки и элементом И-ИЛИ-НЕ 62.

Схемы установки D-триггеров 71, 72, 74 и 75 реализованы соответственно на элементах И-ИЛИ 58, 59, 56 и 57, а схемы сбро5 са D-триггеров 71 и 72 - на элементе И-ИЛИ-НЕ 64, схемы сброса D-триггеров 74 и 75 - на элементе-ИЛ И-НЕ 91 и элементе И-ИЛИ-НЕ 63 соответственно.

Элементы 42, 44 и 45 задержки служат для выполнения временных соотношений в

последовательностях сигналов магистралей МПИ и ОШ. Одновибратор 98 служит для формирования короткого импульса по сбросу сигнала ДЧТ.

Элементы памяти, реализованные на фиг. 3 на D-триггерах 102-105, предназначены для формирования сигналов управления магистралями МПИ на шине 27 устройства. Элемент ИЛИ 89 и D-триггер 81 предназначены для формирования сигнала CXHj-, поступающего через соответствующие приемопередатчики в магистраль ОШ, Одновибратор 96 и элемент 52 задержки предназначены для формирования сигнала сброса обмена, поступающего с четвертого выхода блока 13 управления обменом на четвертый вход блока 10 управления ПДП. Элементы И 36, 37,101,38 и элемент И-ИЛИ 60 предназначены соответственно для установки D-триггеров 102-105, 81. Элемент ИЛИ-НЕ 92 и элементы И-ИЛИ-НЕ 66-68 предназначены соответственно для сброса D-триггеров 102-105.

Схема, состоящая из одновибратора 97, элемента И-ИЛИ-НЕ 69 и D-триггера 106, предназначена для сброса D-триггера 81.

Элементы 46-50 задержки предназначены для выполнения временных соотношений в последовательностях магистралей МПИиОШ.

Элементы памяти, реализованные на фиг. 4 на D-триггерах 82-85, предназначены для формирования сигналов управления магистрали ОШ.

Элемент 86 памяти служит для формирования сигнала ответа устройства в магистраль МПИ, элемент ИЛИ 90 - для формирования сигнала управления приемопередатчиками 4 (управления обменом). Элемент И-ИЛИ-НЕ 70 служит для сброса D-триггеров 82-84 и для формирования сигнала сброса регистра 11 адреса. Элементы И 39-41 и элемент И-ИЛИ 61 соответственно Служат для установки D-триггеров 83-85 и 86. Элементы ИЛИ-НЕ 93 и 94 и одновиб- раторы 99 и 100 предназначены для сброса D-триггеров 86 и 86. Элементы 53 и 54 задержки служат для выполнения временных соотношений в последовательностях сигналов магистралей МПИ и ОШ.

Устройство, реализованное по предлагаемой схеме, не требует специального программного обеспечения. Задержка при обмене данными в ПДП, вносимая устройством, не превышает 1,5 мкс.

Формула изобретения

1. Устройство сопряжения двух магистралей, содержащее восемь приемопередатчиков, регистр адреса, блок управления обменом, вход-выход первого приемопередатчика является входом устройства для подключения к шинам адреса первой магистрали, входы-выходы второго и третьего приемопередатчиков являются входом-выходом устройства для подключения к шинам данных первой магистрали, входы-выходы четвертого и пятого приемопередатчиков являются входами-выходами устройства для подключения к шинам управления первой

0 магистрали, вход-выход шестого приемопередатчика является входом-выходом устройства для подключения к шинам адрес-данные второй магистрали, входы- выходы седьмого и восьмого приемопере5 датчиков являются входами-выходами устройства для подключения к шинам управления второй магистрали, информационный вход первого приемопередатчика соединен с выходом регистра адреса, пер0 вый информационный вход которого соединен с первым выходом шестого приемопередатчика, второй выход которого соединен с вторым информационным входом регистра адреса, вход сброса которого

5 соединен с первым выходом блока управления обменом, вход записи регистра адреса соединен с входом записи блока управления обменом и с первым выходом седьмого приемопередатчика, второй выход которого

0 соединен с первым стробирующим входом блока управления обменом и с синхровхо- дом регистра адреса, вход чтения которого соединен с синхровходом первого приемопередатчика и с вторым выходом блока уп5 равления обменом, третий, четвертый, пятый, шестой и седьмой выходы которого соединены соответственно с синхровхода- ми второго, третьего, четвертого, шестого и седьмого приемопередатчиков, первый вы0 ход управляющих данных блока управления обменом соединен с информационным входом четвертого приемопередатчика, выход которого соединен с первым входом управляющей информации блока управления об5 меном, второй вход управляющей информации которого соединен с информационным выходом седьмого приемопередатчика, информационный вход которого соединен с вторым выходом управляющих

0 данных блока управления обменом, выход прерывания пятого приемопередатчика соединен с вторым стробирующим входом блока управления обменом, третий строби- рующий вход которого соединен с первым

5 выходом восьмого приемопередатчика, информационный выход которого соединен с информационным входом пятого приемопередатчика, первый информационный выход которого соединен с первым информационным входом восьмого приемопередатчика,

первый выход первого приемопередатчика соединен с четвертым стробирующим входом блока управления обменом, отличающееся тем, что, с целью повышения пропускной способности, в него введены блок управления прямым доступом к памяти, блок управления режимом, регистр данных, первый и второй коммутаторы, блок передачи информации, первый, второй, третий и четвертый синхровходы которого соединены соответственно с третьим, четвертым, восьмым и девятым выходами блока управления обменом, десятый выход которого соединен с входом записи блока передачи информации, первый выход первого приемопередатчика соединен с первым информационным входом первого коммутатора и с первым стробирующим входом блока управления режимом, вход записи слов и вход чтения слов которого являются входами записи и чтения устройства для подключения к первой магистрали, выход данных первого приемопередатчика соединен с первым информационным входом блока передачи информации, второй информационный вход которого соединен с выходом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора и с первым выходом блока управления режимом, второй стробирующий вход которого соединен с первым выходом четвертого приемопередатчика, второй информационный вход первого коммутатора соединен с шиной нулевого потенциала устройства, третий и четвертый информационные входы блока передачи информации соединены соответственно с выходом второго приемопередатчика и с выходом второго коммутатора, первый и второй информационные входы которого соединены соответственно с выходом третьего приемопередатчика и с выходом регистра данных, информационный вход которого соединен с выходом третьего приемопередатчика, информационный вход которого соединен с первым выходом блока передачи информации, второй выход которого соединен с информационным входом второго приемопередатчика, третий и четвертый выходы блока передачи информации соединены соответственно с первым и вторым информационными входами шестого приемопередатчика, второй выход которого соединен с пятым информационным входом блока передачи информации и с первым информационным входом блока управления прямым доступом к памяти, второй выход которого соединен с тактовым входом регистра данных, выход режимных данных блока управления режимом соединен с третьим

информационным входом блока управления обменом, третий выход управляющих данных которого соединен с информационным входом блока управления режимом.

третий стробирующий вход которого соединен с первым выходом блока управления прямым доступом к памяти, входы записи и чтения слов которого соединены соответственно с входами записи и чтения слов блока

0 управления режимом, второй выход данных шестого приемопередатчика соединен с вторым информационным входом блока управления прямым доступом к памяти, третий информационный вход которого

5 соединен с выходом данных седьмого приемопередатчика, одиннадцатый выход блока управления обменом соединен с первым стробирующим входом блока управления прямым доступом к памяти, вход сброса ко0 торого соединен с первым выходом восьмого приемопередатчика, выход данных блока управления прямым доступом к памяти соединен с вторым информационным входом восьмого приемопередатчика, второй выход

5 которого соединен с вторым стробирующим входом блока управления прямым доступом к памяти, второй выход которого соединен со стробирующим входом пятого приемопередатчика, третий стробирующий вход бло0 ка управления прямым доступом к памяти соединен с вторым выходом седьмого приемопередатчика.

2, Устройство по п. 1,отличающее- с я тем, что блок управления режимом со5 держит десять элементов И, три элемента ИЛИ, элемент И-ИЛИ, причем первые входы с первого по седьмой элементов И и первый вход первого элемента ИЛИ образуют вход режимных данных блока, первый вход вось0 мого элемента И соединен с вторыми входами первого, четвертого, пятого и шестого элементов И и является входом записи слов блока, второй вход второго элемента И соединен с вторым входом третьего, седьмого

5 и восьмого элементов И и является входом чтения слов блока, первый вход девятого элемента И соединен с первым входом десятого элемента И и с третьими входами третьего, четвертого, пятого и седьмого эле0 ментов И и является первым стробирующим входом блока, четвертый вход седьмого элемента И соединен с вторыми входами девятого и десятого элементов И и с первым, вторым, третьим входами элемента И5 ИЛИ и является вторым стробирующим входом блока, четвертый вход пятого элемента И соединен е третьим входом девятого элемента И и является третьим стробирующим входом блока, выходы первого, второго и восьмого элементов И соединены с вторым, третьим и четвертым входами первого элемента ИЛИ, выход которого соединен с четвертым и пятым входами элемента И-ИЛИ, шестой и седьмой входы которого соединены соответственно с выходами третьего и четвертого элементов И, восьмой вход элемента И-ИЛИ соединен с первым входом второго элемента ИЛИ и с выходом пятого элемента И, первый вход третьего элемента ИЛИ соединен с первым входом первого элемента ИЛИ, вторые входы второго и третьего элементов ИЛИ соединены соответственно с выходами пятого и четвертого элементов И, выход шестого элемента И соединен с четвертым входом девятого и третьим входом десятого элементов И, выход элемента И-ИЛИ, выходы второго и третьего элементов ИЛИ, выходы седьмого и девятого элементов И подключены к выходу режимных данных блока, а выходы шестого и десятого элементов И подключены соответственно к первому и второму выходам блока,

3. Устройство по п. 1,отличающее- с я тем. что блок управления прямым доступом к памяти содержит узел сравнения, дешифратор, узел счетчиков, десять триггеров, шесть элементов И, два элемента И-ИЛИ, три элемента И-ИЛИ-НЕ, выход первого триггера соединен с первыми входами первого элемента И-ИЛИ и первого элемента И-ИЛИ-НЕ и подключен к первому выходу блока, выход второго элемента И- ИЛИ подключен к второму выходу блока, второй, третий, четвертый входы первого элемента И-ИЛИ соединены между собой и с первым входом второго элемента И-ИЛИ и подключены к входу чтения слов блока, пятый, шестой, седьмой и восьмой входы первого элемента И-ИЛИ объединены между собой и подключены к входу записи слов блока, второй вход первого элемента И- ИЛИ-НЕ подключен к первому стробирую- щему входу блока, вход сброса которого подключен к третьему и четвертому входам первого элемента И-ИЛИ-НЕ, к первому и второму входам второго элемента И-ИЛИ- НЕ и к первому и второму входам третьего элемента И-ИЛИ-НЕ, второй и третий входы второго элемента И-ИЛИ объединены между собой и подключены к второму стробиру- ющему входу блока, третий стробирующий вход которого подключен к D-входам второго и третьего триггеров, тактовый вход узла счетчиков соединен с тактовыми входами четвертого и пятого триггеров, с первым входом первого элемента И, с девятым, десятым и одиннадцатым входами первого элемента И-ИЛИ и подключен к первому информационному входу блока, второй вход

первого элемента И соединен с первым входом второго элемента И, с третьим входом третьего элемента И ИЛИ-НЕ и подключен к первому информационному входу блока ,

второй информационный вход которого подключен к адресному входу узла счетчиков, к первому входу узла сравнения, к D-входу шестого триггера и к информационному входу дешифратора, второй вход второго элемента

0 И, четвертый вход третьего элемента И-ИЛИ- НЕ, первый вход третьего элемента И, управляющий вход узла сравнения и третий вход второго элемента И-ИЛИ-НЕ подключены к третьему информационному входу блока,

5 причем третий и четвертый входы второго элемента И-ИЛИ-НЕ объединены между собой, первый вход третьего элемента И соединен с первым входом четвертого элемента И, выход первого элемента И-ИЛИ

0 и выход седьмого триггера подключены к выходу данных блока, причем выход первого элемента И-ИЛИ соединен с D-входом седьмого триггера, выход которого соединен с пятым входом третьего элемента И5 ИЛИ-НЕ, выход третьего элемента И соединен с тактовым входом шестого триггера и с входом разрешения счета узла счетчиков, вход сброса которого соединен с входами сброса первого, четвертого, пято0 го, шестого, восьмого, девятого и десятого триггеров и с выходом первого элемента И-ИЛИ-НЕ, первый и второй выходы узла сравнения соединены соответственно с тактовыми входами второго и третьего тригге5 ров, входы сброса которых соединены с выходом второго элемента И-ИЛИ-НЕ, пятый и шестой входы которого соединены соответственно с выходами второго и третьего триггеров и с вторыми входами третьего

0 и четвертого элементов И, выход четвертого элемента И соединен с управляющим входом дешифратора, первый и второй выходы которого соединены с тактовыми входами соответственно девятого и десятого тригге5 ров, D-входы которых соединены с шиной единичного потенциала устройства, выход девятого триггера соединен с двенадцатым и тринадцатым входами первого элемента И-ИЛИ и с четвертым входом второго эле0 мента И-ИЛИ, пятый вход которого соединен с четырнадцатым, пятнадцатым и шестнадцатым входами первого элемента И-ИЛИ и с выходом десятого триггера, причем шестой вход второго элемента И-ИЛИ

5 подключен к входу записи слоь блока, а седьмой вход второго элемента И-ИЛИ соединен с семнадцатым и восемнадцатым входами первого элэмента И-ИЛИ и с выходом пятого элемента И, первый вход которого соединен с D-входом пятого триггера и

прямым выходом четвертого триггера, инверсный выход которого соединен с D-вхо- дом четвертого триггера, выход пятого триггера соединен с первым входом шестого элемента И, второй вход которого соединен с прямым выходом восьмого триггера, инверсный выход которого соединен с D- входом восьмого триггера и с вторым входом пятого элемента И, выход шестого элемента И соединен с восьмым входом второго и восемнадцатым входом первого элементов И-ИЛИ, тактовый вход восьмого триггера соединен с выходом первого элемента И, выход второго элемента И соединен с тактовым входом седьмого триггера, вход сброса которого соединен с выходом третьего элемента И-ИЛИ-НЕ, тактовый вход первого триггера соединен с выходом узла счетчиков, D-вход первого триггера соединен с шиной единичного потенциала, девятнадцатый вход первого элемента И-ИЛИ соединен с выходом шестого триггера.

иъ8яо ка15

25

wsSnoKaS Я (Ч) ЪЪ(2)

3/

30 25

г 27

В иск 10

26М

Фм.Ъ

26$

схи

Из блока 5

jy/Й 33(2) Л-М

88лок4

8 блок 11

таге 27(2,3} 27

Ц

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом | 1986 |

|

SU1444788A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

Изобретение относится к вычислительном технике и может быть использовано для сопряжения магистрали МПИ с внешними устройствами, имеющими интерфейс Общая шина (ОШ). Целью изобретения является повышение пропускной способности магистрали, Устройство содержит приемопередатчики, блок управления режимом, коммутаторы, регистр данных, блок управления ПДП, регистр адреса, блок передачи информации, блок управления обменом. 2 з.п. ф-лы, 10 ил.

ШигМ

Из5лока13 fflg

20

Jffcffd

Ъ1Ю

Z1

ЧТсяоб

t/ГС

1111

№

ЗПС

Из 5ша1

JSulL

400:01

113

ЗП8

11H

№& )

CX3

115

ЗП5

116

vrc

AOQ:0

со о:

117

tz

CWMK

120

ЗЛС-,

m

1/9

ЗПБ1

85лом 7t9

107

УСТТАА й(Сб)

108

СХИ1

109

в блок8

Фиг. 5

дзл

ИэблокаМ

фиг. 6

I

ex

Мз блока 14

Из блока 16

28 Из блока 1329

06М

А&-+А Т

ЖЈ

8йлох1

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211743A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессорные средства и системы | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-09-07—Публикация

1988-11-22—Подача