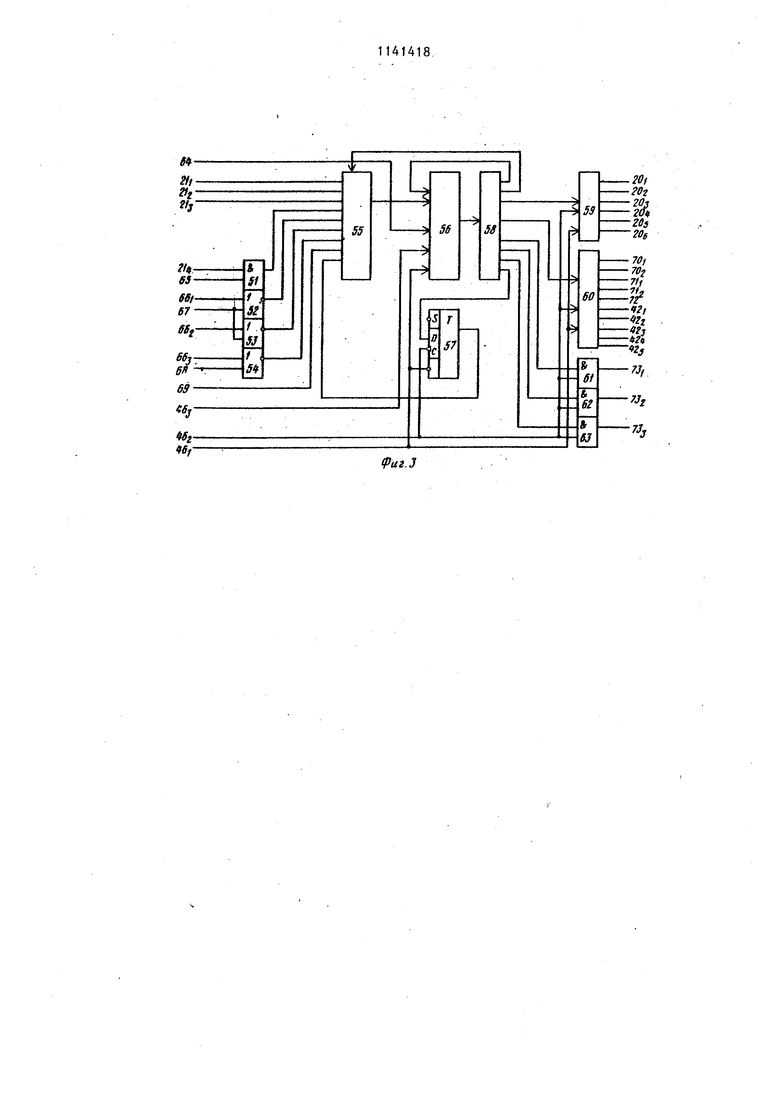

регистра приказов, информационный и управляющий входы которого соединены соответственно с первым информационным входом устройства и шестым выходом блока управления обменом, второй выход блока задания адреса соеди ней с первым информационным входом блока сравнения адреса, второй информационньй вход которого является вторым информационным входом устройства и соединен с информационным входом регистра данных и команд, управляющий вход которого и информационный вход регистра словосостояния соединен соответственно с пятым и шестым выходами блока связи с каналом ввода-вывода, причем блок связи с каналом ввода-вывода содержит мультиплексор, триггер ветвления,память микропрограмм, регистр адреса микро команды, регистр сигналов абонента, регистр сигналов управления, четыре элемента И и три элемента ИЛИ-НЕ, причем выход и первый вход регистра адреса микрокоманд соединены соответственно с входом и первым выходом памяти микропрограмм, второй и третий информационные входы -.соответственно с седьмым входом блока и выходом мультиплексора,а входы синхронизации и сброса - с первьм входом бйока, группа информационных входов мультиплексора подключена к второму и шестому входам блока, выходам первого элемента И и первого, второго и третьего элементов ИЛИ-НЕ и- выходу триггера ветвления, а управляющий вход - к второму выходу памяти микропрограмм, с .третьего по пятый выходы которой соединены

соответственно с информационными входами регистра сигналов абонента, регистра сигналов управления и триггера ветвления, входы синхронизации .и сброса которых соединены с первым В;Ходом блока, первые входы-второго,

третьего и четвертого элементов И подключены соответственно к шестому, седьмому и восьмому выходам памяти микропрограмм, вторые входы к первому входу блока, а выходы образуют шестой выход блока, выход регистра сигналов .абонента является: вторым выходом блока, разрядные выходы регистра .сигналов управления являются соответственно первь, третьим, четвертым и пятым выходами блока, первый и второй входы пер41418

вого элемента И соединены соответственно с вторым и пятым входами ; блока, первый и второй входы первого элемента ИЛИ-НЕ и первые входы второго и третьего элементов ИЛИ-НЕ . образуют восьмой вход блока, вторые входы второго и третьего элементов ИЛИ-НЕ являются соответственно четвертым и третьим входами блока, причем блок управления обменом содержит четыре элемента ИЛИ-НЕ, семь элементов И-НЕ, дешифратор, формирователь импульса, триггер, два элемента НЕ и три элемента- И, причем выход первого элемента ИЛИ-НЕ соединен с входом сброса триггера, информационный вход которого подключен к шине логического нуля, а синхровход и вход установки соединены с выходами первого и второго элементов И-НЕ, выход второго элемента ИЛИ-НЕ соеди. нен с первым входом первого элемента И-НЕ, первые входы второго и третьего элементов И-НЕ и первого элемента И соединены с прямым выходом формирователя импульса, инверсный выход которого подключен к первьм вхо- дам второго и третьего элементов И, .первые йходы четвертого и пятого элементов И-НЕ соединены соответственно с прямым и инверсным .выходами триггера, вторые входы - с вторым входом блока, а выходы - соответственно с первы ш входами шестого и седьмого элементов И-НЕ, выходы которых образуют первый выход блока, а вторые входы соединены соответственно с четвертым входом блока и через первый элемент НЕ с третьим входом блока, выход третьего элемента

I ...

И-НЕ соединен с входом второго элемента НЕ, выход которого и выход первого элемента И-НЕ образуют второй выход блока, первый выход дешифратора соединен с первыми входами/ второго и третьего элементов ИЛИ-НЕ, второй выход - с первым входом четвертого элемента ИЛИ-НЕ, выход которого является шестым выходом блока, третий выход дешифратора подключен к второму входу первого элемента И, выходы первого и второго элементов и образуют четвертый выход блока, выходы третьих элемента ИЛИ-НЕ и элемента И образуют третий выход блокаj выходы первого элемента ИЛИ-НЕ и формирователя импульса образуют пятый . выход блока, первый вход первого элемента ИЛИ-НЕ, вторые входы второго, третьего и четвертого элементов ИЛИ-НЕ, вход формирователя импульса и группа, входов дешифратора соединены с первым

1141418

входом блока, вторые входы первого элемента ИЛИ-НЕ, второго и третьего элементов И-НЕ, второго и третьего элементов I И образуют пятый вход блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ ОБЪЕКТАМИ | 1993 |

|

RU2018944C1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее первый и второй буферные регистры, блок управления обменом, регистр словосостояния, блок коммутации, причем информационный вход первого буферного регистра соединен с первым информационным входом устройства, информационный выход второго буферного регистра соединен с первым информационным выходом устройства и информационным вьгходом регистра словосостояния, выход блока коммутации является вторым информационным выходом устройства, первые выход и.вход блока управления обменом являются соответственно выходом прерывания и управляющим входом устройства, а второй, третий и четвертый выходы соответственно соединены с управляющими входами второго и первого буферных регистров и регистра словосостояния, отличающееся тем, что, с целью расширения класса решаемых задач и повьшения пропускной способности устройства, в него введены блок связи с каналом ввода - вывода, блок задания адреса, блок сравнения адреса, регистр данных и команд, регистр данных и состояний, регистр приказов и блок контроля, причем второй, третий и четвертый входы блока управления обменом соединены соответственно с управляющими выходами Второго и первого буферных регистров и регистра словосостояния, а пя-г тые вход и выход - соответственно с первыми выходом и входом блока связи с каналом ввода-вывода, вторые вход и выход которого являются соответственно входом и выходом синхронизации устройства, третьи вход и (Л выход соединены соответственно с управляющим выходом второго буферного регистра и управляющим входом регистра данных и состояний, информацион-; ный вход и выход которого соединены соответственно с информационным выходом первого буферного регистра и с информационным входом блока коммутации, второй информационный и управляющий входы которого соедине4; ны соответственно с первым выходом .блока задания адреса и четвертым выходом блока связи с каналом вводавывода, четвертый вход которого соЭО единен с управляющим выходом первого буферного регистра, пятый и шес той входы - соответственно с выходами блока сравнения адреса и блока контроля, входом соединенного с выходом регистра данных и команд, информационным входом второго буферного регистра и седьмым входом блока связи с каналом ввода-вывода,, восьмой вход которого соединен с выходом

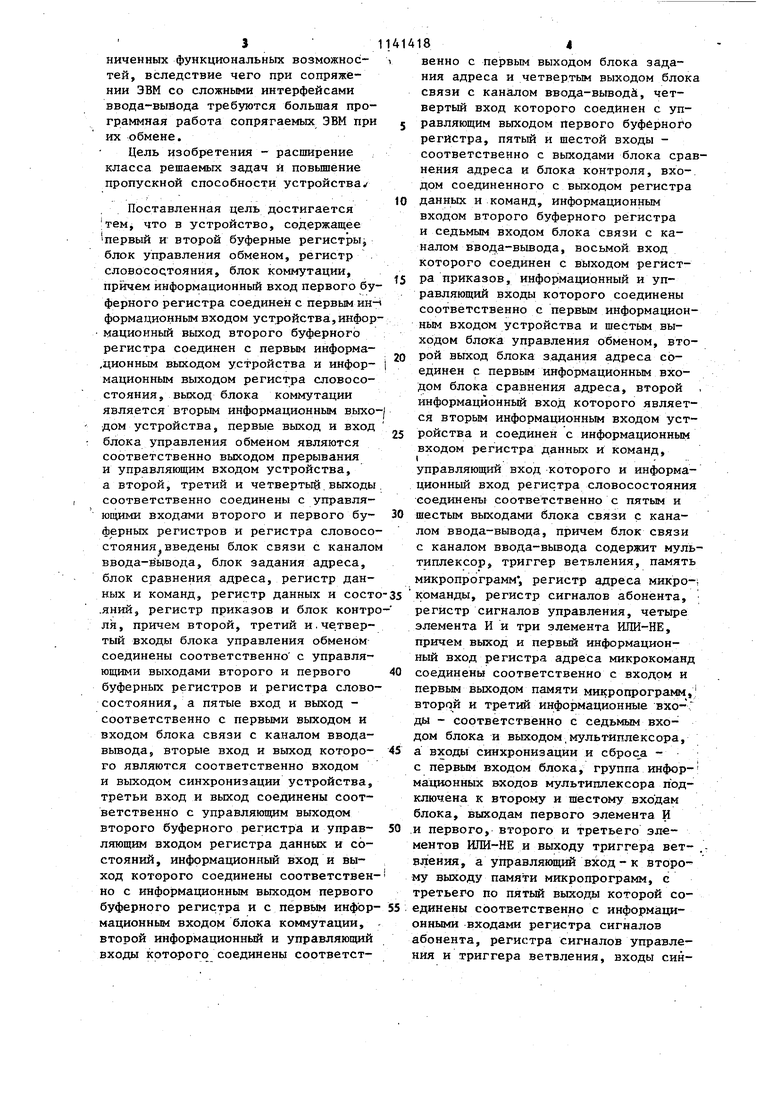

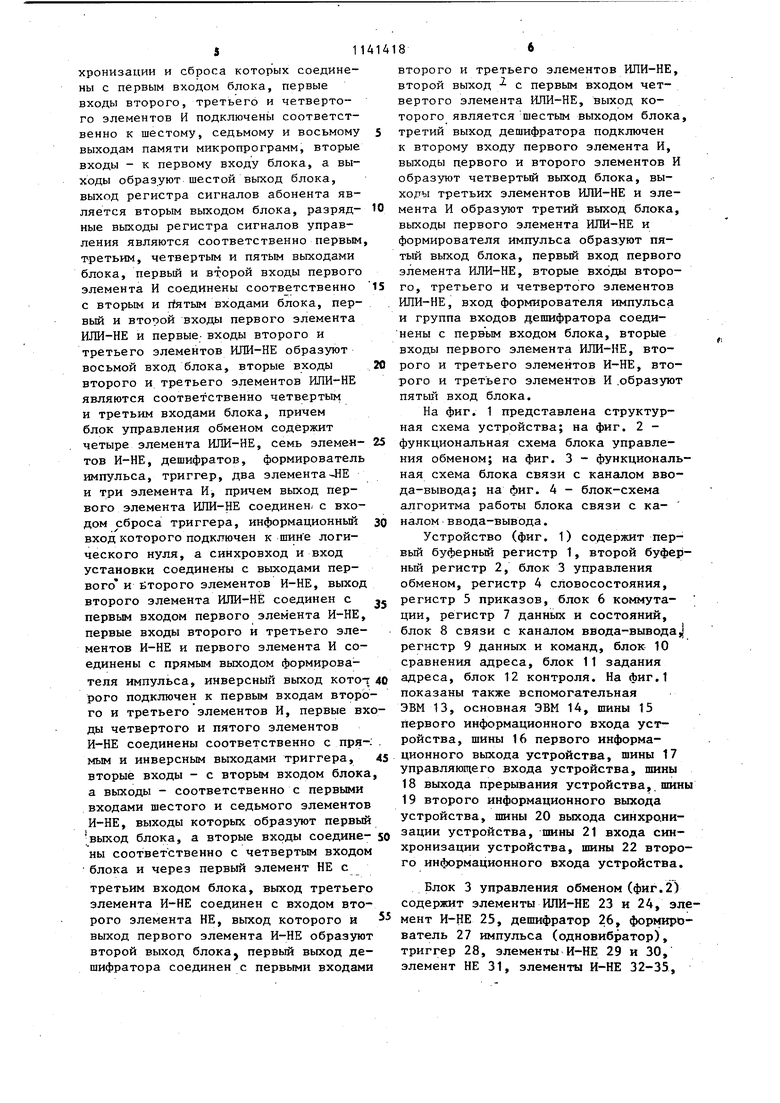

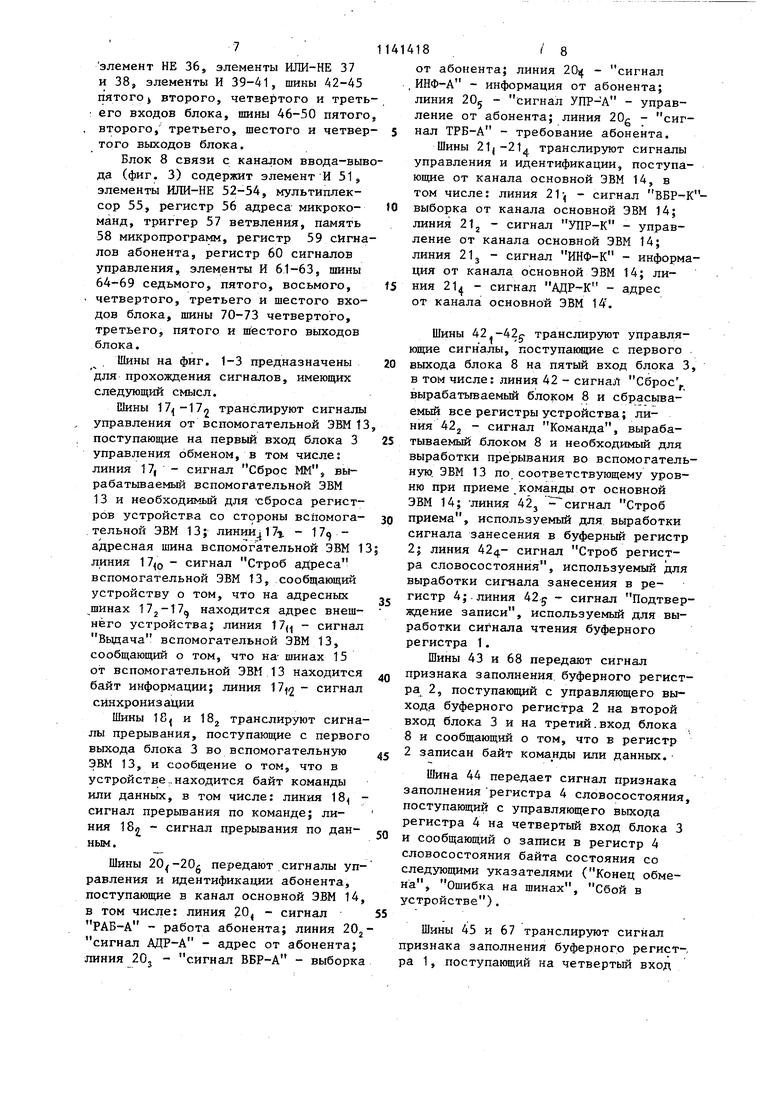

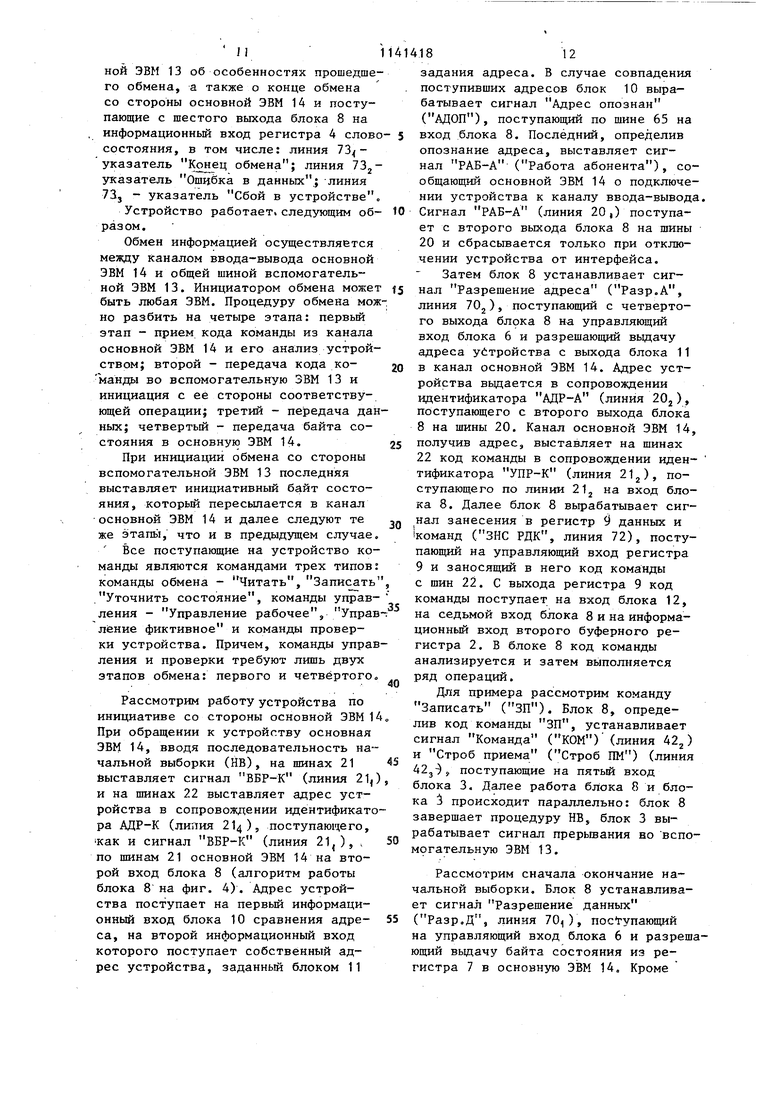

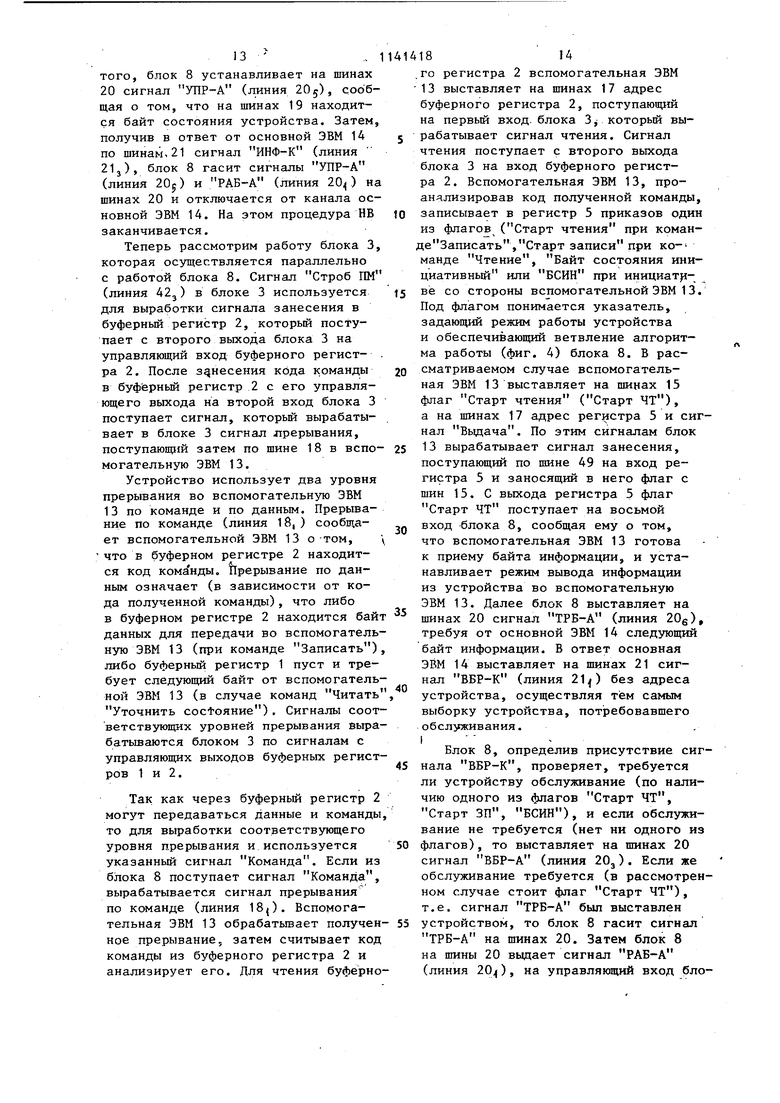

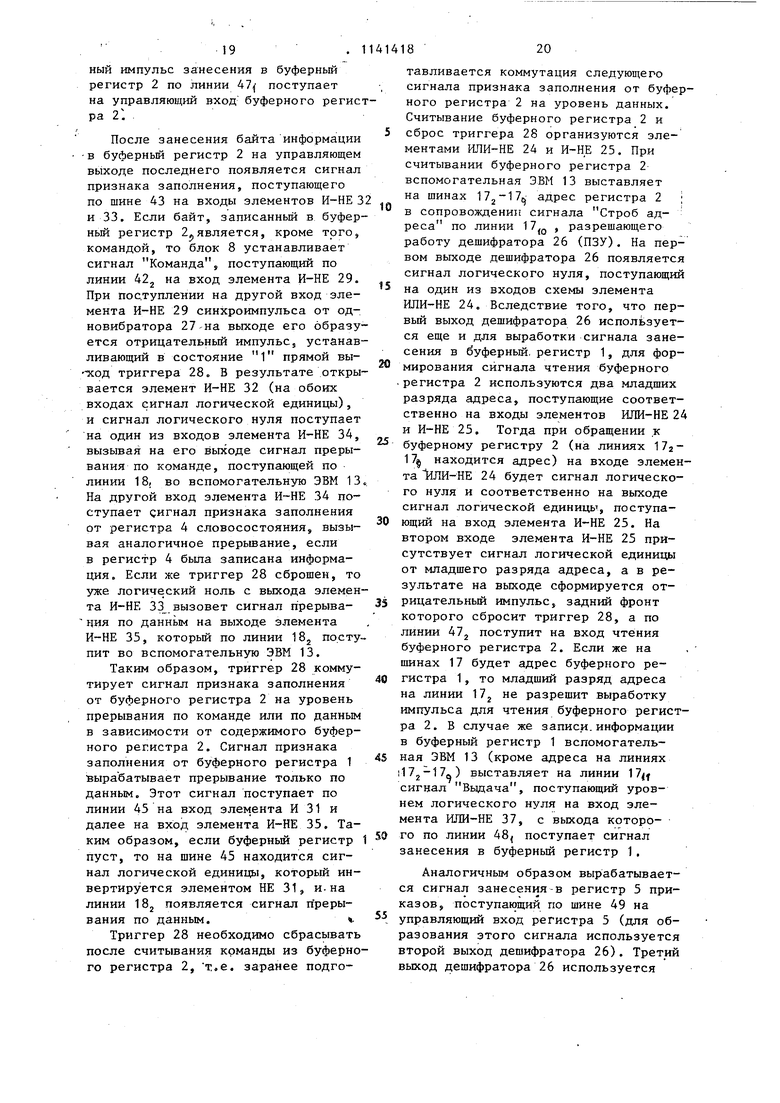

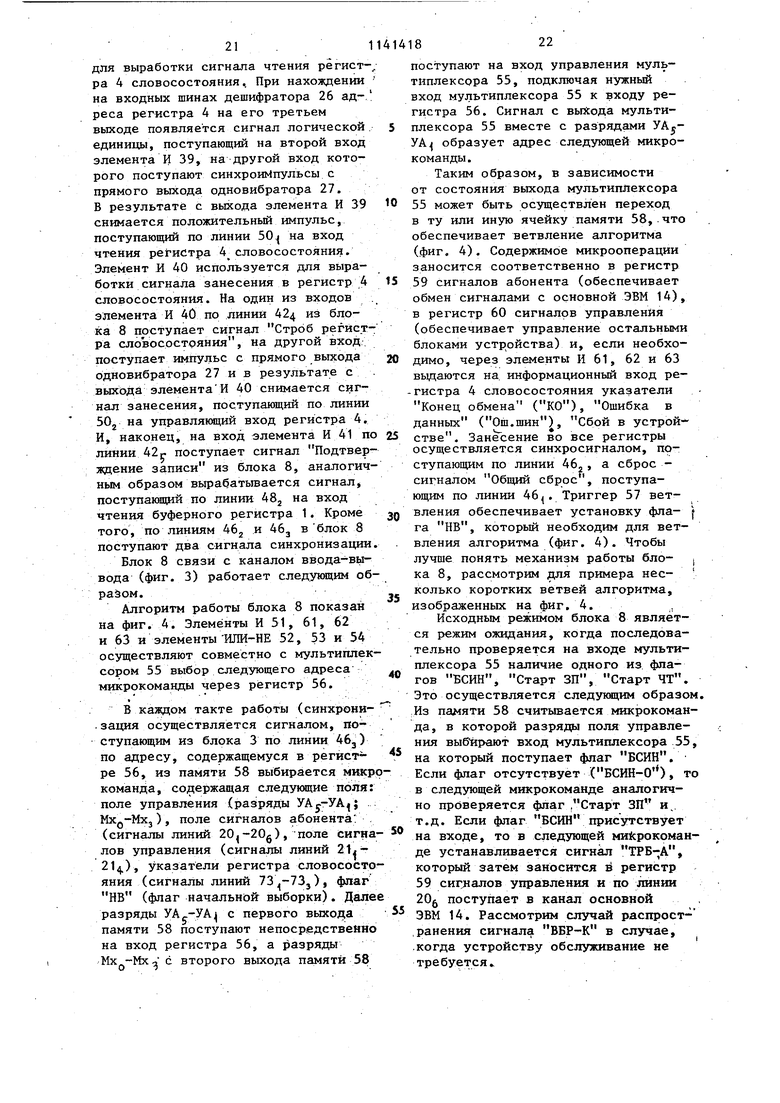

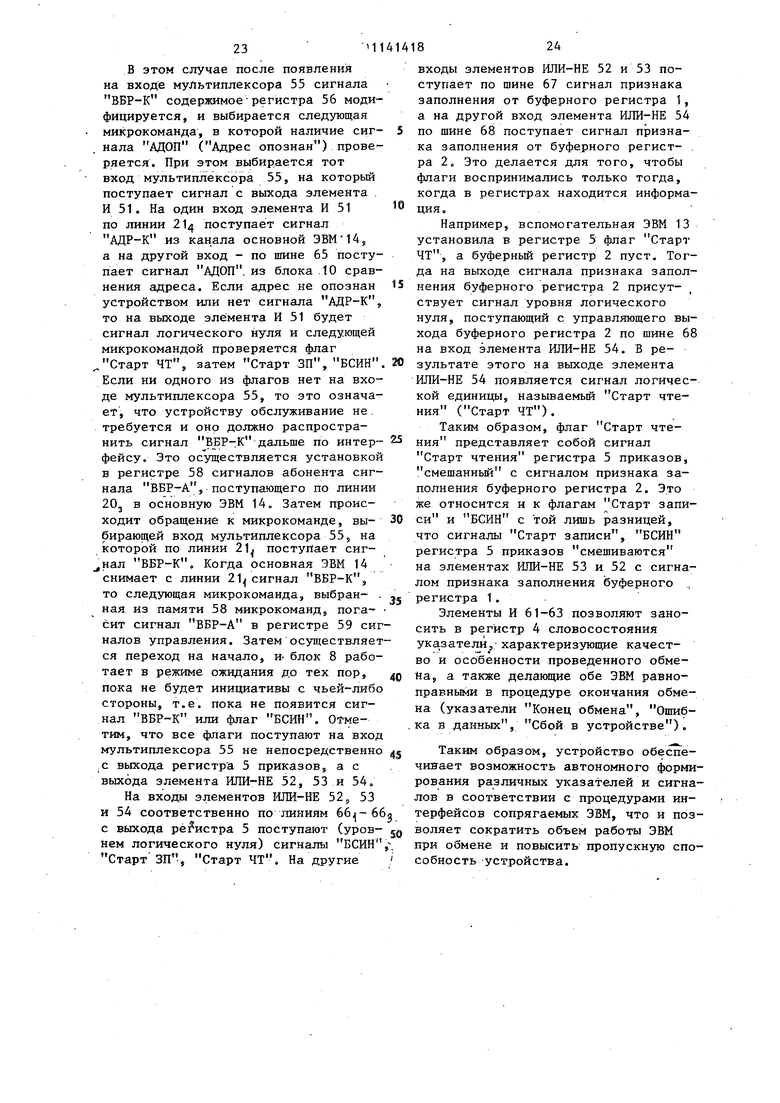

Изобретение относится к вычислительной технике ц может найти применение в многомашинных вычислительных комплексах, региональных и локальных сетях ЭВМ, системах автоматизации . производства и научных исследований для связи между собой вычислительных машин различного типа и функционального назначения . Известны устройства для сопряжекия ЭВМ, содержащие дешифратор, коммутатор, блок формирования управляющих сигналов, блоки усиления, блок обмена, согласователь, блок выполнения прерываний, регистр управления l Устройство имеет ограниченную область применения, так как обеспечивает связи хотя и разнотипных ЭВМ, но относящихся к классу мини-ЭВМ, имеющих упрощенные интерфейсы ввода-вывода и не позволяющих создавать высокопроизводительные вычислительные комплексы. Кроме того, устройство имеет ряд функциональных ограничений, таких как невозможность чтения регистра управления со стороны основной ЭВМ, что лишает ее информации о возникаюпщх в устройстве ситуациях, необходимость основной ЭВМ быть постоянно готовой к приему данных со стороны вспомогательной ЭВМ из-за отсутствия возможности обработки прерываний, неравноправность ЭВМ при определении окончания операции передачи данных. Наиболее близким к изобретению по технической сущности является устройство для сопряжения ЭВМ, содержащее первый и второй буферные регистры, блок управления обменом, первый и второй блоки выдачи, регист словосостояния, блок подсчета времени, причем первый, второй, третий, четвертый, пятый и шестой выходы блока управления обменом соединены : соответственно с первым выходом устройства, с управляющим входом первого буферного регистра, с управляющим входом второго буферного регистра, с вторым выходом устройства, с управляющим входом первого блока вьщачи, с управляющимвходом регистра словосостояния, первый информационный вход которого соединен с первым входом устройства и с информационным входом первого буферного регистра, второй вход устройства соединен с информационным входом второго буферного .регистра и с вторым информационным входом регистра словосостояния, выход которого соединен с информационным входом первого блока выдачи, выход первого буферного регистра и выход первого блока вьщачи соединен с третьим выходом устройства, выход второго буферного регистра соединен с четвертым выходом устройства, третий, четвертый и пятый входы устройства соединены соответственно с первым, вторым и третьим входами блока управления обменом, информационный вход второго блока вьщачи соединен с выходом регистра словосостояния, а управляющий вход второго блока вьщачи соединен с седьмым выходом блока управления обменом, выход второго блока выдачи соединен с четвертым выходом устройства, восьмой выход блока управления обменом соединен с входом блока подсчета времени, выход которого соединен с четвертым входом блока управления обменом Y. Недостаток известного устройства состоит в ограниченном классе решаемых задач и низкой пропускной способности устройства из-за его огра3ниченных функциональных возможностей, вследствие чего при сопряжении ЭВМ со сложными интерфейсами ввода-вывода требуются большая программная работа сопрягаемых ЭВМ при их обмене. Цель изобретения - расширение класса решаемых задач и повьш1ение пропускной способности устройства/ Поставленная цель достигается |тем, что в устройство, содержащее первый и второй буферные регистры, блок управления обменом, регистр словосостояния, блок коммутации, причем информационный вход первого бу ферного регистра соединен с первым инч формационным входом устройства, инфор мационный выход второго буферного регистра соединен с первым информа- .ционным выходом устройства и информационным выходом регистра словосостояния, выход блока коммутации является вторым информационным вьгко дом устройства, первые выход и вход блока управления обменом являются соответственно выходом прерывания и управляющим входом устройства, а второй, третий и четвертый.выходы соответственно соединены с управляющими входами второго и первого буферных регистров и регистра словосо стояния введены блок связи с канало ввода-вывода, блок задания адреса, блок сравнения адреса, регистр данных и команд, регистр данных и сост .яний, регистр приказов и блок контр ля, причем второй, третий и.че.твертый входы блока управления обменом соединены соответственно с управляющими выходами второго и первого буферных регистров и регистра слово состояния, а пятые вход и выход соответственно с первыми выходом и входом блока связи с каналом вводавывода, вторые вход и выход которого являются соответственно входом и выходом синхронизации устройства, третьи вход и выход соединены соответственно с управляющим выходом второго буферного регистра и управляющим входом регистра данных и состояний , информационный вход и выход которого соединены соответствен но с информационным выходом первого буферного регистра и с первым инфор мационным входом блока коммутации, второй информационный и управляющий входы которого соединены соответст184венно с первым выходом блока задания адреса и четвертым выходом блока связи с каналом ввода-вывода, четвертый вход которого соединен с управляющим выходом первого буферного регистра, пятый и шестой входы соответственно с выходами блока сравнения адреса и блока контроля, вхо-. дом соединенного с выходом регистра данных и команд, информационным входом второго буферного регистра и седьмым входом блока связи с каналом ввода-вьшода, восьмой вход которого соединен с выходом регистpa приказов, информационный и управляющий входы которого соединены соответственно с первым информационным входом устройства и шестым выходом блока управления обменом, второй выход блока задания адреса соединен с первым информационным входом блока сравнения адреса, второй информационный вход которого является вторым информационным входом устройства и соединен с информационным входом регистра данных и команд, управляющий вход которого и информационный вход регистра словосостояния соединены соответственно с пятым и шестым выходами блока связи с каналом ввода-вывода, причем блок связи с каналом ввода-вьшода содержит мультиплексор, триггер ветвления, память микропрограмм, регистр адреса микро-; команды, регистр сигналов абонента, регистр сигналов управления, четыре элемента И и три элемента ИПИ-НЕ, причем выход и первый информационный вход регистра адреса микрокоманд соединены соответственно с входом и первым выходом памяти микропрограмм, второй и третий информационные вхо-г ды - соответственно с седьмым входом блока и выходом,мультиплексора, а входы синхронизации и сброса с первым входом блока, группа информахщонных входов мультиплексора подключена к второму и шестому входам блока, выходам первого элемента И и первого, второго и третьего элементов ИПИ-НЕ и выходу триггера вет- .: вления, а управляющий вход - к второму выходу памяти микропрограмм, с третьего по пятый выходы которой соединены соответственно с информационными входами регистра сигналов абонента, регистра сигналов управления и триггера ветвления, входы синS11хронизации и сброса которых соединены с первым входом блока, первые входы второго, третьего и четвертого элементов И подключены соответственно к шестому, седьмому и восьмому выходам памяти микропрограмм, вторые входы - к первому входу блока, а выходы образуют шестой вьссод блока, выход регистра сигналов абонента является вторым выходом блока, разрядные выходы регистра сигналов управления являются соответственно первым третьим, четвертым и пятым выходами блока, первый и второй входы первого элемента И соединены соответственно с вторьм и Ifятым входами блока, первый и второй входы первого элемента ИЛИ-НЕ и первые, входы второго и третьего элементов ИЛИ-НЕ образуют восьмой вход блока, вторые входы второго и третьего элементов ИЛИ-НЕ являются соответственно четвертым и третьим входами блока, причем блок управления обменом содержит четыре элемента ИЛИ-НЕ, семь элементон И-НЕ, дешифратов, формирователь импульса, триггер, два элемента-НЕ и три элемента И, причем выход первого элемента ИЛИ-НЕ соединен, с входом сброса триггера, информационньй вход которого подключен к шине логического нуля, а синхровход и вход установки соединены с выходами первого и второго элементов И-НЕ, выход второго элемента ИЛИ-НЁ соединен с первым входом первого элемента И-НЕ, первые входы второго и третьего элементов И-НЕ и первого элемента И соединены с прямым выходом формирователя импульса, инверсный выход которого подключен к первым входам второ го и третьего элементов И, первые вх ды четвертого и пятого элементов И-НЕ соединены соответственно с прямым и инверсным выходами триггера, вторые входы - с вторым входом блока а выходы - соответственно с первыми входами шестого и седьмого элементов И-НЕ, выходы которых образуют первый выход блока, а вторые входы соединены соответственно с четвертым входом блока и через первый элемент НЕ с третьим входом блока, выход третьег элемента И-НЕ соединен с входом вто рого элемента НЕ, выход которого и выход первого элемента И-НЕ образую второй выход блокаJ первый выход де шифратора соединен с первыми входам второго и третьего элементов ИЛИ-НЕ, второй выход - с первым входом четвертого элемента ИЛИ-НЕ, выход которого является шестым выходом блока, третий выход дешифратора подключен к второму входу первого элемента И, выходы первого и второго элементов И образуют четвертый выход блока, выходы третьих элементов ИЛИ-НЕ и элемента И образуют третий выход блока, выходы первого элемента ИЛИ-НЕ и формирователя импульса образуют пятый выход блока, первый вход первого элемента ИЛИ-НЕ, вторые входы второго, третьего и четвертого элементов ИЛИ-НЕ, вход формирователя импульса и группа входов дешифратора соединены с первым входом блока, вторые входы первого элемента ИЛИ-НЕ, второго и третьего элементов И-НЕ, второго и третьего элементов И .образуют пятьй вход блока. На фиг. 1 представлена структурная схема устройства; на фиг. 2 функциональная схема блока управления обменом; на фиг. 3 - функциональная схема блока связи с каналом ввода-вывода; на фиг. 4 - блок-схема алгоритма работы блока связи с каналом ввода-вывода. Устройство (фиг. 1) содержит первый буферный регистр 1, второй буферный регистр 2, блок 3 управления обменом, регистр 4 словосостояния, регистр 5 приказов, блок 6 коммутации, регистр 7 данных и состояний, блок 8 связи с каналом ввода-вывода регистр 9 данных и команд, блок 10 сравнения адреса, блок 11 задания адреса, блок 12 контроля. На фиг.1 показаны также вспомогательная ЭВМ 13, основная ЭВМ 14, шины 15 первого информационного входа устройства, шины 16 первого информационного выхода устройства, шины 17 управляющего входа устройства, шины 18выхода прерывания устройства, шины 19второго информационного выхода устройства, шины 20 выхода синхронизации устройства, шины 21 входа синхронизации устройства, шины 22 второго информационного входа устройства. Блок 3 управления обменом (фиг.2) содержит элементы ИЛИ-НЕ 23 и 24, элемент И-НЕ 25, дешифратор 26, формирователь 27 импульса (одновибратор), триггер 28, элементы И-НЕ 29 и 30, элемент НЕ 31, элементы И-НЕ 32-35, 7 элемент НЕ 36, элементы ИЛИ-НЕ 37 и 38, элементы И 39-41, шины 42-45 пятогоJ второго, четвертого и треть : его входов блока, шины 46-50 пятого второго, третьего, шестого и четвер того выходов блока. Блок 8 связи с каналом ввода-выв да (фиг. 3) содержит элемент И 51, элементы ИЛИ-НЕ 52-54, мультиплексор 55, регистр 56 адреса микрокоманд, триггер 57 ветвления, память 58 микропрограмм, регистр 59 сигна лов абонента, регистр 60 сигналов управления, элементы И 61-63, шины 64-69 седьмого, пятого, восьмого, четвертого, третьего и шестого входов блока, шины 70-73 четвертого, третьего, пятого и шестого выходов блока. Шины на фиг. 1-3 предназначены для прохождения сигналов, имеющих следзпощий смысл. Шины транслируют сигналы управления от вспомогательной ЭВМ 13 поступающие на первый вход блока 3 управления обменом, в том числе; линия 17, - сигнал Сброс ММ, вырабатьшаемый вспомогательной ЭВМ 13 и необходимый для сброса регистров устройства со стороны вспомогательной ЭВМ 13; линии { 17j. - адресная шина вспомогательной ЭВМ 1 линия - сигнал Строб адреса вспомогательной ЭВМ 13, сообщающий устройству о том, что на адресных шинах 172-17д находится адрес внешнего устройства; линия 17( - сигнал Выдача вспомогательной ЭВМ 13, сообщающий о том, что на- шинах 15 от вспомогательной ЭВМ 13 находится байт информации; линия сигнал синхронизации Шины 18j и IBj транслируют сигна лы прерывания, поступающие с первог выхода блока 3 во вспомогательную ЭВМ 13, и сообщение о том, что в устройстве ..находится байт команды или данных, в том числе: линия 18 сигнал прерьшания по команде; линия 18 - сигнал прерывания по данным. Шины 20|-20g передают сигналы уп равления и идентификации абонента, поступающие в канал основной ЭВМ 14 в том числе: линия 20 - сигнал РАБ-А работа абонента; линия 20 сигнал АДР-А - адрес от абонента; линия 20з - сигнал ВБР-А - выборк 18/8 от абонента; линия 20 - сигнал ИНФ-А - информация от абонента; линия 20 - сигнал УПР-А - управление от абонента; линия 20g - сигнал ТРБ-А - требование абонента. Шины 21(-21ц транслируют сигналы управления и идентификации, поступающие от канала основной ЭВМ 14, в том числе: линия 21 - - сигнал ВБР-К выборка от канала основной ЭВМ 14; линия 21 - сигнал УПР-К - управление от канала основной ЭВМ 14; линия 21J - сигнал ИНФ-К - информация от канала основной ЭВМ 14; линия 21 - сигнал АДР-К - адрес от канала основной ЭВМ 14. Шины . транслируют управляющие сигналы, поступающие с первого выхода блока 8 на пятый вход блока 3, в том числе: линия 42 - сигнал Сброс вырабатываемый блоком 8 и сбрасываемый все регистры устройства; линия 42,, - сигнал Команда, вырабатываемый блоком 8 и необходимый для выработки прерывания во вспомогательную, ЭВМ 13 по соответствующему уровню при приеме команды от основной ЭВМ 14; -линия 42., - сигнал Строб приема, используемый для выработки сигнала занесения в буферный регистр 2; линия 424- сигнал Строб регистра словосостояния, используемый для выработки сигнала занесения в регистр 4;.линия 425 - сигнал Подтверждение записи, используемый для выработки сигнала чтения буферного регистра 1. Шины 43 и 68 передают сигнал признака заполнения, буферного регистра 2, поступающий с управляющего выхода буферного регистра 2 на второй вход блока 3 и на третий.вход блока 8 и сообщающий о том, что в регистр 2 записан байт или данных. Шина 44 передает сигнал признака заполнения регистра 4 словосостояния, поступающий с управляющего выхода регистра 4 на четвертый вход блока 3 и сообщающий о записи в регистр 4 словосостояния байта состояния со следующими указателями (Конец обмена, Ошибка на шинах, Сбой в стройстве). Шины 45 и 67 транслируют сигнал ризнака заполнения буферного регист-. а 1, поступающий на четвертый вход

9

блока 8 и третий вход блока 3 и сообщающий о записи в регистр 1 байта данных или состояния от вспомогательной ЭВМ 13. .

Шины служат для передачи сигналов управления, поступающих с пятого выхода блока 3 на первый вход блока 8, в том числе: линия 46 передает сигнал Общий сброс, сбрасывающий все регистры устройства в исходное состояние (кроме регистра 4 словосостояния, который сбрасывается чтением его); линия 46 сигнал синхронизации, поступающий на регистры блока 8; линия 463- сигнал синхронизации регистра 56 блока 8.

Шины 47, и 47 транслируют сигналы управляющие работой буферного регистра, 2, в том числе: линия 47, сигнал занесения в буферный регистр 2, поступающий с второго выхода блока 3 на управляющий вход буферного регистра 2; линия 472 - сигнал чтени буферного регистра 2, поступающий с второго выхода блока 3 на управляющий вход буферного регистра 2, при этом сигнал на управляющем выходе регистра 2 сбрасывается (т.е. сбрасывается признак заполнения).

Шины 484 и 48j передают сигналы, управляющие работой буферного регисра 1 , в том числе: линия 48, - сигнал занесения в буферньй регистр 1, поступающий с третьего выхода блока 3 на, управляюащй вход буферного регистра 1; линия 48 - сигнал чтения буферного регистра 1, поступающий с третьего выхода блока 3 на управляющий вход буферного регистра 1 .

Шина 49 передает сигнал занесения в регистр 5 приказов, поступающий с шестого выхода блока 3 на управляющий вход регистра 5 приказов.-...

.Шины 50 и 50j транслируют сигналы, управляющие работой регистра 4 словосостояния, в том числе: линия 50 - сигнал занесения в ре- гистр 4 словосостояния, поступающий с четвертого выхода блока 3 на управляющий вход регистра 4 словосостяния; линия 50,, - сигнал чтения регистра 4 словосостояния, поступающий с четвертого выхода блока 3 на управляющий вход (чтения) регистра 4 словосостояния, при этом сигнал

41810

на управляющем выходе (признак заполнения) сбрасьшается.

Шина 64 передает сигнал кода команды, записанный в регистр 9 данных и команд и поступающий с выхода регистра 9 данных и команд на седьмой вход блока В.

Шина 65 передает сигнал опознавания адреса устройства, вырабатываемый блоком 10 сравнения адреса и поступающий на пятый вход блока 8.

Шины транслируют флаговые сигналы, поступающие с выхода регистра 5 приказов на восьмой вход блока 8 и задающие режимы работы устройства, в том числе: линия (tdj- флаг БСИН .(байт состояния инициативный), сигнализирующий о вьщаче байта состояния в основную ЭВМ 14; линия 66 флаг Старт записи,, задающий режим записи информации из вспомогательной ЭВМ 13 в буферный регистр 1 с последующей вьщачей ее в канал основной ЭВМ 14; линия 66 - флаг Старт чтения, задающий режим чтения информации из устройства во вспомогательную ЭВМ 13.

Шина 69 передает сигнал Ошибка на Иннах, поступающий на шестой вход блока 8 с выхода блока 12 контроля, и сообщающий об ошибке в байте информации.

(Шины 70 и 70 Транслируют сигналы управления блоком 6 коммутации, поступающие с четвертого выхода блока 8 на управляющий вход блока 6, в том числе: линия 70 - сигнал, разрешающий вьщачу на шины 19 байта данных или состояния (Разрешение данных); линия 70 - сигнал, разрешающий вьщачу на шины 19 адреса устройства (Разрешение адреса).

Шины 714 и 712 транслируют сигналы управления регистром 7 данных и состояний, поступающие на управляющий вход регистра 7 с третьего выхода блока 8, в том числе: линия 71,сигнал занесения информации в регистр 7 данных и состояний; линия 71 jсигнал установки модификаторов КК, УК (Канал кончил, Устройство кончило) в байте состояния.

Шина 72 транслирует сигнал занесения в регистр 9 данных и команд, поступающий с пятого выхода блока 8 на управляющий вход регистра 9.

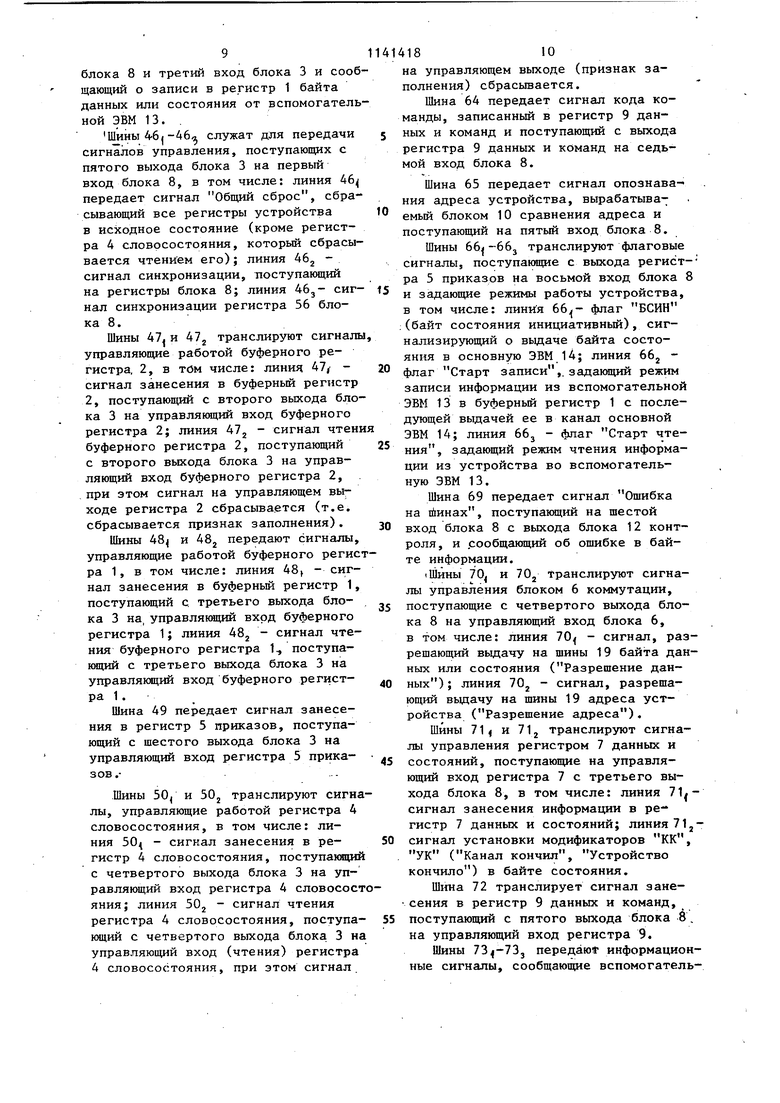

Шины 73|-73з передаю информационные сигналы, сообщающие вспомогатель II ной ЭВМ 13 об особенностях прошедше го обмена, а также о конце обмена со стороны основной ЭВМ 14 и поступающие с шестого выхода блока 8 на информациоиньй вход регистра 4 слов состояния, в том числе: линия указатель Конец обмена ; линия 73 указатель Ошибка в данных.; линия 73j - указатель Сбой в устройстве Устройство работает, следующим образ ом. Обмен информацией осуществляется между каналом ввода-вывода основной ЭВМ 14 и общей шиной вспомогательной ЭВМ 13. Инициатором обмена может быть любая ЭВМ. Процедуру обмена мож но разбить на четыре этапа: первый этап - прием кода команды из канала основной ЭВМ 14 и его анализ устройством; второй - передача кода команды во вспомогательную ЗИМ 13 и инициация с ее стороны соответствующей операции; третий - передача дан ных; четвертый - передача байта состояния в основную ЭВМ 14. При инициации обмена со стороны вспомогательной ЭВМ 13 последняя выставляет инициативный байт состояния, который пересьтается в канал основной ЭВМ 14 и далее следуют те же этапь, что и в предыдущем случае Все поступающие на устройство команды являются командами трех типов команды обмена - Читать, Записать .Уточнить состояние, команды управления - Управление рабочее, Управ ление фиктивное и команды проверки устройства. Причем, команды управ ления и проверки требуют лишь двух этапов обмена: первого и четвёртого Рассмотрим работу устройства по инициативе со стороны основной ЭВМ 1 При обращении к устройству основная ЭВМ 14, вводя последовательность начальной выборки (НВ), на шинах 21 выставляет сигнал ВБР-К (линия 21, и на шинах 22 выставляет адрес устройства в сопровождении идентификато ра АДР-К (линия 214), поступающего, Как и сигнал ВБР-К (линия 21), , по шинам 21 основной ЭВМ 14 на второй вход блока 8 (алгоритм работы блока 8 на фиг. 4). Адрес устройства поступает на первый информационный вход блока 10 сравнения адреса, на второй информационный вход которого поступает собственный адрес устройства, заданный блоком 11 1812 задания адреса. В случае совпадения поступивших адресов блок 10 вырабатывает сигнал Адрес опознан (АДОП), поступающий по шине 65 на вход блока 8. Последний, определив опознание адреса, выставляет сигнал РАБ-А (Работа абонента), сообщающий основной ЭВМ 14 о подключении устройства к каналу ввода-вывода. Сигнал РАБ-А (линия 20,) поступает с второго выхода блока 8 на шины 20 и сбрасывается только при отключении устройства от интерфейса. Затем блок 8 устанавливает сигнал Разрешение адреса (Разр.А, линия 702 поступающий с четвертого выхода блока 8 на управляющий вход блока 6 и разрешающий вьщачу адреса устройства с выхода блока 11 в канал основной ЭВМ 14. Адрес устройства вьщается в сопровождении идентификатора АДР-А (линия 20), поступающего с второго выхода блока 8 на шины 20. Канал основной ЭВМ 14, получив адрес, выставляет на шинах 22 код команды в сопровождении идентификатора УПР-К (линия 21), поступающего по линии 21 на вход блока 8. Далее блок 8 вьфабатывает сигнал занесения в регистр данных и команд (ЗНС РДК, линия 72), поступающий на управляющий вход регистра 9 и заносящий в него код команды с шин 22. С выхода регистра 9 код команды поступает на вход блока 12, на седьмой вход блока 8 и на информационный вход второго буферного регистра 2. В блоке 8 код команды анализируется и затем выполняется ряд операций. Для примера рассмотрим команду Записать (ЗП). Блок 8, определив код команды ЗП, устанавливает сигнал Команда (КОМ) (линия 42) и Строб приема (Строб ПМ) (линия 42j-)j поступающие на пятый вход блока 3, Далее работа блока В и блока 5 происходит параллельно: блок 8 завершает процедуру НВ, блок 3 вырабатывает сигнал прерьшания во вспомогательную ЭВМ 13. Рассмотрим сначала окончание начальной выборки. Блок 8 устанавливает сигнал Разрешение данных (Разр.Д, линия 70), посгупающий на управляющий вход блока 6 и разрешающий вьщачу байта состояния из регистра 7 в основную ЭВМ 14. Кроме 13 , того, блок 8 устанавливает на шинах 20 сигнал УПР-А (линия 265), сообщая о том, что на шинах 19 находится байт состояния устройства. Затем, получив в ответ от основной ЭВМ 14 по шинам,21 сигнал ИНФ-К (линия 21з), блок 8 гасит сигналы УПР-А (линия 20) и РАБ-А (линия 20) на шинах 20 и отключается от канала основной ЭВМ 14. На этом процедура НЕ заканчивается. Теперь рассмотрим работу блока 3, которая осуществляется параллельно с работой блока 8. Сигнал Строб ПМ (линия 42j) в блоке 3 используется для выработки сигнала занесения в буферньш регистр 2, который поступает с второго выхода блока 3 на управляющий вход буферного регистра 2. После занесения кода команды в буферный регистр 2 с его управляющего выхода на второй вход блока 3 поступает сигнал, которьй вырабатывает в блоке 3 сигнал лрерывания, поступающий затем по шине 18 в вспомогательную ЭВМ 13. Устройство использует два уровня прерывания во вспомогательную ЭВМ 13 по команде и по данным. Прерывание по команде (линия 18,) сообщает вспомогательной ЭВМ 13 о-том, что в буферном регистре 2 находится код команды. Прерывание по данным означает (в зависимости от кода полученной команды), что либо в буферном регистре 2 находится бай данных для передачи во вспомогатель ную ЭВМ 13 (при команде Записать) либо буферный регистр 1 пуст и требует следующий байт от вспомогатель ной ЭВМ 13 (в случае команд Читать Уточнить сосФояние). Сигналы соот ветствующих уровней прерывания выра батьшаются блоком 3 по сигналам с управляющих выходов буферных регист ров 1 и 2. Так как через буферный регистр 2 могут передаваться данные и команды то для выработки соответствующего уровня прерывания и используется указанный сигнал Команда. Если из блока 8 поступает сигнал Команда, вырабатывается сигнал прерывания по команде (линия 18). Вспомогательная ЭВМ 13 обрабатывает получен нов прерывание 5 затем считывает код команды из буферного регистра 2 и анализирует его. Для чтения буферно 1814 го регистра 2 вспомогательная ЭВМ 13 выставляет на шинах 17 адрес буферного регистра 2, поступающий на первый вход, блока 3j который вырабатывает сигнал чтения. Сигнал чтения поступает с второго выхода блока 3 на вход буферного регистра 2. Вспомогательная ЭВМ 13, проанализировав код полученной команды, записывает в регистр 5 приказов один из флагов (Старт чтения при комане 3аписать,Старт записи при команде Чтение, Байт состояния инициативный или БСИН при инициат ве со стороны вспомогательной ЭВМ 13. Под флагом понимается указатель, задающий режим работы устройства и обеспечивающий ветвление алгоритма работы (фиг. 4) блока 8. В рассматриваемом случае вспомогательная ЭВМ 13 выставляет на шинах 15 флаг Старт чтения (Старт ЧТ), а на шинах 17 адрес регистра 5 и сигнал Вьщача. По этим сигналам блок 13 вырабатывает сигнал занесения, поступающий по шине 49 на вход регистра 5 и заносящий в него флаг с шин 15. С выхода регистра 5 флаг Старт ЧТ поступает на восьмой вход блока 8, сообщая ему о том, что вспомогательная ЭВМ 13 готова к приему байта информации, и устанавливает режим вывода информации из устройства во вспомогательную ЭВМ 13. Далее блок 8 выставляет на шинах 20 сигнал ТРБ-А (линия ZOg), требуя от основной ЭВМ 14 следующий байт информации. В ответ основная ЭВМ 14 выставляет на шинах 21 сигнал ВБР-К (линия 21) без адреса устройства, осуществляя тем самым выборку устройства, потребовавшего обслуживания, f Блок 8, определив присутствие сигнала ВБР-К, проверяет, требуется ли устройству обслуживание (по наличию одного из флагов Старт ЧТ, Старт ЗП, БСИН), и если обслуживание не требуется (нет ни одного из флагов), то выставляет на шинах 20 сигнал ВБР-А (линия 20). Если же обслуживание требуется (в рассмотренном случае стоит флаг Старт ЧТ), т.е. сигнал ТРБ-А бьш выставлен устройством, то блок 8 гасит сигнал ТРБ-А на шинах 20. Затем блок 8 на шины 20 выдает сигнал РАБ-А (линия 20;j), на управляющий вход блока 6 - сигнал Разрешение адреса (Разр.А, линия 70j ) , а на шины 20идентификатор АДР-А (линия 20), сообщающий о том, что на шинах 19 находится адрес устройства. Канал основной ЭВМ 14, получив адрес устройства, выставляет на шинах 21 сигнал УПР-К (линия-21.; );, разрешая тем самым устройству продолжить операцию. После этого блок 8 снимает сигнал АДР-А (линия 20 и гасит сигнал Разрешение адреса (Разр.А), блокируя выдачу блоком адреса устройства в канал основной ЭВМ 14. Далее блок 8 устанавливает на втором выходе сигнал ИНФ-А (линия 20х), поступающий по шинам 20 приема в канал основной ЭВМ 14 и сообщающий ей, что устройство хоч получить байт данных. В ответ основ ная ЭВМ 14 выставляет на шинах 22 выдачи байт данных, а на шинах 21 идентификатор ИНФ-К (линия 21), сообщающий блоку Б, что байт данных находится на шинах 22, С пятого выхода блока 8 на управляющий вкод регистра 9 поступает сигнал, занося щий байт данных в регистр 9, .Блок 8 вырабатывает сигнал Строб приема (Строб .ПМ,линия 42 ) ,который доступ ет на пятый вход блока 3. Далее, как и в процедуре НВ, происход1 т параллельная работа блоков 3 и 8 Блок 3 по сигналу Строб ПИ выдает на управляющий вход буферного регистра 2 сигнал, заносящий байт данных с выхода регистра 9 в буферный регистр 2 (линия 47). В резуль тате на управляющем выходе буферного регистра 2 появляется сигнал (линии 43 и 68), поступающий на второй вход блока 3 для выработки прерывания по данным во вспомогательную ЭВМ 13, Сигнал прерывания по данным (линия 18) свидетельству ет о том, что в буферном регистре 2 находится байт данных для передачи во вспомогательную ЭВМ 13, Чтение байта данных из буферного регистра осуществляется так же как и чтение байта команды в предшествующей процедуре НВ, Блок 8. параллельно с работой бло ка 3 отрабатывает алгоритм работы с каналом основной ЭВМ при передаче данных, т.е, блок В снимает с шин 20 сигналы ИНФ-А (линия 20) (сообщая, что байт устройством принят) и РАБ-А (линия 20,) (сообщая об отключении устройства от интерфейса), После считывания вспомогательной ЭВМ 13 байта информации на управляющем выходе буферного регистра 2 пропадает сигнал признака заполнения, и блок 8 зафиксирует, что байт информации считан вспомогательной ЭВМ 13 и устройство готово к приему следующего байта. Тогда блок 8 опять выставляет сигнал ТРБ-А (линия 20), и весь цикл передачи снова повторяется Обмен может, завершиться либо по инициативе основной ЭВМ 14, либо по инициативе-вспомогательной ЭВМ 13.. В первом случае,основная ЭВМ 14, завершая передачу, при обмене управляющими сигналами по шинам 20 и 21 в ответ на сигнал ИНФ-А (линия 20х) (т.е. запрос .абонентом следующего байта) отвечает сигналом УПР-К (линия 21j) (при передаче данных ответ сигналом ИНФ-К), что для устройства означает завершение операции обмена. Тогда блок 8 снимает с шин 20 сигналы ИНФ-А (линия 20) и РАБ-А (линия 20j), устанавливает указатель Конец обмена (КО, линия 73;|), поступающий на информационный вход регистра 4, и сигнал Строб регистра словосостояния (линия 42), поступающий на пятый вход блока 3. В блоке 3 по сигналу Строб регистра словосостояния вы забатывается сигнал занесения в регистр 4 (линия 50). После занесения в регистр 4 данных на его управляющем выходе появляется сигнал признака заполнения (шина 44), поступающий на четвертый вход блока 3, где он исполь. зуется для выработки прерывания по команде. Если сигнал признака заполнения от буферного регистра 2 может вызывать прерывание как по команде, так и по данньм, то признак заполнения регистра 4 вырабатьгоает прерывание только по команде. Вспомогательная ВМ 13, получив прерывание по комане (линия 18|), определяет что это прерывание от регистра 4, так как прерывание по команде от буферного егистра 2 придти не может в си.пу занятости устройства текущей операцией. Вспомогательная ЭВМ 13, обработав прерывание, читает регистр 4 (аналогично чтению буферного регнстpa 2). Сигнал чтения регистра 4 (линия SOj) поступает с четвертого выхода блока 3, и в результате пропадает сигнал на управляющем выходе регистра 4, сообщая тем самым о том, что информация считана.

Вспомогательная ЭВМ 13, определив указатель КО в байте, считанном из регистра 4, гасит флаг Старт ЧТ в регистре 4 (гашение осуществляется записью в регистр 5 нулевых флагов). Затем формирует конечный байт состояния устройства и заносит его в буферный регистр 1. Для этого байт состояния выставляется на шинах 15, а на шинах 17 устанавливается адрес буферного регистра 1 и сигнал Вьщача, поступающие на первый вход блока 3. По адресу регистра и сигналу Вьщача в блоке 3 вырабатьшается сигнал занесения в буферный регистр 1 (линия 48,), поступающий затем на управляющий вход буферного регистра 1. После занесения байта состояния в буферный регистр 1 на его управляющем выходе появляется сигнал признака заполнения (линии 45 и 67), поступаюпщй на в1соды блоков 3 и В. Блок 8, определив наличие флага БСИН на восьмом входе и признака заполнения буферного регистра 1 на четвертом входе, устанавливает на шинах 20 сигнал ТРЕ-А (линия 20).

В ответ основная ЭВМ 14 начинает последовательность выборки устройства требующего обслуживания, т.е. устанавливает сигнал ВВР-К (линия 21f) устройство отвечает сигналом РАБ-А (линия 21). После этого блок 8 устанавливает сигнал занесения в регистр 7 (линия 71), переписывающий байтсостояния из буферного регистра 1, и сигнал Подтверждение записи (Подтв.ЗП) (линия 425). В блоке :. сигнал Подтв.ЗП вырабатывает сигна чтения буферного регистра 1. В результате этого на управляющем выходе буферного регистра 1. пропадает сигнал признака заполнения. Это будет зафиксировано блоком 3, после чего он вырабатывает сигнал прерывания по данным во вспомогательную ЭВМ 13. Для последнего это будет сообщением, что байт состояния принят устройством сопряжения и буфер- ный регистр 1 свободен.

г

Далее вспомогательная ЭВМ 13 сбрасывает регистр 5 (гасит флаг БСИН)

и записывает в буферный регистр 1 фиктивньш байт. Последнее необходимо для того, чтобы сигнал признака заполнения буферного регистра 1 не вьфабатывал в блоке 3 сигнала прерывания по данным, т.е. это является запрещением прерывания от буферного регистра 1. Блок 8 после выдачи сигНеша Подтв.ЗП вьщает сигнал Разрешение данных (Разр.Д, линия 70), поступающий на управляющий вход блока 6 и разрешающий вьщачу конечного байта состояния устройства на шины 19 и сигнал УПР-А (линия 205). Канал основной ЭВМ 14, получив сигнал УПР-А, отвечает сигналом ИНФ-К (линия 21j) на шинах 21, сообщая тем самым, что конечный байт состояния принят. После блок 8 гасит сигналы УПР-А и РАБ-А и операция считается законченной. В случае завершения операции по инициативе вспомогательной ЭВМ 13, последняя гасит Старт ЧТ в регистре 5, записывает в буферный регистр 1 байт состояния, а в регистр 5 - флаг БСИН. Дальнейшая работа устройства происходит так же как и в случае окончания операции по инициативе основной ЭВМ 14. Блок 3 управления обменом (фиг.2) работает следукнцим образом.

На вход элемента ИЛИ-НЕ 23 по линиям 17 и 42 поступают соответственно сигналы Сброс ММ от вспомогательной ЭВМ 13 и сигнал Сброс от блока 8. Таким образом, формируется сигнал Общий сброс, т.е. при появлении на любом из входов элемента ИЛИ-НЕ 23 сигнала логической единицы на ее выходе вырабатывается сигнал логического нуля, поступаннций по лишний 46 в блок 8 вход сброс триггера 28. Этот сигнал сбрасывает также все регистры устройства. При записи байта в буферный регистр 2 (как отмечалось при рассмотрении работы устройства в целом) блок 8 выдает по линии 42 сигнал Строб приема, поступающий на вход элемента И-НЕ 30, на другой вход которого поступают импульсы тактовой частоты от одновибратора 27, работающего от задающей частоты, поступающей по линии от вспомогательной ЭВМ 13. В результате на выходе элемента И-НЕ 30 вырабатывается отрицательный импульс, который затем инвертируется элементом НЕ 36, и положительный импульс занесения в буферный регистр 2 по линии 47 поступает на управляющий вход буферного регистра 2,

После занесения байта информации в буферный регистр 2 на управляющем выходе последнего появляется сигнал признака заполнения, поступающего по шине 43 на входы элементов И-НЕ 32 и 33. Если байт, записанньш в буферный регистр 2,,является, кроме того, командой, то блок 8 устанавливает сигнал Команда, поступающий по линии 42 на вход элемента И-НЕ 29. При поступлении на другой вход элеента И-НЕ 29 синхроимпульса от одновибратора 27-на выходе его образуется отрицательный импульс, устанавивающий в состояние 1 прямой выод триггера 28 В результате открывается элемент И-НЕ 32 (на обоих входах сигнал логической единицы), и сигнал логического нуля поступает на один из входов элемента И-НЕ 34, вызывая на его выходе сигнал прерывания по команде, поступающей по линии 18, во вспомогательную ЭВМ 13. На другой вход элемента 34 поступает сигнал признака заполнения от регистра 4 словосостояния, вызывая аналогичное прерьшание, если в регистр 4 была записана информация. Если же триггер 28 сброшен, то уже логический ноль с выхода элемента И-НЕ 33 вызовет сигнал прерывация по данньм на выходе элемента И-НЕ 35, который по линии 182 поступит во вспомогательную ЭВМ 13.

Таким образом, триггер 28 коммутирует сигнал признака заполнения от буферного регистра 2 на уровень прерывания по команде или по данным в зависимости от содержимого буферного регистра 2. Сигнал признака заполнения от буферного регистра 1 ьырабатывает прерывание только по данным. Этот сигнал поступает по линии 45 на вход элемента И 31 и далее на вход элемента И-НЕ 35. Таким образом, если буферный регистр 1 пуст, то на шине 45 находится сигнал логической единицы, который инвертируется элементом НЕ 31, и-на линии 182 появляется сигнал прерывания по данным. Триггер 28 необходимо сбрасывать после считывания команды из буферного регистра 2, т.е. заранее подготавливается коммутация следующего сигнала признака заполнения от буферного регистра 2 на уровень данных. Считывание буферного регистра 2 и 5 сброс триггера 28 организуются элементами ИЛИ-НЕ 24 и И-НЕ 25. При считывании буферного регистра 2 вспомогательная ЭВМ 13 выставляет на шинах адрес регистра 2 ;

в сопровождении сигнала Строб адреса по линии 17jQ , разрешающего работу дешифратора 26 (ПЗУ). На первом выходе дешифратора 26 появляется сигнал логического нуля, поступающий

5 на один из входов схемы элемента

ИЛИ-НЕ 24. Вследствие того, что первый выход дешифратора 26 используется еще и для выработки сигнала занесения в буферный, регистр 1, для формирования сигнала чтения буферного .регистра 2 используются два младших разряда адреса, поступающие соответственно на входы элементов ИЛИ-НЕ 24 и И-НЕ 25. Тогда при обращении к

5 буферному регистру 2 (на линиях 17217 находится адрес) на входе элемента ЙЛИ-НЕ 24 будет сигнал логического нуля и соответственно на выходе сигнал логической единицы, поступающий на вход элемента И-НЕ 25. На втором входе элемента И-НЕ 25 присутствует сигнал логической единицы от младшего разряда адреса, а в результате на выходе сформируется отрицательный импульс, задний фронт которого сбросит триггер 28, а по линии 47 поступит на вход чтения буферного регистра 2. Если же на шинах 17 будет адрес буферного регистра 1, то младший разряд адреса на линии 17 не разрешит выработку импульса для чтения буферного регистра 2. В случае же записи.информации в буферный регистр 1 вспомогательная ЭВМ 13 (кроме адреса на линиях ) выставляет на линии П сигнал Вьздача, поступающий уровнем логического нуля на вход элемента ШШ-НЕ 37, с выхода которого по линии 48 поступает сигнал занесения в буферный регистр 1,

Аналогичным образом вырабатывается сигнал занесения-в регистр 5 приказов, поступающий по шине 49 на управляющий вход регистра 5 (для образования этого сигнала используется второй выход дешифратора 26). Третий выход дешифратора 26 используется

для выработки сигнала чтения рёгист-, ра 4 словосостояния, При нахождении на входных шинах дешифратора 26 ад-, раса регистра 4 на его третьем выходе появляется сигнал логической , единицы, поступающий на второй вход элемента И 39, на другой вход которого поступают синхроимпульсы с прямого выхода одновибратора 27. В результате с выхода элемента И 39 снимается положительный импульс, поступающий по линии 50| на вход чтения регистра 4 словосостояния. Элемент И 40 используется для выработки сигнала занесения в регистр 4 словосостояния. На один из входов элемента И 40 по линий 424 блока 8 поступает сигнал Строб регистра словосостояния, на другой вход поступает имйульс с прямого выхода одновибратора 27 и в результате с . выхода элементаИ 40 снимается сигнал занесения, поступающий по линии 50 на управлякиций вход регистра 4. И, наконец, на вход элемента И 41 по линии 42г поступает сигнал Подтверяздение записи из блока 8, аналогичным образом вырабатьшается сигнал, поступающий по линии 48 на вход чтения буферного регистра 1. Кроме того, по линиям 46 и 46., вблок 8 поступают два сигнала синхронизации.

Блок 8 связи с каналом ввода-вывода (фиг. 3) работает следующим обpaSoM.

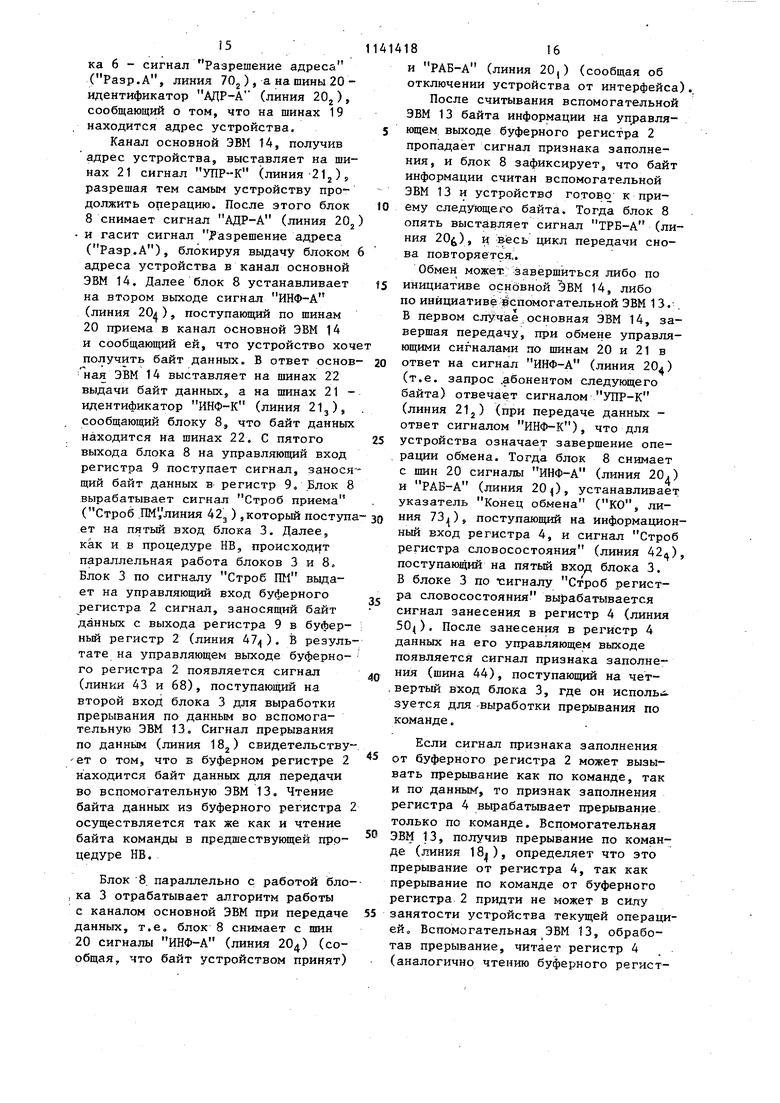

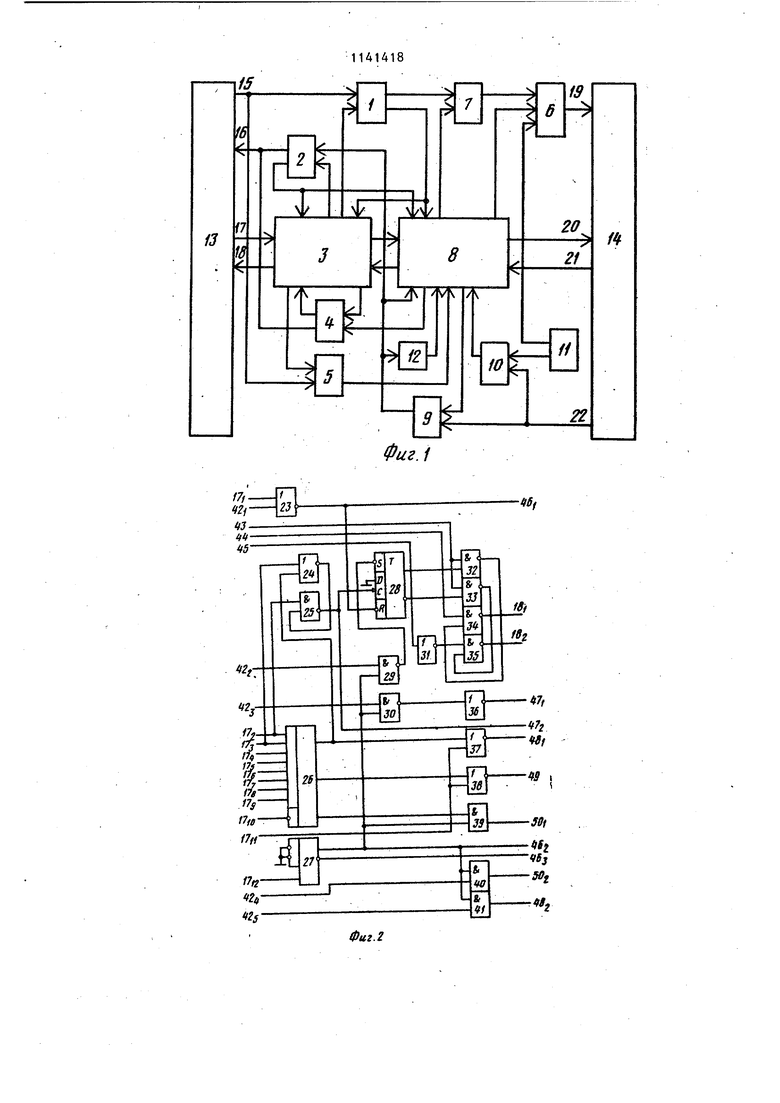

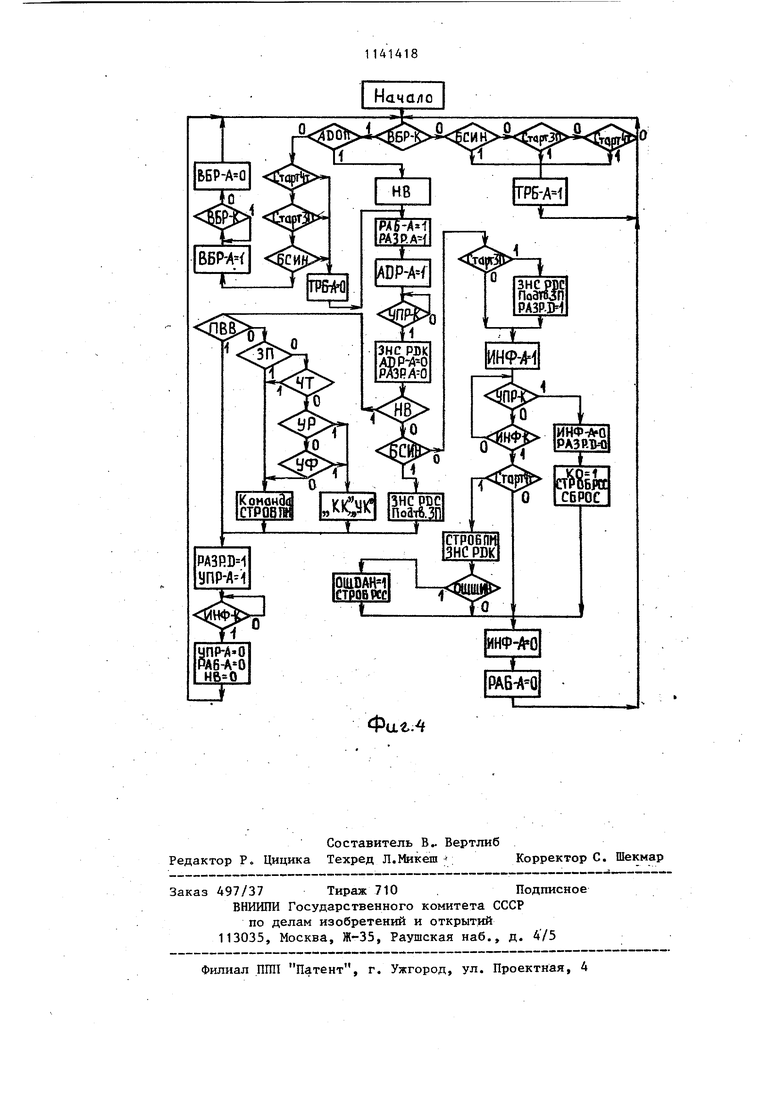

Алгоритм работы блока 8 показан на фиг. 4. Элементы И 51, 61, 62 и 63 и элементы-ИЛИ-НЕ 52, 53 и 54 осуществляют совместно с мультиплексором 55 выбор следующего адреса микрокоманды через регистр 56.

В каждом такте работы (синхрони.зация осуществляется сигналом, поступающим из блока 3 по линии 463) по адресу, содержащемуся в регистре 56, из памяти 58 выбирается микрокоманда, содержащая следукмцие поля: поле управления (разря;с ;ы MxQ-Mxj), поле сигналов абонента: . (сигналы линий ), поле сигналов управления (сигналы линий 2t.21ц.), указатели регистра словосостояния (сигналы линий ), флаг НВ (флаг начальной выборки). Далее разряды с первого выходз а памяти 58 поступают непосредственно на вход регистра 56, а разряды второго выхода памяти 58

поступают на вход управления мультиплексора 55, подключая нужный вход мультиплексора 55 к входу регистра 56. Сигнал с выхода мультиплексора 55 вместе с разрядами образует адрес следующей микрокоманды.

Таким образом, в зависимости от состояния выхода мультиплексора 55 может быть осуществлен переход в ту или иную ячейку памяти 58, что обеспечивает ветвление алгоритма (фиг. 4). Содержимое микрооперации заносится соответственно в регистр 59 сигналов абонента (обеспечивает обмен сигналами с основной ЭВМ 14), в регистр 60 сигналов управления (обеспечивает управление остальными блоками устройства) и, если необходимо, через элементы И 61, 62 и 63 выдаются на. информационный вход ре-гистра 4 словосостояния указатели Конец обмена (КО), Ошибка в данных (Ош.шин), Сбой в устройстве . Занесение во все регистры осуществляется синхросигналом, поступающим по линии 46, , а сброс сигналом Общий сброс , поступающим по линии 46. Триггер 57 ветвления обеспечивает установку флага НВ, который необходим для ветвления алгоритма (фиг. 4). Чтобы лучше понять механизм работы блока 8, рассмотрим для примера несколько коротких ветвей алгоритма, изображенных на фиг. 4. .

Исходным режимом блока 8 является режим ожидания, когда последовательно проверяется на входе мультиплексора 55 наличие одного из флагов БСИН, Старт ЗП, Старт ЧТ. Это осуществляется следукщим образо Из памяти 58 считывается микрокоманда, в которой разряды поля управления выбйрают вход мультиплексора 55 на который поступает флаг БСИН. Если флаг отсутствует (БСИН-0), т в следующей микрокоманде аналогично проверяется флаг ,Старт ЗП и, т.д. Если флаг БСИН присутствует на входе, то в следующей мийрокоманде устанавливается сигнал ТРБ-А, который затем заносится и регистр 59 сиг;налов управления и по линии 20 поступает в канал основной ЭВМ 14. Рассмотрим случай распрост,ранения сигнала ВБР-К в случае, .когда устройству обслуживание не требуется В этом случае после появления на входе мультиплексора 55 сигнала ВБР-К содержимоерегистра 56 модифицируется, и выбирается следующая микрокоманда, в которой наличие сигнала АДОП (Адрес опознан) проверяется. При этом выбирается тот вход мультиплексора 55, на который поступает сигнал с выхода элемента , И 51. На один вход элемента И 51 по линии 21 поступает сигнал АДР-К из канала основной ЭВМ14, а на другой вход - по шине 65 поступает сигнал АДОП. из блока .10 сравнения адреса. Если адрес не опознан устройством или нет сигнала АДР-К, то на выходе элемента И 51 будет сигнал логического нуля и следующей микрокомандой проверяется флаг ,Старт ЧТ, затем Старт ЗП, БСИН Если ни одного из флагов нет на входе мультиплексора 55, то это означает, что устройству обслуживание не. требуется и оно должно распростра ВБР-Книть сигнал BtiF-K дальше по интерфейсу. Это осуществляется установкой в регистре 58 сигналов абонента сигнала ВБР-А, поступающего по линии 20 в основную ЭВМ 14. Затем происходит обращение к микрокоманде, выбирающей вход мультиплексора 55, на которой по линии 21 постуйает сиг,нал ВБР-К. Когда основная ЭВМ 14 снимает с линии 21 сигнал ВБР-К, то следующая микрокоманда, выбран- . ная из памяти 58 микрокоманд, погасит сигнал ВБР-А в регистре 59 сиг налов управления. Затем осуществляет ся переход на начало, и- блок 8 работает в режиме ожидания до тех пор, пока не будет инициативы с чьей-либо стороны, т.е. пока не появится сигнал ВБР-К или флаг БСИН. Отметим, что все флаги поступают на вход мультиплексора 55 не непосредственно .с выхода регистра 5 приказов, а с выхода элемента ИЛИ-НЕ 52, 53 и 54. На входы элементов ИЛИ-НЕ 52 53 и 54 соответственно полиниям с выхода рё истра 5 поступают (уровНем логического нуля) сигналы БСИН Старт ЗП, Старт ЧТ. На другие входы элементов ИЛИ-НЕ 52 и 53 поступает по шине 67 сигнал признака заполнения от буферного регистра 1, а на другой вход элемента ИЛИ-НЕ 54 по шине 68 поступает сигнал признака заполнения от буферного регист- . ра 2« Это делается для того, чтобы флаги воспринимались только тогда, когда в регистрах находится информация . Например, вспомогательная ЭВМ 13 установила в регистре 5 флаг Старт ЧТ, а буферньй регистр 2 пуст. Тогда на выходе сигнала признака заполнения буферного регистра 2 присутствует сигнал уровня логического нуля, поступающий с управляющего выхода буферного регистра 2 по шине 68 на вход элемента ИЛИ-НЕ 54. В результате этого на выходе элемента ИЛИ-НЕ 54 появляется сигнал логической единицы, называемый Старт чтения (Старт ЧТ). Таким образом, флаг Старт чтения представляет собой сигнал Старт чтения регистра 5 приказов, смешанньй с сигналом признака заполнения буферного регистра 2. Это же относится и к флагам Старт записи и БСИН с той лишь разницей, что сигналы Старт записи, БСИН регистра 5 приказов смешиваются на элементах ИЖ-НЕ 53 и 52 с сигналом признака заполнения буферного , регистра 1. Элементы И 61-63 позволяют заносить в регистр 4 словосостояния ука затели,- характеризующие качество и особенности проведенного обмейа, а также делающие обе ЭВМ равноправными в процедуре окончания обмена (указатели Конец обмена, Ошибка в данных, Сбой в устройстве). Таким образом, устройство обеспечивает возможность автономного формирования различных указателей и сигналов в соответствии с процедурами интерфейсов сопрягаемых ЭВМ, что и позволяет сократить объем работы ЭВМ при обмене и повысить пропускную способность устройства.

Фиг.1

КононЭЛ I

стррвти

РАБ

Фаг.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения эвм | 1975 |

|

SU581467A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-23—Публикация

1983-10-26—Подача