Канал ЗВМ 3-У

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения периферийных устройств с ЭВМ | 1987 |

|

SU1425699A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1983 |

|

SU1160426A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515168A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах управления, сбора и обработки информации. Целью изобретения является распшрение номенклатуры сопрягаемых устройств. Устройство содержит два блока 1 и 4 приемопередатчи- дешифратор 3 управляющих сигна- дешифратор 3 адреса и шифратор ил., ков, лов, 5. 7 1 т абл.

..

М

а

со

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах управл(ния, сбора и обработки информации.

Цель изобретения - расширение номенклатуры сопрягаемых устройств.

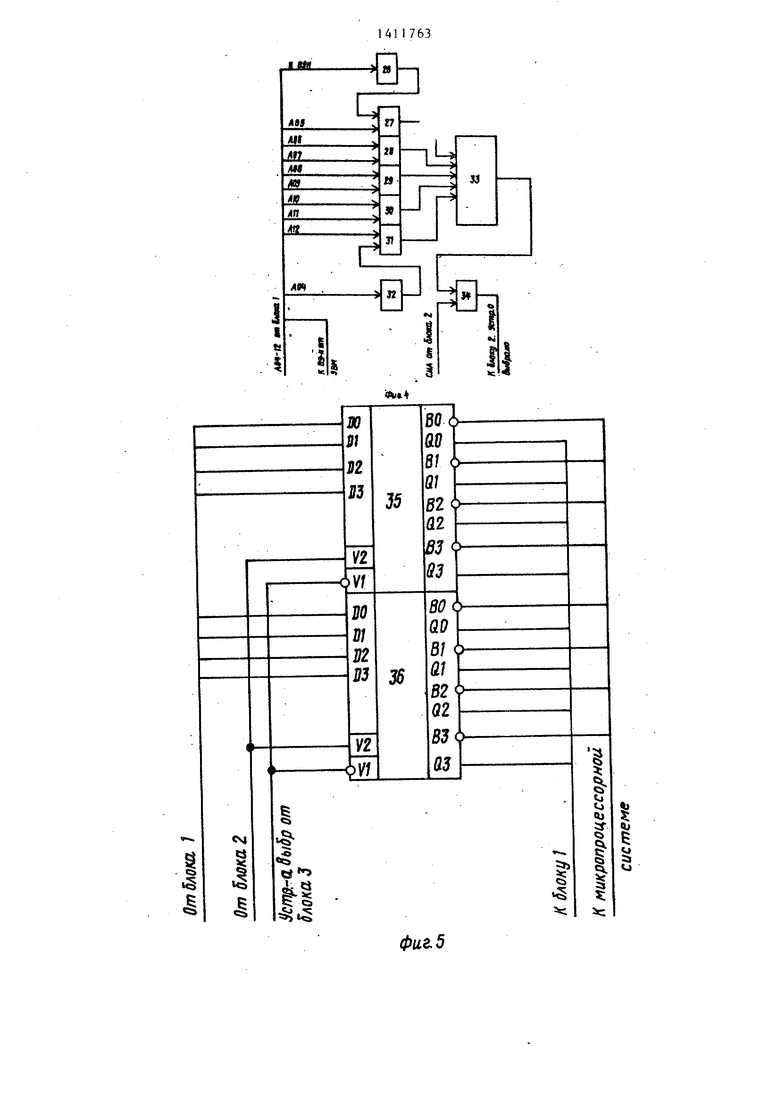

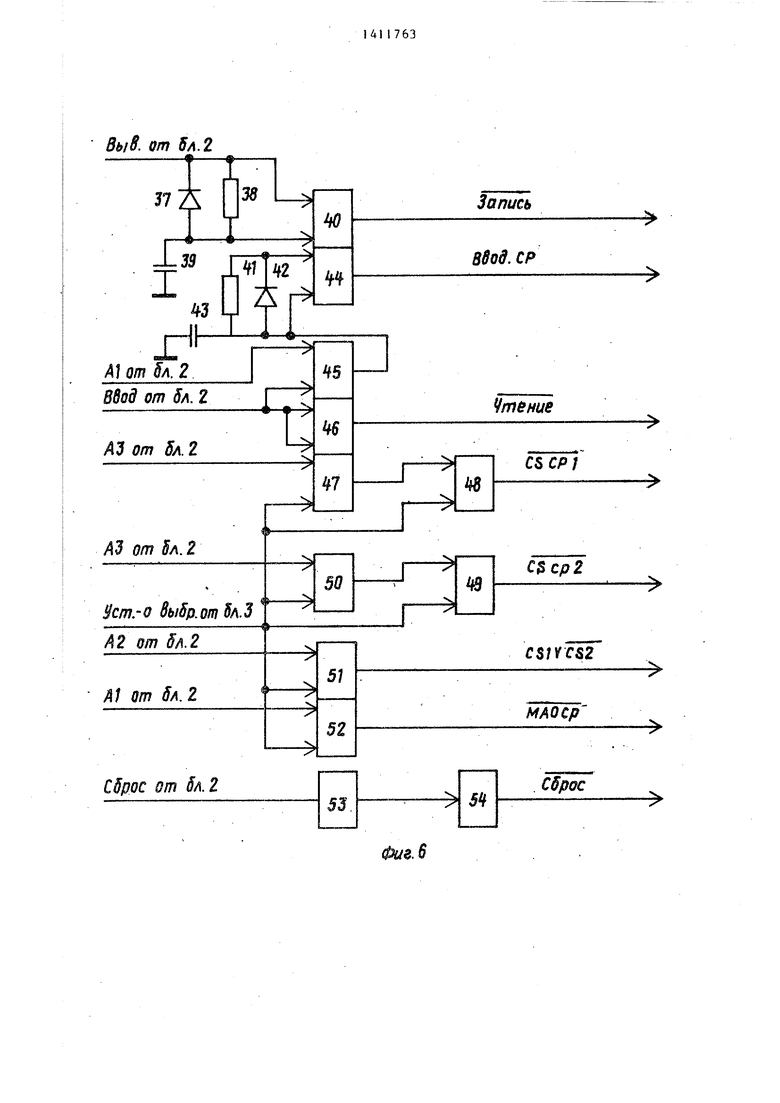

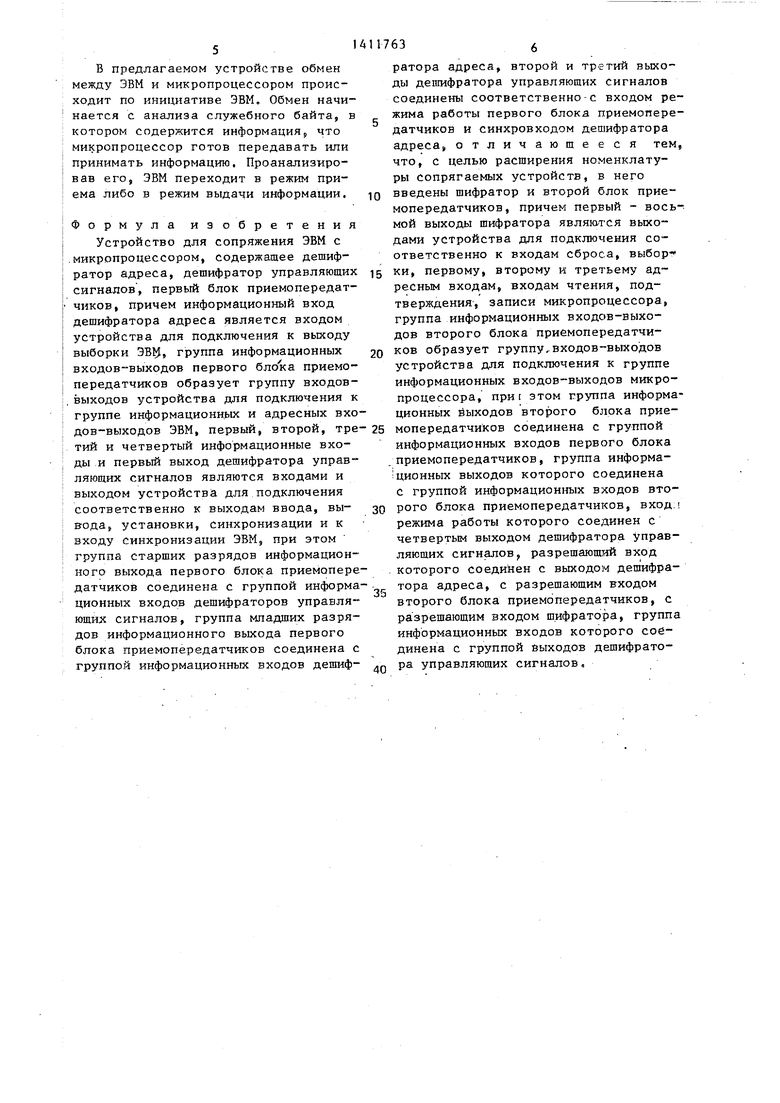

На фиг, 1 приведена структурная схема устройства для сопряжения ЭВМ с микропроцессором; на фиг. 2 схе- ма первого блока приемопередатчиков; на фиг. 3 схема дешифратора управляющих сигналов; на фиг, 4 - схема дешифратора адреса; на фиг. 5 - схема второго блока приемопередатчиков; на фиг. 6 - схема шифратора; на фиг. 7 - временные диаграммы работы устройства в режимах ввода и вывода.

Устройство содержит первый блок 1 приемопередатчиков, дешифратор 2 управляющих сигналов, дешифратор 3 адреса, второй блок 4 приемопередатчиков и шифратор 5. .

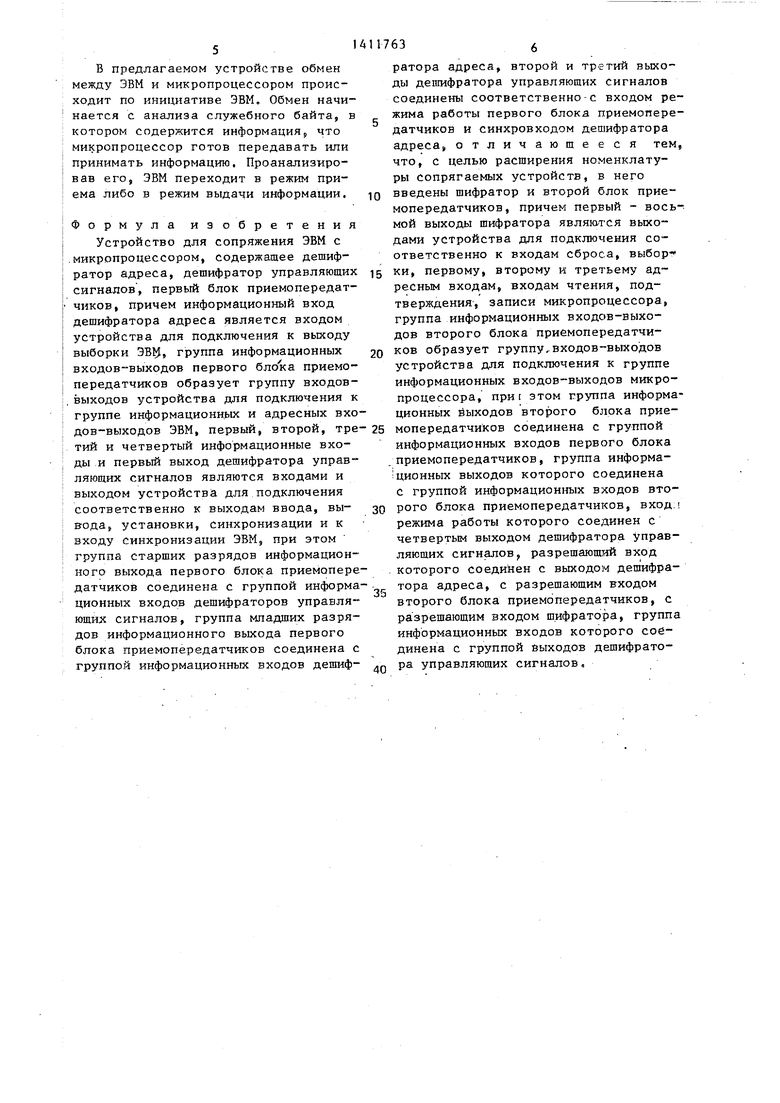

Первый блок 1 приемопередатчиков (фиг. 2) предназначен для приема или передачи информации в канал ЭВМ и состоит из четырех многоканальных приемопередатчиков 6-9. Эти приемопередатчики находятся в режиме приема информации от ЭВМ (режим Вы- вод). В режим выдачи информации в ЭВМ из микропроцессора приемопередатчики переводятся сигналом ПРД,

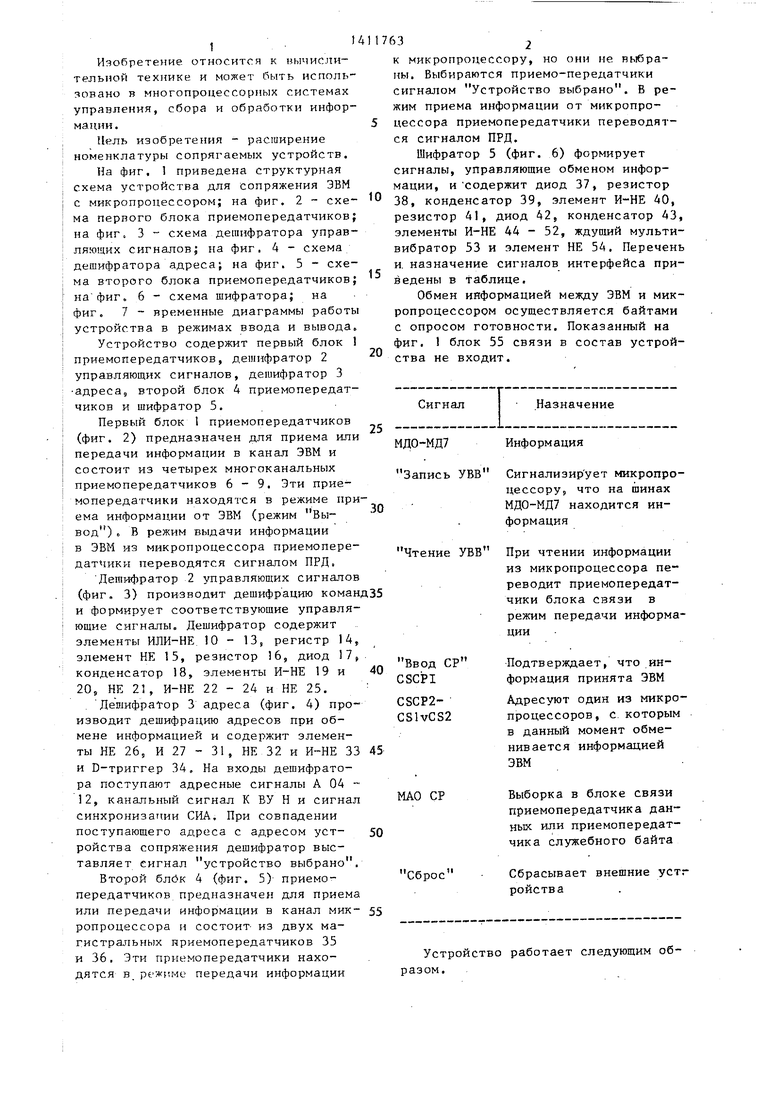

Детифратор 2 управляющих сигналов (фиг 3) производит дешифрацию коман и формирует соответствующие управляющие сигналы. Дешифратор содержит элементы ИЛИ-НЕ 10 - 13, регистр 14, элемент НЕ 15, резистор 6, диод 17, конденсатор 18, элементы И-НЕ 19 и 20, НЕ 21, И-НЕ 22 - 24 и НЕ 25.

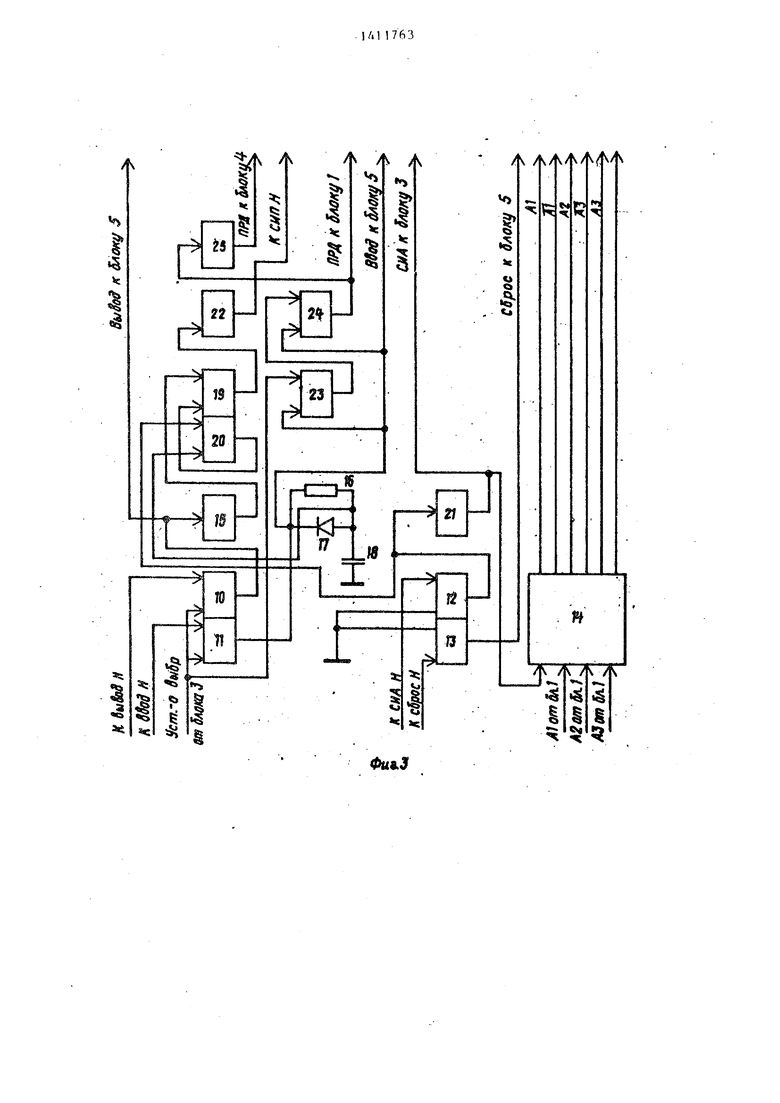

Дешифратор 3 адреса (фиг. 4) производит дешифрацию адресов при обмене информацией и содержит элементы НЕ 26, И 27 - 31, НЕ 32 и И-НЕ 33 и D-триггер 34, На входы дешифратора поступают адресные сигналы А 04 12, канальный сигнал К ВУ Н и сигнал синхронизации СИЛ. При совпадении поступающего адреса с адресом уст- ройства сопряжения дешифратор выставляет сигнал устройство выбрано.

Второй блбк 4 (фиг. 5)- приемопередатчиков предназначен для приема или передачи информации в канал мик- ропроцессора и состоит- из двух магистральных приемопередатчиков 35 и 36, Эти приемопередатчики находятся в режиме передачи информации

к микропроцессору, но они не выбраны. Выбираются приемо-передатчики сигналом Устройство выбрано. В режим приема информации от микропроцессора приемопередатчики переводятся сигналом ПРД.

Шифратор 5 (фиг. 6) формирует сигналы, управляющие обменом информации, и содержит диод 37, резистор 38, конденсатор 39, элемент И-НЕ 40, резистор 41, диод 42, конденсатор 43, элементы И-НЕ 44 - 52, ждупшй мультивибратор 53 и элемент НЕ 54. Перечень и. назначение сигналов интерфейса приведены в таблице.

Обмен информацией между ЭВМ и микропроцессором осуществляется байтами с опросом готовности. Показанный на фиг. 1 блок 55 связи в состав устройства не входит.

Сигнал

.Назначение

УВВ

УВВ

Информация

Сигнализир ует микропроцессору, что на шинах МДО-МД7 находится информация

При чтении информации из микропроцессора переводит приемопередатчики блока связи в режим передачи информации

Подтверждает, что информация принята ЭВМ

Адресуют один из микропроцессоров, с которым в данный момент обменивается информацией ЭВМ

Выборка в блоке связи приемопередатчика данных или приемопередатчика служебного байта

Сброс

Сбрасывает ройства

внешние устг

Устройство работает следующим образом.

3I

Устройство обеспечивает работу

в режимах Ввод и Вьгоод.

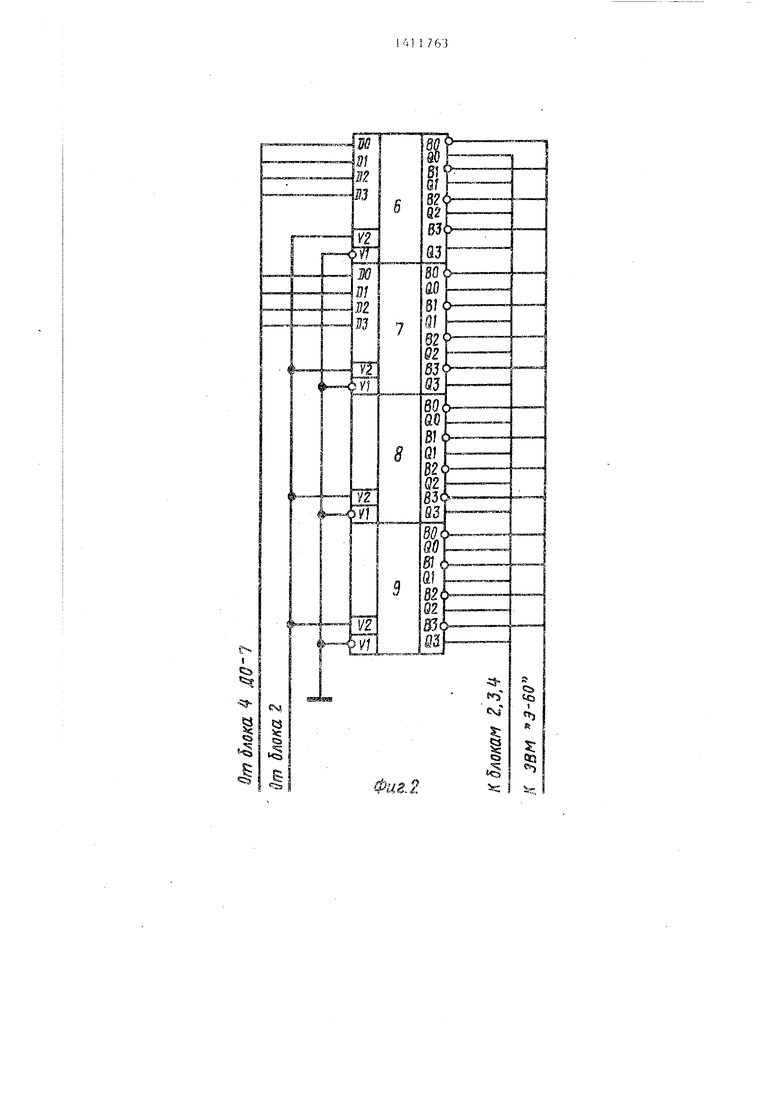

В режиме Ввод (временная диаграмма, фиг. 7) информация передается из микропроцессора в ЭВМ.

Порядок вьшолнения операций следующий. ЭВМ в адресной части передает п6 линиям К ДА (00 - 15) Н в блок I (фиг. 1) приемопередатчиков адрес устройства сопряжения а также сигнал К ВУ Н в дешифратор 3 адреса Дешифратор 3 адреса дешифрирует принятую информацию (А04 - 12) и вырабатывает сигнал Устройство выбрано, через 150нс после выдачи адреса вырабатывается сигнал К СИЛ Н, по переднему фронту которого сигнал Устройство выбрано запоминается в дешифраторе 3 адреса на время действия сигнала К СИЛ Н, а в дешифраторе 2 управляющих сигналов запоминаются значения сигналов А01 - 03. После этого ЭВМ снимает информацию с линий К ДА (00 - 15)-Н, очищает линию К ВУ Н и выставляет в дешифратор 2 управляющих сигналов сигнал к ввод Н, сигнализируя о том, что ЭВМ готова принять информацию от .устройства для сопряжения.

Дешифратор 2 управляющих сигналов, приняв сигналы К СИА Н, К-ввод Н, Устройство выбрано, формирует сигналы Ввод, А01 - 03 и ПРД, который переводит блок 1 приемопередатчиков в режим передачи данных к ЭВМ, а блок 4 приемопередатчиков - в режим приема информации от микропроцессора. Работа этого блока разрешается сигналом Устройство выбрано. По сигналам Ввод и А01 - 03 шифратор 5 выставляет сигналы адресации CSCPI, CSCP2, CSI CS2, МАО СР и сигнал разрешения чтения Чтение УВВ.

При наличии сигналов адресации и .Чтение троисходит чтение информации от микропроцессора. Эта информация поступает :через блок 4 приемопередатчиков по шинам ДО - 7 в блок 1 приемопередатчиков, который выставляет эту информацию в канал ЭВМ. Одновременно с задержкой относительно сигнала К ввод Н дешифратор 2 управляющих сигналов формирует сигнал К СИП Н, который извещает ЭВМ, что информация выставлена в канал.

Одновременно с задержкой относительно сигнала К ввод Н шифратор 5

0

5

0

5

0

5

0

5

7634

формирует сигнал Ввод СР, извещающий микропроцессор, что информация принята ЭВМ. ЭВМ принимает сигнал К СИП Н, принимает данные с канала и снимает сигнал К ввод. Дешифратор 2 управляющих сигналов снимает сигнал К СИП Н, завершая передачу данных, ЭВМ по заднему фронту К СИП Н снимает сигнал К СИА Н, завершая канальный цикл Ввод.

В режиме Вывод (временные диаграммы, фиг. 7) информация передается из ЭВМ в микропроцессор.

ЭВМ выставляет на линии К ДА (00 - 15) Н адрес устройства сопряжения и сигнал К ВУ Н. Дешифратор 3 (фиг. 1) адреса дешифрирует информацию и вырабатывает сигнал Устройство выбрано. Через 150 не после выдачи адреса ЭВМ вырабатывает сигнал К СИА Н, по переднему фронту которого запоминаются значения сигналов АОI - 03 и Устройство выбрано, который разрешает работу дешифратора 2 управляющих сигналов и блока 4. приемопередатчиков данных.

ЭВМ снимает адрес, очищает линию К ВУ Н, после чего помещает данные . на линии К ДА (00 - 07) и через 100 НС выдает сигнал К вьшод. Дешифратор 2 управляющих сигналов, приняв сигналы К СМ Н, К вьгоод, Устройство выбрано, формирует сигнааы Вывод, А01 - 03 и ПРД.. Сигнал ПРД переводит блок 1 приемопередатчиков в режим приема данных из ЭВМ, а блок 4 приемопередатчиков - в режим передачи данных в микропроцессор. По сигналам Вьшод и АО - 3 шифратор 5 выставляет сигналы адресации С CPI, С СР2, С 1 С 2, МАО СР и сигнал Запись УВВ, который, извещает блок 55 связи, что на шинах МДО - 7 находит-, ся информация.

При наличии сигналов адресации и Запись УВВ происходит запись информации в микропроцессор. Дешифратор 2 управляющих сигналов посьшает в ЭВМ сигнал К СИП Н, означающий, что данные приняты устройством для сопряжения, ЭВМ, получив сигнал К СИП Н, очищает через 150 не линию к вывод, а через 250 не после получения сигнала К СИП Н ЭВМ снимает данные с линий К ДА (00 - 07) Н. Устройство для сопряжения снимает сигнал К СИП Н, а ЭВМ снимает сигнал К СИА Н, завершая тем самым цикл вывода.

В предлагаемом устройстве обмен между ЭВМ и микропроцессором происходит по инициативе ЭВМ. Обмен начи- нается с анализа служебного байта, в ; котором содержится информация что мик;ропроцессор готов передавать или принимать информацию. Проанализиро- I вав его, ЭВМ переходит в режим при- i ема либо в режим выдачи информации.

Формула изобретения

Устройство для сопряжения ЭВМ с .микропроцессором, содержащее дешифратор адреса, дешифратор управляющих сигналов, первый блок приемопередатчиков, причем информационный вход дешифратора адреса является входом устройства для подключения к выходу выборки ЭВу, группа информационных I входов-выходов первого бло ка приемо- I передатчиков образует группу входов- . выходов устройства для подключения к группе информационных и адресных входов-выходов ЭВМ, первый, второй, третий и четвертый информационные входы и первый выход дешифратора управляющих сигналов являются входами и выходом устройства для подключения соответственно к выходам ввода, вывода, установки, синхронизации и к входу Синхронизации ЭВМ, при этом группа старших разрядов информационного выхода первого блока приемопередатчиков соединена с группой информационных входов дешифраторов управляющих сигналов, группа младших разрядов информационного выхода первого блока приемопередатчиков соединена с группогд информационных входов дешифратора адреса, второй и третий выходы дешифратора управляющих сигналов соединены соответственно-с входом режима работы первого блока приемопередатчиков и синхровходом дешифратора адреса, отличающееся тем, что, с целью расширения номенклатуры сопрягаемых устройств, в него

введены шифратор и второй блок приемопередатчиков, причем первый - восьмой выходы шифратора являются выходами устройства для подключения соответственно к входам сброса, выбор-

ки, первому, второму и третьему адресным входам, входам чтения, подтверждения, записи микропроцессора, группа информационных входов-выходов второго блока приемопередатчиков образует группу,входов-выходов устройства для подключения к группе информационных входов-выходов микропроцессора, при этом группа информационных йыходов второго блока приемопередатчиков соединена с группой

информационных входов первого блока .приемопередатчиков, группа информа- циоиных выходов которого соединена с группой информацион1П)1х входов второго блока приемопередатчиков, входм режима работы которого соединен с четвертым выходом дешифратора управляющих сигналов у разрешающий вход . которого соединен с выходом дешифратора адреса, с разрешающим входом второго блока приемопередатчиков, с ра зрешающим входом шифрато за, группа информационных входов которого соединена с группой йыходов дешифратоpa управляющих сигналов,

cS

Фаг. 5

. от ff/1.2

Фие.§

ВУ

UQ

X /19рес

СНА

X

Устр-0 SvSp. /

ВВод

Чтение Ш

сип

т

X

Да X / Данные

Ш

Л.

f///7

шд- У

1Ж

Режим Зод

Ланные С

у

X

V

у

X

у

х.

у

Режим„Вы§од

У

х:

У

X

у

X

у

X

X

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-12—Подача