12

13

(П

4

09 Од СО Ю

ts

ков 5.1-5.I1-1, триггера 6 контрольного разряда, счетчика 7, дешифратора 8, О-триггеров 9.1-9,р+15 сумматора 10 по модулю два и задающего генератора 11. Внешними сигналами на входы 14 и 15 устройство приводится в исходное состояние и определяется вид контролируемого кода (двоичный или фибоначчиевый). Сигналом по входу 12 ;во входной регистр 1 записывается код контролируемого числа. По тактовым сигналам генератора 11 при помощи D-триггеров 9..1-9.Р+1 и сумматора

10 по модулю два выделяются разряды с нечетными весами р-кода Фибоначчи. Суммирование единиц по модулю два выделенных разрядов осуществляется последовательно в логических блоках Ь,1-5.п-1. Стробирование логических блоков 5 осуществляется сигналами дешифратора 8, Информация о четности контролируемого кода определяется сигналом с выхода триггера 6 контрольного двоичного кода осуществляется только сигналом, поступающим по входу 12. 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Генератор последовательности обобщенных @ -чисел фибоначчи с произвольными начальными условиями | 1986 |

|

SU1474627A2 |

| Конвейерный сумматор | 1988 |

|

SU1541595A1 |

| Синхронный десятичный счетчик | 1989 |

|

SU1661994A1 |

| Генератор последовательности обобщенных чисел Фибоначчи с произвольными начальными условиями | 1986 |

|

SU1345181A1 |

| Устройство для приведения кодов Фибоначчи к минимальной форме | 1989 |

|

SU1633496A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1984 |

|

SU1252779A1 |

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

Изобретение относится к вычислительной технике и используется для контроля на четность информации прие- мопередающих устройста, использующих фибоначчиевые коды. Цель изобретения - расширение функциональных возможностей за счет контроля информации в р-кодах Фибоначчи. Устройство со- . стоит из регистров 1.1-1.h входного кода, элементов И 2-4, логическихбйо

1

Изобретение относится к измерительной технике и может быть использовано для проверки информации на четность в системах приемопередачи и обработки данных, использующих фибоначчиевые коды.

Цель изобретения - расширение функиональных возможностей устройства за счет обеспечения возможности контроля чисел в р-кодах Фибоначчи.

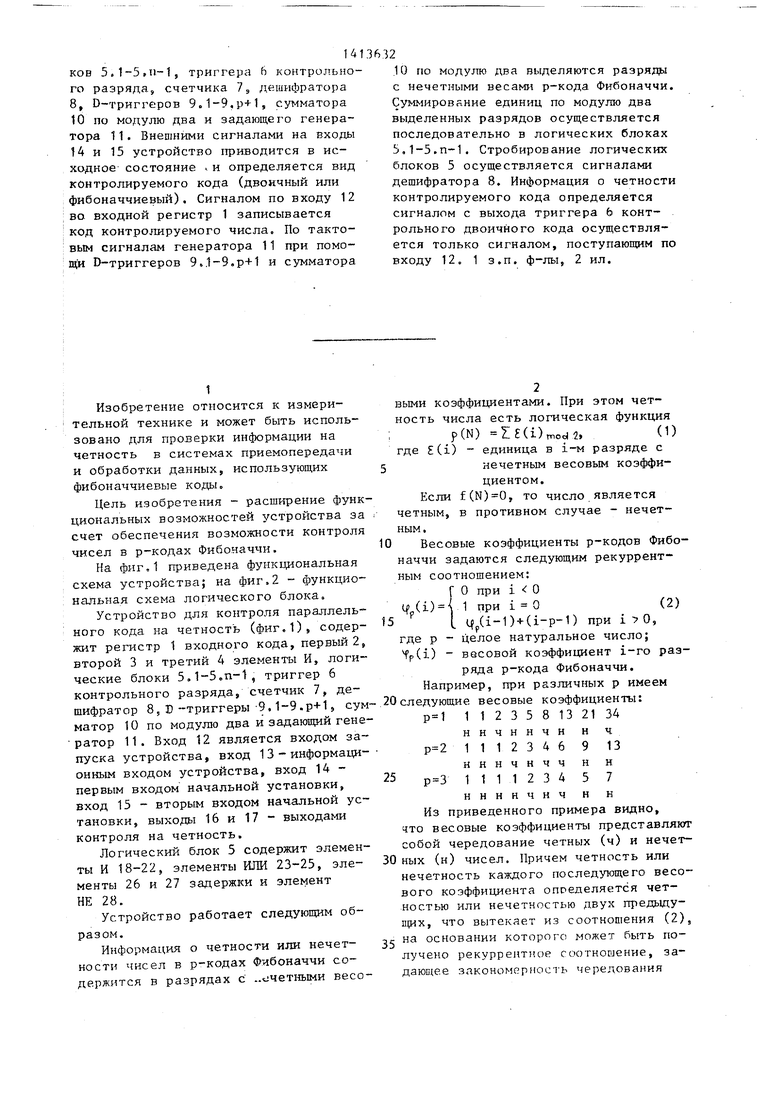

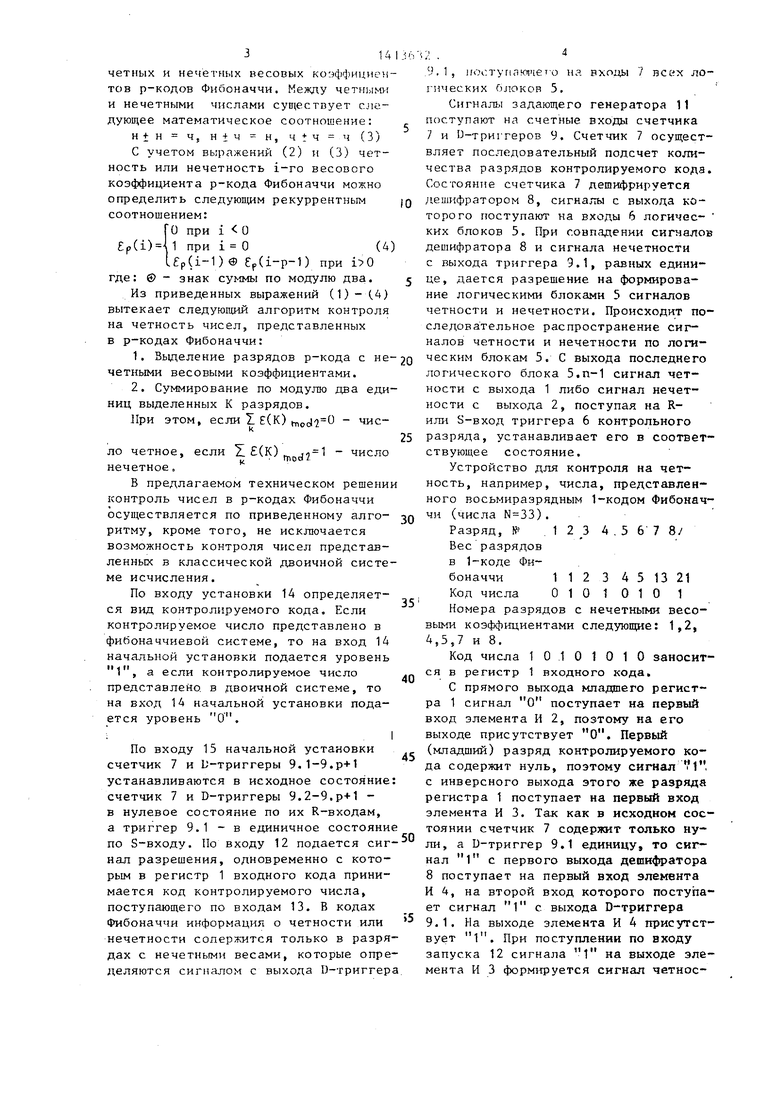

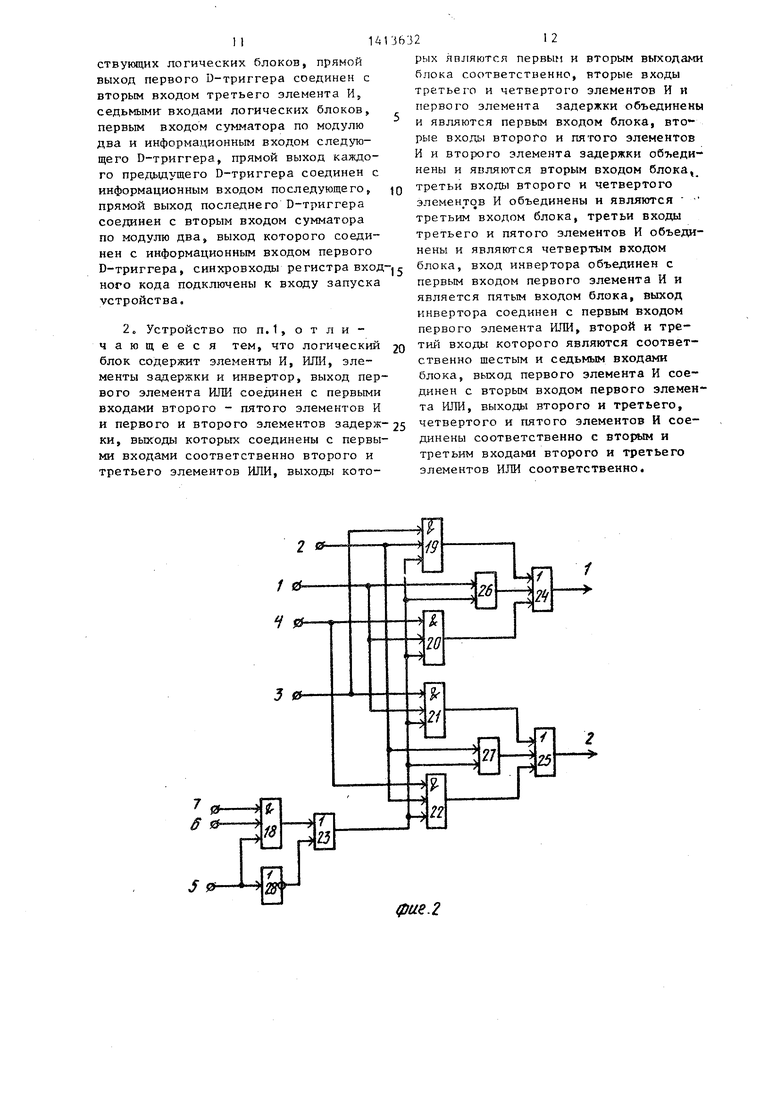

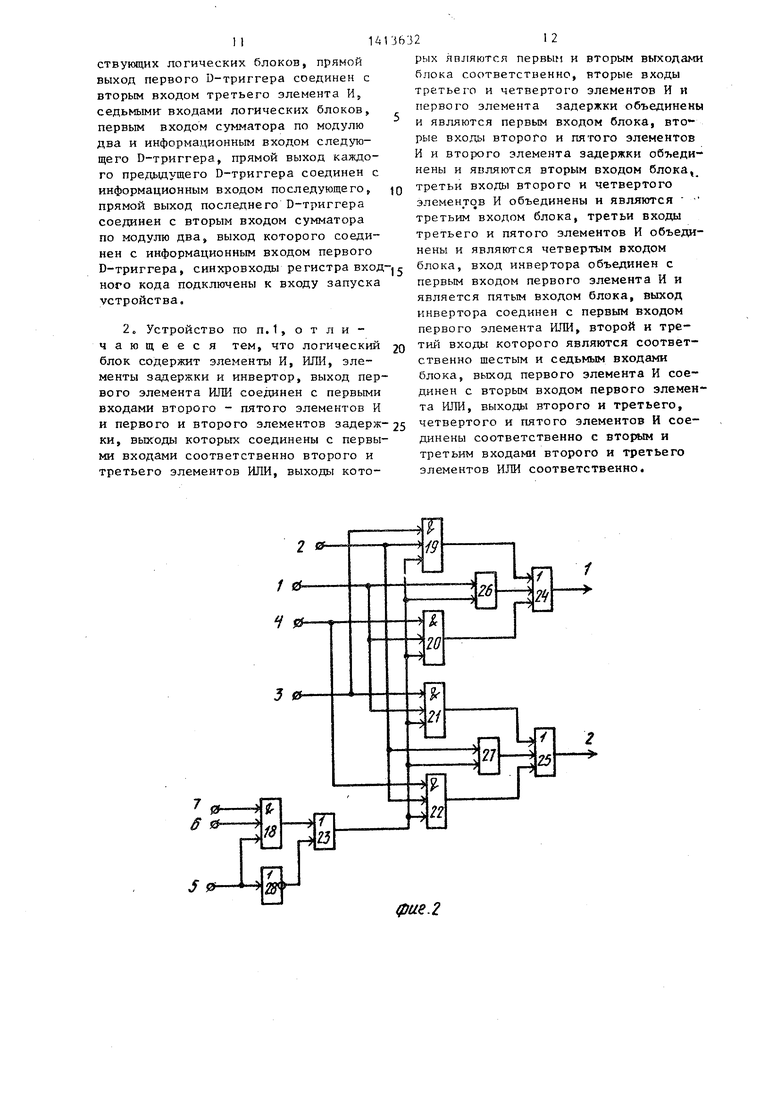

На фиг,1 приведена функциональная схема устройства; на фиг.2 функциональная схема логического блока.

Устройство для контроля параллельного кода на четность (фиг.О, содержит регистр 1 входного кода, первый 2, второй 3 и третий 4 элементы И, логические блоки 5.1-5,п-1, триггер 6 контрольного разряда, счетчик 7, дешифратор 8,Г -триггеры -9,1-9.р+1, сумматор 10 по модулю два и задающий гене- ратор 11. Вход 12 является входом запуска устройства, вход 13 - информационным входом устройства, вход 14 - первым входом начальной установки, вход 15 - вторым входом начальной установки, выходы 16 и 17 - выходами контроля на четность.

Логический блок 5 содержит элементы И 18-22, элементы ИЛИ 23-25, элементы 26 и 27 задержки и элемент НЕ 28.

Устройство работает следующим образом.

Информация о четности или нечетности чисел в р-кодах Фибоначчи соержится в разрядах с ..чет1в,1ми весовьши коэффициентами. При этом четность числа есть логическая функция

: p(N) l(i)od2, (1)

где (i) - единица в i-м разряде с 5нечетным весовым коэффициентом.

Если f(N)0, то число является четным, в противном случае - нечетным.

10 Весовые коэффициенты р-кодов Фибоначчи задаются следующим рекуррентным соотношением:

Г О при i О U (i) { 1 при 1 0(2)

15

Mip(i-1) + (i-p-1) при i.yO,

где р - целое нат фальное число; l p(i) - васовой коэффициент i-ro разряда р-кода Фибоначчи. Например, при различных р имеем 0 следующие весовые коэффициенты: 1 1 2 3 5 8 13 21 34

ннчннчн н ч 1 1 1 2 3 4 6 9 13

нннчнчч н н 5 111123457 ннннчнч н н Из приведенного примера видно, что весовые коэффициенты представляют собой чередование четных (ч) и нечет- 0 ных (н) чисел. Причем четность или нечетность каждого последующего весового коэффициента определяется четностью или нечетностью двух предыдущих, что вытекает из соотношения (2), г на основании которого может быть получено рекуррентное cooтнoDJeниe, задающее закономерность чередования

314

четных и нечётных весовых коэффициентов р-кодов Фибоначчи. Между четными и нечетными числами суп1естпует следующее математическое соотношение:

Н±Н ч, Н1Ч Н, 4t4 ч (3)

С учетом выражений (2) и (3) четность или нечетность i-ro весового коэффициента р-кода Фибоначчи можно определить следующим рекуррентным соотношением:

Го при i 0 p(i)(l при 1 0(4)

Up(i-l)® ep(i-p-l) при где: © - знак суммы по модулю два.

Из приведенных выражений (1)-Ч4) вытекает следую1ций алгоритм контроля на четность чисел, представленных в р-кодах Фибоначчи:

1ри этом, если Z Е(К) fT,ool 2 0

ло четное, если X (К) d число нечетное,

В предлагаемом техническом решении контроль чисел в р-кодах Фибоначчи осуществляется по приведенному алго- ритму, кроме того, не исключается возможность контроля чисел представленных в классической двоичной системе исчисления.

По входу установки 14 определяется вид контролируемого кода. Если контролируемое число представлено в фибоначчиевой системе, то на вход 14 начальной установки подается уровень 1, а если контролируемое число представлейо. в двоичной системе, то на вход 14 начальной установки подается уровень О . -,

По входу 15 начальной установки счетчик 7 и D-триггеры 9.1-9.р+1 устанавливаются в исходное состояние счетчик 7 и D-триггеры 9.2-9. - в нулевое состояние по их R-входам, а триггер 9.1 - Б единичное состояни по S-входу. По входу 12 подается сиг нал разрешения, одновременно с которым в регистр 1 входного кода принимается код контролируемого числа, поступающего по входам 13. В кодах Фибоначчи информация о четности или нечетности содержится только в разрядах с нечетными весами, которые определяются сигналом с выхода D-триггер

0

5

0

Q

5

5

5

.9.1, 1гоотуг1аю1че ч:) на входы 7 всех логических блоков 5,

Сигналы задающего генератора 11 поступают на счетные входы счетчика

7и и-триггеров 9. Счетчик 7 осуществляет последовательный подсчет количества разрядов контролируемого кода. Состояние счетчика 7 дешифрируется дешифратором 8, сигналы с выхода которого поступают на входы 6 логичес- ких блоков 5. При совпадении сигналов дешифратора 8 и сигнала нечетности

с выхода триггера 9.1, равных единице, дается разрешение на формирование логическими блоками 5 сигналов четности и нечетности. Происходит последовательное распространение сигналов четности и нечетности по логическим блокам 5. С выхода последнего логического блока 5.П-1 сигнал четности с выхода 1 либо сигнал нечетности с выхода 2, поступая на R- или S-вход триггера 6 контрольного разряда, устанавливает его в соответствующее состояние.

Устройство для контроля на четность, например, числа, представленного восьмиразрядным 1-кодом Фибоначчи (числа ).

Разряд, № 1 2 3 4 . 5 6 7 8/ Вес разрядов в 1-коде Фибоначчи 1 1 2 3 4 5 13 21 Код числа 0101010 1 Номера разрядов с нечетными весовыми коэффициентами следующие: 1,2, 4,5,7 и 8.

Код числа 10101010 заносится в регистр 1 входного кода.

С прямого выхода младшего регистра 1 сигнал О поступает на первый вход элемента И 2, поэтому на его выходе присутствует О. Первый (младший) разряд контролируемого кода содержит нуль, поэтому сигнал 1, с инверсного выхода этого же разряда регистра 1 поступает на первый вход элемента И 3. Так как в исходном состоянии счетчик 7 содержит только нули, а D-триггер 9.1 единицу, то сигнал 1 с первого выхода дешифратора

8поступает на первый вход элемента

И 4, на второй вход которого поступает сигнал 1 с выхода D-триггера 9.1. На выходе элемента И 4 присутствует 1. При поступлении по входу запуска 12 сигнала 1 на выходе элемента И 3 формируется сигнал четноети нпадшего разряда контролируемого кода. Сигнал 1 на выходе триггера свидетельствует о том, что анализируемый первьй разряд контролируемого кода является разрядом с нечетным весовым коэффициентом. Сигнал нечетности, равный нулю, с выхода элемента И 2 поступает на вход 2 логического блока 5.1, на входе 1 которого присутствует сигнал четности, равный единице, с выхода элемента ИЗ

Первый тактовый сигнал задающего генератора 11 увеличивает содержимое счетчика 7 на едиргацу. Соответствующее состояние счетчика 7 дешифрируется дешифратором. 8 и сигнал 1 с его второго выхода поступает на второй вход элемента И 18 логического блока 5 . 1 . На третьем входе элемента И 18 присутствует сигнал 1, поступающий по входу 14 устройства. Первый тактовый импульс содерл имое D-триггера 9.1 заносит в D-триггер 9.2, Так KtiK в исходном состоянии триггер 9,1 содержит единицу, а триггер 9.2 содержит нуль, то результат суммирования по модулю два на сумматоре 10, равный единице, принимается D-триггером 9.1, Таким образом, на выходе D-триггера 9,1 присутствует сигнал 1, Это .свидетельствует о том, что анализируемый в первом такт второй разряд контролируемого кода является разрядом с нечетным весовым коэффициентом. Этот сигнал поступает на первый вход элемента И 18 логического блока 5.1. На втором входе элемента И 18 также присутствует сигнал 1 с выхода дешифратора 8. Поэтому на выходе элемента И 18 присутствует сигНеШ 1, который через элемент ИЛИ 23 разрешает формирование сигналов четности или нечетности логического блока 5.1 и блокирует элемент 26 и 27 задержки по вторым входам. В первом такте на остальных входах логического блока 5,1 имеются следующие уровни сигналов: на выходе 1 - 1 с выхода элемента И 2; на входе 2 - О с выхода элемента И 3; на входе 3 - 1 с прямого выхода второго разряда регистра 1 , на входе 4 - 1 с инверсного выхода второго разряда регистра 1„

Так как на входе 2 имеется О, то элементы И 19 и 22 блокированы по вторым входам и на их выходах также присутствует О, как на вхо

5

0

5

де 4 находится О, то блокирован и элемент И 20 по первому вхойу.На все входы элемента И 21 поступает 1 с входов 3 и 1 и выхода элемента ИЛИ 23. Следовательно, на выходе элемента И 21 присутствует сигнал 1, которьш через элемент ИЛИ 25 поступает на выход 2 распространения сигнала нечетности логического блока 5.1,

Второй тактовый сигнал задающего генератора 11 осуществляет перезапись содерлшмых D-триггеров 9. Так как перед приходом второго тактового импульса D-триггеры 9 содержат единицы, то результат суммирования по модулю два на сумматоре 10, равный нулю, принимается D-триггером , Таким образом, на выходе D-триггера 9.1 присутствует сигнал О. Это свидетельствует о том, что анализируемый во втором такте третий разряд контролируемого кода является разрядом с четным весовым коэффициентом. Сигнал лог.О, поступая на первый вход элемента И 18 (вход 7) логического блока 5.2, запрещает формирование сигналов четности и нечетности. Так как на выходе элемента И 18 и на выходе элемента НЕ 28 имеется сигнал О, то и на выходе элемента ИЛИ 23 присутствует О, который блокирует все элементы И 19-22 логического блока 5.2. Одновременно этот жесигнал О поступает на вторые входы элемен- тов 26 и 27, разрешая задержку на один такт результатов анализа четности и нечетности предыдущих разрядов, поступающ} х на первые входы этих элементов, соответственно по входу 2 - сигнала нечетности, равного единице и по входу 1 - сигнала четности, равного нулю, на выходе 1 имеет О, а на выходе 2 - 1. Таким образом, во втором такте происходит только запоминание результатов контроля на четность предыдупщх разрядов на логическом блоке 5.2. Третий тактовый импульс также осуществляет перезапись содержимого D-триггеров 9. Так как перед приходом третьего тактового импульса результат суммирования на сумматоре 10 по модулю два был равен единице из-за наличия О на выходе D-триггера 9.1 и 1 на выходе D-триггера 9.2, то третьим тактовым сигналом ;( единица принимается D-триггером 9,1, свидетельствуя о нечетности весового коэффициента, равного 3, анализируе0

0

5

0

мого в третьем такте четвертого разряда кода. В этом такте на входах логического блока 5,3 имеются следующие сигналы: на входе 1 - О результат ангшиза предыдупщх разрядов - . сигнал четност на входе 2 - 1 результат анализа предыдущих разря-- ДОН сигнал нечетности; на входе 3 - 1, поскольку четвертый разряд кода содержит единицу; на входе 4 - О, поскольку четвертый разряд кода содержит единицу; на входе 7 - 15 поскольку D-триггер 9.1 содержит единицу; на входе 6 - 1 с выхода дешифратора 8.

Элементы И 20 и 21 блокированы сигналом О с входа 1. Элемент И 22

2 равным 13. Поэтому в логическом бл ке 5,6 происходят те же процессы, что и при анализе пятого разряда кода. На выходе 1 логического блок 5,6 имеется сиг нал четности анали

также блокирован сигналом О с входа 4. На входах элемента И 19 присут-2Q зируе№1Х разрядов, равный единице, ствуют сигналы 1 с входов 2 и 3 и , а на выходе 2 - сигнал нечетности, с выхода элемента ИЛИ 23, поскольку анализируемый разряд является разряравный нулю.

В седьмом такте на входах послед него логического блока .5.7 (5.п-1 25 имеются следующие сигналы: на вход

дом с нечетным весовым коэффициентом Единичный сигнал с выхода элемента И 19 поступает по первому входу элемента ИЛИ 24 блока 5.3 на выход 1, сигнализируя о четности анализируемых разрядов, т.е. сумма единиц анализи- первых двух разрядов с нечет- .jn ными весовыми коэффИ1щентами равна нулю.

В пятом такте на входах логического блока 5.4 имеются следующие сигналы: на входе 1 - 1 результат предыдущих логических операций; на входе 2 О результат предыдущих логических операций; на входе 3 - О ,, поскольку анализируемый разряд содержит нуль; на входе 4 - 1, поскольку пятый разряд кода содержит нуль;

25

35

40

на входе 7 - 1, поскольку анализи- нал 1, который через элемент ИЛИ

руемый разряд является разрядом с нечетным весовым коэффициентом, равным 5; на входе 6 - 1 с выхода дешифра-, тора 8.

Элементы И 19, 21 и 22 блокированы нулями с входов 2 и 3. На входах элемента И 19 присутствуют единичные сигналы с входов 1 и 4 и с выхода элемента ИЛИ 23, поэтому на выходе элемента И 20 присутствует единичный сигнал, который через третий вход элемента ИЛИ 24 поступает на выход 1 распространения сигнала четности логического блока 5.4. Так как следую- ащй, шестой, разряд кода является разрядом с четным весовым коэффициентом равным В, то в пятом такте происходит только запоминание сигналов четностд и нечетности на элементах 26 и 27 задержки результатов анализа предыду1 ;,их разрядов, как было описано для случая анализа третьего разряда. На выходе 1 элемента 1Ш: 24 блока 5.5 имеется сигнал четности анализируеь ых разрядов, равный едиQ нице, а на выходе 2 - сигнал нечетности, равный нулю.

В шестом такте анализируемый разряд содержит нуль и является разрядом с нечетным весовым коэффициентом,

2 равным 13. Поэтому в логическом бло- ке 5,6 происходят те же процессы, что и при анализе пятого разряда кода. На выходе 1 логического блока 5,6 имеется сиг нал четности аналиQ зируе№1Х разрядов, равный единице, а на выходе 2 - сигнал нечетности,

зируе№1Х разрядов, равный единице, а на выходе 2 - сигнал нечетности,

равный нулю.

В седьмом такте на входах последнего логического блока .5.7 (5.п-1) имеются следующие сигналы: на входе

1- 1 - сигнал четности; на входе

2- О - сиг нал нечетности; на входе 3 - 1, поскольку последний разряд кода содержит единицу; на входе 4 - О, поскольку последний разряд кода содержит единицу; на входе 7 - 1, поскольку восьмой разряд кода имеет нечетный весовой коэффициент, равный 21; на входе 6 - 1 - свыхоДа дешифратора 8.

Следовательно, элементы И 19,20 и 22 блокированы сигналами с входов 2 и 4. На входах элемента И 20 присутствуют сигналы единицы с входов 1 и 3 и с выхода элемента ИЛИ 23. На выходе элемента И 21 появляется сиг

0

25 поступает 2 нечетности логического блока 5.7, Этот сигнал с с выхода 2 поступает на S-вход триггера 6 контрольного разряда и устанавливает его в единичное состояние, что свидетельствует о нечетности контролируемого кода числа N 33„по выходу 16. Действительно, сумма единиц в разрядах 1,2,4,5,7 и 8 с нечетными весовыми коэффициентами равна единице:

f(N)I-(i)d 0+U1+0+0+1 1. Число + 1 .1+0-2+1 -З+О-З-И-В+О-13+ + 1 -21 33 также есть число нечетное.

В этом же такте переполняется счетчик 7, коэффициент пересчета которого выбирается равным разрядности п конт9 14

ролнруемого кода. Сигнал переполнения счетчика 7 может быть использован в качеств признака окончания работы устройства (не показано).

Работа устройства при контроле двоичного кода аналогична описанному с той лишь разницей, что при этом отпадает необходимость определения четности и нечетности весовых коэффициентов и поэтому подачей нулевого уровня на вход 14 устройства блокируется задающий генератор 11. Счетчик 7 находится в нулевом состоянии. В D-триггер 9.1 заносится единица по его S-входу подачей сигнала по входу 15. Нулевое состояние счетчика 7 дешифрируется дешифратором 8 и на входах элемента И 4 присутствуют единичные сигналы. Сигнал 1 с выхода элемента И 4 разрешает работу элементов И 2 и 3. Контроль двоичного кода осуществляется только сигналом, поступающим по входу 12 запуска с устройства, длительность которого выбирается в зависимости от суммарной длительног сти переходных процессов логических блоков 5, т,.е,

Т (n-1).,, где - длительность переходных процессов одного логического блока;

п - разрядность кода; ty- - время срабатывания элемента И.

В этом случае устройство представляет собой комбинационную схему контроля на четность двоичного кода и полностью выполняет функции прототипа

При контроле в кодах Фибоначчи длительность сигнала определяется по периоду следования тактовых импульсов зада1€щего генератора 11, т.е.

Т7(г}-1)

где t - период тактовых импульсов.

Таким образом, при помощи несущественного усложнения устройства для контроля на четность параллельного кода удается осуществить контроль чисел представленных в двоичной системе и в р-кодах Фибоначчи, тем самым расширяются функциональные возможности устройства. Кроме того, использование кодов Фибоначчи при построении устройств контроля вычислительной техники позволяет повы ть надежность и точность самих средств контроля.

Q о 5

0

Q

5

0

5

3210

Формула и 3 о п р е т е н и я

2,, Устройство по п. 1, о т л и - чающееся тем, что логический блок содержит элементы И, ИЛИ, элементы задержки и инвертор, выход первого элемента ИЛИ соединен с первыми входами второго - пятого элементов И и первого и второго элементов задержки, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, выходы которых являются первым и вторым выходами блока соответственно, вторые входы третьего и четвертого элементов И и первого элемента задержки объединены и являются первым входом блока, вторые входы второго и Г1ятого элементов И и второго элемента задержки объединены и являются вторым входом блока, третьи входы второго и четвертого элементов И объединены и являются третьим входом блока, третьи входы третьего и пятого элементов И объединены и являются четвертым входом блока, вход инвертора объединен с первым входом первого элемента И и является пятым входом блока, выход инвертора соединен с первым входом первого элемента ИЛИ, второй и третий входы которого являются соответственно шестым и седьмым входами блока, выход первого элемента И соединен с вторым входом первого элемента ИЖ, выходы второго и третьего, четвертого и пятого элементов И соединены соответственно с вторым и третьим входами второго и третьего элементов ИЛИ соответственно.

| Журавлев Ю.П., Котемок Л.А., Циклинский И.И | |||

| Надежность и контроль ЭВМ | |||

| - М.: Сов | |||

| радио, 1978, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-05—Подача