Изобретение относится к вычислительной технике и используется для подсчета импульсов в двоично-десятичном коде, а также в коде Фибоначчи.

Целью изобретения является расширение функциональных возможностей за счет встроенного функционального контроля.

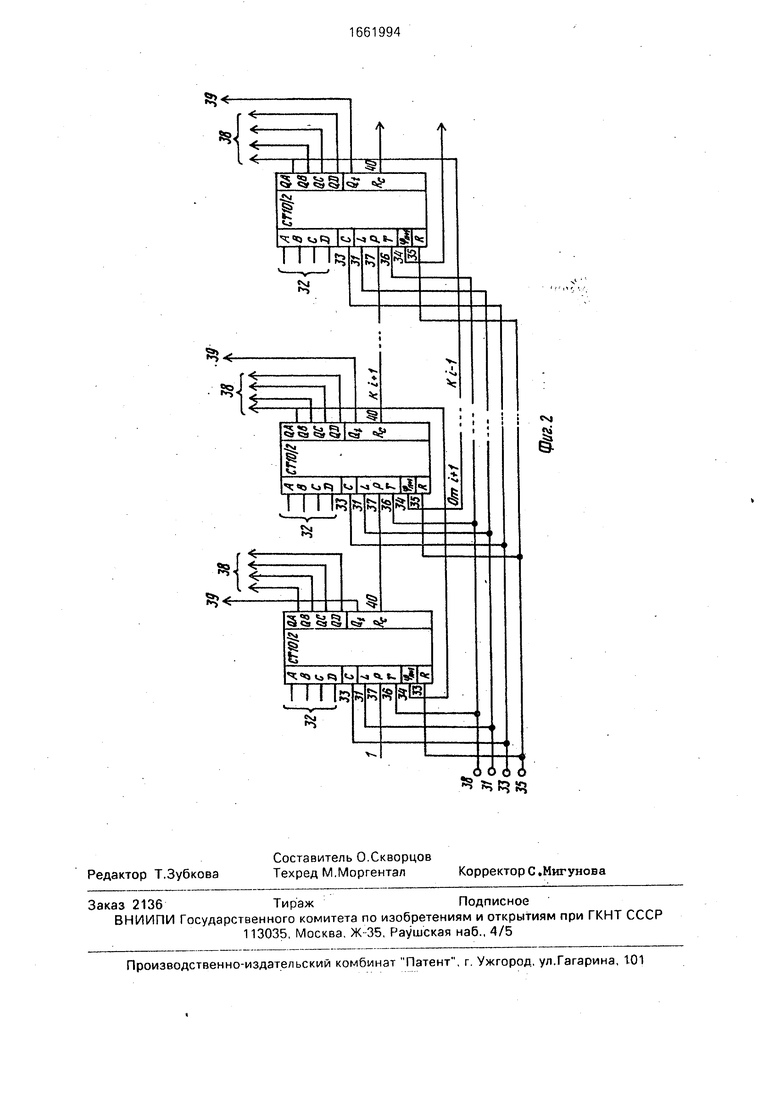

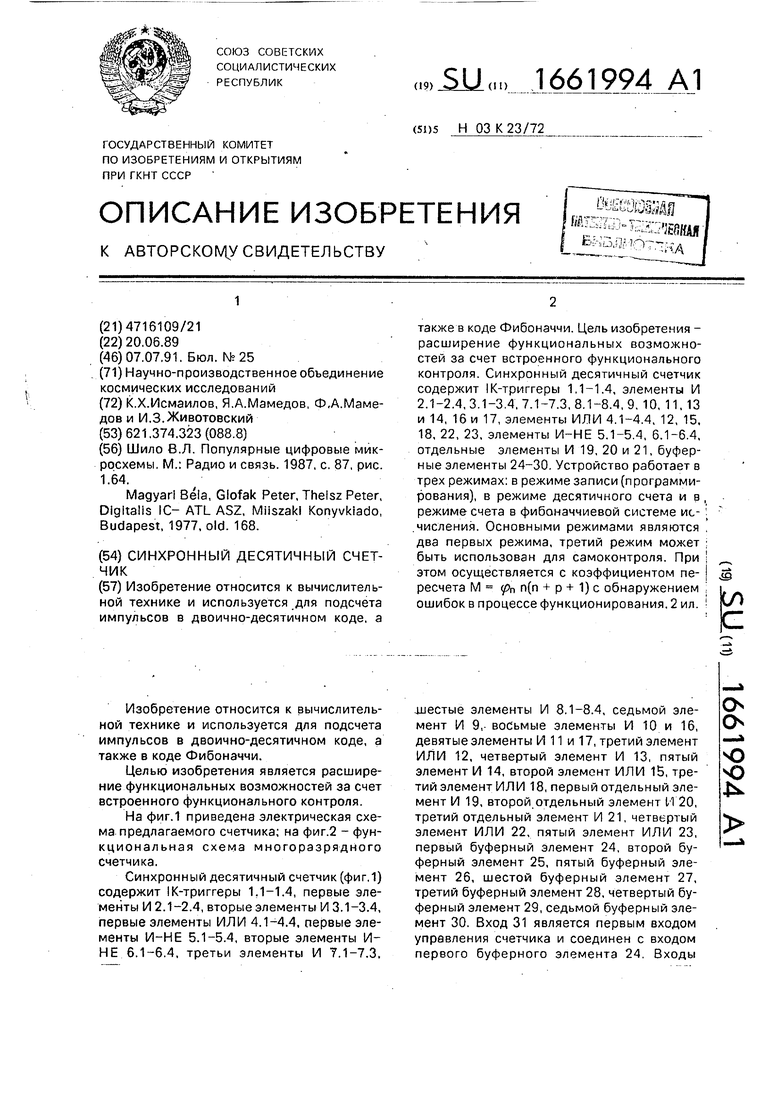

На фиг.1 приведена электрическая схема предлагаемого счетчика; на фиг.2 - фун- кциональная схема многоразрядного счетчика.

Синхронный десятичный счетчик (фиг.1) содержит IK-триггеры 1.1-1.4, первые элементы И 2.1-2.4, вторые элементы И 3.1-3.4, первые элементы ИЛИ 4.1-4.4, первые элементы И-НЕ 5.1-5.4, вторые элементы И-НЕ 6.1-6.4, третьи элементы И 7.1-7.3,

шестые элементы И 8.1-8.4, седьмой элемент И 9, восьмые элементы И 10 и 16, девятые элементы И 11 и 17, третий элемент ИЛИ 12, четвертый элемент И 13, пятый элемент И 14, второй элемент ИЛИ 15, третий элемент ИЛИ 18, первый отдельный элемент И 19, второй отдельный элемент 11 20, третий отдельный элемент И 21, четвертый элемент ИЛИ 22, пятый элемент ИЛИ 23, первый буферный элемент 24, второй буферный элемент 25, пятый буферный элемент 26, шестой буферный элемент 27, третий буферный элемент 28, четвертый буферный элемент 29, седьмой буферный элемент 30. Вход 31 является первым входом управления счетчика и соединен с входом первого буферного элемента 24. Входы

CN С

Ю О

32.1-32.4 являются информационными входами счетчика и соединены с первыми входами вторых элементов И-НЕ 6.1-6.4. Вход 33 является входом синхронизации и соединен с входом второго буферного элемента 25. Вход 34 является входом каскадирования и соединен с входом пятого буферного элемента 26. Вход 35 является входом установки нуля и соединен с входом третьего буферного элемента 28. Вход 36 является вторым входом управления счетчика и соединен с первым входом четвертого буферного элемента 29, с первым входом седьмого буферного элемента и с четвертым входом первого отдельного элемента И 19 Вход 37 является третьим входом управления счетчика и соединен с вторым входом четвертого буферного элемента 29, с вторым входом седьмого буферного-элемента 30 и с третьим входом первого отдельного элемента И 19 Выходы 38 1-38.4 являются информационными выходами счетчика и со единены с прямыми выходами соответствующих 1К-триггеров 1.1-1.4 Выход 39 является выходом контроля счетчика и соединен с выходом пятого элемента ИЛИ 23. Выход 40 является выходомкаскадирования

счетчика и соединен с выходом четвертого элемента ИЛИ 22, Выходы элементов И 2.1-2.4 соединены с (-входами соответствующих IK-триггеров 1.1-1.4. Выходы элементов И 3.1-3.4 соединены с К-входами соответствующих IK-триггеров 1.1-1 4 Выход каждого из элементов ИЛИ 4.1-4.4 соединен с вторым входом соответствующего элемента И 2.1-2.4 и с первым входом соответствующего элемента И 3.1-3.4. Выход каждого из элементов И-НЕ 5.1-5.4 соединен с первым входом соответствующего элемента И 2.1-2.4. Выход каждого из элементов И-НЕ 6.1-6.4 соединен с вторым входом соответствующего элемента И 3.1- 3.4 и с вторым входом соответствующего элемента И-НЕ 5.1-5,4. Выход каждого из элементов И 7.1-7.3 соединен с первым входом соответствующего элемента ИЛИ 4.1- 4.3. Выход элемента И 9 соединен с третьим входом элемента ИЛИ 4.2 Выходы элемента И 10 и элемента И 11 соедиены с входами третьего элемента ИЛИ 12. выход которого соединен с третьим входом элемента ИЛИ 4.3. Выходы элемента И 13 и элемента И 14 соединение входами второго элемента ИЛИ 15, выход которого соединен с первым входом элемента ИЛИ 4.4 Выходы элемента И 16 и элемента И 17 соединены с входами элемента ИЛИ 18 выход которого соединен с третьим входом элемента ИЛИ 4 4 Выходы отдельных элементов И 19 20 и 21 соединены с входами четвертого элемента ИЛИ

22 Выходы шестых элементов И 8.1-8.4 соединены с входами пятого элемента ИЛИ 23. Прямой выход К-триггера 1.1 соединен с первым входом элемента И 8.1, с вторым

входом элемента И 7.2, с вторым входом элемента И 9, с вторым входом элемента И 7.3, с вторым входом элемента И 11, с вторым входом элемента И 13, с вторым входом элемента И 14, с вторым входом элемента И

0 19 и с вторым входом элемента И 21. Инверсный выход IK-триггера 1.1 соединен с пятым входом элемента И 10. Прямой выход IK-триггера 1.2 соединен с первым входом элемента И 8.2, с вторым входом элемента

5 И 8.1, с третьим входом элемента И 7.3, с третьим входом элемента И 10, с третьим входом элемента И 13, с четвертым входом элемента И 16 и с вторым входом элемента И 20. Инверсный выход К-триггера 1.2 сое0 динен с вторым входом элемента И 7.1, с четвертым входом элемента И 11 и с вторым входом элемента И 17. Прямой выход IK- триггера 1.3 соединен с первым входом элемента И 8.3 с вторым входом элемента И 8.2,

5 с пятым входом элемента И 11, с четвертым входом элемента И 13, с третьим входом элемента И 17 и с третьим входом элемента И 21. Инверсный выход IK-триггера 1.3 соединен с третьим входом элемента И 9, с

0 вторым входом элемента И 10 и с вторым входом элемента И 16. Прямой выход IK- триггера 1.4 соединен с первым входом элемента И 8.4, с вторым входом элемента И

8.3,с третьим входом элемента И 14,стреть- 5 им входом элемента И 16, с первым входом

элемента И 19 и с первым входом элемента И 20. Инверсный выход IK-триггера 1.4 соединен с третьим входом элемента И 7.2, с четвертым входом элемента И 10, с третьим

0 входом элемента И 11 и с четвертым входом элемента И 17. Выход первого буферного элемента 24 соединен с первыми входами элементов И-НЕ 5.1-5.4, с вторыми входами элементов ИЛИ 4.1-4.4 с вторыми вхо5 дами элементов И-НЕ 6.1-6.4. Выход второго буферного элемента 25 соединен с входами синхронизации IK-триггеров 1.11.4.Выход пятого буферного элемента 26 соединен с входом шестого буферного эле0 мента, с вторым входом элемента И 8.4, с четвертым входом элемента И 21. Выход шестого буферного элемента 27 соединен с пятым входом элемента И 16 и с четвертым входом элемента И 17. Выход третьего бу5 ферного элемента 28 соединен с R-входами триггеров 1,1-1.4. Выход четвертого буферного элемента 29 соединен с третьим входом элемента ИЛИ 4,1, с первыми входами элементов И 7.2, 7.3 и с первыми входами элементов И 13 и 14, Выход седьмого буферного элемента 30 соединен с первым входом элемента И 7.1, с первым входом элемента И 9, с первыми входами элементов И 10, 11, 16 и 17, с третьим входом элемента И 20 и с первым входом элемента И 21.

Синхронный десятичный счетчик работает следующим образом.

Подачей высокого уровня на вход 35 установки нуля устройство приводится в исходное нулевое состояние сигналом с выхода буферного элемента 28 на R-входы IK-триггеров 1.1-1.4.

Сигналы на управляющих входах 31, 36 и 37 определяют режимы работы устройства.

Режим записи выбирается подачей низкого уровня сигнала на вход 31 первого буферного элемента 24. В этом режиме состояние входов 36 и 37 безразлично. Режимы работы IK-триггеров 1.1-1.4 определяются сигналами на информационных входах 32.1-32.4. Сигналы с этих входов поступают на первые входы элементов И-НЕ 6.1-6.4. На первых входах элементов И-НЕ 5.1-5.4, на вторых входах элементов И-НЕ 6.1-6.4 и на вторых входах элементов ИЛИ 4.1-4.4 присутствует единичный (высокий уровень) сигнал с выхода буферного элемента 24. Поэтому на втором входе элементов И 2.1-2.4 и первом входе элементов И 3.1-3.4 присутствует высокий уровень. Допустим, что в первый разряд устройства необходимо записать логический нуль (низкий уровень), поступающий по входу 32.1. В этом случаема выходе элемента И-НЕ 6.1 присутствует единичный сигнал. Следовательно, на выходе элемента И 3.1 также появится высокий уровень. В то же время высокий уровень сигнала с выхода элемента И-НЕ 6.1 поступает на второй вход элемента И- НЕ 5.1 и на его выходе появится низкий уровень. Следовательно, на выходе элемента И 2.1 будет низкий уровень сигнала. Таким образом, на 1-входе IK-триггера 1,1 - низкий, а на К-входе IK-триггера 1.1 - высокий уровни сигнала. Вход I является входом синхронной записи единицы,а вход К - входом записи нуля IK-триггеров. Следовательно, в IK-триггер 1.1 запишется низкий уровень при поступлении синхросигнала на вход 33. Допустим, что в первый разряд устройства необходимо записать логическую единицу (высокий уровень), поступающий по входу 32.1. В этом случае на выходе элемента И-НЕ 6.1 присутствует низкий уровень. На выходе элемента И-НЕ 5.1 высокий уровень сигнала. На выходе элемента И 3.1 - низкий, а на выходе элемента И 2.1 - высокий уровни сигнала, и IK-триггер находится в режиме записи единицы. Остальные

разряды устройства работают аналогично,Вторым режимом устройства является

режим десятичного счета. Для выбора этого режима на управляющие входы 31 и 36

подается высокий уровень сигнала. При

отдельном использовании четырезхразрядного счетчика на вход 37 необходима подача

высокого уровня. Единичный сигнал с выхо0 да буферного элемента 29 поступает на вход элемента ИЛИ 4.1, а с выхода последнего - на входы элементов И 2.1 и 3.1. Поскольку на входе 31 присутствует высокий уровень сигнала, то с выхода буферного элемента 24

5 низкий уровень сигнала блокирует элементы И-НЕ 5.1-5.4 и 6.1-6.4, на выходах которых появятся высокие уровни сигнала. Таким образом, поскольку на входах элементов И 2.1 и 3.1 присутствуют высокие

0 уровни, то IK-триггер 1.1 будет находиться в счетном режиме. Режим работы IK-триггера 1.2 будет определяться только состоянием IK-триггера 1.1, сигнал с прямого выхода которого поступает на второй вход элемента

5 И 7.2 и через элемент ИЛИ 4.2 на входы элементов И 2.2 и 3.2. На выходах этих элементов будет присутствовать высокий уровень, а значит IK-триггер 1.2 будет находиться в счетном режиме только в том

0 случае, когда I К-тригг.ер 1.1 содержит единицу. Это условие нарушается по достижении устройством состояния, предшествующего последнему, т.е. когда в счетчик запишется код 1000 (8ю). Сигнал низкого уровня с ин5 версного выхода I К-триггера 1.4 поступит на третий вход элемента И 7.2 и блокирует его, В этом случае IK-триггер 1.2 будет находиться в режиме хранения, обусловленного низким уровнем на его I и К-входах. Состояние

0 IК-триггера 1.3 определяется сигналами IK- триггеров 1.1 и 1.2, поступающими на второй и третий входы элемента 7.3 соответственно. При единичном состоянии ГК-триггеров 1.1 и 1.2 IK-триггер 1.3 будет

5 находиться в счетном режиме, а в остальных случаях - в режиме хранения. Состояние IK-триггера 1.4 определяется сочетаниями сигналов с выходов IK-триггеров 1.1-1.3 и своим состоянием в предыдущий момент

0 времени. Сигналы с выходов IK-триггеров 1.2 и 1,3 поступают на третий и четвертый входы элемента И 13, на второй вход которого поступает сигнал с выхода I К-триггера 1.1, который также подается на второй вход

5 элемента И 14, на третий вход которого подается сигнал с выхода IK-триггера 1.4. Таким образом, счетный режим IK-триггера 1.4 определяется двумя сочетаниями сигналов. До достижения счетчиком состояния 1000 (8ю) счетный режим IK-триггера 1.4 определяется единичными состояниями IK-ттриггеров 1.1-1.3, а при достижении последнего состояния 1001 (9ю) IK-триггеров 1.1 и 1.4. В этом состоянии нетрудно убедиться, что IK-триггеры 1.2 и 1.3 находятся в режиме хранения. Так как 1К-триггеры 1.1 и 1.4 находятся в счетном режиме, то десятый счетный сигнал установит счетчик в исходное нулевое состояние. По достижении счетчиком состояния 1001 на первом и втором входах отдельного элемента И 19 единичные сигналы с выходов IK-триггеров 1,4 и 1.1. На четвертом входе элемента И 19 единичный сигнал с входа 36, а на третьем входе элемента И 19 с входа 37. Следовательно, на входе элемента ИЛИ 22 единичный сигнал, поступающий на вход 37 следующего счетчика при каскадировании, и разрешающий счет (см. фиг.2).

Третьим режимом устройства является режим самоконтроля или режим счета в фи- боначчиевой системе исчисления.

Для выбора этого режима на управляющий вход 36 подается низкий уровень сигнала. Состояние входа 37 при отдельно используемом устройстве - единичное, такое же состояние и на входе 34.

При подаче низкого уровня на вход 36 буферный элемент 29 блокирован. Следовательно, блокированы элементы И 7.2, 7.3, 13 и 14. Нулевой сигнал с входа 36 поступает на инвертирующий вход буферного элемента 30, и поскольку на другом входе этого элемента присутствует единичный сигнал, то на выходе элемента 30 появляется единичный сигнал, который поступает на первые входы элементов И 7.1, 9, 10, 11, 16, 17, 21 и третий вход элемента И 20.

В этом режиме рашгы состояния I К-триггеров 1.1 и 1.2 будут определяться сигналами с выходов элементов И 7.1 и 9, поступающими на входы элементов ИЛИ 4.1 и 4.2, а состояния IK-триггеров 1.3 и 1.4 -с элементов И 10, 11 и 16, 17, поступающими на входы элемента ИЛИ 12 и 18, с выходов которых сигналы поступают на третьи входы элементов ИЛИ 4.3 и 4.4. Т.е. режимы работы IK-триггеров определяются состояниями каждого последующего IK-триггера подачей сигнала с инверсного выхода на вход соответствующего элемента И предыдущего разряда. Так, режим работы IK-триггера 1.1 определяется сигналом с инверсного выхода 1К-триггера 1.2, поступающего на второй вход элемента И 7.1. Режим работы IK-триггера 1.2 - сигналом с инверсного выхода IK-триггера 1.3, поступающего на третий вход элемента И 9. Режим работы IK-триггера 1.2 определяется также сигнапом с прямого выхода IK-триггера 1.1, поступающего на второй вход элемента И 9.

Режим работы IK-триггеров 1.3 и 1.4 определяется на основании логического урав- нения:

для произвольного р

li Ki Qi+pA...AQ j+i(QjAQMAQ ,-2Л... Qi-p-iVQiA AQi-iAQi-#...AQ,.p-i)(1)

для описываемого устройства при фор- 0 мула приобретает.вид

IгККЫ (0,ЛО i-iAQj-2+QiAQi-i AQ ,2), (2) где Qi -.состояние 1-го разряда в момент времени tn.

Для IK-триггера 1.4 сигнал QM поступа- 5 ет с входа 34 через буферные элементы 26 и 27.

На входы элемента И 16 сигналы поступают соответственно с инверсного выхода IK-триггерз 1.3, с прямого выхода IK-тригге- 0 ра 1.4, с прямого выхода IK-триггера 1.2, с буферного элемента 27, На входы элемента И 10 сигналы поступают соответственно с инверсного выхода IK-триггера 1.3, с прямого выхода IK-триггера 1.2, с инверсного вы- 5 хода IK-триггера 1.4. На входы элемента И

IIсигналы поступают соответственно с прямого выхода IK-триггера 1.1, с инверсного выхода IK-триггера 1.4, с инверсного выхода IK-триггера 1.2 и с

0 прямого выхода IK-триггера 1.3. Отличительной особенностью работы счетчика в этом режиме является то, что в произвольный момент времени два подряд идущих разряда (в общем случае р+1) могут содер5 жать только один единичный разряд, т.е. счетчик в основании системы исчисления использует минимальную форму р-кодов Фибоначчи.

В исходном состоянии все триггеры

0 содержат нули. На выходе элемента И 7.1 присутствует единичный сигнал, обусловленный единичным сигналом с инверсного выхода IK-триггера 1.2. Элемент И 9 блокирован нулевым сигналом с прямого

5 выхода IK-триггера 1.1. Элементы И 10, 11 и 16, 17 блокированы нулевыми сигналами с выходов IK-триггеров 1.2 и 1,3. Таким образом, первый синхросигнал установит в единичное состояние IK-триггер 1.1. На входе

0 элемента И 7.2 и, следовательно, на его выходе и на I- и К-входах IK-триггера 1.2 появится единичный сигнал, и этот триггер перейдет в режим счетного триггера. Режимы остальных триггеров не меняются. Вто5 рой синхросигнал в счетчик запишет код 0010. На основании логического уравнения (2) и описанных выше связей IK-триггер 1,3 будет находиться в режиме счетного триггера перед приходом третьего синхросигнала, поскольку на выходе элемента И 10 будет

присутствовать единичный сигнал, который через элементы ИЛИ 12 и 4.3 и элементы И

2.3и 3.3 поступит на 1-й К-входы 1К-триггера 1.3. Третий синхросигнал в счетчик запишет код 0100. Режим IK-триггера 1.1 аналогичен режиму в первом такте. На основании уравнения (2) остальные триггеры .4 будут находиться в режиме хранения, так как QI з 0 и QI 2 0. Соответственно на выходах элементов И 10,11 и 16, 17-нулевые сигналы и, следовательно, на I- и К-входах IK-триггеров 1.2-1.4 нули. Четвертый синхросигнал запишет в счетчик код 0101. Перед приходом пятого синхросигнала IK-тригге- ры 1.1 и 1.3 находятся в счетном режиме, а 1 К-триггер 1.2 в режиме хранения, так как QI з 0, элемент И 9 блокирован и на его выходе нулевой сигнал. На выходе элемента И 11 единичный сигнал, так как на его входах присутствуют единичные сигналы, т.е. QI 1 1. Qi,.Qi4 1 nQi2 1. iK-триггер

1.4также находится в счетном режиме, так как на выходе буферного элемента 27 присутствует единичный сигнал; Ch A 1 с инверсного выхода IK-триггера 1.4, Сиз 1 с прямого выхода IK-триггера 1.3 и Qi2 1с инверсного выхода IK-триггера 1.2. Таким образом, на входах элемента И 17 присутствуют единичные сигналы и, следовательно, этот сигнал через элементы ИЛИ 18 и 4.4 и элементы И 2.4 и 3.4 поступает на I- и К-входы IK-триггера 1.4. Пятый синхросигнал запишет в счетчик код 1000. В дальнейшем работа счетчика аналогична описанному выше и продолжается до состояния 1010. Так как перед приходом последнего синхросигнала IK-триггеры 1.1 и 1.3 находятся в режиме хранения, а IK-триггеры 1.2 и 1.4 - в счетном режиме, то последний синхросигнал приведет счетчик в исходное состояние. Таким образом, имеем счетчик в 1-м коде Фибоначчи с коэффициентом пересчета М р (п+р+1) 8. По достижении счетчиком состояния 1010 на входах элемента И 20 присутствуют единичные сигналы с выходов IK-триггеров 1.2 и 1.4. На выходе элемента И 20 и на выходе элемента ИЛИ 22 единичный сигнал. При каскадировании на вход 3 следующего каскада поступит единичный сигнал и разрешит его работу.

Следующий синхросигнал установит в единичное состояние IK-триггер 1.1 следующего каскада, и сигнал низкого уровня поступает на вход 34 предыдущего каскада. Элементы И 16 и 17 этого каскада оказываются блокированными и до окончания счета IK-триггера 1.4 будут находиться в режиме хранения. В этом случае предыдущий каскад может достигнуть только состояния 0101, после чего следующим синхросигналом установится в исходное состояние. При единичном сигнале на входе 34 на выходе

буферного элемента 26 также единичный сигнал. Элемент И 13 разблокирован и при состоянии 0101 на его входах будут присутствовать единичные сигналы с выходов IK-триггеров 1.1 и 1.3. На выходе элемента

И 21 и на выходе элемента ИЛИ 22 единичный сигнал. Таким образом, обеспечивается каскадирование. В режиме счета в минимальной форме кода Фибоначчи возможно обнаружение ошибок по признаку нарушения минимальной формы. Сигналы с прямых выходов IK-триггеров 1.1-1.4 поступают на первые входы соответствующих элементов И 8.1-8.4, На вторые входы элементов И 8.1-8.3 поступают сигналы с прямых выходов IK-триггеров 1.2-1.4. На второй вход элемента И 8 4 сигнал поступает с выхода буферного элемента 26, на вход которого поступает сигнал с прямого выхода 38.1 младшего разряда (К-триггера 1.1 следующего каскада (см. фиг.2). Выходной сигнал элемента ИЛИ 23 формирует сигнал по уравнению п

Qt V. QI A Q.-M.(3)

При наличии двух единиц подряд на 1-м

и (Ы)-м или (1+1)-м и i-м разрядах на выходе 39 элемента ИЛИ 23 появится единичный сигнал, свидетельствующий об ошибке. При каскадировании каждый выход 39 может быть использован для контроля каждого каскада, тогда ошибкообнаружительная способность одного каскада равна

16 -8 по. -те 100 Ј po 2 - n+P+i):100%

50%.

Выход 39 также может быть использован как общий контрольный выход при объединении в монтажное ИЛИ. Тогда ошибкообнаружительная способность, например, четырехкаскадного счетчика (16 разрядов) равна

рп ).

Таким образом, удается обеспечить режим счета в фибоначчиевой системе исчисления, позволяющей относительно просто обнаруживать ошибки в процессе счета, если счет ведется в кодах Фибоначчи, или

позволяет тестировать при работе в двоичной или десятичной системе исчисления. Формула изобретения Синхронный десятичный счетчик, содержащий в каждом разряде IK-триггер,

первый и второй элементы И, первый и второй элементы И-НЕ,1 элемент ИЛИ, второй и третий разряды содержат третий элемент И, выход которого соединен с первым вводом элемента ИЛИ, четвертый разряд содержит четвертый и пятый элементы И, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с первым входом первого элемента ИЛИ, причем з каждом разряде выход второго элемента И-НЕ соединен с вторыми входами первого элемента И-НЕ и второго элемента И, выход первого элемента И-НЕ соединен с первым входом первого элемента И, выход элемента ИЛИ соединен с вторым и первым входами соответственно первого и второго элементов И, выходы которых соединены соответственно с - и К- входами IK-триггера, первые входы первых элементов И-НЕ, вторые входы вторых элементов И-НЕ и вторые входы элементов ИЛИ всех разрядов объединены и соединены с выходом первого буферного элемента, вход которого является первым входом управления счетчика, первый вход второго элемента И-НЕ каждого разряда соединен с соответствующим информационным входом счетчика, вход синхронизации которого соединен с входом второго буферного элемента, выход которого соединен с входом синхронизации IK-триггеров всех разрядов, входы установки нуля которого объединены и соединены с выходом третьего буферного элемента, вход которого является входом установки нуля, второй и третий входы управления которого соединены с входом четвертого буферного элемента, выход которого соединен с третьим входом первого элемента ИЛИ первого разряда, с первым входом третьих элементов И второго и третьего разрядов,с первыми входами четвертого и пятого элементов И, прямой выход IK-триггера первого разряда соединен с вторыми входами третьих элементов И второго и третьего разрядов, с вторыми входами четвертого и пятого элементов И четвертого разряда и с вторым входом отдельного элемента И, третий вход которого соединен с вторым входом четвертого буферного элемента, прямой выход IK-триггера второго разряда соединен с третьим входом третьего элемента И третьего разряда, с третьим входом четвертого элемента И четвертого разряда, прямой выход IK-триггера третьего разряда соединен с четвертым входом четвертого элемента И четвертого разряда, прямой выход IK-триггера четвертого разряда соединен с третьим входом пятого элемента И четвертого разряда и с первым входом отдельного элемента И, инвернсный выход IK-триггера четвертого разряда соединен с третьим входом третьего элемента И второго разряда, прямые выходы IK-триггеров всех разрядов являются информационными выходами счетчика, отличающийся тем, что, с целью расширения функцинальных возможностей за счет встроенного функционально0 го контроля, в каждый разряд введены шестой элемент И, первый вход которого соединен с прямым выходом соответствующего IK-триггера, второй вход - с прямым выходом IK-триггера следующего разряда,

5 в первый разряд дополнительно введен третий элемент И, выход которого соединен с первым входом элемента ИЛИ, во второй разряд введен седьмой элемент И, выход которого соединен с третьим входом эле0 мента ИЛИ, в третий и четвертый разряды введены восьмой и девятый элементы И, выходы которых соединены с третьим элементом ИЛИ, выход которого соединен с третьим входом первого элемента ИЛИ со5 ответствующего разряда, кроме того, в счетчик введены пятый, шестой и седьмой буферные элементы, второй и третий отдельные элементы И, четвертый и пятый элементы ИЛИ, прямой выход IK-триггера

0 первого разряда соединен с вторым входом седьмого элемента И второго разряда, с вторым входом девятого элемента И третьего разряда и вторым входом третьего отдельного элемента И, инверсный выход IK-триг5 гера первого разряда соединен с пятым входом восьмого элемента И третьего разряда, прямой выход IK-триггера второго разряда соединен с третьим входом восьмого элемента И третьего разряда, с четвертым

0 входом восьмого элемента И четвертого разряда и с вторым входом второго отдельного элемента И, инверсный выход IK-триггера второго разряда соединен с вторым входом третьего элемента И первого разря5 да, с четвертым входом девятого элемента И третьего разряда и с вторым входом девятого элемента И четвертого разряда, прямой выход IK-триггера третьего разряда соединен с пятым входом девятого элемен0 та И третьего разряда, с третьим входом девятого элемента И четвертого разряда и с третьим входом третьего отдельного элемента И, инверсный выход третьего IK-триггера третьего разряда соединен с третьим

5 входом седьмого элемента И второго разряда, с вторым входом восьмого элемента И третьего разряда, с вторым входом восьмого элемента И четвертого разряда, прямой выход IK-триггера четвертого разряда соединен с третьим входом восьмого элемента

I/I четвертого разряда и с первым входом второго отдельного элемента И, инверсный выход IK-триггера четвертого разряда соединен с третьим входом третьего элемента И второго разряда, с четвертым входом восьмого элемента И и с третьим входом девятого элемента И третьего разряда, с четвертым входом девятого элемента И четвертого разряда, выходы шестых элементов И всех разрядов соединены с соответствую- щими входами пятого элемента ИЛИ, выход которого является выходом контроля счета устройства, вход каскадирования которого соединен с пятым буферным элементом, выход которого соединен с вторым входом ше- стого элемента И четвертого разряда, с четвертым входом третьего отдельного элемента И, с входом шестого буферного элемента, выход которого соединен с пятым входом восьмого и девятеу-о элементов И

четвертого разряда, первый вход четвертого буферного элемента соединен с четвертым входом первого отдельного элемента И и с первым входом седьмого буферного элемента, второй вход четвертого буферного элемента соединен с вторым входом седьмого буферного элемента, выход которого соединен с первым входом третьего элемента И первого разряда, с первым входом седьмого элемента И второго разряда, с первым входом восьмого и девятого элементов И третьего и четвертого разрядов, с третьим входом второго отдельного элемента И и первым входом третьего отдельного элемента И, выходы отдельных элементов И соединены с соответствующими входами четвертого элемента ИЛИ, выход которого является выходом каскадирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Генератор последовательности обобщенных чисел Фибоначчи с произвольными начальными условиями | 1986 |

|

SU1345181A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Генератор последовательности обобщенных @ -чисел фибоначчи с произвольными начальными условиями | 1986 |

|

SU1474627A2 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для формирования последовательности натуральных чисел в @ -коде Фибоначчи | 1984 |

|

SU1249007A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

Изобретение относится к вычислительной технике и используется для подсчета импульсов в двоично-десятичном коде, а также в коде Фибоначчи. Цель изобретения - расширение функциональных возможностей за счет встроенного функционального контроля. Синхронный десятичный счетчик содержит JK-триггеры 1.1 - 1.4, элементы И 2.1 - 2.4, 3.1 - 3.4, 7.1 - 7.3, 8.1 - 8,4, 9, 10, 11, 13 и 14, 16 и 17, элементы ИЛИ 4.1 - 4.4, 12, 15, 18, 22, 23, элементы И - НЕ 5.1 - 5.4, 6.1 - 6.4, отдельные элементы И 19, 20 и 21, буферные элементы 24 - 30. Устройство работает в трех режимах: в режиме записи /программирования/, в режиме десятичного счета и в режиме счета в фибоначчиевой системе исчисления. Основными режимами являются два первых режима, третий режим может быть использован для самоконтроля. При этом счет осуществляется с коэффициентом пересчета M = φN(N + P + 1) с обнаружением ошибок в процессе функционирования. 2 ил.

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Популярные цифровые микросхемы | |||

| М.: Радио и связь | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Magyar Bela, Glofak Peter, Thelsz Peter, Digitalis 1C- ATL ASZ, Miiszaki Konyvkiado, Budapest, 1977, old | |||

| Приспособление, заменяющее сигнальную веревку | 1921 |

|

SU168A1 |

Авторы

Даты

1991-07-07—Публикация

1989-06-20—Подача