Изобретение относится к импульсной ехнике и может быть использовано для чета импульсов в коде Фибоначчи, Цель изобретения - погзытение быстодействия пересчетной схем,.

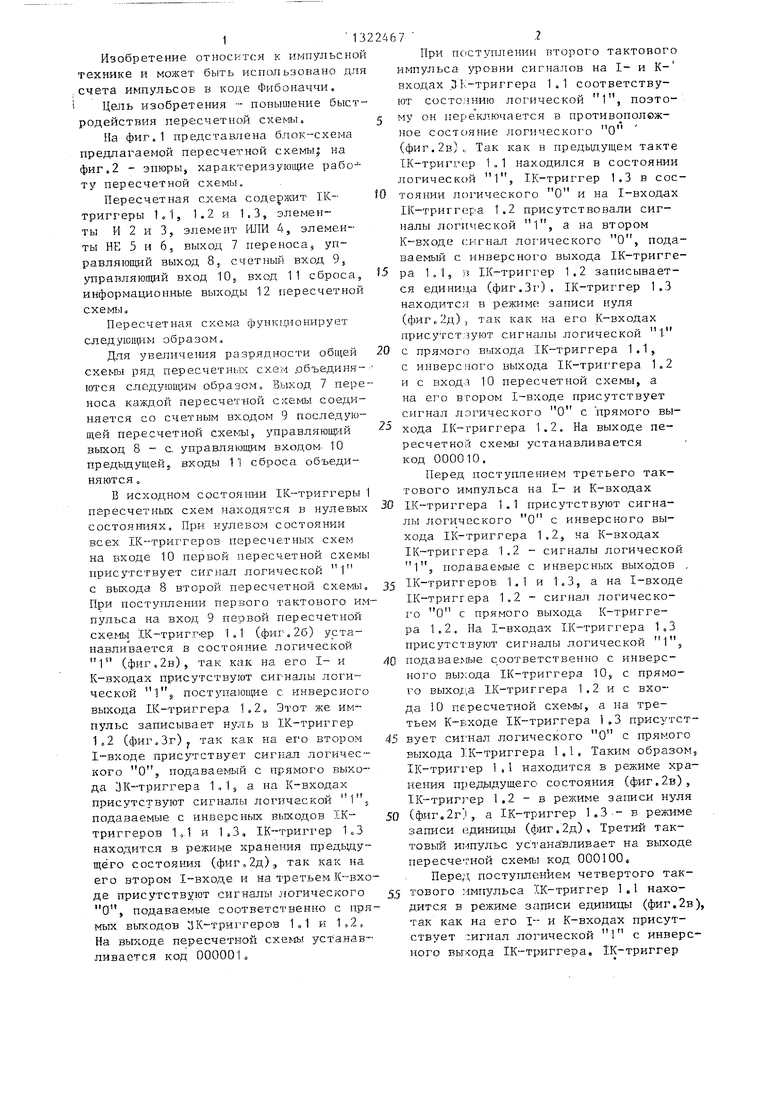

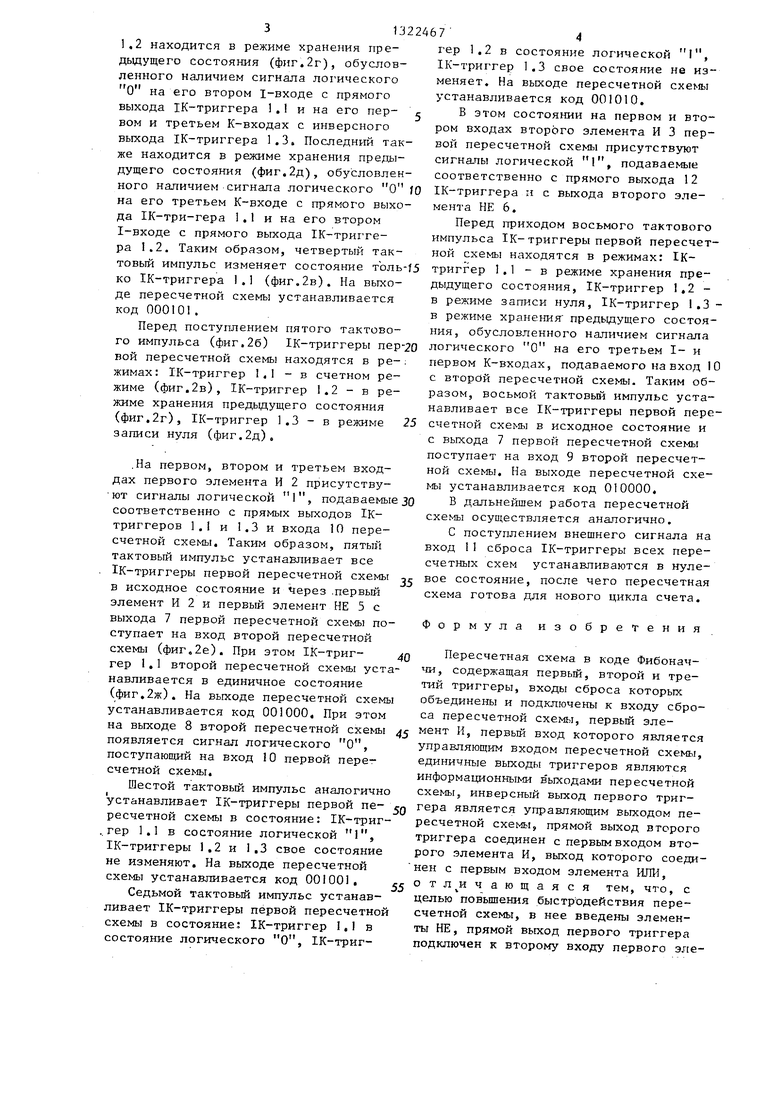

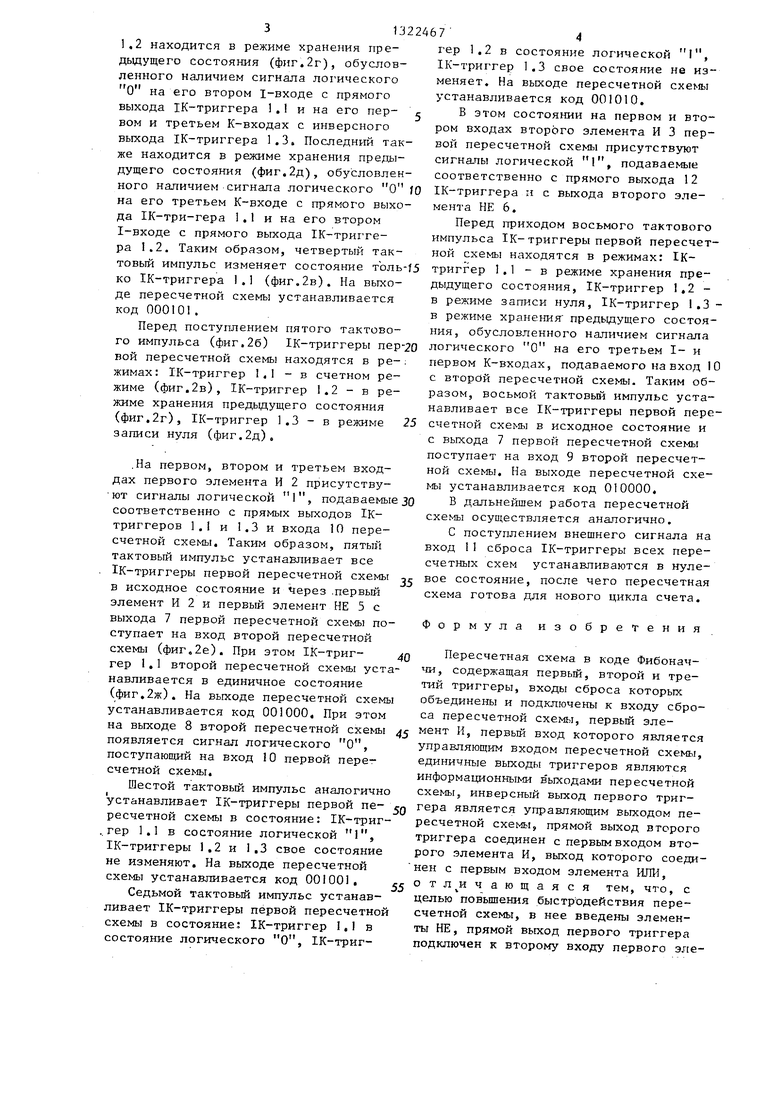

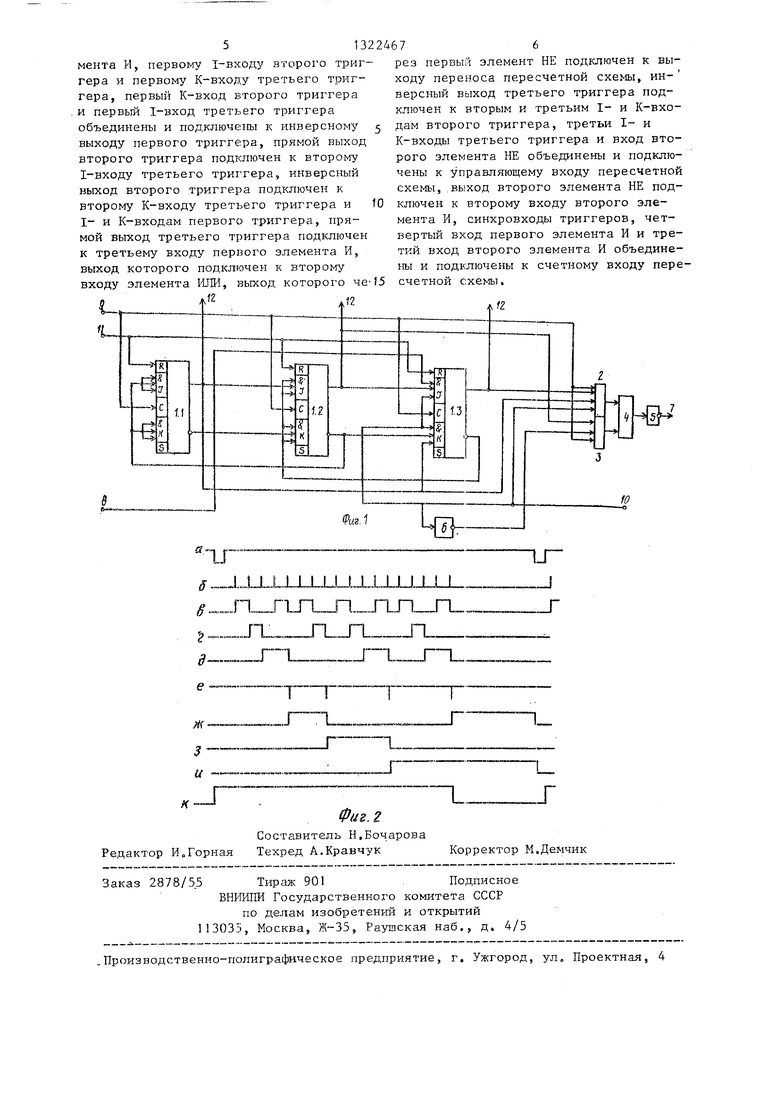

На фиг,1 пре:дстааг1ена блок-схема предлагаемой пе.ресчетной схемы; на фиг.2 - эпюры, характеризующие работу пересчетной схемы,

Пересчетная содерлсит IK- триггеры U1, 1.2 и 1.3, элементы И 2 и 3, элемент ИЛИ 4, элементы НЕ 5 и 6, выход 7 переноса, управляющий выход 8,, счетный вход 9, управляющий вход 10, вход 11 сброса, информационные выходы 12 пересчетной схем1 1.

Пересчетная схема функщ-юнирует следуюпрм образом.

Для увеличения разрядности общей схег-Вз ряд пересчетных схем .объедини- ются следу ощим образом. 7 переноса каждой пересчетной схемы соединяется со счетным входом 9 последующей пересчетной схекы, управляющий выход 8 - с. управляющим входом- 10 предыдущей, входы 11 сброса объединяются „

В исходном состоянии 1К-триггеры 1 пересчетных схем находятся в нулевых состояниях. При нулевом состоянии всех 1К-триггеров пересчетных схем на входе 10 первой пересчетной схемы присутствует сигнал логической 1 с выхода 8 второй пересчетной схемы. При поступлени.и первого тактового импульса на вход 9 первой пересчетной схемь Ж-тригг-ер 1,1 (фиг о 26) устанавливается в состояние логической 1 (фиг,2в), так как на его I- и К-входах присутствуют сигналы логической поступающие с инверсного 1К-триггера 1,2, Этот же импульс записывает нуль в 1К-триггер 1.2 (фиг.Зг) так как на его втором 1-входе присутствует сигнал логического О, подаваемый с прямого выхода ЗК-триггера l.il, а на К-входах присутствуют сигналы логической подаваемые с инверсных выходов 3-К-- триггеров 1о1 и 1.3, 1К триггер 1«3 находится в режиме хранения предьщу- щёго состояния (фиг„2д),, так как на его втором 1 входе и на. третьем К-вхо- де присутствуют сигналы логического О, подаваемые соответственно с прямых выходов ; К-триггерС1В 1«1 и 1,2 о На выходе пересчетной схемы устанавливается код 000001 о

При лс ступлении второго тактового импульса уровни сигналов на 1-й К- входах ЗЬ триггера 1.1 соответствуют состолнию логической 1, поэтому он переключается в противополеж- ное состояние логического О (фиг.2Б)„ Так как в предыдущем такте ТК-триггсф 1„1 находился в состоянии

логической

Ч

1К-триггер 1.3 в сос

тоянии логического О и на 1-вход-ах 1К-триггер а 1.2 присутствовали сигналы логической 1, а на втором К входе сигнал логического О, подаваемый с инверсного выхода 1К-тригге- ра 1,1, 53 1К-триггер 1.2 записывается единица (фиг.Зг). 1К-триггер 1.3 находится в режиме записи нуля (фиг„2д):, так как на его К-входах присутствуют сигналы логической 1 с прямого выхода 1К-триггера 1.1, с инверсного выхода 1К-тригтера 1.2 и с входа 10 пересчетной схемы, а на его втором 1-входе присутствует сигнал логического О с прямого выхода 1К триггера 1.2, На выходе пе- ресчетноЭ схемы устанавливается код 000010.

Перед поступпением третьего тактового импульса на I- и К-входах

1К триггера 1,1 присутствуют сигналы логического О с инверсного хода 1К-триггера 1.2, на К-входах 1К триггера 1.2 - сигналы логической 1, иораваеь1ые с инверсных выходов ,

1К-триггеров 1.1 и 1.3, а на 1-входе 1К триггера 1.2 - сигнал логическо- г о О с прямого выхода К-тригге- ра 1.2, Па 1-входах Т.К-триггера 1,3 присутствуют сигналы логической I,

подаваемые соответственно с инверсного 1К-триггера 10, с прямого 1К-триггера 1.2 и с входа 10 пересчетной схемы, а на третьем К-Еходе 1К-триггера .3 присутствует сих нал логического О с прямого выхода .К-триггера 1.1. Таким образом, IK-триггер 1,1 находится в режиме хранения предьщущего состояния (фиг,2в), IK-TpHri ep 1,2 - в режиме загшси нуля

(фиг,2г |, а 1К-триггер 1,3 - в режиме записи единицы (фиг,2д). Третий тактовый импульс усТана вливает на выходе пересчетной код 000100,

Перед поступлением четвертого тактового ммпульса 1К-триггер 1 находится в режиме записи единицы (фиг,2в), так как на его I-- и К-входах присутствует :;игпал логической I с инверсного вылюда 1К-триггера« 1К-триггер

1,2 находится в режиме хранения нре- дыдущего состояния (фиг.2г), обусловленного наличием сигнала логического О на его втором 1-входе с прямого выхода 1К-триггера 1.1 и на его пер- вом и третьем К-входах с инверсного выхода 1К-триггера 1.3. Последний также находится в режиме хранения предыдущего состояния (фиг,2д), обусловленного наличием сигнала логического О W на его третьем К-входе с прямого выхода 1К-три-гера 1.1 и на его втором 1-входе с прямого выхода 1К-тригге- ра 1.2. Таким образом, четвертый тактовый импульс изменяет состояние тЬль- 5 ко 1К-триггера 1.1 (фиг.2в). На выходе пересчетной схемы устанавливается код 000101.

Перед поступлением пятого тактовогер 1.2 в состояние логической I, 1К-триггер 1.3 свое состояние не изменяет. На выходе пересчетной схемы устанавливается код 001010,

В этом состоянии на первом и втором входах второго элемента И 3 первой пересчетной схемы присутствуют сигналы логической 1, подаваемые соответственно с прямого выхода 12 1К-триггера и с выхода второго элемента НЕ 6.

Перед приходом восьмого тактового импульса IK-триггеры первой пересчет ной схемы находятся в режимах: IK- триггер 1.1 - в режиме хранения предыдущего состояния, 1К-триггер 1.2 - в режиме записи нуля, 1К-триггер 1,3 в режиме хранения предыдущего состоя ния, обусловленного наличием сигнала

го импульса (фиг.2б) 1К-триггеры пер-20 логического О на его третьем I- и

вой пересчетной схемы находятся в режимах: 1К-триггер 1.1 - в счетном режиме (фиг,2в), 1К-триггер 1,2 - в режиме хранения предыдущего состояния (фиг.2г), 1К-триггер 1.3 - в режиме записи нуля (фиг.2д),

.На первом, втором и третьем вход- дах первого элемента И 2 присутству- ют сигналы логической 1, подаваемые соответственно с прямых выходов IK- триггеров 1.1 и 1.3 и входа 10 пересчетной схемы. Таким образом, пятый тактовый импульс устанавливает все 1К-триггеры первой пересчетной схемы в исходное состояние и через .первый элемент И 2 и первый элемент НЕ 5 с выхода 7 первой пересчетной схемы поступает на вход второй пересчетной схемы (фиг,2е). При этом 1К-триг- гер 1,1 второй пересчетной схемы устанавливается в единичное состояние (фиг,2ж). На выходе пересчетной схемы устанавливается код 001000, При этом на выходе 8 второй пересчетной схемы появляется сигнал логического О,

Пересчетная схема в коде Фибоначчи, содержащая первый, второй и третий триггеры, входы сброса которых объединены и подключены к входу сброса пересчетной схемы, первый элемент И, первый вход которого является управляющим входом пересчетной схемы, единичные выходы триггеров являются информационными выходами пересчетной схемы, инверсный выход первого тригпоступающий на вход 10 первой пересчетной схемы.

Шестой тактовый импульс аналогично устанавливает 1К-триггеры первой пе- Q гера является управляющим выходом пересчетной схемы в состояние: 1К-триг- ресчетной схемы, прямой выход второго

триггера соединен с первым входом второго элемента И, выход которого соеди- нен с первым входом элемента ИЛИ, чающаяся тем, что, с целью повышения быстродействия пересчетной схемы, в нее введены элементы НЕ, прямой выход первого триггера подключен к второму входу первого эле.гер 1,1 в состояние логической 1, 1К-триггеры 1,2 и 1,3 свое состояние не изменяют. На выходе пересчетной схемы устанавливается код 001001,

Седьмой тактовый импульс устанавливает 1К-триггеры первой пересчетной схемы в состояние: 1К-триггер 1,1 в состояние логического

О, IK-триггер 1.2 в состояние логической I, 1К-триггер 1.3 свое состояние не изменяет. На выходе пересчетной схемы устанавливается код 001010,

В этом состоянии на первом и втором входах второго элемента И 3 первой пересчетной схемы присутствуют сигналы логической 1, подаваемые соответственно с прямого выхода 12 1К-триггера и с выхода второго элемента НЕ 6.

Перед приходом восьмого тактового импульса IK-триггеры первой пересчетной схемы находятся в режимах: IK- триггер 1.1 - в режиме хранения предыдущего состояния, 1К-триггер 1.2 - в режиме записи нуля, 1К-триггер 1,3 в режиме хранения предыдущего состояния, обусловленного наличием сигнала

первом К-входах, подаваемого на вход 1 с второй пересчетной схемы. Таким образом, восьмой тактовый импульс устанавливает все 1К-триггеры первой пересчетной схемы в исходное состояние и с выхода 7 первой пересчетной схемы поступает на вход 9 второй пересчетной схемы. На выходе пересчетной схемы устанавливается код 010000.

В дальнейшем работа пересчетной схемы ocyo ecтвляeтcя аналогично.

С поступлением внешнего сигнала на вход 11 сброса 1К-триггеры всех пере- счетных схем устанавливаются в нулевое состояние, после чего пересчетная схема готова для нового цикла счета.

Формула изобретения

Пересчетная схема в коде Фибоначчи, содержащая первый, второй и третий триггеры, входы сброса которых объединены и подключены к входу сброса пересчетной схемы, первый элемент И, первый вход которого является управляющим входом пересчетной схемы, единичные выходы триггеров являются информационными выходами пересчетной схемы, инверсный выход первого триггера является управляющим выходом пересчетной схемы, прямой выход второго

мента И, первому 1-входу второго триггера и первому К-входу третьего триггера, первый К-вход второго триггера и первый 1-вход третьего триггера объединены и подключеиз к инверсному выходу первого триггера, прямой выход второго триггера подключен к второму 1-входу третьего триггера, инверсный выход второго триггера подключен к второму К-входу третьего триггера и I- и К-входам первого триггера, прямой выход третьего триггера подключен к третьему входу первого элемента И, выход которого подключен к второму входу элемента ИЛИ, выход которого че Kf2t2

t U.

рез первый элемент HE подключен к выходу переноса пересчетной схемы, ин- версный выход третьего триггера подключен к вторым и третьим I- и К-входам второго триггера, третьи I- и К-входы третьего триггера и вход второго элемента НЕ объединены и подключены к управляющему входу пересчетной схемы, .выход второго элемента НЕ подключен к второму входу второго элемента И, синхровходы триггеров, четвертый вход первого элемента И и третий вход второго элемента И объединены и подключены к счетному входу пересчетной схемы,

г

-g

t.)

f.2

Ь

fi

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный десятичный счетчик | 1989 |

|

SU1661994A1 |

| Устройство для формирования последовательности натуральных чисел в @ -коде Фибоначчи | 1984 |

|

SU1249007A1 |

| Пересчетное устройство в @ -кодах Фибоначчи | 1987 |

|

SU1497743A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Генератор последовательности обобщенных чисел Фибоначчи с произвольными начальными условиями | 1986 |

|

SU1345181A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Генератор последовательности обобщенных @ -чисел фибоначчи с произвольными начальными условиями | 1986 |

|

SU1474627A2 |

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1984 |

|

SU1252779A1 |

Изобретение относится к вычислительной технике и может быть использовано при подсчете импульсов в коде Фибоначчи. Целью изобретения является повышение быстродействия. Для этого устройство содержит 1К-триггеры, элементы И, элементы РШИ и злемен- ты НЕ. Изобретение позволяет сократить объем оборудования, что приводит к повышению надежности. 2 ил. м 4 О5 SJ

Ь

fe.f

Ю

-M

S .Li.ll±l.-LL.Ll.JLLLJJ.Ll

S...™™n.,,

. n: П П П

..J

r

Редактор И„Горная

г. г

Составитель Н.Бочарова Техред А.Кравчук

Корректор М.Демчик

Заказ 2878/55 Тиралс 901 . Подписное ВШ ШПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, , Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Двоичный счетчик с последовательным переносом | 1976 |

|

SU577682A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1985-04-29—Подача