4

О

ю

Изобретение сл-носится к вычислн- |тельной технике и предназначено для построения быстродействующих арифметических устройств.

Цель изобретения - повышение быстродействия.

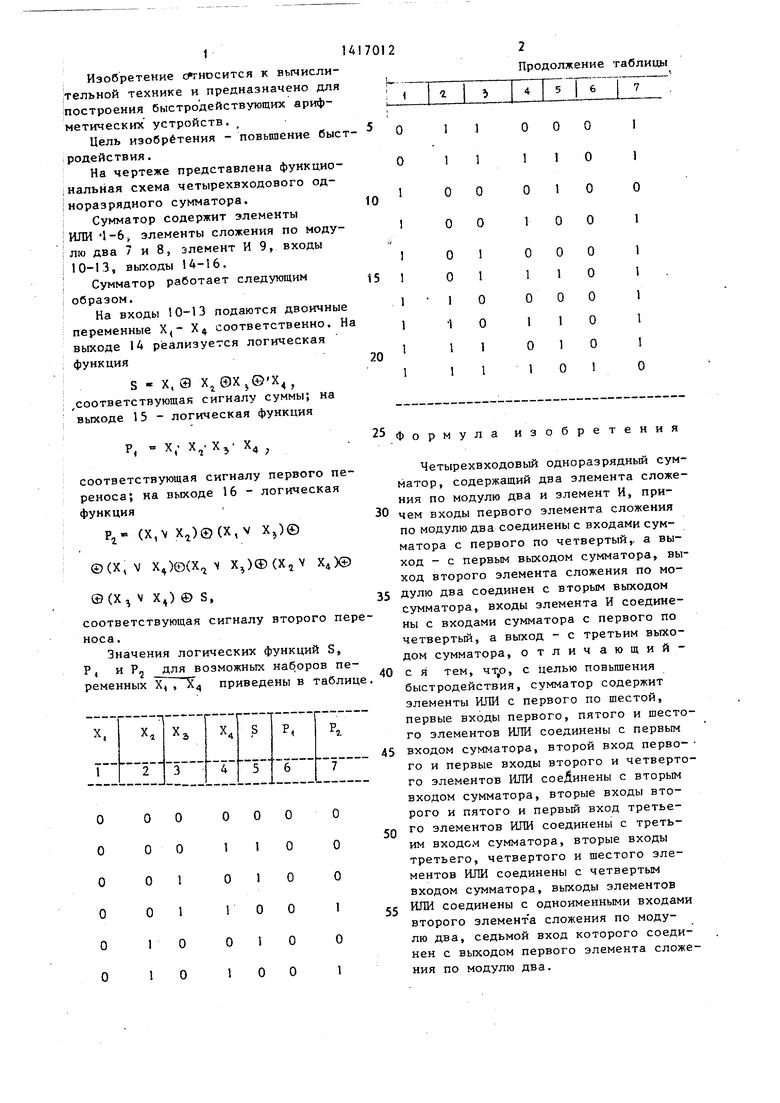

На чертеже представлена функцио- ;нальная схема четырехвходового од- нораэрядного сумматора. I Сумматор содержит элементы ИЛИ 1 -61 элементы сложения по моду- ; лю два 7 и 8, элемент И 9, входы 10-13, выходы 14-16. Сумматор работает следующим образом.

На входы 10-13 подаются двоичные переменные X,- Х4 соответственно. На выходе 14 реализуется логическая функция

S - Х,0 соответствующая сигналу суммы; на выходе 15 - логическая функция

Р, Х- X,. X,- Х

соответствующая сигналу первого переноса; на выходе 16 - логическая функция

Р,« (Х, Х,)©(Х, V Xj)© ©(X,V Х)©(Х, N X,)®(X,jV Х)©

® (X, V Х) © S,

соответствующая сигналу второго переноса.

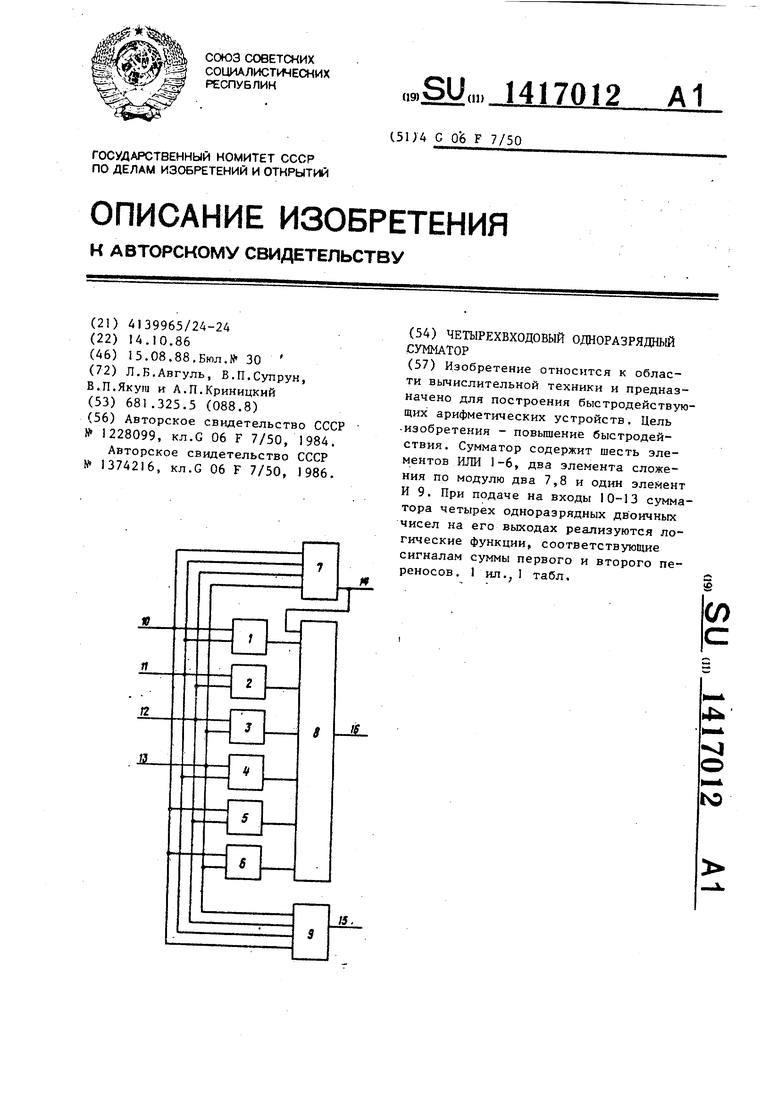

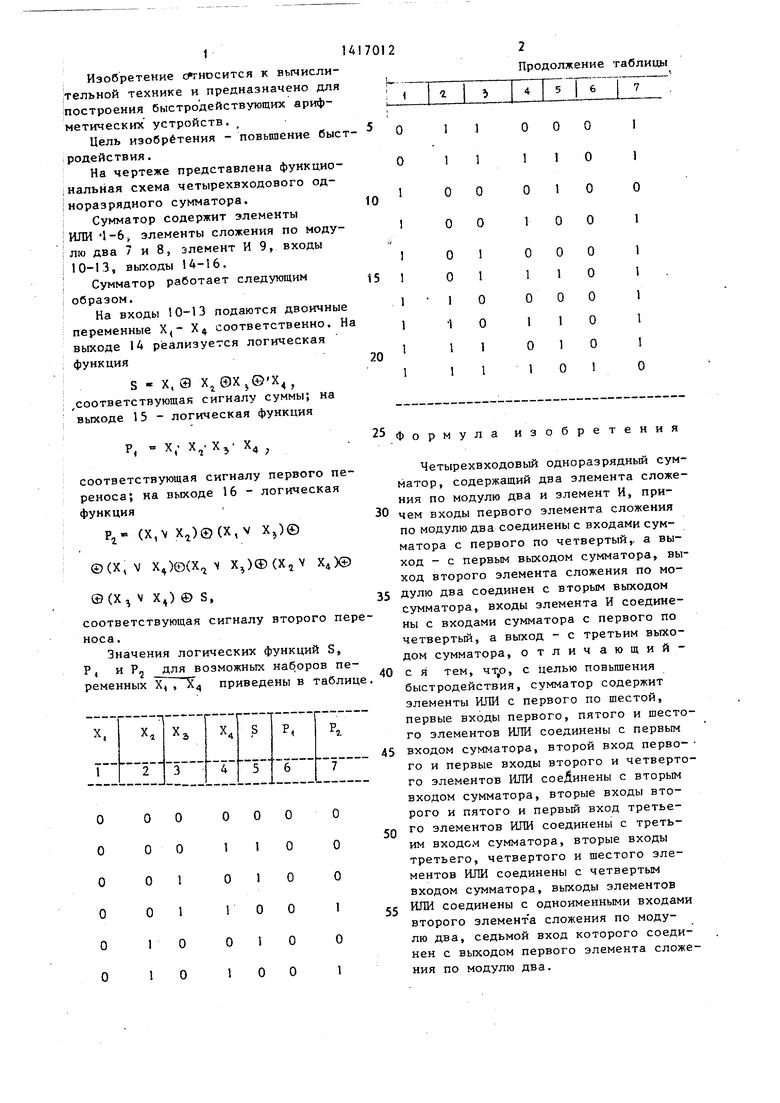

Значения логических функций S, Р, и Р, для возможных наборов переменных приведены в таблице

25

Формула изобретения

0

5

0

0

5

Четырехвходовый одноразрядный сумматор, содержащий два элемента сложения по модулю два и элемент И, причем входы первого элемента сложения по модулю два соединены с входами сумматора с первого по четвертый,, а выход - с первым выходом сумматора, выход второго элемента сложения по модулю два соединен с вторым выходом сумматора, входы элемента И соединены с входами сумматора с первого по четвертый, а выход - с третьим выходом сумматора, отличающий- с я тем, чт,о, с целью повышения быстродействия, сумматор содержит элементы ИЛИ с первого по шестой, первые входы первого, пятого и шестого элементов ИЛИ соединены с первым 5 входом сумматора, второй вход первого и первые входы второго и четвертого элементов ИЛИ соеДинены с вторым входом сумматора, вторые входы второго и пятого и первый вход третьего элементов ИЛИ соединены с третьим входом сумматора, вторые входы третьего, четвертого и шестого элементов ИЛИ соединены с четвертым входом сумматора, выходы элементов ИЛИ соединены с одноименными входами второго элемент а сложения по модулю два, седьмой вход которого соединен с выходом первого элемента сложения по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1374216A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1571578A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1575172A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1658146A1 |

| Четырехвходовый одноразрядный сумматор | 1987 |

|

SU1479928A1 |

| Многовходовой одноразрядный сумматор | 1988 |

|

SU1730620A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797111A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1587486A1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

Изобретение относится к области вычислительной техники и предназначено для построения быстродействующих арифметических устройств. Цель -изобретения - повышение быстродействия. Сумматор содержит шесть элементов ИЛИ 1-6, два элемента сложения по модулю два 7,8 и один элемент И 9. При подаче на входы 10-13 сумматора четырех одноразрядных двоичных чисел на его выходах реализуются логические функции, соответствующие сигналам суммы первого и второго переносов. 1 ил., I табл.

| Четырехвходовый одноразрядный сумматор | 1984 |

|

SU1228099A1 |

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1374216A1 |

Авторы

Даты

1988-08-15—Публикация

1986-10-14—Подача