(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1417012A1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1575172A1 |

| Четырехвходовый одноразрядный сумматор | 1984 |

|

SU1228099A1 |

| Многовходовой одноразрядный сумматор | 1988 |

|

SU1730620A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| Четырехвходовой одноразрядный сумматор | 1989 |

|

SU1683007A1 |

| Четырехвходовый одноразрядный сумматор | 1987 |

|

SU1479928A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

Изобретение относится к области вычислительной техники и предназначено для построения многооперандных быстродействующих арифметических устройств. Цель изобретения - упрощение сумматора. В состав устройства входят три элемента сложения по модулю два 1,2,3, два элемента И 4,5, один элемент РАВНОЗНАЧНОСТЬ 7, один элемент НЕ 6, четьфе входа 8-11, выход 12 суммы и два выхода 13, 14 переноса. При подаче на информационные входы двоичных сигналов на выходе устройства реализуются логические функции, соответствующие сигналам суммы и переноса в старшие разряды. 1 ил., 1 табл.

со м ьо

. 113

Изобретение относится к вычислительной технике.и предназначено для построения многооперандных быстродействующих арифметических устройств,

Цель лзобретения - упрощение четы- рехвходового одноразрядного сумматора.

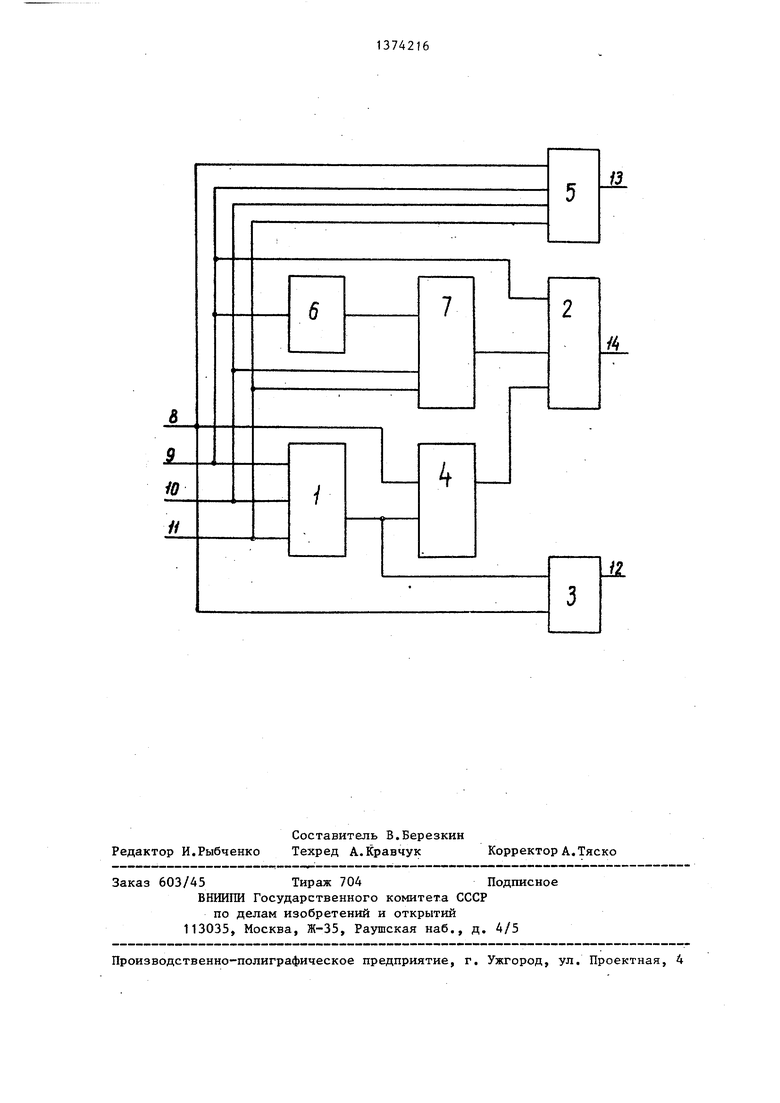

На чертеже представлена функциональная схема четырехвходового одно- разрядного сумматора.

Сумматор содержит элементы 1-3 сложения по модулю два, элементы И 4, 5, элемент НЕ 6, элемент РАВНОЗНАЧНОСТЬ 7, входы 8-11, выход 12 сум- мы, выходы 13 и 14 старщего и младшего переносов.

Сумматор работает следующим образом.

На входы 8-11 подаются двоичные

переменные х

На выходе 12

реализуется логическая функция

X.

X.

3

на выч 3 4 Соответствующая сигналу суммы,

ходе 13 - логическая функция

ц

соответствующая сигналу старшего переноса; на выходе 14 - логическая функция

© R(X2,X j,X4)®(x,. (x,j®Xj® ©X,)),

соответствующая сигналу младшего переноса.

Здесь RGci,Xj,x) V ,х функция равнозначности.

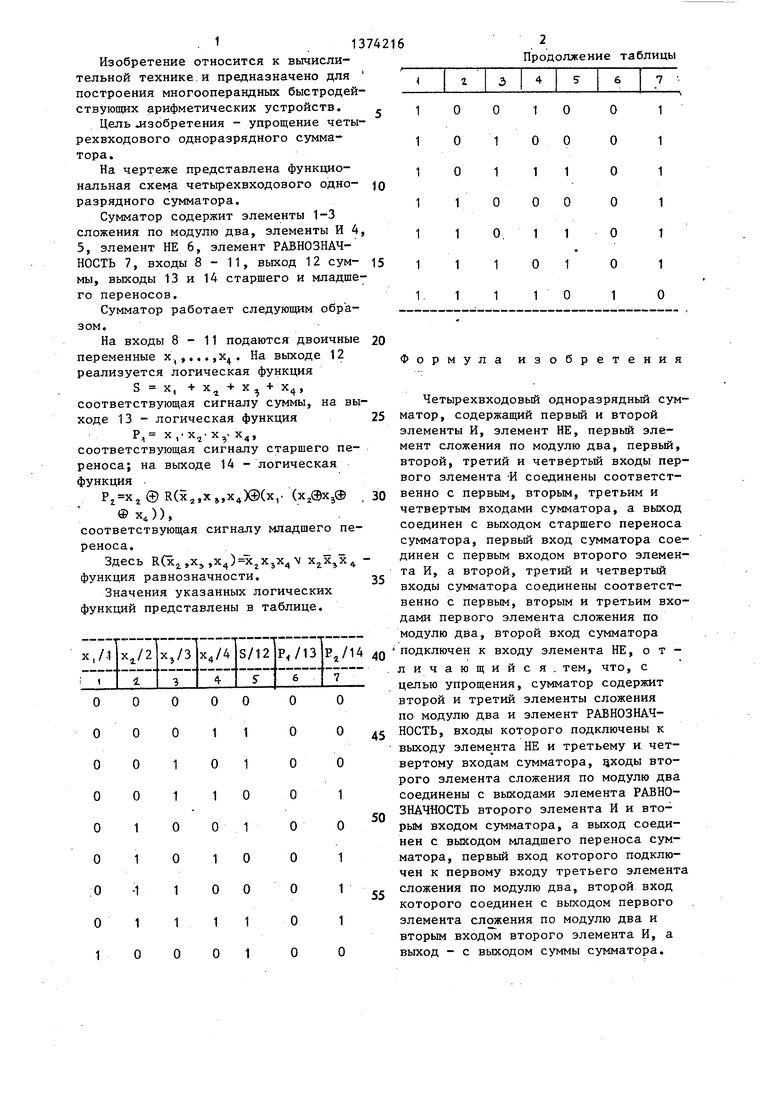

Значения указанных логических функций представлены в таблице.

О О

1 1

Продолжение таблицы

5

0

5

0

5

0

5

Формула изобретения

Четырехвходовый одноразрядный сумматор, содержащий первый и второй элементы И, элемент НЕ, первый элемент сложения по модулю два, первый, второй, третий и четвертый входы первого элемента -И соединены соответственно с первым, вторым, третьим и четвертым входами сумматора, а выход соединен с выходом старщего переноса сумматора, первый вход сумматора соединен с первым входом второго элемента И, а второй, третий и четвертый входы сумматора соединены соответственно с первым, вторым и третьим входами первого элемента сложения по модулю два, второй вход сумматора подключен к входу элемента НЕ, отличающийся, тем, что, с целью упрощения, сумматор содержит второй и третий элементы сложения по модулю два и элемент РАВНОЗНАЧНОСТЬ, входы которого подключены к выходу элеме нта НЕ и третьему и четвертому входам сумматора, цходы второго элемента сложения по модулю два соединены с выходами элемента РАВНОЗНАЧНОСТЬ второго элемента И и вторым входом сумматора, а выход соединен с выходом мпадшего переноса сумматора, первьш вход которого подключен к первому входу третьего элемента сложения по модулю два, второй вход которого соединен с выходом первого элемента сложения по модулю два и вторым входом второго элемента И, а выход - с выходом суммы сумматора.

iL 11

/4

| Устройство для параллельного счета количества единиц(нулей)в двоичном числе | 1972 |

|

SU450160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логическое проектирование.БИС/ /Под ред | |||

| В.А.Мищенко | |||

| М.: Радио и связь, 1984, с.55-56, рис,4.3. | |||

Авторы

Даты

1988-02-15—Публикация

1986-07-30—Подача