«f

ЙЕ &

J2

ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1833860A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1658146A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| Устройство для выделения симметрических булевых функций | 1991 |

|

SU1833859A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1290290A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1730621A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1765820A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1748149A1 |

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметических устройств ЭВМ и спецпроцессоров. Цель изобретения - расширение области применения за счет увеличения количества входов с четырех до шести. Цель достигается тем, что устройство содержит два элемента СЛОЖЕНИЕ ПО МОДУЛЮ 21, 2,пороговый элемент 4 с порогом 2, пороговый элемент 5 с порогом 4 и элемент И 3,имеет шесть входов 6-11 и три выхода 12-14. На входы 6-11 подаются двоичные переменные xi, ха, хз, Х4, xs. xe, а на выходах 12-14 реализуются логические функции f0, fi, f2, соответствующие сигналам суммы младшего и старшего переносов. 1 ил., 1 табл.

№

со о о

N)

о

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметических устройств ЭВМ и спецпроцессоров.

Цель изобретения - расширение области применения за счет увеличения количества входов с четырех до шести.

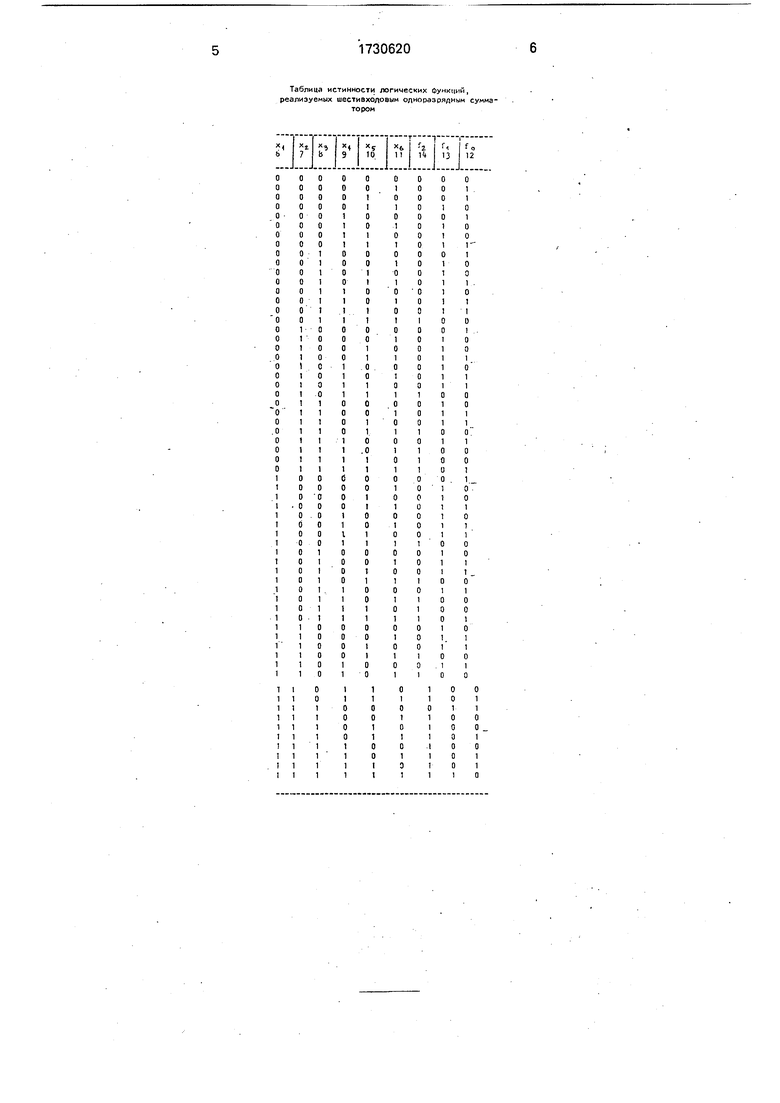

На чертеже представлена схема шести- входового одноразрядного сумматора.

Сумматор содержит два элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 1 и 2, элемент И 3, пороговый элемент 4 с порогом 2, пороговый элемент 5 с порогом 4, шесть входов 6-11, три выхода 12, 13 и 14.

Шестивходовый одноразрядный сумматор работает следующим образом.

На входы 6-11 подаются двоичные переменные Х1-Х6 соответственно, на выходах 12, 13 и 14 реализуются логические функции fo, fi и f2 соответственно, составляющие двоичный код числа логических единиц, содержащихся во множестве входных сигналов {Х1, Х2, ХЗ, Х4, Х5, Хб}

N X xj 4f2 + 2fI + fo.

j 1

Логические функции f0, fi и f2 реализуются сумматором согласно следующим выражениям:

г Х2 ± хз + Х4 -ь ХБ -t хе;

ft Х1Х2ХЗХ4Х5Х6 F2(X1, Х2, ХЗ, Х4, Х5, ХбУ+ + F4(X1, Х2, ХЗ, Х4, Х5, Хб); f2 F4(X1, Х2, ХЗ, Х4, Х5, Хб),

где функции пороговых элементов 4 и 5 с порогом k (k 2,4) определяются как

i если 2 XJ - k J 1

Fk(xi, X2Щ

О, если 2 XJ к- j i

0

0

5

0

5

0

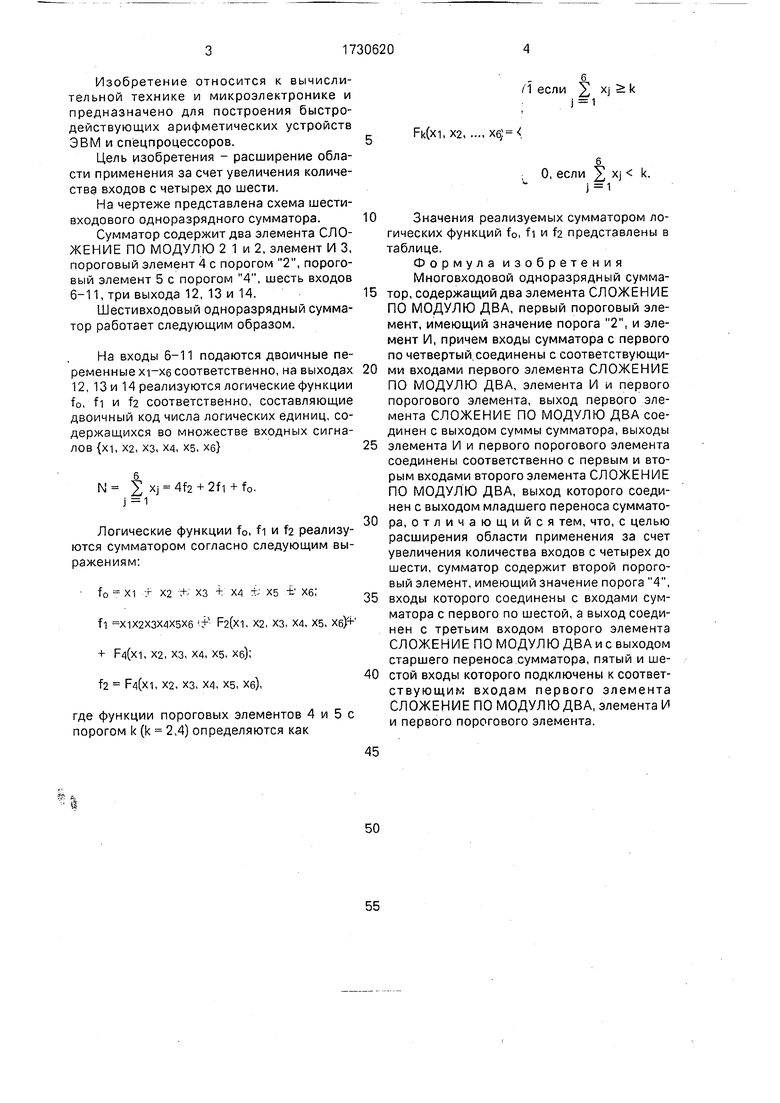

Значения реализуемых сумматором логических функций f0, fi и f2 представлены в таблице.

Формула изобретения Многовходовой одноразрядный сумма- 5 тор, содержащий два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, первый пороговый элемент, имеющий значение порога 2, и элемент И, причем входы сумматора с первого по четвертый соединены с соответствующими входами первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, элемента И и первого порогового элемента, выход первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с выходом суммы сумматора, выходы элемента И и первого порогового элемента соединены соответственно с первым и вторым входами второго элемента СЛ ОЖЕ Н И Е ПО МОДУЛЮ ДВА, выход которого соединен с выходом младшего переноса сумматора, отличающийся тем, что, с целью расширения области применения за счет увеличения количества входов с четырех до шести, сумматор содержит второй пороговый элемент, имеющий значение порога 4, входы которого соединены с входами сумматора с первого по шестой, а выход соединен с третьим входом второго элемента СЛОЖЕНИЕ ПО МОДУЛ Ю ДВА и с выходом старшего переноса сумматора, пятый и шестой входы которого подключены к соответствующим входам первого элемента СЛОЖЕНИЕ ПО МОДУЛ Ю ДВА, элемента И и первого порогового элемента.

Таблица истинности логических Функций, реализуемых шестивходовым одноразрядным сумматором

| Патент США № 3535502, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1374216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1988-09-22—Подача