тателя по модупю Р( подключен к информационным входам третьего и чет-i вертого блоков элементов И -и групгпл,а выход суммы сумматора-вычи да теля по модулю - к информационным вводам пятого, шестого и седьмого блоков элементов И i -и группы, выходы четвертого и пятого блоков элементов И i-и группы подключены соответственно ко входу четвертого и первому входу пятого регистров 4-й группы, выход седьмого блока элементов И -и группы подключен ко. второму входу второго регистра 1 -и группы, выход четвертого регистра 1-Й группы подключен к информационным входам восьмого и девятого блоков элементов И i -и группы, выходы которых подключены соответст- венноко входу шестого к втрррму входу пятого регистров ч -и группы, выход пятого регистра | -и группы подключен ко входу седьмого регистра -и группы, выход шестого регистра 1 -и группы подключен к информа- , цйонным входам десятого и рдиннадцатого блоков элементов И f-и группы, выход седьмого регистра ч-и группы подключен к информационным входам двенадцатого и тринадцатого блоков элементов И 1 -и группы, выхол дал-десятого и тринадцатого блоков элементов .И t -и группы подключены соответственно ко второму и третьему вхрДс1М третьего регистра -и группы, выход одиннадцатого блока элементов И i -и группу подключен к третьему входу пятого регистра i-й группы, выходы третьего и двенадцатого блоков элементов И I -и группы подключены ко входам восьмого регистра i-и группы, выход шестого блока элементов И i-и группы подключен к первому входу девятого регистраi -и группы, выход восьмого и второй вход девятого регистров ( -и группы по 1ключены соответственно ко входу -го разряда множимого умножителя и к выходу i-го разряда умножителя, выход .девятого (регистра -и группы подключен к -му входу преобразователя модулярного кода в двоичный код, первый выход которого подключен ко входу второго регистра, а второй, третий и четвертый выходы - ко входам соответствующих групп разрядов первого выходного регистра, выходы второго и третьего регистров подключены к сортветствуввдим группам адресных входов блока постоянной памяти выход. , которого подключен к Информационному входу третьего регистра и через второй блок элементов И - к информационному входу первого регистра, установочные входы первого и Гвторого регистров являются ус- ано вочными входами устройства, выход

первого блока элементов И является выходом порядка преобразуемых чисел устройства, управляющие входы первого и второго блоков элементов И, а также объединенные управляющие входы одноименных блоков элементов И четырех групп подключены к соответствующим тактовым входам устройства.

2.У-СТРОЙСТВО TIO п. 1, о т л и чающееся тем, что преобразователь двоичного кода, в модулярный код состоит из перЪого, второго и третьего блоков постоянной памяти и четырех суммирукадих блоков, в каждом из которых содержится пять регистров и два сумматора, причем адресные входыk-го ( Ц 1, 2, 3) блока постоянной памяти являются первым, вторым и k + 2) -м входами, преобразователя двоичного кода в модулярный код,t -я группа выходов k-ro блока постоянной памяти подключена ко входу регистра в i -и суммирующем блоке, выходы первого И второго регистров.каждого суммируюдего блока подключены ко входам соо.тветствующего первого сумматора, выход которого подключен ко входу четвертого регистра этого суммируюего блока, выход третьего регистра в суммирующем блоке подключен ко входу пятого регистра, выход которого и выход четвертого регистра того же суммирующего блока подключены ко входам соответствуняцего. второго сумматора, выходы вторьрс сумматоров С5 м рующих блоков явля-, ются выходами преобразователя двоичного кода в модулярный код,

3.Устройство по п. 1, о т л ич а ю щ е е с я тем, что преобразователь модулярного кода в двоичный код состоит из девяти сумматоров, двадцати одного элемента задержки и блока постоянной памяти, причем первые входы первого, второго и третьего сумматоров являются соответственно первым, вторым и третьим входами преобразователя Модулярного кода в двоичный код, объединенные вторые входы первого, второго и третьего сумматоров явяются четвертым входом преобразоателя модулярного кода в двоичный код, выход первого сумматора через оследовательно соединенные первый, торой, третий и четвертый элементы задержки подключен к первому входу етвертого сумматора, выход второго сумматора через последовательно соединенные пятый, шестой,,седьмой восьмой элементы задержки подлслючен к первому входу пятого сумматора, выходы четвертого и пятого умматоров соответственно через евятый и десятый элементы задержки подключены к адресным входам блока

постоянной памяти, выход третьего сумматора через одиннадцатый элемент задержки подключен к первому входу шестого сумматора, второй вход шестого сумматора подключен к выходу шестого элемента задержки, а выход шестого сумматора через двенадцатый элемент задержки подключен к первому входу седьмого сумматора, второй вход которого и первый вход восьмого сумматора подключены к выходу вта рого элемента задержки, второй вход восьмого сумматора подключен к выходу седьмого элемента задержки, выходы седьмого и восьмого сумматоров через тринадцатый и четырнадцатый элементы задержки подключены ко входе1м девятого сумматора, выход которого через пятнадцатый элемент

задержки подключен ко вторым входам четвертого и пятого сумматоров и входу шестнадцатого элемента задержки, вход семнадцатого элемента Зс1дёржки подключен ко вторым входам первого, второго и третьего сумматоров, а выход семнадцатого элемента задержки через последовательно соединенные восемнадцатый, девятнадцатый и двадцатый элементы задержки подключён ко входу двадцать первого элемента задержки, первый и второй выходы блока постоянной памяти, а также выходы шестнадцатого и двадцать первого элементов задержки являются соответственно первым, вторым, третьим и четвертым выходами преобразователя Iмодулярного кода в двоичный код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для вычисления дискретного преобразования Фурье в модулярной системе счисления | 1988 |

|

SU1633423A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1732353A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯРНОМ КОДЕ | 1991 |

|

RU2015620C1 |

1. АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ , содержащее восемь входных и восемь вькодных регистров, семь выходных блоков элементов и,, i сумматрры-вычитатели по модулю Р{ 2 (j 1, 2, 3, 4 - номер сумматора-вычитателя, Р - целое положительное число), умножитель, причем информационные входы входных регистров являются входами отсчетов входного сигнала устройства, вход множителя умножителя является входом поворачивсшщегб множителя устройства, выход j -го ( j ) выходного регистра подключен ко входу (j+1)-го выходного регистра и к информационному входу -го выходного блока элементов И, выходы всех выходных блоков элементов И и восьмого выходного регистра являются информационными выходакш ус ройства, управляшций вход укоюжителя, а также . соединенные между собою управлякхцие входы выходных блоков элементов И «подключены к соответствующим тактовым входам устройства, отличающееся тем, что, с целью повышения быстродействия и повышения точности устройства, оно содержит преобразователь дбоичного кода в модулярный код, преобразователь модулярного кода в двоичный код, первый, второй и третий регистры, первый и второй блоки элементов И, блок (постоянной памяти, а также регистры и блоки элементов И, объединенные в четыре группы, каждая из которых состоит из девяти регистров и тринадцати блоков элементов И, причем, выход j -го (} 1-7) вход;ного регистра подключен к дополни тельному информационному входу (j+l)-ro входного регистра, выход первого регистра подключен к информационному входу первого блока элементов И, к первому входу преобразователя двоичного кода в моду(Л лярный код, выход знакового разряда восьмого входного регистра подс ключен ко второму; входу преобразо-; вателя двоичного кода в модулярный; код, выходы разрядов с bf nobg + I + Ье4,- 1 (е О, 1, 2j bo , bi., bj , 03 - натуральные числа такие , что Ьо+Ъ +Ь2 +b-j г + г-г + г,- - 1 Ъ-) 2) восьмого входного регистра, образующие его

Изобретение относится к автоматике и вычислительной технике для использования в быстродействующих процессорах быстрого преобразования Фурье с основанием 4, ориентированных на обработку сигналов невысокой разрядности (12-24 бит.

Большинство известных устройств для быстрого преобразования Фурье . выполняют различные алгоритмы с основанием 2, которые характеризуются максимёшьным количеством последовательных шагов, а следовательно, и умножений чисел. : Использование алгоритмов быстрого преобразования Фурье с основанием 4 позволяет существенно уменьшить общее число умножений. Кроме того, алгоритма с основанием 4 ртличаются более высокой точностью t4

Недостатком известных быстродействующих процессоров быстрого преобразования Фурье с основанием 4 является сложность их арифметииеских устройств.

Наиболее близким к изобретению является арифметическое устройство, реализующее алгоритм быстрого преоб разования Фурье с основанием 4 в модулярных системах счисления и co.t держащее восемь входных и восемь выходных регистров, семь выходных блоков элементов И, четыре сумматора-вычитателя по модулю PJ 2 ((, 1,2, 3,4- номер сумматора-вычитателя - целое положительное число) , умножитель 2 .

Недостатками известного устройства являются низкая точность, обусловленная большой погрешностью

используемой процедуры масштабирогэ вания, и малое быстродействие. Цель изобретения - повышение быстродействия и повышение точности 5 устройства.

Поставленная цель достигается тем, что арифметическое устройство для процессора быстрого преобразоваг НИН Фурье, содержащее восемь вход-,

0 ных и восемь выходных регистров, семь выходных блоков элементов И, четыре сумматора-вычитателя по мр-т дулю PC, ( ; 1, 2, 3, 4 - номер сумматора-вычитателя; Pj - целое

5 положительное число), умножитель, причем информационные входы входных регистров являются входами отсчетов входного сигнала устройства, вход множителя-умножителя является.входом

л поворачиваквдего множителя устройртва, выход i -ro(i 1-7) выходного регистра подключен ко входу (j+ 1)-го выходного регистра и к информационному входу J-го выходного блока

с элементов И, выходы всех выходных

блоков элементов И и восьмого вы-, кодного регистра являются информационными выходами устройства, управляющий вход умножителя, а также соединенные между собою управляющие

0 входы выходных блоков элементов И подключены к соответствующим тактовым входам устройства, содержит преобразователь двоичного кода в модулярной код, преобразователь

5 модулярного кода в двоичный код, первый, второй и третий регистры, первый, второй блоки элементов И, блок постоянной памяти, а также |регист Ж и блоки элементов И, объединенные в четыре группы, каждая из которых состоит из девяти регистров и тринадцати блоков элементов И, причем выход j -го j 1-7) входного регистра подключен к дополнительному информационному входу 1)-го входного регистра, выход первого регистра подключен к информацис нному входу первого блока элементов И и к первому входу преобразователя двоичного кода в модулярный код, выход знакового разряда восьмого входного регистра подключен ко второму входу преобразователя двоичного кода в модуI лярный код, вь1ходы разрядов с bg по Ье + Ье4г к В о, 1, 2; Ьо , Ь Ъ , Ь - натуральные числа такие, что Ьй+Ц+Ь7+Ь г + 2 + Г +Г4 , . Ьр l,) восьмого входного регис ра, образующие его С + 1)-й параллельный выход, подключены к (С +3)входу преобразователя двоичного кода в модулярный код, (-и ( 1-4 выход преобразователя двоичного кода в модулярный код подключен к информационным входам первого и второго блоков элементов И { -и группы, выходы которых подключены соответственно ко входу первого и и первому входу второго регистров i-и группы, выход первого регистра i-и группы подключен к первому вход третьего регистра i -и группы, выход которого, а также выход второго регистра I -и группы подключены ко входам соответственно сумматора-вычитателя по модулю Р,, выход разнос ти сумматора-вычитателя по модулю Р подключен к информационным входам третьего и четвертого блоков элементов И f -и группы, а выход суммы сумматора-вычитателя по модулю Р - к информационным входам пятого, шестого и седьмого блоков элементов И i -и группы, выходы четвертого и пятого блоков элементов И { -и группы подключены соответстве но ко входу четвертого и первому входу пятого регистров ч -и группы, выход се;1:1Ы юго блока элементов И 1-й группи подключен, ко второму вхо ду второго регистра i -и группы, выход четвертогорегистра ч -И группы подключен к информационным входам восылзго и девятого блоков элементов И -и группы, выходы кото,рых подключены соответственно ко входу шестого и второму входу пятого регистров 1 й группы, выход пятого регистра i -Л группы подключен ко входу седьмого регистра {-и группы, выход-шестого регистра }-й группы под| лючен к информацион ным входам десятого, и одиннадцатого блоков элементов Ki -и группы, выхо седьмого регистра i-и группы подключен к информационным входам две надцатого и тринадцатого блоков элементов И j-и группы, выходы де- сятого и тринадцатого блоков элементов И 4-и группы подключены соответственно ко второму и третьему входам третьего регистра и-и группы, выход одиннадцатого блока элементов И i -и группы подключен, к третьему входу пятого регистра i -и :группь, выходы третьего и двенадцатого блоков элементов И 4-и группы подключены ко входам восьмого регистра i -и группы, выход шестого блока элементов И i -и .группы подключен к первому входу девятого регистра i -и группы, выход восьмого и рторой вход девятого регистров i-и группы подключены соответственно ко входу i -го разряда, множимого умножителя и к выходу 1 -го разряда умножителя, выход девятого регистра f -и группы подключен к i -му входу преобразователя модулярного кода в двоичный код, первый выход которого подключен ко входу второго регистра, а второй, третий и четвертый выходы - ко входам соответствующих групп разрядов первого выходного регистра, выходы второго и третьего регистров подключены к соответствующим группам адресных входов блока постоянной памяти, выход которого подключен к информационному входу третьего регистра и через второй блок элементов И - к информационному входх первого регистра, установочные входы первого и второго регистров являются установочными входами устройстваi выход первого блока элементов И является выходом порядка преобразуе- мых чисел устройства, управляющие входы первого и второго блоков элеК«ентов И, а также соединенные управляющие входы одноименных блоков элементов И четырех групп подключены к соответствующим тактовым входам устройства. Кроме того, преобразователь двоичного кода в модулярный код состоит из первого, второго и третьего блоков постоянной памяти и четырех .суммирующих блоков, в каждом из которых содержится пять регистров и два сумматора, причем адресные входы k-ro (k 1,2,3) блока постоянной памяти являются первым, BTOIHJIM и (k + 2)-м входами преобразователя цвоичного кода в модулярный код, i-я группа выходов k-ro блока постоянной памяти подключена ко входу k-ro регистра в i -м суммирующем, блоке, выходы первого и второго регистров каждого суммирующего блока подключены ко входам соответствующего первого сумматора, выход которого подключен ко входу четвертого регистра в этом суммирующем блр.ке.

ВЫХОД третьего регистра в суммирующем блоке подключен ко входу пятого регистра, выход которого и выход четвертого регистра в том же суммирующем блоке подключены ко входам соответствующего второго сумматора выходы вторых сумматоров суммирующих блоков являются выходами преобразователя двоичного кода в модулярный код.

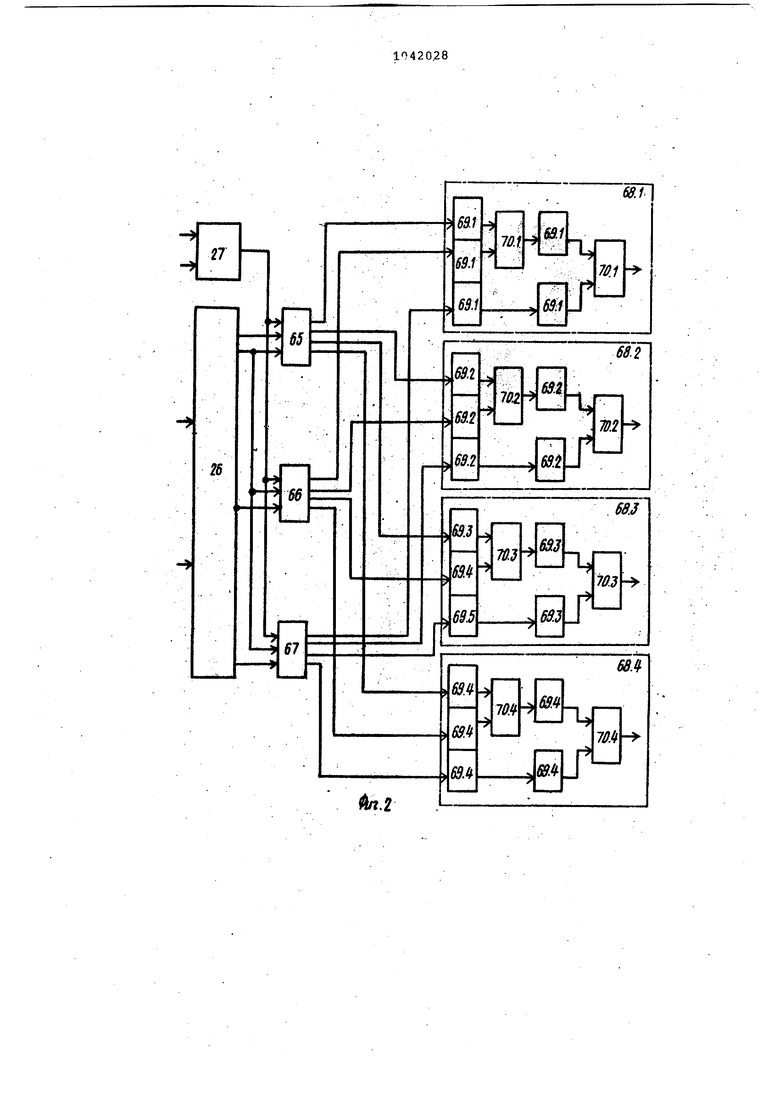

При этом преобразователь модулярного кода в двоичный код coctoит из девяти сумматоров, двадцати одного элемента задержки и блока постоянной памяти, причем первые входы первого, второго и третьего сумматоров являются соответственно первым, вторым и третьим входами преобразователя модулярного кода в двоичный код, соединенные вторые входы первого, второго и третьего сумматоров являются четвертым входо преобразователя модулярного .кода в двоичный код, выход первого сумматора через последовательно соединенные первый, второй, третий и четвертый элементы задержки подключен к первому входу четвертого сумматора, выход второго сумматора через последовательно соединенные пятый, шестой, седьмой и восьмой элементы задержки подключен к первому входу пятого сумматора, выходы четвертого и пятого сумматоров соответственно через девятый и десятый элементы задержки подключены к адресным входам блока постоянной памяти, выход третьего сумматора через одиннадцатый лемент задержки подключен к первому входу шестого сумматора, второй вход шестого сумматора подключен к выходу шестого элемента задержки, а выход шестого сумматора через двенадцатый элемент задержки ..под ключей к первому входу седьмого сумматора, второй вход которого вместе с первым входом восьмого сумматора подключен к выходу второго элемента задержки, второй вход восьмого сумматора подключен к выходу седьмогЬ элемента задержки, выходы седьмого и восьмого сумматоров через тринадцатый и четырнадцатый элементы задержки подключены к входам девятого сумматора, выход которого через пятнадцатый элемент задержки подключен ко вторым входам четвертого и пятого сумматоров и входу шестнадцатого элемента задержки, вход семнадцатого элемента задержки подключен ко вто{%1м входам первого, второго и третьего сумматоров, а выход семнадцатого элемента задержки через последовательно соединелные восемнадцатый, девятнадцатый и двадцатый элементы задержки подключен ко входу двадцать первого элемента задержки, первый и второй

выходы бло.ка постоянвой памяти, а также выходы шестнадцатого и двадцать первого элементов задержки являются соответственно первым, вторым, третьим и четвертым выходами -преобраэователя модулярного кода в двоичный код.

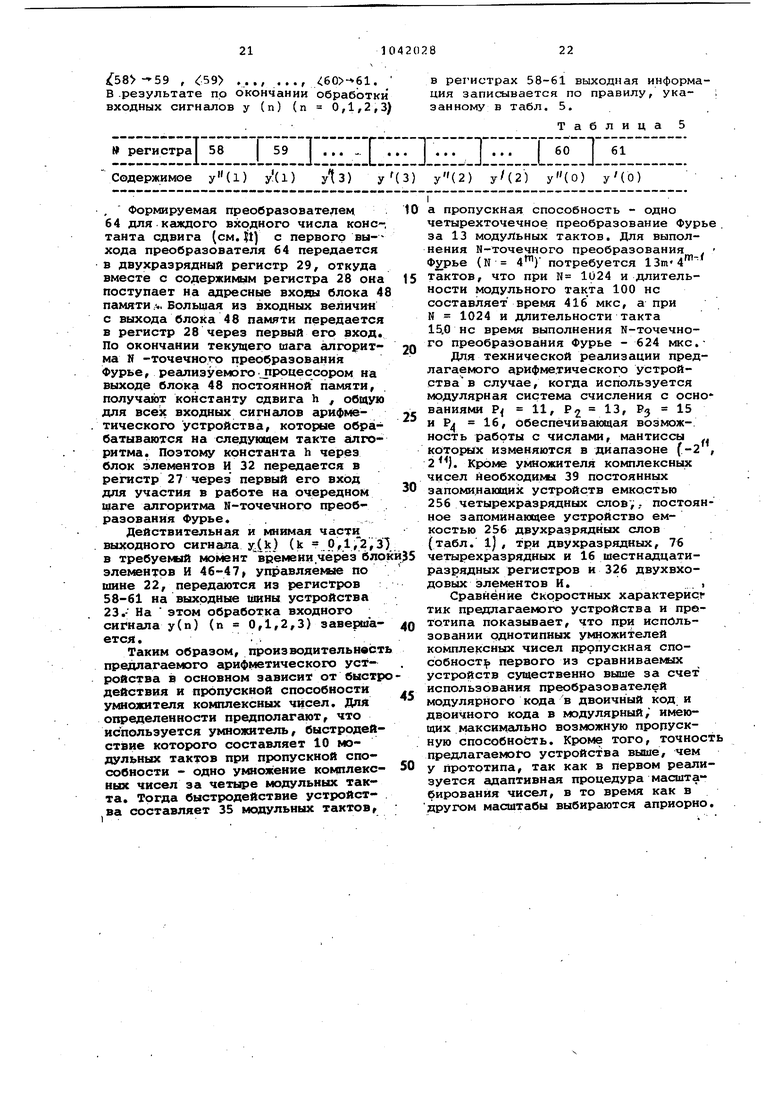

На фиг. 1 представлена структурная схема предлагаемого арифметического устройства для процессора быстрого преобразования Фурье; на фиг. 2 и 3 - соответственно структурные схекы преобразователя двоичного кода в модулярный код и преобразователя модулярного кода в ДВОИЧНЫЙ код.

На фиг. 1, 2 и 3 приняты обозначения: информационные входы 1, ус. тановочный вход 2, тактовый вход 3,

:Выход 4 порядка преобразуемых чиQ сел, тактовые входы 5-17, информа|ционные входы 18 поворачивающего 1множителя, тактовый вход 19, установочный вход 20, тактовые входы 21 и 22, информационные выходы 23, входные регистры 24-26, предназна ченные для хранения мантисс отсчетов входного сигнала, двухразрядные регистр 27 константы сдвига, регистр 28 текущего значения константы сдвига и регистр 29, преобразователь 30 двоичного кода в модулярный код, блоки двухвходовых элементов И 31, 32, ЗЗ; -45i(i 1-4 и 46-47 блок 48 постоянной памяти, регистры 49 -57 ( ( 1-4), выходные регистры 58-61 устройства, предназначенные для хранения мантисс отсчетов выходного сигнала, сумматор-вычитатель 62 j по 1-му модулю Р используемой непозиционной системы счисления. ( 1-4), умножитель 63 комплексных чисел в непозиционном коде и преобразователь 64 модулярного кода в двоичный код.

Преобразователь 30 двоичного Кода в модулярный код включает блоки 65-67 постоянной памяти для хранения констант в модулярном коде и суммирующие блоки 68.1-68.4 (для суммирования вычетов по модулям система счисления), i -и из которых (i 1-4) состоит из пяти регистров 69; и двух сумматоров 70 по модулю

R;.

Преобразователь 64 модулярного кода в двоичный код включает сумма торы 71.1-71.3, 72-75, 76.1 и 76.2 вычетов с весом, блок 77 постоянной памяти, хранящий таблицу старших разрядов двоичного кода, элементы 78 (i 1-4), 79-81 и 82 (, 2 и 3 задержки.

Разрядность регистров, номера которых снабжены индексом{i 1-4) , составляет ti Jlog, бит, где через Д х обозначаетсянаименьшее 5 целое число, не меньшее действительного числа X, Разрядность входных и выходных регистров устрс ства равна г llog2 t/ i 1 2, 3 и 4. . .Все функционёшьные узлы предлага емого устройства, за исключе.нием регистров и групп элементов И,

48

X, У;

Х,Уе|0,1,2,з

62; (,2, X, Y,

, уе(о,1,.

Р - 1

h, s, В., ; h€(o,

1,2,3} ; ,l5 f ,1,..., - 1

Таблица 1

Таблица 2

4Х + Y.шах Х, Y5

Х.2ЧУ

рх - Y/p. , /X + Y/p.

h.2.(/B,. , если

+ S2 V B i .1,2,3,4 |(2Ь,-«А.2 Л;еслй

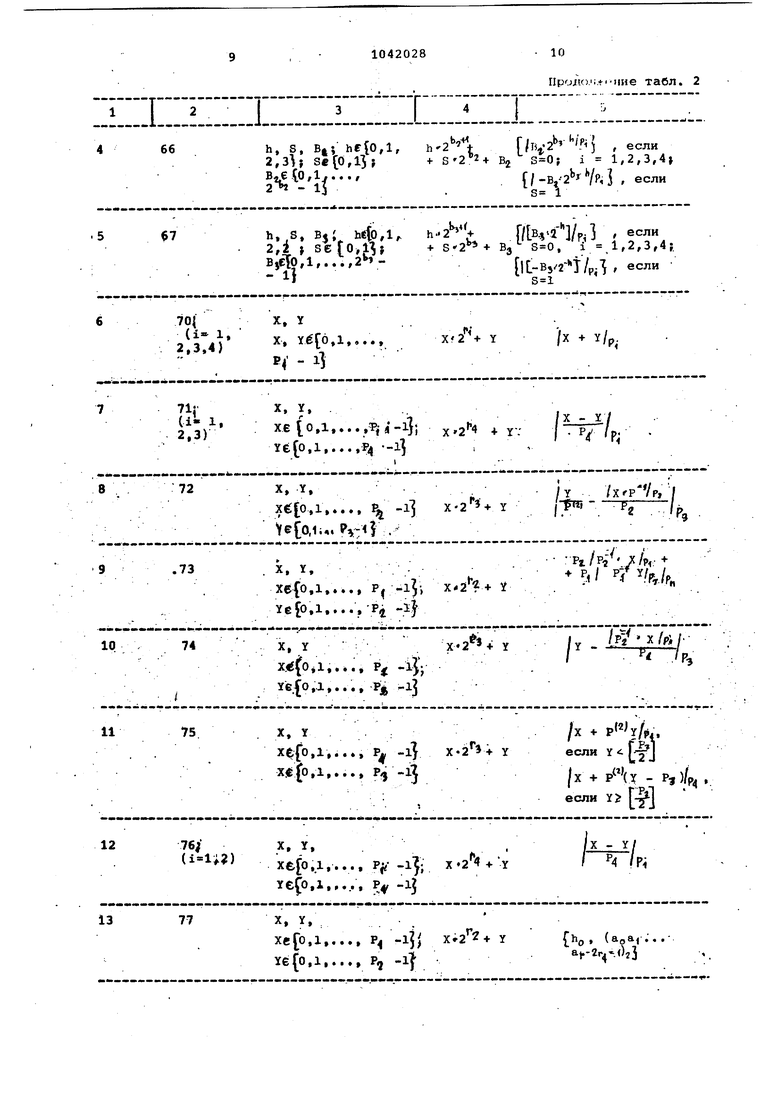

s l реализуются на основе постоянных запоминакн$1их устройств небольшой емкости. В табл. 1 для каждого из функцирнальных узлов указаны параметры соответствующих постоянных запоминакяцих устройств, а в табл.2правила формирования содержимого тлх памяти..

1042028 10

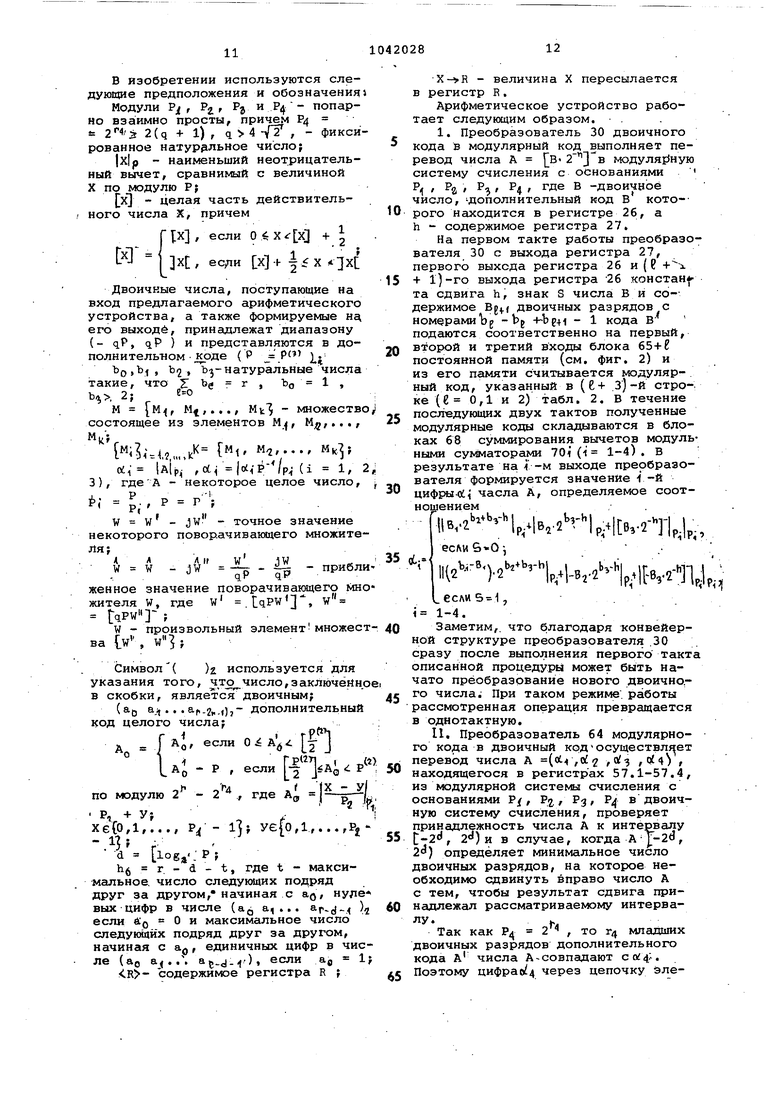

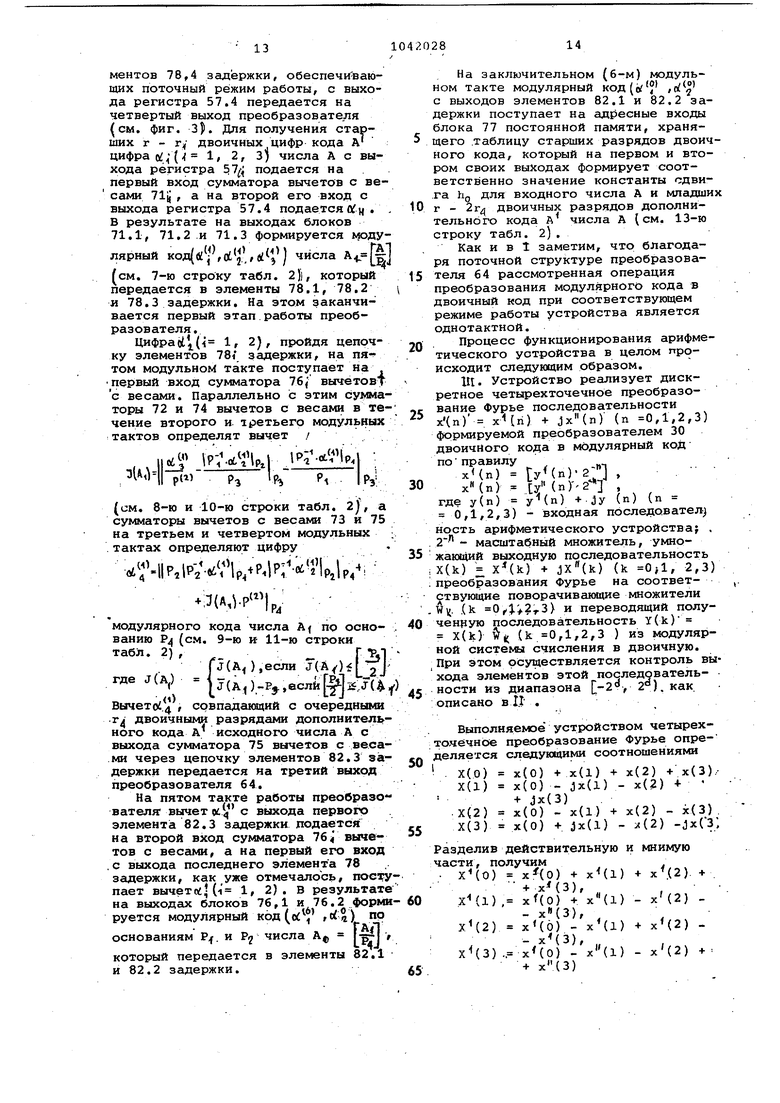

Прод().;.11|це табл. 2 В изобретении используются следующие предположения и обозначения Модули Pj( , Pji , Pg и Р - попарно взаимно просты, причем Щ s 243 2(q + 1), , - фикси рованное натуральное число; |х|р - наименьший неотрицательный вычет, сравнимый с величиной X по модулю Р} х1 - целая часть действительного числа X, причем ti:x , если О + 2 Х, если М-ь Двоичные числа, поступающие на вход предлагаемого арифметического устройства, а также формируемые на его выходе, принадлежат диапазону (- q.P чР ) и представляются в дополнительном доДе (Р Р Ц Ър.ъ, Ь2 , Ьз УР ьные числа такие, что 5Г bg г , Ъо 1 , Ь, 2; М if М,.,., MV. - множеств состоящее из элементов М, М,... .лК м,, м.г,..., м,; JAlp,- ,ot |oti-p-/p (i 1, 3), гдеA - некоторое целое число , -l,. некоторого поворачивающего множите ля; АД Л |г w 1W W W -JW - ПрибЛ q.r qf женное значение поворачивающего мн w .tqPw жителя W, где tqPw w - произвольный элемент множес ва tw, W«b Символ ( )2 используется для указания того, чт число,заключённ в скобки, являемся двоичным; (ац а,;,.. . а.2.,),- дополнительный код целого числа; А, если 0 I I.A; . Р где А по модулю 2 - 2 ., 1 + Vtfхе{о,1,..., р - уе{о,1,...,Рз -d logj-: Р ; h г. - d - t, где t - максимальное, число следукяцих подряд друг за другом, начиная с а, нул вых цифр в числе (ад а,... если ёС(5 О и максимальное число следующйх подряд друг за другом, начиная с а, единичных цифр в чи ле (во а.. а.), если а содержимое регистра R ; - величина X пересылается в регистр R. Арифметическое устройство работает следующим образом. 1. Преобразователь 30 двоичного кода в модулярный код выполняет перевод числа А модуляЕ ную систему счисления с основаниями Рц , Ра РЗ 4 -двоичное число, -дополнительный код В кото-рого находится в регистре 26, а h - содержимое регистра 27. На первом такте работы преобразователя 30 с выхода регистра 27, первого выхода регистра 26 и (8 + 1)-го выхода регистра 26 констан та сдвига h, знак S числа В и со-держимое Bg. двоичных разрядов с номерамиЪр -bf -bbp+l - 1 кода В подаются соответственно на первый, второй и третий входы блока 65+6 постоянной памяти (см. фиг. 2) и из его памяти считывается модулярный код, указанный в ( 6 + ,3) -и строке (8 0,1 и 2) табл. 2. В течение последующих двух тактов полученные модулярные коды складываются в блоках 68 суммирования вычетов модульными сукматорами 70i (i 1-4). В результате на I -м выходе преобразователя формируется значение -и цифры-и часла А, определяемое соотношением; . .jlB.-jbi+brhi 1 Ц-Ь| ,lB..|te,.2-Ti,U, если j ||/2.Л, ;IFV2- 1J рЛ1-В2-2 если 5 1, i 1-4. Заметим,, что благодаря конвейерной структуре преобразователя .30 сразу после выполнения первого такта описанной процедуры может быть начато преобразование нового двоично,го числа; При таком режиме работы рассмотренная операция превращается в однотактную. 11. Преобразователь 64 модулярного кода в двоичный код осуществляет перевод числа А (оС. ,2 , t находящегося в регистрах 57.1-57.4, из модулярной системы счисления с основаниями Р, Р, РЗ, Р в двоичную систему счисления, проверяет принадлежность числа А к интервалу С-З, 2) и в случае, когда А J;-2d, 2°) определяет минимальное число двоичных разрядов, на которое необходимо сдвинуть вправо число А с тем, чтобы результат сдвига принадлежал рассматриваемому интервалу. Так как 2 то Г4 младших двоичных разрядов дополнительного кода А числа А совпадают c«4. Поэтому цифрав 4 через цепочку элементов 78,4 задержки, обеспечи вающих поточный режим работы, с выхода регистра 57.4 передается на четвертый выход преобразователя см. фиг. 3J). Для получения старших г - гу двоичных цифр кода А цифра ( 1, 2, 3) числа А с выхода регистра 57 подается на первый вход сумматора вычетов с весами 71iJ , а на второй его вход с выхода регистра 57.4 подается . В результате на выходах блоков 71.1, 71.2 и 71.3 формируется моду лярный KOfi{(,ti числа А. (см. 7-ю строку табл. 2}), который передается в элементы 78.1, 78.2 и 78.3 задержки. На этом заканчивается первый этап работы преобразователя. ЦифраЙ(-( 1, 2), пройдя цепочку элементов 78i задержки, на пятом модульном такте поступает на . первый вход сумматора 76j вычетовт с весами. Параллельно с этим сумма торы 72 и 74 вычетов с весами в те чение второго и третьего модульных тактов определят вычет / |, pV. A Ill p(l) p IK. РЗ P-i (см, 8-ю и 10-ю строки табл. 2), а сумматоры вычетов с весами 73 и 75 на третьем и четвертом модульных тактах определяют цифру .11г, 1п- .,(1 .о1оН(0| «t l|PИf /« V%, , модулярного кода числа Af пр основанию Р(см. 9-ю и 11-ю строки табл. 2) , Г31 1 f, ,если (Af) 2/ rj(A ) ,есл1 Р j (А,)-РЗ-,« где J(A.) , .. л V . Вычеты , совпадающий с очередными гд двоичными разрядами дополнительного кода А исходного числа А с выхода сумматора 75 вычетов с весами через цепочку элементов 82.3 задержки передается на третий выход преобразователя 64. На пятом такте работы преобразователя вычет с выхода первого элемент;а 82.3 задержки подается на второй вход сумматора 764 вычетов с весами, а на первый его вход , с выхода последнего элемента 78 задержки, как уже отмечалось, посту пает вычете 4 (i 1 2). В результате на выходах блоков 76,1 и 76.2 форми руется модулярный код (о(У ei{) по основаниям Р. и Pj числа А, который передается в элементы 82.1 и 82.2 задержки. Ha заключительном (6-м) модульном такте модулярный код( ,( с выходов элементов 82.1 и 82.2 задержки поступает на адресные входы блока 77 постоянной памяти, хранящего .таблицу старших разрядов двоичного кода, который на первом и втором своих выходах формирует соответственно значение константы сдвига h(j для входного числа А и младаиих г - 2г двоичных разрядов дополнительного кода А числа А (см. 13-ю строку табл. 2). Как и в 1 заметим, что благодаря поточной структуре преобразователя 64 рассмотренная операция преобразования модулярного кода в двоичный код при соответствующем режиме работы устройства является однотактной. Процесс функционирования арифметического устройства в целом происходит следующим образом. 1U. Устройство реализует дискретное четырехточечное преобразование Фурье последовательности хЧп) . хЧп) + jx(n) (п 0,1,2,3) формируемой преобразователем 30 двоичного кода в модулярный код поправилу (п) х(п)-2 , .у . . - где у(п) у (п) +.jy (п) (п 0,1,2,3) - входная последователе ность арифметического устройства; . 2 - масштабный множитель, умножающий выходную последовательность X(k) X(k) + jx(k) (k , 2,3) преобразования Фурье на соответ- ,. твующие поворачивающие множители W. .(k 0,.J. и переводящий полученрую последовательность y(k) X(k) Wj( (k 0,1,2,3 ) из модулярной систелы счисления в двоичную. При этом осуществляется контроль выхода элементов этой последовательности Из диапазона -2°, 2°). как. описано в1Г , Выполняемое устройством четырехояёчнбе преобразование Фурье опрееляется следующими соотношениями . Х(0) х(0) + х(1) + х(2) + х(3)..Х(1) х(0) - Jx(l) - х(2) + -ь Jx(3) Х(2) х(0) - х(1) + х(2) - i(3) Х(3) х(0) + Jx(l) - i((2) -Jx(X азделив действительную и мнимую асти, получим хМо) х (о) + x4l) + ). + + х(3), .) , ) + х(1) - х (2) -,(3 « ХЧ2) х(6) - х(1) + х(2) Х(3) ., хЧо) -х(1) - х (2) - х(3)

и Х(0) х (Э) + х (1) -I- х (2) +

+ х(3), Х(1) х(0) - х (1) - х (2) +

-х(3),

Х(2) хЧо) --х) + ) .-х(3), Х(3) хЧо) + X () - х (2)

-х(3).

В начале первого шага, реалйэуемого процессором алгоритма N-точечного () быстрого преобразовани Фурье, в регистр 27, а в начале каждого из m шагов в регистр 28 через установочные входы устройства 2 И 20 соответственно передаются нулевые значения. Содержимое регист ра 28 корректируется блоком 48 постоянной памяти по правилу, указанному в 1-й строке табл. 2, после каждого четырех-точечного пр.еобразования Фурье, выполняемого арифметическим устройством. По истече регистра 24 25 Содержикюе у{3) y(i) у-уЗ) у

На первом такте работы устройства величина у (О) из регистра 26 поступает в преобразователь 30 двоичного кода в модулярный код, где, как было описано в I , начинается формирование модулярного кода числа хМо).В то же время содержимое i-ro входного регистра передается в (i+ 1)-й регистр через второй его вход для всех i 1, 2,... 7.

На втором модулярном такте преобразователем 30 На 1инается формирование модулярного кода величи- ны х1(2), а содержимое ( -го входного регистра передается в ( i l)регистр для всех i 2,...,7. Описанная последовательность действий повторяется до тех пор, пока величина у(3), находившаяся перед на(0) - x(2)L. .. 5,8,9 fx (0) x(2)|p:

нии каждого шаца Л-точечного преобразования Фурье блок 48 постоянной памяти выдает новое значение константы сдвига h, которая, пройдя через блок элементов И 32, управляемый по шине 21, поступает на первый вход регистра 27. Величина h из регистра 27 может быть передана через блок элементов И 31, управляемый по шине 3, на выходную шину устройства 4. Это производится в момент коррекции процессором быстрого преобразования Фурье, порядка обрабатываемых чисел.

Мантиссы действительных и мнимы частей отсчетов у(п) (п Р,1, 2, и 3 ) : входного сигнала арифметического устройства через входные шины устройства 1 поступают соответственно во входные регистры 24-26 устройства в порядке, задаваемым табл. 3.

Таблица 3

.I:::.J.:::...L.-.

(1) ) ) у (2) у (0)

чалом первого такта в регистре 24/ не поступит из perkctpa 26 в преобра зователь jp,. Это происходит на, восьмом модулярном такте.

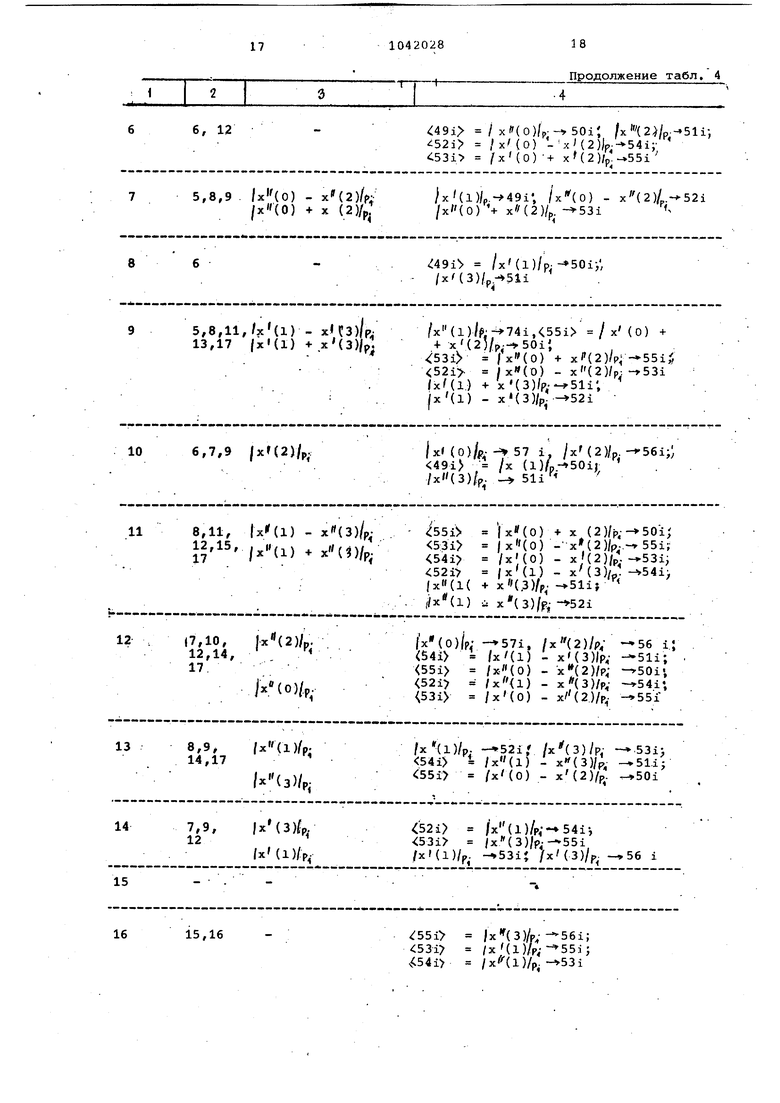

Начиная с третьего такта, модуляр ные коды чисел х (0) , х (2) ,.. .) последовательно такт за тактом . начинают появляться на выходах itpeобразователя 0. В табл. 4 для каждого из модульных тактов работы арифметического устройства, инюющих номера 3-20, указаны те из тактовых шин устройства, по которым в данном такте подаются единичные сигналы, а также перечень пересылок, обусловленных появлением этих сигналов, и операции, выполняексле модульными сумматорами-вычитателями 62 (i 1-4).

Таблица 4

(х (0)/

O4i /хЧо)/ , /хСг)/ -.51i PfPI (o)/p-v49i, /x(0) - xf(2) /x(0) V xl(2)/j,,

Продолжение табл. 4

IZflC

17

16

18

16

20 Из табл. 4 и фиг. 1 видно, что модулярный код, сформированный на выходах преобразователя 30, на (2В -t-l) -м такте через блоки элемен тов И 33.1-33,4 передается в регис ры 49.1-49.4, а на (гС + 2)-м такт через блоки элементов И 34.1-34.4 в регистры 51.1-51.4 для всех Е 1-4. Кроме.того, на (2 + 2)-м . такте (б 1-4) содержимое регистра 49( пересылается в регистр 50,-. ( 1-4) . В результате на 4, 6, 8 10-м тактах во входные регистры 50J .и 51 сумматора-вычитателя по модулю 62 соответственно подаются i-е цифры модулярных кодо пар чисел х-(о), хЧ2);; х(0), х(2); хЧ1), х (3) и х(1). х(3) .(). На модульных тактах с номерами 5-9 арифметическое устройство выполняет действия, указанные в со ответствующих строках табл. 4, и н 10-м такте сумматоры-вычитатели 62.. 1-62.4 в соответствии с (1) за веЕяигиот вычисление действительных частей х (о) и х (2) отсчетов х(0) и х(2) выходного сигнала четырехточечного преобразования Фурье. Модулярный код числа х (2) с первых выходов сумматоров-вычитателей 62.1-62.4 поступает в регистры 56.1-56.4, а на 11-м модульном так те - в умножитель 63 комплексных чисел, где начинается операция умножения комплексного числа х (2) на роответствуетций поворачивающий множитель. Отсчету ) соответствует поворачивающий множите:(1ь, равный единице, поэтому модулярный код чис ла X (0) со вторых выходов сумматоров-вычитателей 62.1-62.4 поступает в регистры 57.1-57.4 через вторые их входы (см. фиг. 1 и табл. 4} и начиная с 11-го такта преобразовате 64 начинает выполнение, как это

Продолжение табл.4

55i /х(l)/p, 53i ь /х(1)/р,- --.SSi

55i /:

(D/p.

56i описано в П операции перевода числа х (0) из модулярной системы счисления в двоичную. На 11 и 12-м модульных тактах устройство, работая в соответствии с табл 4 -иформулой (,2), находит модулярные коды чисел х (0) и х (2), которые со второго и первого выходов сум7«иторов-вычитателей 62.162.4 поступают соответственно в регистры 57.1-57.4 и 56.1-56.4. Модулярные коды пар чисел х (1) , .х (З) и х (3), х (1) сумматорами-вычитателями 62.1-62,4 формируются соответственно на 13 и 14-м модульных . тактах. Число х (3) через блоки , элементов И 35.1-35.4 передается в регистры 54.1-54.4 через первые их входы на 14-м модульном такте, а числа х(3), k (1) , хU) через блоки элементов И 44 .1-44.4 поступают в регистры 56.1-56.4 через вторые их входы соответственно на 16, 18 и 20-м модульных тактах (табл. 4). На выходах умножителя 63 комплекбных чисел полученные им произведения появляются в следующем порядке у (2), уП(2}, у- U), УЧЗ), У (1), y(lj . в таком же порядке через регистры 57.1-57.4 они поступают в преобразователь 64. Учитывая, что числа х (о) у (0) и х (0) у10) в преобразователь 64 поступают ранее в соответствии с Ц заключаем что двоичные коды действительных . и мнимых частей отсчетов выходных сигналов предлагаемого арифметического устройства со второго, третьего и четйертого выходов преобразователя 64 поступают в выходной регистр устройства 58 в следующем порядке: у (0) , у(0), у (2) , у{2}., у 13) / у (3) , у (1) , У (1) . Перед записью в регистр 58 Р-го из указанных чисел (i 2, 3, ... 8) параллельно осуществляются пересылки:

, , .

В .результате по окончании обработки входных сигналов у (п) (п 0,1,2,3) регистра I ... Содержимое у(1) y(l) ) Формируемая преобразователем 64 для каждого входного числа конс танта сдвига (см. it с первого выхода преобразователя 64 передается в двухразрядный регистр 29, откуда вместе с содержимым регистра 28 она поступает на адресные входы блока 4 памяти .4. Большая из входных величин с выхода блока 48 памяти передается в регистр 28 через первый его вход По окончании текущего шага алгоритма N -точечного преобразования Фурье, реализуемогО 1роцессором на выходе блока 48 постоянной памяти, получают константу сдвига h , общую для всех входных сигналов арифметического устройства, которые обрабатываются на следующем такте алгоритма. Поэтому константа h через блок элементов И 32 передается в регистр 27 через первый его вход для участия в работе на очередном шаге алгоритма N-точечного преобразования Фурье. Действительная и мнимая части выходного сигнала yjk) (k p,l,2,3 в требуемый мок1ент в;ремени,через бло элементов И 46-47 управляемые по шине 22, передгиотся нз регистров 58-61 на выходные ипны устройства 23.- На этом обработка входного сигнала у(п) (п - 0,1,2,3) завершается.. Таким образом, производительност предлагаемого арифметического устройства в основном зависит от быстр действия и пропускной способности умножителя комплексных чисел. Для определенности предполагают, что используется умножитель, быстродействие которого составляет 10 модульных тактов при пропускной способности - одно умножение комплекс ных чисел за четыре модульных такта. Тогда быстродействие устройства составляет 35 модульных тактов,

в ретистрах 58-61 выходная информация записывается по правилу, указанному в табл. 5.

Таблица 5 Г ... 1 ... 1 ... Г 60 1 61 уЧЗ) у(2) ) у(0) у (о) а пропускная способность - одно четырехточечное преобразование Фурье за 13 модульных тактов. Для выполнения N-точечного преобразования Фурье (N 4) потребуется 13in«4 тактов, что при N 1024 и длительности модульного такта 100 не составляет время 416 мкс, а при N 1024 и длительности такта 15tO НС время выполнения N-точечного преобразования Фурье - 624 мкс.Для технической реализации предлагаемого арифметического устройства в случае, когда используется модулярная система счисления с основаниями Р 11, Р2 13, РЗ 15 и Р 16, Обеспечивакхцая возможность работы с числами, мантиссы которых изменяются в диапазоне f-2 , . Кроме умножителя комплексных чисел Необходикы 39 постоянных запоми,нающих устройств емкостью 256 четырехразрядных слов.- постоянное запоминающее устройство емкостью 256 дэухразрядных слов (табл. 1) , три двухразр5шных, 76 четырехразрядных и 16 шестнадцатиразрядных регистров и 326 двухвходовых элеь4ентов И., Сравнение Скоростных характерисг тик предлагаемого устройства и прототипа показывает, что при использовании однотипных умножителей комплексных чисел пропускная способност первого из сравниваемых устройств существенно выше за счет использования преобразователей модулярного кода в двоичный код и двоичного кода в модулярный, имеющих максимально возможную пропускную способность. Кроме того, точность предлагаемоt-o устройства выше, чем у прототипа, так как в первом реализуется адаптивная процедура масштабирования чисел, в то время как в другом масштабы выбираются априорно.

-)

п

н

tf

26

66

57 -

/

йН

Г1,

tr

Ш

Ш

к,

Ш

т

6S3

J2J

Ш

68Л

%

lO.if

(4«.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3920978, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ben-Dan Trang | |||

| G.A | |||

| Jullian, member, IEEE and Willian C | |||

| Miller | |||

| Implementation of FFT Structures Using Sistem | |||

| IEEE, Trans Comprit, 1979, 11, p | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1983-09-15—Публикация

1981-12-18—Подача