(Л

с:

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ считывания графической информации и устройство для его осуществления | 1981 |

|

SU976457A1 |

| Устройство для считывания графической информации | 1981 |

|

SU982040A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1427398A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Устройство для считывания графической информации | 1983 |

|

SU1124350A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1550549A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1681316A1 |

| Устройство для считывания графической информации | 1983 |

|

SU1120378A1 |

| Устройство для управления @ -фазным мостовым вентильным преобразователем | 1982 |

|

SU1032590A1 |

| Устройство для считывания графической информации | 1980 |

|

SU932517A1 |

Изобретение относится к автоматике, в частности к устройству для считывания графической информации. Цель изобретения состоит в повьшении точности и надежности устройства и достигается путем селекции сигнала считывания на фоне помех, что обеспечивается введением второго интегратора, дифференцирующего элемента, второго порогового элемента, второго формирователя сигналов и элемента И. 2 ил.

00

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для считьшания графической информации, и может быть использовано для создания устройств полуавтоматического преобразования . графической информации в цифровой код.

Цель изобретения - повьшение точности и надежности устройства.

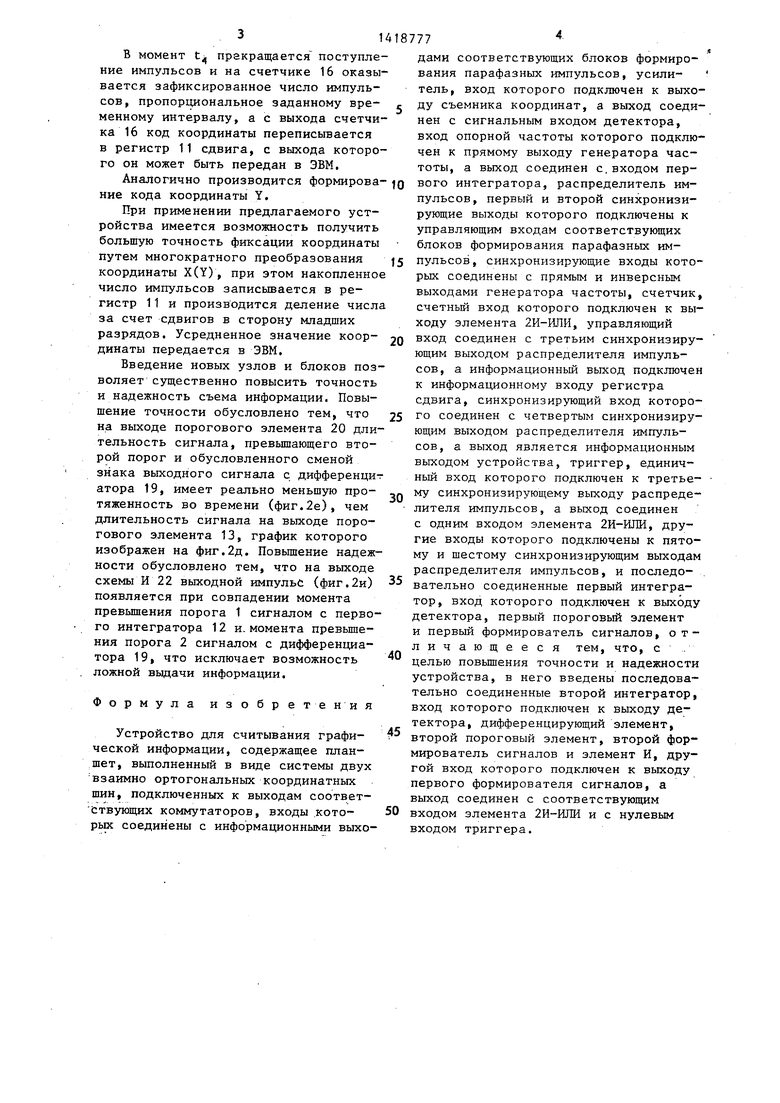

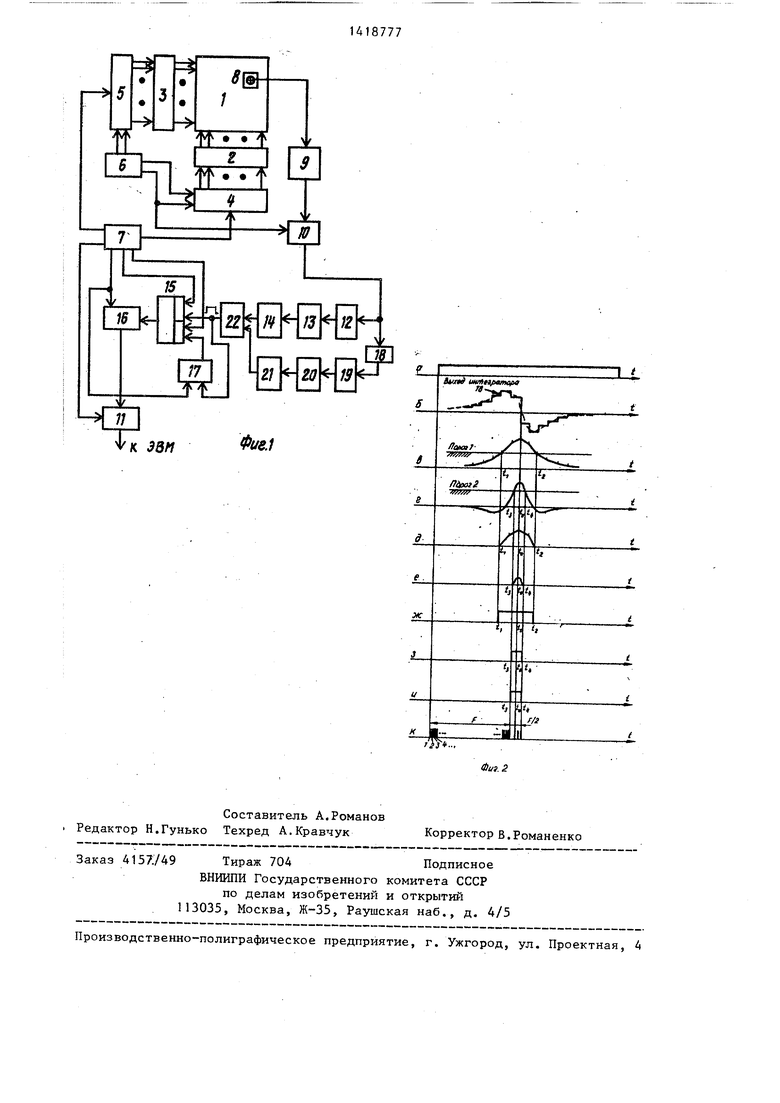

На фиг,1 представлена блок-схема устройства; на фиг,2 - временная диаграмма поясняющая его работу.

Устройство содержит планшет 1, коммутаторы 2 и 3 по осям X и Y, блоки 4 и 5 формирования парафазных импульсов, генератор 6 частоты, распределитель 7 импульсов, съемник 8 координат, усилитель 9, фазочувствитель- ный детектор 10, регистр 11 сдвига, первый интегратор 12, первый пороговый элемент 13, первый формирователь 14 сигнала, элемент 2И-2Ш1И 15, счетчик 16, триггер 17, второй интегратор 18, дифференцирующий элемент 19, второй пороговый элемент 20, второй формирователь 21 и элемент И 22,

Устройство работает следующим образом, .

Б соответствии с управляющими сигналами распределителя 7 импульсов блок 4 вырабатывает импульсы с высокочастотным заполнением, фаза которого определяется противофазными опорными сигналами, вьфабатываемыми генератором 6 частоты. Импульсы возбуждения, пройдя коммутатор 2, подводятся к соответствующим координатным шинам. Одновременно с началом поочередной коммутации шин X (фиг,2а) на выходе распределителя 7 импульсов появляется сигнал, взводящий триггер 17, который с этого момента разрешает прохождение импульсов на счетный вход счетчика 16 через второй вход второго элемента И, входящего в элемент 2И-2ИЛИ 15, Этот же сигнал устанавливает на управляю- щем входе 16 разрешение подсчета импульсов, На втором входе первого элемента И, входящего в элемент 2И-2Ш1И 15, связанном с выходом элемента И 22, в начальный момент устанавливается нулевой уровень, запрещающий прохождение импульсов на вход счетчика 16, „

По мере поочередной коммутации шин группа одновременно возбужденных парафазными импульсами шин приближается к съемнику 8 координат, расположенному в заданной точке на планшете. На съемнике 8 индуцируется ЭДС полезного сигнала, который, пройдя усилитель 9, детектируется фазочувстви- тельным детектором 10, Форма сигнала на выходе детектора приведена на фиг,2б, Этот ступенчатый сигнал подается на вход интегратора 12, на выхоQ де которого получается результирующий сигнал (фиг,2в), представленный отрезками прямых линий. Тот же сигнал поступает на вход второго интегратора 18, имеющего постоянную времени,

5 сравнимую со временем опроса одной шины, С выхода второго интегратора 18 сигнал, представляющий собой кривую, показанную на фиг,26. пунктирной линией, поступает на вход дифференци0 рующего элемента 19 (дифференциатора) , на инверсном выходе которого получается результирующий сигнал, представленный на фиг,2г. На выходе первого порогового элемента 13 поя5 вится часть проинтегрированного сигнала, превысившая установленный порог 1 (фиг,2д). На выходе второго порогового элемента 20 появится часть продифференцированного сигнала, пре0 высившая установленный порог 2 (фиг,2е), Сигнал на выходе первого формирователя 14 (фиг,2ж) представляет собой единичный логический уровень, который появляется в момент пересечения порогового уровня фронтом проинтегрированного сигнала и исчезает в момент t пересечения первого порогового уровня спадом проинтегри-; рованного сигнала. Сигнал на выходе второго формирователя 21 (фиг,3) представляет собой единичный логический уровень, который появляется в момент пересечения второго порогового уровня фронтом продифференцирован ного сигнала и исчезает в момент t пересечения второго порогового уровня спадом продифференцированного сигнала, На выходе элемента И 22 получается сигнал, представленный на фнг,2и,

0

В момент t выходной сигнал элемента И 22 переключает триггер 17 в нулевое состояние и запрещает поступление импульсов на вход счетчика 16 5 через элемент 2И-ИЛИ 15 и разрешает поступление импульсов другой частоты на вход счетчика 16 через другую половину элемента 2И-2ИЛИ 15.

5

0

5

j( прекращается поступлеВ момент t

кие импульсов и на счетчике 16 оказывается зафиксированное число импульсов, пропорциональное заданному временному интервалу, а с выхода счетчика 16 код координаты переписывается в регистр 11 сдвига, с выхода которого он может быть передан в ЭВМ.

Аналогично производится формирова-jg вого интегратора, распределитель им15

ние кода координаты Y,

При применении предлагаемого устройства имеется возможность получить большую точность фиксации координаты путем многократного преобразования координаты X(Y), при этом накопленное число импульсов записывается в регистр 11 и производится деление числа за счет сдвигов в сторону младших разрядов. Усредненное значение коор- 2П дннаты передается в ЭВМ.

Введение новых узлов и блоков позволяет существенно повысить точность и надежность съема информации. Повы- щение точности обусловлено тем, что 25 на выходе порогового элемента 20 длительность сигнала, превышающего второй порог и обусловленного сменой знака выходного сигнала с дифференциатора 19, имеет реально меньшую протяженность во времени (фиг.2е), чем длительность сигнала на выходе порогового элемента 13, график которого изображен на фиг.2д, Повьшение надежности обусловлено тем, что на выходе схемы И 22 выходной импульС (фиг.2и) появляется при совпадении момента превышения порога 1 сигналом с первого интегратора 12 и. момента превьш1е- ния порога 2 сигналом с дифференциатора 19, что исключает возможность ложной выдачи информации.

30

35

40

пульсов, первый и второй синхронизирующие выходы которого подключены к управляющим входам соответствующих блоков формирования парафазных импульсов, синхронизирующие входы которых соединены с прямым и инверсным выходами генератора частоты, счетчик, счетный вход которого подключен к выходу элемента 2И-ИЛИ, управляющий вход соединен с третьим синхронизирующим выходом распределителя импульсов, а информационный выход подключен к информационному входу регистра сдвига, синхронизирующий вход которого соединен с четвертым синхронизирующим выходом распределителя импульсов, а выход является информационным выходом устройства, триггер, единичный вход которого подключен к третьему синхронизирующему выходу распределителя импульсов, а выход соединен с одним входом элемента 2И-ИЛИ, другие входы которого подключены к пятому и шестому синхронизирующим выходам распределителя импульсов, и последо- вательно соединенные первый интегратор, вход которого подключен к выходу детектора, первый пороговый элемент и первый формирователь сигналов, отличающееся тем, что, с целью повышения точности и надежности устройства, в него введены последовательно соединенные второй интегратор, вход которого подключен к выходу детектора, дифференцирующий элемент, второй пороговый элемент, второй формирователь сигналов и элемент И, другой вход которого подключен к выходу первого формирователя сигналов, а выход соединен с соответствующим входом элемента 2И-ИЛИ и с нулевым входом триггера.

Формула изобретения

Устройство для считывания графической информации, содержащее планшет, выполненный в виде системы двух взаимно ортогональных координатных шин, подключенных к выходам соответ- Ствующих коммутаторов, входы которых соединены с информационными выхо1877

.

дами соответствующих блоков формирования парафазных импульсов, усили- тель, вход которого подключен к выходу съемника координат, а выход соединен с сигнальным входом детектора, вход опорной частоты которого подключен к прямому выходу генератора частоты, а выход соединен с,входом пер5

П

5

0

5

0

5

0

пульсов, первый и второй синхронизирующие выходы которого подключены к управляющим входам соответствующих блоков формирования парафазных импульсов, синхронизирующие входы которых соединены с прямым и инверсным выходами генератора частоты, счетчик, счетный вход которого подключен к выходу элемента 2И-ИЛИ, управляющий вход соединен с третьим синхронизирующим выходом распределителя импульсов, а информационный выход подключен к информационному входу регистра сдвига, синхронизирующий вход которого соединен с четвертым синхронизирующим выходом распределителя импульсов, а выход является информационным выходом устройства, триггер, единичный вход которого подключен к третьему синхронизирующему выходу распределителя импульсов, а выход соединен с одним входом элемента 2И-ИЛИ, другие входы которого подключены к пятому и шестому синхронизирующим выходам распределителя импульсов, и последо- . вательно соединенные первый интегратор, вход которого подключен к выходу детектора, первый пороговый элемент и первый формирователь сигналов, отличающееся тем, что, с целью повышения точности и надежности устройства, в него введены последовательно соединенные второй интегратор, вход которого подключен к выходу детектора, дифференцирующий элемент, второй пороговый элемент, второй формирователь сигналов и элемент И, другой вход которого подключен к выходу первого формирователя сигналов, а выход соединен с соответствующим входом элемента 2И-ИЛИ и с нулевым входом триггера.

IS

ш.

JPLJ

VK

к 38П

Фие.1

| Устройство для считывания графической информации | 1977 |

|

SU714434A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для считывания графической информации | 1981 |

|

SU982040A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-08-23—Публикация

1985-10-02—Подача