(Л

ТШ

Линия сдязи

4

05

СО

Линия сдязи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Передающее устройство телеизмерительной системы | 1977 |

|

SU656095A1 |

| Устройство для контроля линии связи | 1985 |

|

SU1241501A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2384012C1 |

| Способ измерения частоты электрического сигнала и устройство для его осуществления | 1991 |

|

SU1793388A1 |

| Устройство для ввода информации | 1987 |

|

SU1522189A1 |

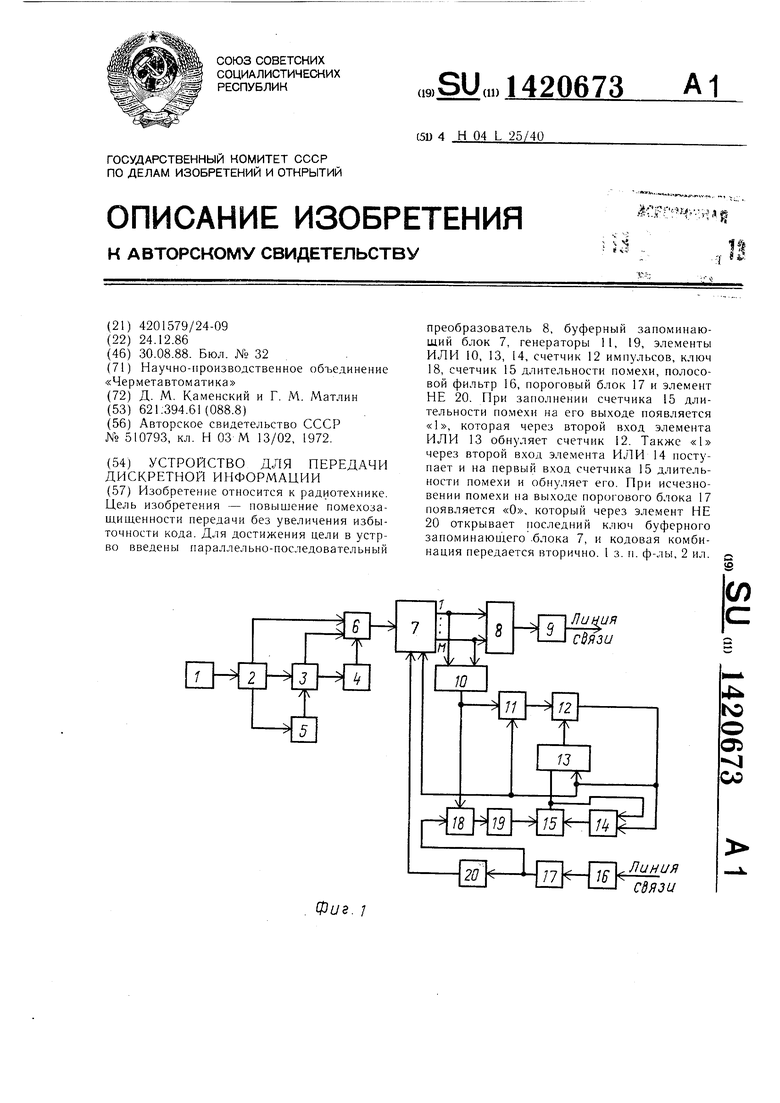

Изобретение относится к радиотехнике. Цель изобретения - новышение помехозащищенности передачи без увеличения избыточности кода. Для достижения цели в устр- во введены параллельно-последовательный преобразователь 8, буферный запоминающий блок 7, генераторы 11, 19, элементы ИЛИ 10, 13, 14, счетчик 12 импульсов, ключ 18, счетчик 15 длительности помехи, полосовой фильтр 16, пороговый блок 17 и элемент НЕ 20. При заполнении счетчика 15 длительности по.мехи на его выходе появляется «1, которая через второй вход элемента ИЛИ 13 обнуляет счетчик 12. Также «1 через второй вход элемента ИЛИ 14 поступает и на первый вход счетчика 15 длительности помехи и обнуляет его. При исчезновении помехи bia выходе порогового блока 17 появляется «О, который через элемент НЕ 20 открывает последний ключ буферного запоминаюихего .блока 7, и кодовая комбинация передается вторично. I з. п. ф-лы, 2 ил. (О

Фие. 7

Изобретение относится к радиотехнике и может быть использовано в системах передачи дикретной информации.

Цель изобретения - повышение помехозащищенности передачи без увеличения избыточности кода.

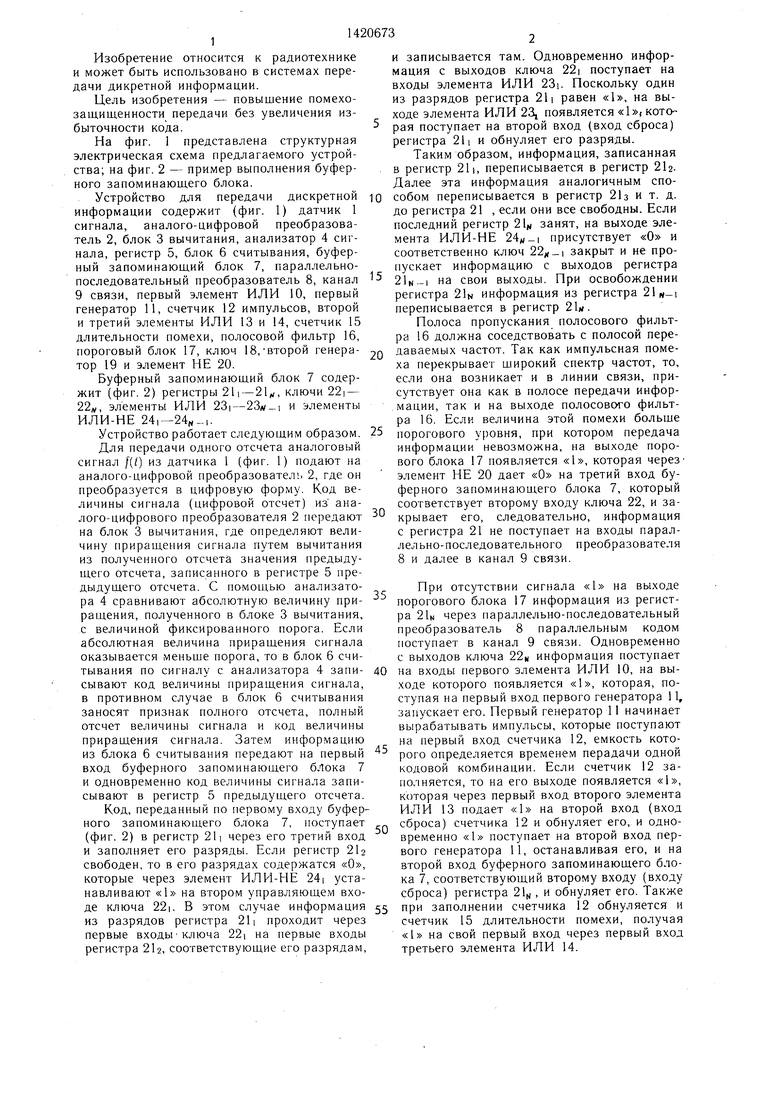

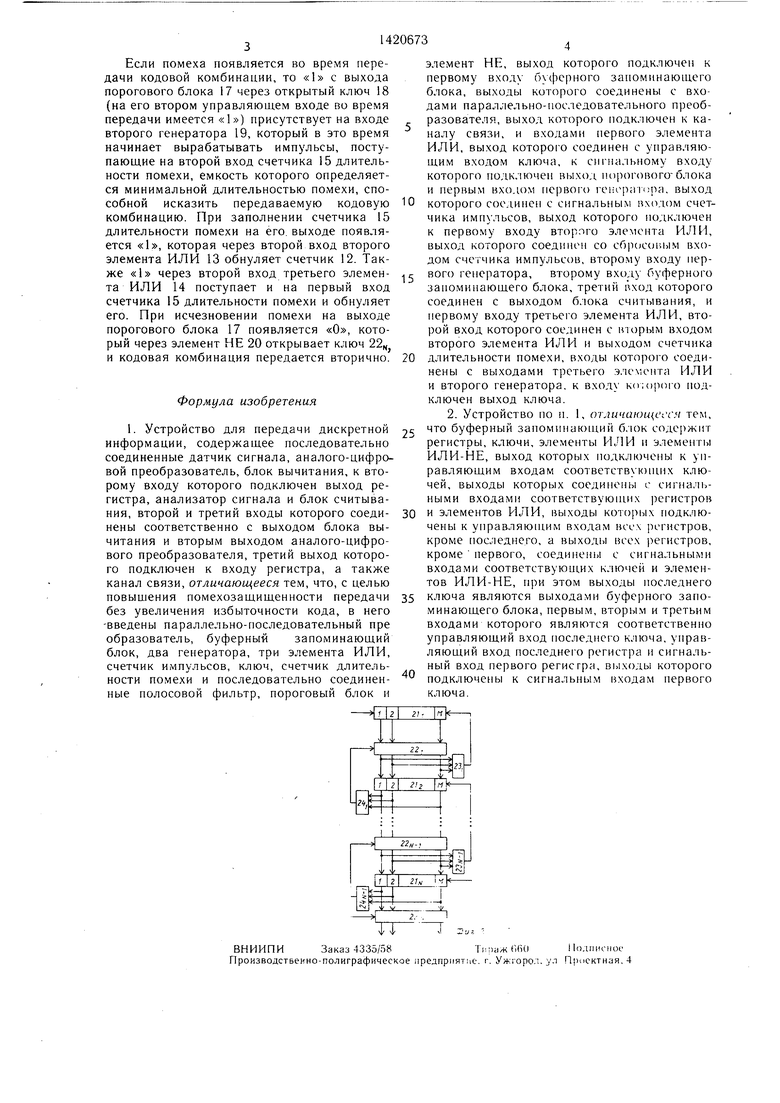

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - пример выполнения буферного запоминающего блока.

Устройство для передачи дискретной информации содержит (фиг. 1) датчик 1 сигнала, аналого-цифровой преобразователь 2, блок 3 вычитания, анализатор 4 сигнала, регистр 5, блок 6 считывания, буферный запоминающий блок 7, параллельно- последовательный преобразователь 8, канал 9 связи, первый элемент ИЛИ 10, первый генератор 11, счетчик 12 импульсов, второй и третий элементы ИЛИ 13 и 14, счетчик 15 длительности помехи, полосовой фильтр 16, пороговый блок 17, ключ 18,-второй генератор 19 и элемент НЕ 20.

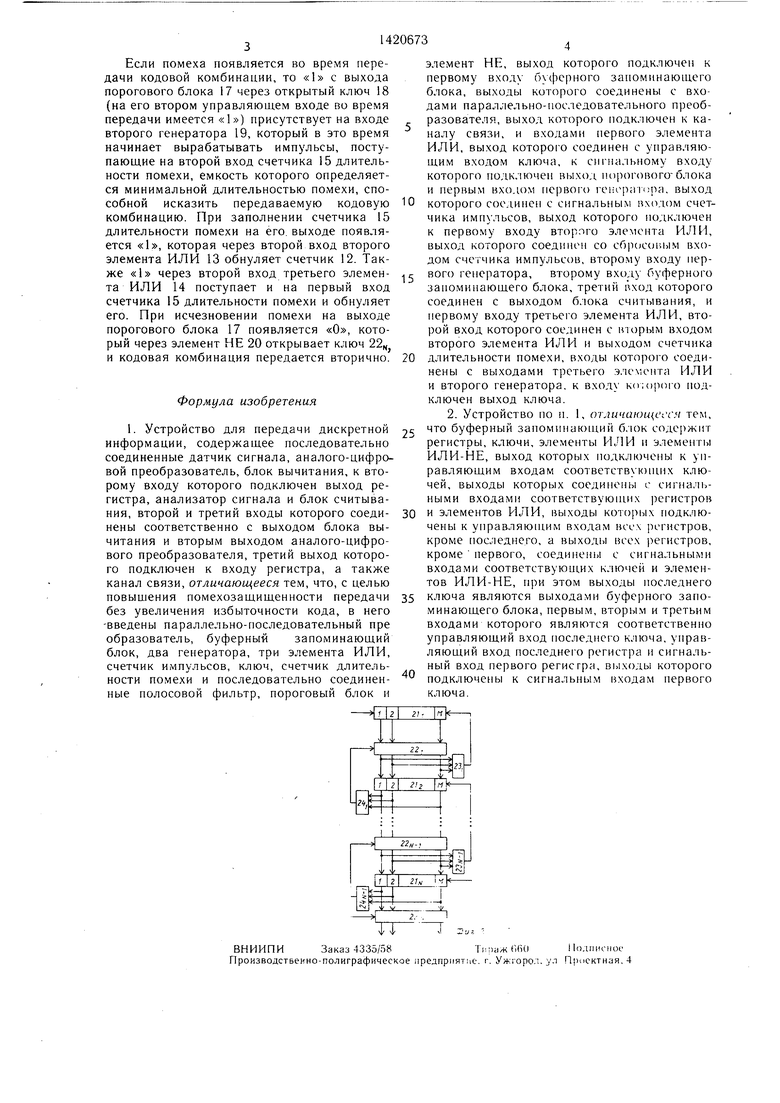

Буферный запоминающий блок 7 содержит (фиг. 2) регистры 21i-21„, ключи 22| - 22v, элементы ИЛИ 23i-23« i и элементы ИЛИ-НЕ .|.

Устройство работает следующим образом.

Для передачи одного отсчета аналоговый сигнал f(t) из датчика 1 (фиг. 1) подают на аналого-цифровой преобразователь 2, где он преобразуется в цифровую форму. Код величины сигнала (цифровой отсчет) из аналого-цифрового преобразователя 2 передают на блок 3 вычитания, где определяют величину приращения сигнала путем вычитания из полученного отсчета значения предыдущего отсчета, записанного в регистре 5 предыдущего отсчета. С помощью анализатора 4 сравнивают абсолютную величину при- ращения, полученного в блоке 3 вычитания, с величиной фиксированного порога. Если абсолютная величина приращения сигнала оказывается меньше порога, то в блок 6 считывания по сигналу с анализатора 4 запи- сывают код величины приращения сигнала, в противном случае в блок 6 считывания заносят признак полного отсчета, полный отсчет величины сигнала и код величины приращения сигнала. Затем информацию из блока 6 считывания передают на первый вход буферного запоминающего блока 7 и одновременно код величины сигнала записывают в регистр 5 предыдущего отсчета. Код, переданный по первому входу буферного запоминающего блока 7, поступает (фиг. 2) в регистр 211 через его третий вход и заполняет его разряды. Если регистр 212 свободен, то в его разрядах содержатся «О, которые через элемент ИЛИ-НЕ 24| устанавливают «1 на втором управляюще.ад входе ключа 22:. В этом случае информация из разрядов регистра 211 проходит через первые входы Ключа 22i на первые входы регистра 212, соответствующие его разрядам.

0

0

5

5

0 5

и записывается там. Одновременно информация с выходов ключа 22i поступает на входы элемента ИЛИ 23i. Поскольку один из разрядов регистра 211 равен «1, на выходе элемента ИЛИ 23i появляется «1 которая поступает на второй вход (вход сброса) регистра 211 и обнуляет его разряды.

Таким образом, информация, записанная в регистр 211, переписывается в регистр 212. Далее эта информация аналогичным способом переписывается в регистр 21з и т. д. до регистра 21 , если они все свободны. Если последний регистр 21 занят, на выходе элемента ИЛИ-НЕ присутствует «О и соответственно ключ 22 : закрыт и не пропускает информацию с выходов регистра 21м-I на свои выходы. При освобождении регистра 21м информация из регистра 21 1 переписывается в регистр 21.

Полоса пропускания полосового фильтра 16 должна соседствовать с полосой передаваемых частот. Так как импульсная помеха перекрывает щирокий спектр частот, то, если она возникает и в линии связи, присутствует она как в полосе передачи информации, так и на выходе полосового фильтра 16. Если величина этой помехи больше порогового уровня, при котором передача информации невозможна, на выходе поро- вого блока 17 появляется «1, которая через элемент НЕ 20 дает «О на третий вход буферного запоминающего блока 7, который соответствует второму входу ключа 22, и закрывает его, следовательно, информация с регистра 21 не поступает на входы параллельно-последовательного преобразователя 8 и далее в канал 9 связи.

При отсутствии сигнала «1 на выходе порогового блока 17 информация из регистра 2IN через параллельно-последовательный преобразователь 8 параллельным кодом поступает в канал 9 связи. Одновременно с выходов ключа 22,| информация поступает на входы первого элемента ИЛИ 10, на выходе которого появляется «1, которая, поступая на первый вход первого генератора 11, запускает его. Первый генератор 11 начинает вырабатывать импульсы, которые поступают на первый вход счетчика 12, емкость которого определяется временем перадачи одной кодовой комбинации. Если счетчик 12 заполняется, то на его выходе появляется «1, которая через первый вход второго элемента ИЛИ 13 подает «1 на второй вход (вход сброса) счетчика 12 и обнуляет его, и одновременно «1 поступает на второй вход первого генератора 11, останавливая его, и на второй вход буферного запоминающего блока 7, соответствующий второму входу (входу сброса) регистра 21 , и обнуляет его. Также при заполнении счетчика 12 обнуляется и счетчик 15 длительности помехи, получая «1 на свой первый вход через первый вход третьего элемента ИЛИ 14.

Если помеха появляется во время передачи кодовой комбинации, то « с выхода порогового блока 17 через открытый ключ 18 (на его втором управляющем входе во время передачи имеется «1) присутствует на входе второго генератора 19, который в это время начинает вырабатывать импульсы, поступающие на второй вход счетчика 15 длительности помехи, емкость которого определяется минимальной длительностью помехи, способной исказить передаваемую кодовую комбинацию. При заполнении счетчика 15 длительности помехи на его. выходе появляется «1, которая через второй вход второго элемента ИЛИ 13 обнуляет счетчик 12. Также «1 через второй вход третьего элемен- та ИЛИ 14 поступает и на первый вход счетчика 15 длительности помехи и обнуляет его. При исчезновении помехи на выходе порогового блока 17 появляется «О, который через элемент НЕ 20 открывает ключ 22, и кодовая комбинация передается вторично.

Формула изобретения

элемент НЕ, выход которого подключен к первому входу буферного запоминающего блока, выходы которого соединены с входами параллельно-последовательного преобразователя, выход которого подключен к каналу связи, и входами первого элемента ИЛИ, выход которого соединен с управляющим входом ключа, к сш налыюму входу которого подключен выход порогового-блока и первым входом nepsoix) rei:cp;iiopa. выход которого соединен с сигнальным входом счетчика импульсов, выход которого подключен к первому входу второго ИЛИ, выход которого соединен со c6p(jcoiibiM входом счетчика импульсов, второму входу первого генератора, второму входу буферного запоминающего блока, третий вход которого соединен с выходом блока считывания, и первому входу третьего элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента ИЛИ и выходом счетчика длительности помехи, входы которого соединены с выходами третьего э.чсмснта ИЛИ и второго генератора, к входу коюрого подключен выход ключа.

информации, содержащее последовательно соединенные датчик сигнала, аналого-цифровой преобразователь, блок вычитания, к второму входу которого подключен выход регистра, анализатор сигнала и блок считыварегистры, ключи, элементы ИЛИ и элементы ИЛИ-НЕ, выход которых подключены к управляющим входам соответствук)П1пх ключей, выходы которых соедипоны с сишаль- ными входами соответствуюп1их регистров

ния, второй и третий входы которого соеди- 30 и элементов ИЛИ, выходы которых подклюнены соответственно с выходом блока вычитания и вторым выходом аналого-цифрового преобразователя, третий выход которого подключен к входу регистра, а также канал связи, отличающееся тем, что, с целью

чены к управляющим входам всех регистров, кроме последнего, а выходы всех регистров, кроме первого, соединен) с сигнальными входами соответствуюп,их к.чючей и элементов ИЛИ-НЕ, ри этом выходь оследнего

повыщения помехозащищенности передачи 35 ключа являются выходами буферного запобез увеличения избыточности кода, в негоминающего блока, первым, и третьим

-введены параллельно-последовательный пре

образователь, буферный запоминающий

блок, два генератора, три элемента ИЛИ,

входами которого являются соответственно управляющий вход послед е -о , ляющий вход последне О регистра сигнальный вход первого регистра, в 1ходы которого подключены к сигнальным входам первого ключа.

счетчик импульсов, ключ, счетчик длительности помехи и последовательно соединенные полосовой фильтр, пороговый блок и

элемент НЕ, выход которого подключен к первому входу буферного запоминающего блока, выходы которого соединены с входами параллельно-последовательного преобразователя, выход которого подключен к каналу связи, и входами первого элемента ИЛИ, выход которого соединен с управляющим входом ключа, к сш налыюму входу которого подключен выход порогового-блока и первым входом nepsoix) rei:cp;iiopa. выход которого соединен с сигнальным входом счетчика импульсов, выход которого подключен к первому входу второго ИЛИ, выход которого соединен со c6p(jcoiibiM входом счетчика импульсов, второму входу первого генератора, второму входу буферного запоминающего блока, третий вход которого соединен с выходом блока считывания, и первому входу третьего элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента ИЛИ и выходом счетчика длительности помехи, входы которого соединены с выходами третьего э.чсмснта ИЛИ и второго генератора, к входу коюрого подключен выход ключа.

регистры, ключи, элементы ИЛИ и элементы ИЛИ-НЕ, выход которых подключены к управляющим входам соответствук)П1пх ключей, выходы которых соедипоны с сишаль- ными входами соответствуюп1их регистров

входами которого являются соответственно управляющий вход послед е -о , ляющий вход последне О регистра сигнальный вход первого регистра, в 1ходы которого подключены к сигнальным входам первого ключа.

1

| Способ адаптивной передачи информации | 1972 |

|

SU510793A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-30—Публикация

1986-12-24—Подача