Изобретение относится к технике электросвязи, может быть использовано в системах передачи данных по каналам

связи для разделения направлений пере-- разом.

дачи, и является усовершенствованием устройства, описанного в авт. св. № 1133675.

Цель изобретения - повышение помехозащищенности.10

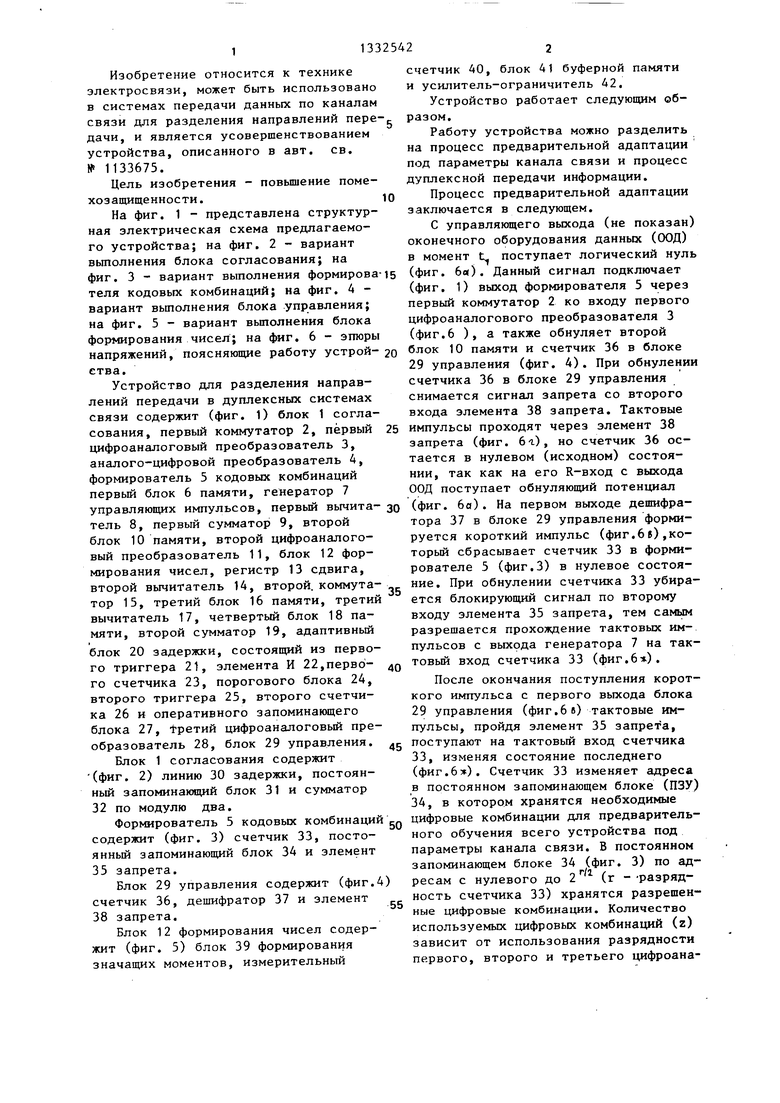

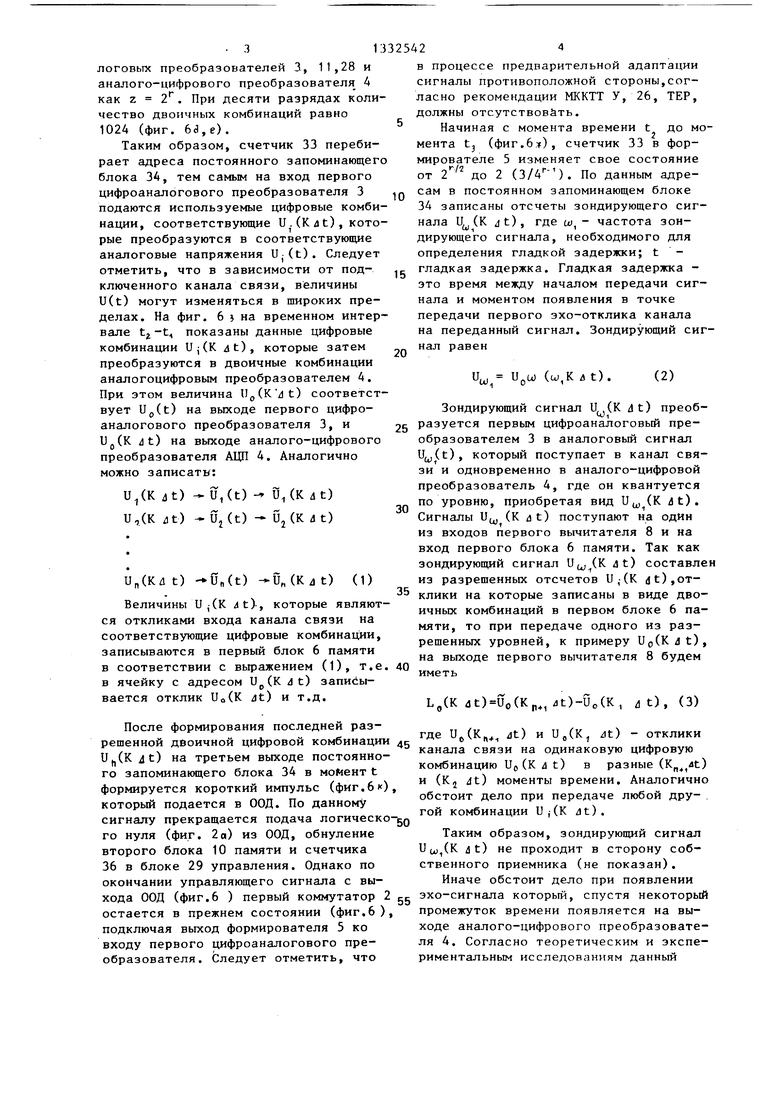

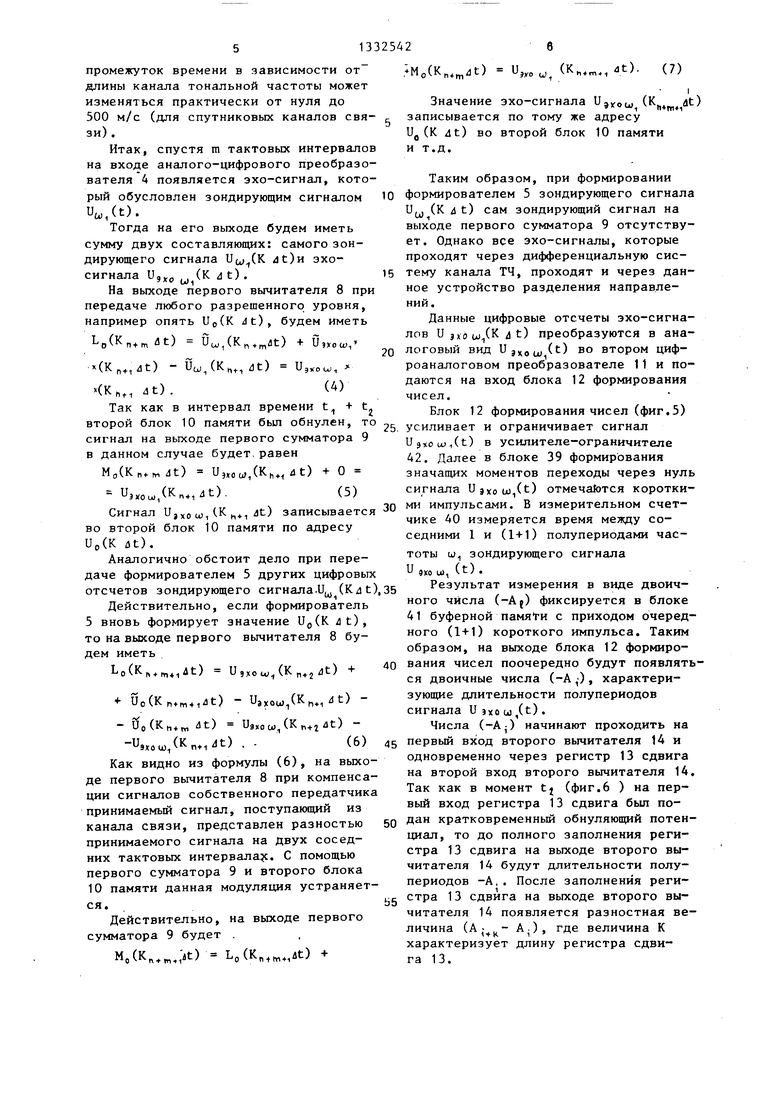

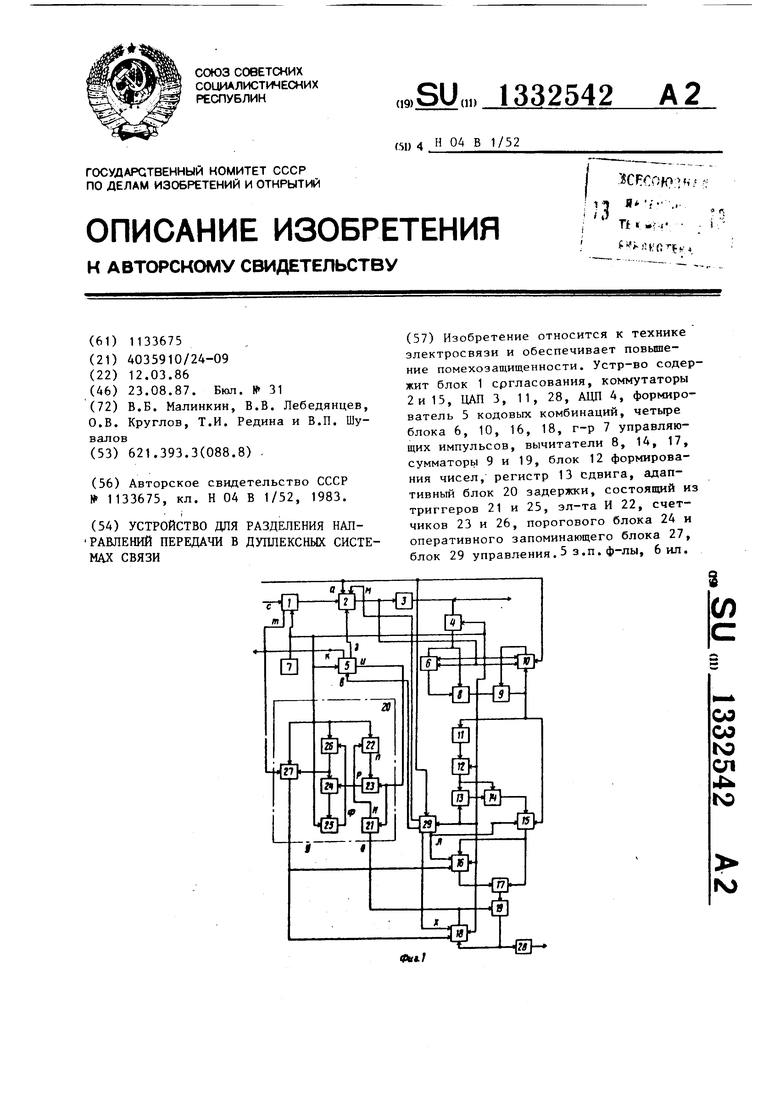

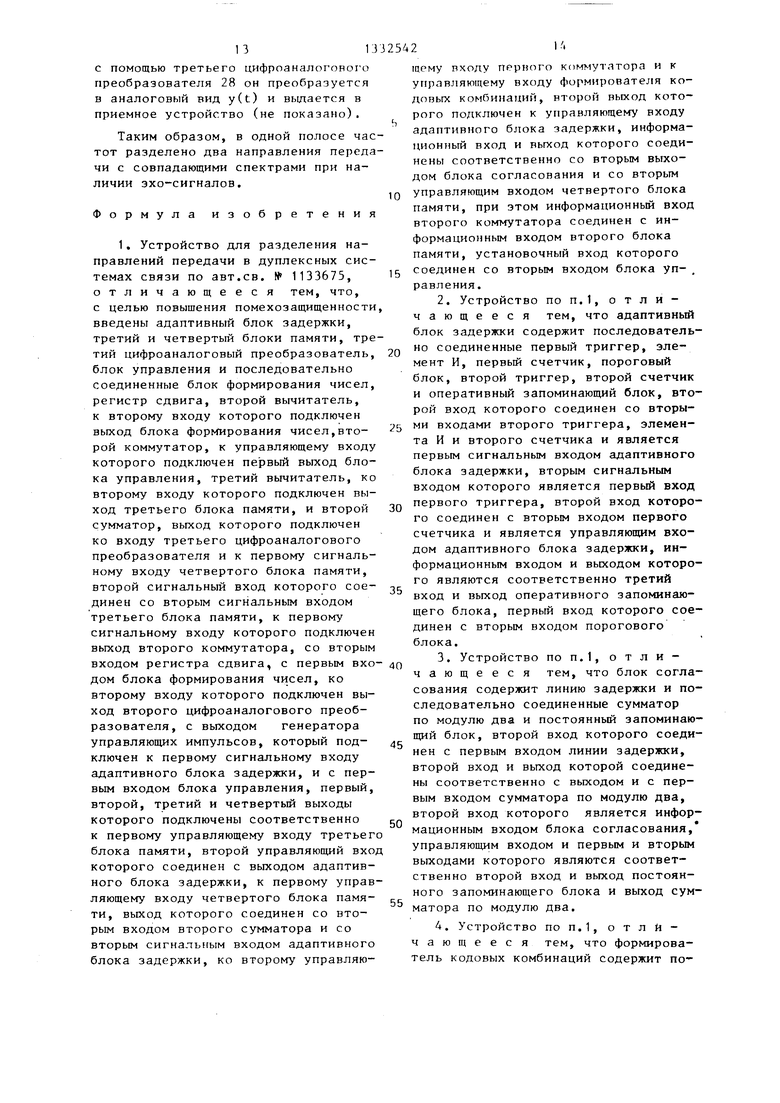

На фиг. 1 - представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - вариант вьтолнения блока согласования; на фиг. 3 - вариант выполнения формирова-15 теля кодовых комбинаций; на фиг. 4 - вариант вьтолнения блока управления; на фиг. 5 - вариант вьтолнения блока формирования чисел; на фиг. 6 - эпюры

Работу устройства можно разделить на процесс предварительной адаптации под параметры канала связи и процесс дуплексной передачи информации.

Процесс предварительной адаптации заключается в следующем.

С управляющего выхода (не показан оконечного оборудования данных (ООД) в момент Ц поступает логический нул (фиг. 6о). Данный сигнал подключает (фиг. 1) выход формирователя 5 через первый коммутатор 2 ко входу первого цифроаналогового преобразователя 3 (фиг.6 ), а также обнуляет второй

напряжений, поясняющие работу устрой- 20 блок 10 памяти и счетчик 36 в блоке

етва.

Устройство для разделения направлений передачи в дуплексных системах связи содержит (фиг. 1) блок 1 согласования, первый кoм fyтaтop 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, формирователь 5 кодовых комбинаций первый блок 6 памяти, генератор 7

управляющих импульсов, первый вычита- зо (фиг. 6а). На первом выходе дешифра-

тель 8, первый сумматор 9, второй блок 10 памяти, второй цифроаналоговый преобразователь 11, блок 12 формирования чисел, регистр 13 сдвига, второй вычитатель 14, второй, коммутатор 15, третий блок 16 памяти, третий вычитатель 17, четвертый блок 18 памяти, второй сумматор 19, адаптивньй

блок 20 задержки, состоящий из первого триггера 21, элемента И 22,первого счетчика 23, порогового блока 24, второго триггера 25, второго счетчика 26 и оперативного запоминающего блока 27, Фретий цифроаналоговый преобразователь 28, блок 29 управления.

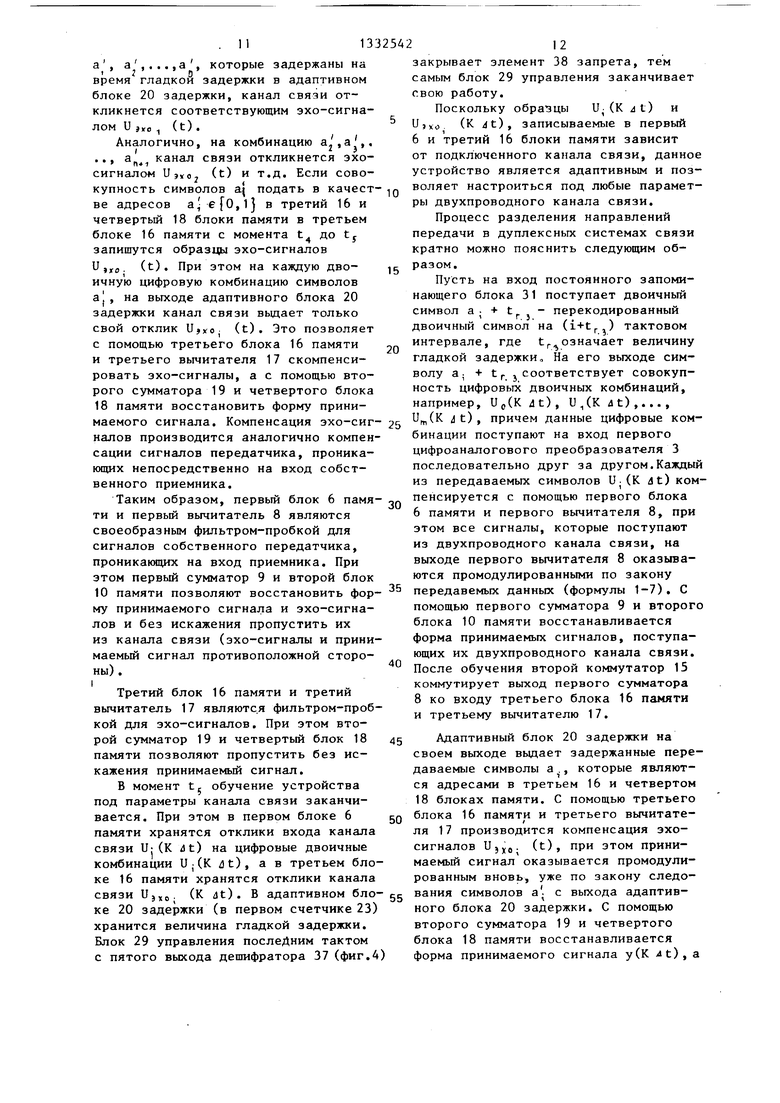

Блок 1 согласования содержит (фиг. 2) линию 30 задержки, постоянный запоминающий блок 31 и сумматор 32 по модулю два.

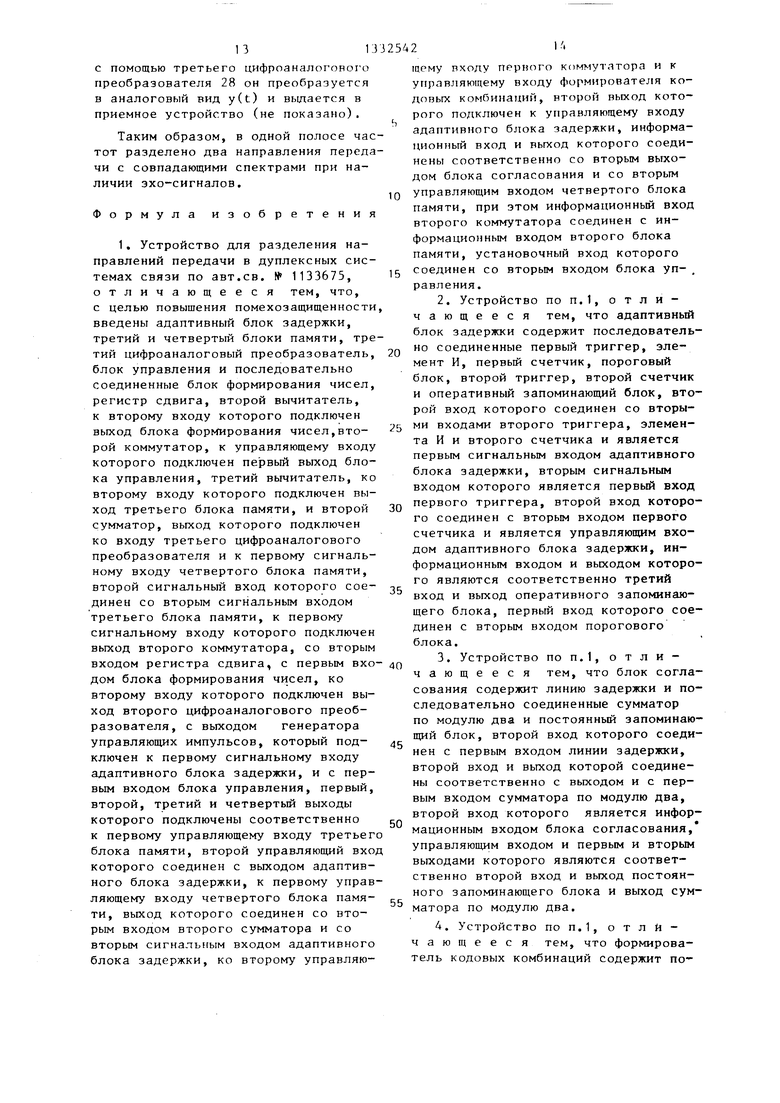

Формирователь 5 кодовых комбинаций Q цифровые комбинации для предваритель- содержит (фиг. 3) счетчик 33, посто- ного обучения всего устройства под янный запоминающий блок 34 и элемент 35 запрета.

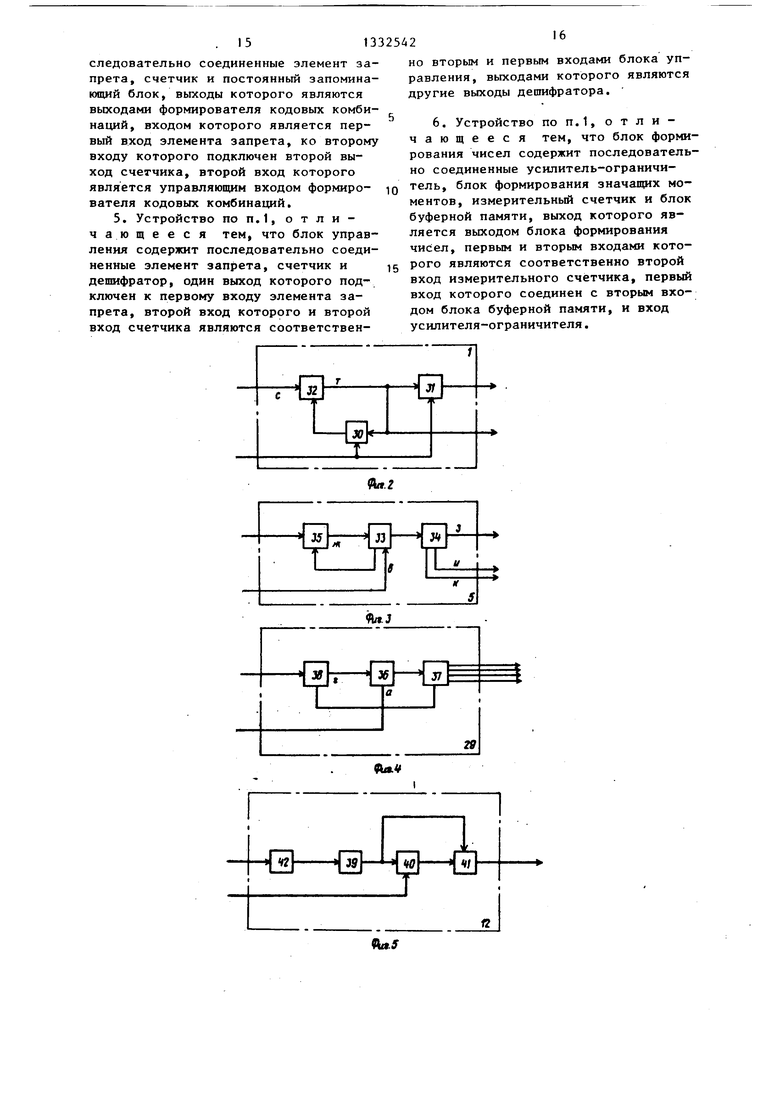

Блок 29 управления содержит (фиг.4) счетчик 36, дешифратор 37 и элемент 38 запрета.

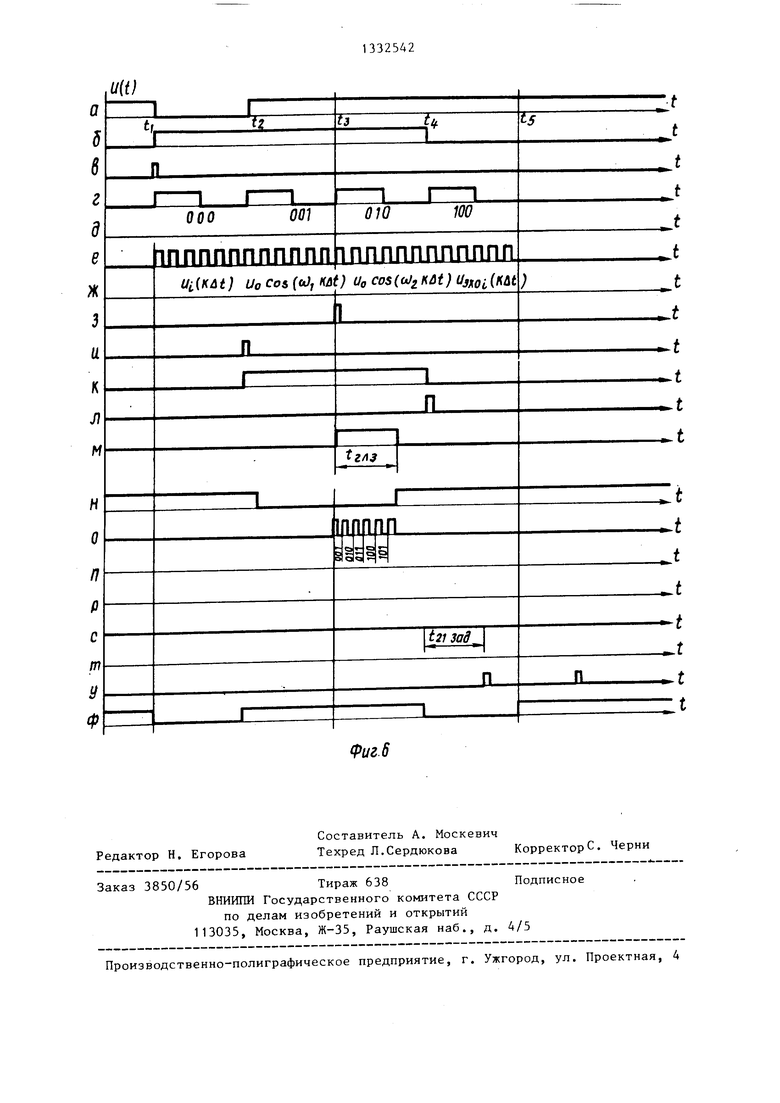

Блок 12 формирования чисел содержит (фиг. 5) блок 39 формирования значащих моментов, измерительный

55

параметры канала связи. В постоянном запоминающем блоке 34 (фиг. 3) по адресам с нулевого до 2 (г - -разряд- ность счетчика 33) хранятся разрешенные цифровые комбинации. Количество используемых цифровых комбинаций (z) зависит от использования разрядности первого, второго и третьего цифроанасчетчик 40, блок 41 буферной памяти и усилитель-ограничитель 42.

Устройство работает следующим обРаботу устройства можно разделить на процесс предварительной адаптации под параметры канала связи и процесс дуплексной передачи информации.

Процесс предварительной адаптации заключается в следующем.

С управляющего выхода (не показан) оконечного оборудования данных (ООД) в момент Ц поступает логический нуль (фиг. 6о). Данный сигнал подключает (фиг. 1) выход формирователя 5 через первый коммутатор 2 ко входу первого цифроаналогового преобразователя 3 (фиг.6 ), а также обнуляет второй

29 управления (фиг. 4). При обнулении счетчика 36 в блоке 29 управления снимается сигнал запрета со второго входа элемента 38 запрета. Тактовые импульсы проходят через элемент 38 запрета (фиг. 6i), но счетчик 36 остается в нулевом (исходном) состоянии, так как на его R-вход с выхода ООД поступает обнуляющий потенциал

5

0

5

тора 37 в блоке 29 управления формируется короткий импульс (фиг.6в),который сбрасывает счетчик 33 в формирователе 5 (фиг.З) в нулевое состояние. При обнулении счетчика 33 убирается блокирующий сигнал по второму входу элемента 35 запрета, тем самым разрешается прохождение тактовых импульсов с выхода генератора 7 на тактовый вход счетчика 33 (фиг.6).

После окончания поступления короткого импульса с первого выхода блока 29 управления (фиг.6 в) тактовые импульсы, пройдя элемент 35 запрета, поступают на тактовый вход счетчика

33,изменяя состояние последнего (фиг.6). Счетчик 33 изменяет адреса в постоянном запоминающем блоке (ПЗУ)

34,в котором хранятся необходимые

цифровые комбинации для предваритель- ного обучения всего устройства под

параметры канала связи. В постоянном запоминающем блоке 34 (фиг. 3) по адресам с нулевого до 2 (г - -разряд- ность счетчика 33) хранятся разрешенные цифровые комбинации. Количество используемых цифровых комбинаций (z) зависит от использования разрядности первого, второго и третьего цифроаналотовых преобразователей 3, 11,28 и аналого-цифрового преобразователя 4 как Z 2. При десяти разрядах количество двоичных комбинаций равно 1024 (фиг. 6d,e).

Таким образом, счетчик 33 перебирает адреса постоянного запоминающего блока ЗА, тем самым на вход первого цифроанапогового преобразователя 3 подаются используемые цифровые комбинации, соответствующие U.(К л t), которые преобразуются в соответствующие аналоговые напряжения Uj(t). Следует отметить, что в зависимости от под- ключенного канала связи, величины U(t) могут изменяться в широких пределах. На фиг. 6 J на временном интервале t -t, показаны данные цифровые комбинации иj(К 4t), которые затем преобразуются в двоичные комбинации анапогоцифровым преобразователем 4. При этом величина Uo(K /lt) соответствует Up(t) на выходе первого цифро- аналогового преобразователя 3, и Uj(K jt) на выходе аналого-цифрового преобразователя АЦП 4. Аналогично можно записатн:

и/к 4t) - ) - и(к at)

и,(К t) - U,(t) - и, (К at)

u-CKdt) (t) u.CKdt) (1)

Величины и,(к it), которые являются откликами входа канала связи на соответствующие цифровые комбинации, записываются в первый блок 6 памяти в соответствии с вьфажением (1), т.е. 40 в ячейку с адресом t) запиёы- вается отклик Uo(K at) и т.д.

После формирования последней разрешенной дйоичной цифровой комбинации 45 и(К 4t) на третьем выходе постоянного запоминающего блока 34 в момент t формируется короткий импульс (фиг.6 к), который подается в ООД. По данному сигналу прекращается подача логическо-gQ го нуля (фиг. 2а) из ООД, обнуление второго блока 10 памяти и счетчика 36 в блоке 29 управления. Однако по окончании управляющего сигнала с выхода ООД (фиг.6 ) первый коммутатор 2 gg остается в прежнем состоянии (фиг.6), подключая выход формирователя 5 ко входу первого цифроаналогового преобразователя. Следует отметить, что

в процессе предварительной адаптации сигналы противоположной стороны,согласно рекомендации ЖКТТ У, 26, ТЕР, должны отсутствовать.

Начиная с момента времени t до момента tj (фиг.6.), счетчик 33 в формирователе 5 изменяет свое состояние от 2 до 2 (). По данным адресам в постоянном запоминающем блоке 34 записаны отсчеты зондирующего сигнала Ц (К J t), где 1м - частота зондирующего сигнала, необходимого для определения гладкой задержки; t - гладкая задержка. Гладкая задержка - это время между началом передачи сигнала и моментом появления в точке передачи первого эхо-отклика канала на переданный сигнал. Зондирующий сигнал равен

Ш, UpU) (ш,К А t).

(2)

Зондирующий сигнал и.(К At) преобразуется первым цифроаналоговый преобразователем 3 в аналоговый сигнал U((t), который поступает в канал связи и одновременно в аналого-цифровой преобразователь 4, где он квантуется по уровню, приобретая вид I (К &t) . Сигналы и, (к dt) поступают на один из входов первого вычитателя 8 и на вход первого блока 6 памяти. Так как зондирующий сигнал U, (К dt) составлен из разрешенных отсчетов U,-(K ijt),отклики на которые записаны в виде двоичных комбинаций в первом блоке 6 памяти, то при передаче одного из разрешенных уровней, к примеру U(,(Kdt), на выходе первого вычитателя 8 будем иметь

L/K dt)Uo(Kp, Jt)-lJe(K, 4t), (3)

где U(,(K at) и UO(K, Jt) - отклики канала связи на одинаковую цифровую комбинацию U(, (К л t) в разные () и (KJ jt) моменты времени. Аналогично обстоит дело при передаче любой дру- . гой комбинации U((K at).

Таким образом, зондирующий сигнал и to,(К ut) не проходит в сторону собственного приемника (не показан).

Иначе обстоит дело при появлении эхо-сигнала который, спустя некоторый промежуток времени появляется на выходе аналого-цифрового преобразователя 4. Согласно теоретическим и экспериментальным исследованиям данный

промежуток времени в зависимости от длины канала тональной частоты может изменяться практически от нуля до 500 м/с (для спутниковых каналов связи) .

Итак, спустя га тактовых интервалов на входе аналого-цифрового преобразователя 4 появляется эхо-сигнал, который обусловлен зондирующим сигналом Uw,(t).

Тогда на его выходе будем иметь сумму двух составляюпщх: самого зондирующего сигнала U,(K 4С)и эхо- сигнала ы/ -

На выходе первого вычитателя 8 при передаче любого разрешенного уровня, например опять Uo(K 4t), будем иметь

Lo() Uu.,(K,it) + и,хош/ «(Kn,4t) -UCJ/K, jt) ), «(К,., dt).(4)

Mtl

Так как в интервал времени t +

г

второй блок 10 памяти бьш обнулен, сигнал на выходе первого сумматора 9 в данном случае будет, равен

M,(Kn.,jt) U5,o(j,(Kf,+, dt) + О U,,,/K,,4t).(5)

Сигнал U,vn О). (К

г

то

j,.t, At) записывается памяти по адресу

эхо

во второй блок 10 UO(K dt).

Аналогично обстоит дело при передаче формирователем 3 других цифровых отсчетов зондирующего сигнала-иц, ()

Действительно, если формирователь 5 вновь формирует значение UQ(K 4t), то на выходе первого вычитателя 8 будем иметь

LO(K

h +

dt)

и 9X0 ш (к п+2 at)

Uo(,t) - UjxoWiCKn i lt) - - UO(K + ut) Ua,ou.,() ).,

Jt)

(6)

Как видно из формулы (6), на выходе первого вычитателя 8 при компенсации сигналов собственного передатчика принимаемый сигнгш, поступающий из канала связи, представлен разностью принимаемого сигнала на Двух соседних тактовых интервала с. С помощью первого сумматора 9 и второго блока 10 памяти данная модуляция устраняется.

Действительно, на выходе первого сумматора 9 будет .

MO(K,

.;jt) L(K,,,,it) +

Mo(K,Jt)

)to и.

(К.

It). (7)

10

15

20

25.

30

Значение эхо-сигналаUj d (К dt)

записывается по тому жеадресу

Ug(К At) во второй блок10 памяти и т.д.

Таким образом, при формировании формирователем 5 зондирующего сигнала U(j (К и t) сам зондирующий сигнал на выходе первого сумматора 9 отсутствует. Однако все эхо-сигналы, которые проходят через дифференциальную систему канала ТЧ, проходят и через данное устройство разделения направлений.

Данные цифровые отсчеты эхо-сигналов и 3x0 ц; (К 4 t) преобразуются в аналоговый вид Uanouj - ° втором циф- роаналоговом преобразователе 11 и подаются на вход блока 12 формирования чисел.

Блок 12 формирования чисел (фиг.3) усиливает и ограничивает сигнал UjKouj t) в усилителе-ограничителе 42. Далее в блоке 39 формирования значащих моментов переходы через нуль сигнала Uj ouj/t) отмечаются короткими импульсами. В измерительном счетчике 40 измеряется время между соседними 1 и (1+1) полупериодами час5

0

0

5

тоты U), зондирующего сигнала

и 9КО U), (t) .

Результат измерения в виде двоичного числа (-А() фиксируется в блоке 41 буферной памя ги с приходом очередного (1+1) короткого импульса. Таким образом, на выходе блока 12 формирования чисел поочередно будут появляться двоичные числа (-А ,), характеризующие длительности полупериодов сигнала U эхо ы (t) .

Числа (-А-) начинают проходить на 5 первый вход второго вычитателя 14 и одновременно через регистр 13 сдвига на второй вход второго вычитателя 14. Так как в момент tj (фиг.6 ) на первый вход регистра 13 сдвига был подан кратковременный обнуляющий потенциал, то до полного заполнения регистра 13 сдвига на выходе второго вычитателя 14 будут длительности полупериодов -А,. После заполнения регистра 13 сдвига на выходе второго вычитателя 14 появляется разностная величина ( А.), где величина К характеризует длину регистра сдвига 13.

Так как с момента t до t третий блок 16 памяти обнулен (фиг.6 ), то выход второго вычитателя 14 через второй коммутатор 15 и третий вычипамяти, то Uy (t) не проходит в сторону собственного приемника. На выходе первого коммутатора 2 будут лишь присутствовать эхо-сигналы U,oj (t),

10

татель 17 оказывается подключенным ко 5 которые обусловлены сигналом Цц, (t), входу второго сумматора 19.Сигнал U о (t), пройдя блок 12форПусть на выходе второго вычитате- мированин чисел, преобразуется в ля 14 прявилось число (-А), которое числа (+В.), аналогично полученным характеризует длительность первого полупериода частоты сигнала (t)Данное число (-А) проходит через второй вычитатель 14, второй коммутатор 15 и третий вычитатель 17, подается на вход второго сумматора 19. Так как четвертый блок 18 памяти с момента t до t бьш обнулен (фиг.бз), то на выходе второго сумматора 19 будем иметь число (-А). С приходом (-AJ) на выходе второго сумматора 19 имеем -(А А ) и т.д.

После заполнения регистра 13 сдвига на выходе второго сумматора 19 будем иметь

к

20

ранее числам (-А,), которые характеризовали сигнал U,xoto(t). Таким образом как только из канала связи будет приниматься сигнал U ,,д j (t), зто означает, что гладкая задержка закончилась. Для удобства реализации адаптивного блока 20 задержки, в котором фиксируется величина гладкой задержки, выбирают lAj (В,.|.

С этой целью на тактовый вход измерительного счетчика 33 с выхода генератора 7 подают частоту, определяемую выражением

т + 1 f - . . . (.11)

т -(А ...+А)-Х А..8)

25

2U..

1

2со,

fii

После (К+1) полупериода будем иметь

к11+1

-11 A--A,-(-A., -Z А; (9)

)

30

14

После (К+п) полупериодов будем иметь

К.+ П

-LA. . (10)

i h

Таким образом, начиная с момента

(

где m - разрядность счетчика 35; u)j- частоты зондирующих сигналов } (t) и U, (t) соответственно.

При поступлении чисел +В, характеризующих длительности полупериодов частоты Wj сигнала Ui (t), на вход второго сумматора 19 на его выходе через определенное время, называемое 35 временем ангшиза, появится сигнал, равный

fctm

Т f I() t.

t, и до t,

второй сумматор 19 совместно с четвертым блоком 18 памяти выполняет функцию скользящего сумма- 40 тора. В момент t формирователь 5 начинает генерировать второй зондирующий сигнал и (К 4.t). С этой целью тактовые импульсы, проходя через элемент 35 запрета переводят счетчик 33 в формирователе 5 в состоТ f I() t.

Время между началом передачи сигнала UujjCt) и появлением сигнала и,5ы (t) прошедшего эхо-тракт подключенного канала связи, характеризует величину гладкой згщержки. Для ее измерения служит первый триггер 21,

- -.---.- элемент И 22 и первый счетчик 23 в

яние 2 (где г - разрядность счет- адаптивном блоке 20 задержки (фиг.1). чика ЗЗХ. В постоянном запоминающем При формировании сигнала Uu (К dt) блоке 34 по адресам, начиная с 2 формирователем 5 на втором выходе подо 2 , записаны цифровые отсчеты вто- 50 следнего появляется короткий импульс рого зондирующего сигналаUu(K Jt), (фиг.6 ), который устанавливает пер- представляющего собой синусоиду с вый триггер 21 в единичное состояние частотой следования u)i.(фиг. 6н), а первый счетчик 23 приЭондирующий сигнал U (t) поступа- нудительно устанавливается в исходное

.. gg ростояние (фиг.бр). Первый триггер 21

принудительно разблокирует элемент ,И 22 (фиг.бп), тем самым тактовые импульсы с выхода генератора 7 проходят на вход первого счетчика 23, коет в канал связи и одновременно в аналого-цифровой преобразователь 4. iТак как U (t) также составлен из цифровых отсчетов U(K.dt), реакции на которые имеются в первом блоке 6

памяти, то Uy (t) не проходит в сторону собственного приемника. На выходе первого коммутатора 2 будут лишь присутствовать эхо-сигналы U,oj (t),

которые обусловлены сигналом Цц, (t), Сигнал U о (t), пройдя блок 12фор

мированин чисел, преобразуется в числа (+В.), аналогично полученным

ранее числам (-А,), которые характеризовали сигнал U,xoto(t). Таким образом как только из канала связи будет приниматься сигнал U ,,д j (t), зто означает, что гладкая задержка закончилась. Для удобства реализации адаптивного блока 20 задержки, в котором фиксируется величина гладкой задержки, выбирают lAj (В,.|.

С этой целью на тактовый вход измерительного счетчика 33 с выхода генератора 7 подают частоту, определяемую выражением

т + 1 f - . . . (.11)

2U..

1

2со,

где m - разрядность счетчика 35; u)j- частоты зондирующих сигналов } (t) и U, (t) соответственно.

При поступлении чисел +В, характеризующих длительности полупериодов частоты Wj сигнала Ui (t), на вход второго сумматора 19 на его выходе через определенное время, называемое временем ангшиза, появится сигнал, равный

fctm

В,. (12)

Т f I() t.

Время между началом передачи сигнала UujjCt) и появлением сигнала и,5ы (t) прошедшего эхо-тракт подключенного канала связи, характеризуторыи начинает изменять свое состояние до тех пор, пока с выхода скользящего сумматора не появится сигнаш Т (К+га), который вернет первый триггер 21 в исходное состояние (фиг.6) и закроет элемент И 22, Следует отметить, что счетчик 23 выполняется с предустановкой, в которой в первьш момент фиксируется число, равное половине длины регистра сдвига 13-К/2. Двоичное число, которое записано в счетчике 23, характеризует гладкую задержку данного канала связи.

В момент t счетчик 33 достигает значения 2. После этого элемент 35 запрета закрывается, и формирователь 5 прекращает свою работу.

В момент t начинается обучение устройства разделения под эхо-сигналы

С этой целью сигнал со второго вы- 20 яние второго счетчика 26 достигнет

хода блока 29 управления подключает выход первого сумматора 9 через второй коммутатор 15 на вход третьего блока 16 памяти и на один из входов третьего вычитателя 17 (фиг.6k).

Начиная с момента до момента t, производится обнуление четвертог блока 18 памяти (фиг.бх) сигналом с третьего выхода блока 29 управления.

Короткий импульс с четвертого выхода блока 29 управления (фиг.блО в момент t. возвращает первый коммутаТак как выход второго счетчика 26 подключен к адресным входам оперативного запоминающего блока 27, то протор 2 в исходное состояние. Этим самым выход блока 1 оказывается подключенным ко входу первого цифроаналого- 35 величину гладкой задержки, вого преобразователя 3. С информаци- Таким образом, если на входе адап- онного выхода ООД начинает поступать случайный двоичный сигнал а. (фиг.6с), который в блоке 1 с помощью сумматора 32 по модулю два и линии 30 задержки 40 (фиг.2) перекодируется в относительизводится задержка символов а. ровно

тивного блока 20 задержки появляется информационный символ а. в момент t

появляется в момент t+t ..,

1 гл. вд

(фиг.6 г), то на его выходе данный символ а I (фиг.6 v) .

ный сигнал по следующему закону (6): а а- 0 а . , (13)

где а. и а. - соответственно перекодированный и неперекодированный двоичные символы, подлежащие передаче.50 В соответствии со значением перекодированного сигнала в постоянном запоминающем блоке 31 хранятся соответствующие цифровые отсчеты и,- (Kdt), порядок следования которых соответст- 55 проходят лидаь сигналы, которые посту- вует амплитудной, частотной или фазо- пают из канала связи. Так как эхо- вой модуляции. Следует отметить,что

°h дать по каналу связи (фиг.6т), Каждый

из передаваемых символов а. состоит из совокупности разращенных цифровых комбинаций U;(К ut).

Как показано выше, передаваемые сигналы U(t) с выхода первого цифро- аналогового преобразователя 3 на вход собственного приемника не проходят. К приемному устройству (не показано)

сигнапы возвращаются из канала связи через время гладкой задержки, то на совокупность передаваемых символов

каждому перекодированному символу а соответствует определенная совокуп2542

10

.

ность цифровых отсчетов U ,-(К/i t) , отклики КС на которые записаны в первом блоке 6 памяти.

Перекодированные символы al поступают в адаптивный блок 20 задержки, который должен их задерживать ровно на величину гладкой задержки. Как показано выше, величина гладкой задержки в виде двоичного числа хранит10 ся в первом счетчике 23.

Пусть второй счетчик 26 и второй триггер 25 находятся в нулевом состоянии. Второй счетчик 26 под действием тактовых импульсов с выхода ге15 нератора 7 начинает изменять свое состояние. Пороговый блок 24 сравнивает состояние второго счетчика 26 с величиной гладкой задержки, хранимой в первом счетчике 23. Как только состовеличины гладкой задержки, на выходе порогового блока 24 появляется логическая единица, которая фиксируется во втором триггере 25. Сигнал с вы- хода второго триггера 25 обнуляет второй счетчик 26, и цикл работы последнего повторяется. Таким образом, период работы второго счетчика 26 определяется величиной гладкой задержки,

которую обозначим через t . (фиг.6).

гл. 5ад

Так как выход второго счетчика 26 подключен к адресным входам оперативного запоминающего блока 27, то про величину гладкой задержки, Таким образом, если на входе адап-

величину гладкой задержки, Таким образом, если на входе адап-

изводится задержка символов а. ровно

величину гладкой задержки, Таким образом, если на входе адап

тивного блока 20 задержки появляется информационный символ а. в момент t

величину гладкой задержки, Таким образом, если на входе адап-

появляется в момент t+t ..,

1 гл. вд

(фиг.6 г), то на его выходе данный символ а I (фиг.6 v) .

Пусть на входе постоянного запоминающего блока 31 последовательно появляются (фиг.2) двоичные символы а ,

а

которые необходимо перепроходят лидаь сигналы, которые посту- пают из канала связи. Так как эхо-

°h дать по каналу связи (фиг.6т), Каждый

из передаваемых символов а. состоит из совокупности разращенных цифровых комбинаций U;(К ut).

Как показано выше, передаваемые сигналы U(t) с выхода первого цифро- аналогового преобразователя 3 на вход собственного приемника не проходят. К приемному устройству (не показано)

проходят лидаь сигналы, которые посту- пают из канала связи. Так как эхо-

сигнапы возвращаются из канала связи через время гладкой задержки, то на совокупность передаваемых символов

II

г

, которые задержаны на время гладкой задержки в адаптивном блоке 20 задержки, канал связи откликнется соответствующим эхо-сигналом и ,,0 (t).

Аналогично, на комбинацию а ,а ,. .., а канал связи откликнется эхо- сигналом и (t) и т.д. Если совокупность символов aj подать в качестве адресов а efO,l в третий 16 и четвертый 18 блоки памяти в третьем блоке 16 памяти с момента t до tj запишутся образцы эхо-сигналов Ujxo. (t). При этом на каждую двоичную цифровую комбинацию символов aJ, на выходе адаптивного блока 20 задержки канал связи выдает только свой отклик Ujvoj (t). Это позволяет с помощью третьего блока 16 памяти и третьего вычитателя 17 скомпенсировать эхо-сигналы, а с помощью второго сумматора 19 и четвертого блока 18 памяти восстановить форму принизакрывает элемент

12 38

запрета, тем

10

15

20

самым блок 29 управления заканчивает свою работу.

Поскольку образцы U-(К jt) и Ujxo ( 4t), записываемые в первый 6 и третий 16 блоки памяти зависит от подключенного канала связи, данное устройство является адаптивным и позволяет настроиться под любые параметры двухпроводного канала связи.

Процесс разделения направлений передачи в дуплексных системах связи кратно можно пояснить следующим образом.

Пусть на вход постоянного запоминающего блока 31 поступает двоичный символ а -I- t - перекодированный двоичный символ на (i+t,. ) тактовом интервале, где tr,O3Ha4aeT величину гладкой задержки. На его выходе символу а- t г J соответствует совокупность цифровых двоичных комбинаций, например, U(,(K 4t), U,(K at),....

маемого сигнала. Компенсация эхо-сиг- 25 причем данные цифровые комбинации поступают на вход первого цифроаналогового преобразователя 3 последовательно друг за другом.Каждый из передаваемых символов Uj(К At) компенсируется с помощью первого блока 6 памяти и первого вычитателя 8, при этом все сигналы, которые поступают из двухпроводного канала связи, на выходе первого вьр4итателя 8 оказьгеа- ются промодулированными по закону передавемых данных (формулы 1-7), С помощью первого сумматора 9 и второго блока 10 памяти восстанавливается форма принимаемых сигналов, поступающих их двухпроводного канала связи. После обучения второй коммутатор 15 коммутирует выход первого сумматора 8 ко входу третьего блока 16 памяти и третьему вычитателю 17.

30

налов производится аналогично компенсации сигналов передатчика, проникающих непосредственно на вход собственного приемника.

Таким образом, первый блок 6 памяти и первый вычитатель 8 являются своеобразным фильтром-пробкой для сигналов собственного передатчика, проникающих на вход приемника. При этом первый сумматор 9 и второй блок 10 памяти позволяют восстановить фор- му принимаемого сигнала и эхо-сигналов и без искажения пропустить их из кансша связи (эхо-сигналы и принимаемый сигнал противоположной стороны) . I

Третий блок 16 памяти и третий

вычитатель 17 являютс.я фильтром-пробкой для эхо-сигналов. При этом второй сумматор 19 и четвертый блок 18 памяти позволяют пропустить без искажения принимаемый сигнал.

В момент t обучение устройства под параметры канала связи заканчивается. При этом в первом блоке 6 памяти хранятся отклики входа канала связи U:(K 4t) на цифровые двоичные комбинации Uj(K jt), а в третьем блоке 16 памяти хранятся отклики канала связи и,,о (К dt). В адаптивном бло- 55 вания символов а с выхода адаптив40

45

50

бинации поступают на вход первого цифроаналогового преобразователя 3 последовательно друг за другом.Кажды из передаваемых символов Uj(К At) ко пенсируется с помощью первого блока 6 памяти и первого вычитателя 8, при этом все сигналы, которые поступают из двухпроводного канала связи, на выходе первого вьр4итателя 8 оказьгеа- ются промодулированными по закону передавемых данных (формулы 1-7), С помощью первого сумматора 9 и второг блока 10 памяти восстанавливается форма принимаемых сигналов, поступающих их двухпроводного канала связи. После обучения второй коммутатор 15 коммутирует выход первого сумматора 8 ко входу третьего блока 16 памяти и третьему вычитателю 17.

Адаптивный блок 20 задержки на своем выходе выдает задержанные пере даваемые символы а., которые являются адресами в третьем 16 и четвертом 18 блоках памяти. С помощью третьего блока 16 памяти и третьего вычитателя 17 производится компенсация эхосигналов U5,(o- (t) при этом принимаемый сигнал оказывается промодули- рованным вновь, уже по закону следоке 20 задержки (в первом счетчике 23) хранится величина гладкой задержки. Блок 29 управления последним тактом с пятого выхода дешифратора 37 (фиг.4)

кого блока 20 задержки. С помощью второго сумматора 19 и четвертого блока 18 памяти восстанавливается форма принимаемого сигнала у (К ),

элемент

12 38

запрета, тем

самым блок 29 управления заканчивает свою работу.

Поскольку образцы U-(К jt) и Ujxo ( 4t), записываемые в первый 6 и третий 16 блоки памяти зависит от подключенного канала связи, данное устройство является адаптивным и позволяет настроиться под любые параметры двухпроводного канала связи.

Процесс разделения направлений передачи в дуплексных системах связи кратно можно пояснить следующим образом.

Пусть на вход постоянного запоминающего блока 31 поступает двоичный символ а -I- t - перекодированный двоичный символ на (i+t,. ) тактовом интервале, где tr,O3Ha4aeT величину гладкой задержки. На его выходе символу а- t г J соответствует совокупность цифровых двоичных комбинаций, например, U(,(K 4t), U,(K at),....

причем данные цифровые причем данные цифровые ком

вания символов а с выхода адаптив

бинации поступают на вход первого цифроаналогового преобразователя 3 последовательно друг за другом.Каждый из передаваемых символов Uj(К At) компенсируется с помощью первого блока 6 памяти и первого вычитателя 8, при этом все сигналы, которые поступают из двухпроводного канала связи, на выходе первого вьр4итателя 8 оказьгеа- ются промодулированными по закону передавемых данных (формулы 1-7), С помощью первого сумматора 9 и второго блока 10 памяти восстанавливается форма принимаемых сигналов, поступающих их двухпроводного канала связи. После обучения второй коммутатор 15 коммутирует выход первого сумматора 8 ко входу третьего блока 16 памяти и третьему вычитателю 17.

Адаптивный блок 20 задержки на своем выходе выдает задержанные передаваемые символы а., которые являются адресами в третьем 16 и четвертом 18 блоках памяти. С помощью третьего блока 16 памяти и третьего вычитателя 17 производится компенсация эхования символов а с выхода адаптивсигналов U5,(o- (t) при этом принимаемый сигнал оказывается промодули- рованным вновь, уже по закону следования символов а с выхода адаптивкого блока 20 задержки. С помощью второго сумматора 19 и четвертого блока 18 памяти восстанавливается форма принимаемого сигнала у (К ), а

13133

с помощью третьего цифроаналогояого преобразователя 28 он преобразуется в аналоговый РИД y(t) и выдается в

приемное устройство (не показано).

Таким образом, в одной полосе частот разделено два направления передачи с совпадающими спектрами при наличии эхо-сигналов.

Формула изобретения

1. Устройство для разделения направлений передачи в дуплексных системах связи по авт.св. № 1133675, отличающееся тем, что, с целью повышения помехозащищенности введены адаптивный блок задержки, третий и четвертый блоки памяти, третий цифроаналоговый преобразователь, блок управления и последовательно соединенные блок формирования чисел, регистр сдвига, второй вычитатель, к второму входу которого подключен выход блока формирования чисел,вто- рой коммутатор, к управляющему входу которого подключен первый выход блока управления, третий вычитатель, ко второму входу которого подключен выход третьего блока памяти, и второй сумматор, выход которого подключен ко входу третьего цифроаналогового преобразователя и к первому сигнальному входу четвертого блока памяти, второй сигнальный вход которого сое- динен со вторым сигнальным входом третьего блока памяти, к первому сигнальному входу которого подключен выход второго коммутатора, со вторым входом регистра сдвига, с первым вхо- дом блока формирования чисел, ко второму входу которого подключен выход второго цифроаналогового преобразователя, с выходом генератора управляющих импульсов, который под- ключен к первому сигнальному входу адаптивного блока задержки, и с первым входом блока управления, первый, второй, третий и четвертый выходы которого подключены соответственно к первому управляющему входу третьего блока памяти, второй управляюгций вход которого соединен с выходом адаптивного блока задержки, к первому управляющему входу четвертого блока памя- ти, выход которого соединен со вторым входом второго сумматора и со вторым сигнальным входом адаптивного блока задержки, ко второму управляю

0

5 0 5 0 5 0 5 Q c

щему входу пррного коммутатора и к управляющему входу формирователя кодовых комбинаций, второй выход которого подключен к управляющему входу адаптивного блока задержки, информационный вход и выход которого соединены соответственно со вторым выходом блока согласования и со вторым управляющим входом четвертого блока памяти, при этом информационный вход второго коммутатора соединен с информационным входом второго блока памяти, установочный вход которого соединен со вторым входом блока уп- . равления.

2.Устройство по П.1, отличающееся тем, что адаптивный блок задержки содержит последовательно соединенные первый триггер, элемент И, первый счетчик, пороговый блок, второй триггер, второй счетчик и оперативный запоминающий блок, второй вход которого соединен со вторыми входами второго триггера, элемента И и второго счетчика и является первым сигнальным входом адаптивного блока задержки, вторым сигнальным входом которого является первый вход первого триггера, второй вход которого соединен с вторым входом первого счетчика и является управляющим входом адаптивного блока задержки, информационным входом и выходом которого являются соответственно третий вход и выход оперативного запоминающего блока, первый вход которого соединен с вторым входом порогового блока.

3.Устройство по П.1, отличающееся тем, что блок согласования содержит линию задержки и последовательно соединенные сумматор

по модулю два и постоянный запоминающий блок, второй вход которого соединен с первым входом линии задержки, второй вход и выход которой соединены соответственно с выходом и с первым входом сумматора по модулю два, второй вход которого является информационным входом блока согласования, управляющим входом и первым и вторьм выходами которого являются соответственно второй вход и выход постоянного запоминающего блока и выход сумматора по модулю два.

4. Устройство по П.1, отличающееся тем, что формирователь кодовых комбинаций содержит по15

следовательно соединенные элемент запрета, счетчик и постоянный запоминающий блок, выходы которого являются выходами формирователя кодовых комбинаций, входом которого является первый вход элемента запрета, ко второму входу которого подключен второй выход счетчика, второй вход которого является управляющим входом формирователя кодовых комбинаций.

5. Устройство по П.1, отличающееся тем, что блок управления содержит последовательно соединенные элемент запрета, счетчик и дешифратор, один выход которого подключен к первому входу элемента запрета, второй вход которого и второй вход счетчика являются соответствен2

но вторым и первым входами блока управления, выходами которого являются другие выходы дешифратора.

6, Устройство по П.1, отличающееся тем, что блок формирования чисел содержит последовательно соединенные усилитель-ограничитель, блок формирования значащих моментов, измерительный счетчик и блок буферной памяти, выход которого является выходом блока формирования чисел, первым и вторым входами которого являются соответственно второй вход измерительного счетчика, первый вход которого соединен с вторым входом блока буферной памяти, и вход усилителя-ограничителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1984 |

|

SU1223373A2 |

| Устройство разделения направлений передачи в дуплексных системах связи | 1988 |

|

SU1570001A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1390803A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2223599C2 |

Изобретение относится к технике электросвязи и обеспечивает повышение помехозащищенности. Устр-во содержит блок 1 сргласования, коммутаторы 2 и 15, ЦАП 3, 11, 28, АЦП 4, формирователь 5 кодовых комбинаций, четьфе блока 6, 10, 16, 18, г-р 7 управляющих импульсов, вычитатели 8, 14, 17, сумматоры 9 и 19, блок 12 формирования чисел, регистр 13 Сдвига, адаптивный блок 20 задержки, состоящий из триггеров 21 и 25, эл-та И 22, счетчиков 23 и 26, порогового блока 24 и оперативного запоминающего блока 27, блок 29 управления. 5 3 .п. ф-лы, бил. г (Л со со 1чЭ СЛ to N .t

Авторы

Даты

1987-08-23—Публикация

1986-03-12—Подача