зобретение относится к электроради- оизмерениям и может использоваться для определения частоты электрического сигнала с повышенной точностью в условиях воз- дей( твия помех.

звестен способ измерения средней частоты импульсов, заключающийся в форми- ров жии импульсов нормализованной амп 1итуды из входного сигнала, формировании временного интервала накопления (tH), заполнении интервала накопления им- пул1сами измеряемой частоты (1/Тх), подсчитывании числа импульсов измеряемой частоты (N) за интервал накопления (гн). рав- ногс N tH/Tx. Этот способ реализован в устройстве, содержащем формирователь входного сигнала, формирователь интервала накопления, ключ, счетчик, дешифратор и отсчетное устройство.

Основным недостатком известных способа и устройства является большое время измерения частоты, обусловленное тем, что фильтрация помех осуществляется за счет осреднения измеряемого сигнала в счетчике, что требует значительного времени, т.к. чем больший уровень помех, чем большее время требуется для осреднения сигнала.

Наиболее близким по технической сущности к заявляемому техническому решению является способ измерения частоты электрического сигнала, заключающийся в определении и запоминании мгновенных значений длительностей периодов измер яе- мого сигнала в пределах сформированного

-ч4 Ю CJ СО СО 00

временного интервала накопления, определении числа мгновенных значений, равных между собой длительностей периодов измеряемого электрического сигнала путем последовательного суммирования и последующего выделения наибольшей из всех полученных сумм и соответствующих ей длительности периода и частоты, которые и принимают за результат измерения.

Этот способ реализован в устройстве, содержащем формирователь импульсов, ключ, формирователь интервалов накопления, преобразователь временного интервала в код, блок управления, двухпортовое оперативное запоминающее устройство (ДПОЗУ) и блок выбора наибольшего.

Основным недостатком известного способа и устройства является большое время измерения, обусловленное тем, что поиск наибольшего из сумм производится во всем диапазоне измеряемых частот в каждом цикле измерения, и чем шире диапазон измеряемых частот, тем больше время требуется для поиска наибольшей суммы. Кроме того требуются большие аппаратурные затраты, т.к. чем шире диапазон измеряемых частот и выше, точность измерения, тем больше требуемое адресное пространство для блока выбора наибольшего и соответственно большая емкость ДПОЗУ.

Цель изобретения - уменьшение времени измерения частоты в условиях воздействия помех на измеряемый сигнал.

Поставленная цель достигается тем, что в известном способе, по которому определяют и запоминают мгновенные значения длительностей периодов измеряемого сигнала в пределах сформированного временного интервала накопления, определяют число мгновенных значений равных между собой длительностей периодов измеряемого электрического сигнала путем последовательного суммирования и выделяют наибольшую из всех полученных сумм и соответствующую ей длительность периода или частоту, производят формирование области накопления меньшей, чем диапазон измеряемых частот, и перемещают сформированную область накопления по диапазону измерения до момента обнаружения наибольшей суммы, отслеживают положе- ние области накопления путем запоминания положения наибольшей суммы относительно начала диапазона измерения и смещения области накопления на величину, соответствующую положению наибольшей суммы внутри области накопления.

Поставленная цель достигается также и тем, что обнаружение наибольшей суммы в диапазоне измеряемых частот производится путем последовательного изменения частоты дискретизации измеряемого сигнала, от величины, при которой диапазон измеряемых частот размещается в области накоп- ления, до величины, обеспечивающей заданную точность измерения.

Поставленная цель достигается также и тем, что в известное устройство для измерения частоты электрического сигнала, содер

жащее последовательно соединенные

формирователь входного сигнала, ключ и преобразователь временного интервала в код, состоящий из генератора тактовых импульсов, одновибратора, вход которого явлается входом преобразователя временного интервала в код, а выход через элемент И соединен со счетным входом счетчика, выход и вход обнуления которого являются соответственно выходом и входом

управления преобразователя временного интервала в код, а также формирователь интервала накопления, первый выход которого подключен к управляющему входу ключа, двухпортовое оперативное

запоминающее устройство, процессор, выход которого является выходом всего устройства, а также блок управления, состоящий из последовательно соединен- ных магистрального приемопередатчика и

счетчика данных, триггера флага и формирователя цикла обмена, вход которого подключен к выходу ключа, а первый и второй выходы соединены соответственно с входом предустановки и счетным входом счетчика данных, причем выход преобразователя временного интервала в код подключен к адресному входу первого порта двухпортового оперативного запоминающего устройства, входы-выходы данных

-и управления которого соединены соответственно с входами-выходами магистрально- го приемопередатчика и через первую шину управления с формирователем цикла обмена, выход формирователя цикла обмена через вторую шину управления подключен к входу управления преобразователя временного интервала в код, а вход счетчика данных соединен с информационным входом магистрального приемопередатчика, адресные входы, входы-выходы данных и управления второго порта двухпортового оперативного запоминающего устройства соединены соответственно с адресным входом, входами-выходами данных и управления процессора, второй выход формирователя интервалов накопления подключен к установочному входу триггера флага вход обнуления и выход которого соединены с соответствующими входами-выходами управления процессора.

дополнительно введены буферный регистр, делутельчастоты,второй и третий элементы И, причем сходы адреса, входы-выходы данных управления буферного регистра сое- дин.;ны с соответствующим выходом и вхо/ами-выходами процессора, а первый и второй информационные выходы буферногистра соединены соответственно с инмационным входом счетчика

бразователя временного интервала в

л входом управления делителя частоты,

которого соединен с выходом генератактовых импульсов, а выход - с втовходом первого элемента И. а второй

дсчетчика преобразователя временного р фор пре код вхо, тор; рым вых

го и нтервала в код соединен с первыми входам 1 второго и третьего элементов И, со вторым входом второго элемента И соединен) линия Чтение-запись первой шины управления, а выход второго элемента И соединен со входом Чтение-запись первого пэрта двухпортового оперативного запо- миьающего устройства, а второй вход третьего элемента И соединен с третьим вых вых вхо, рал

дом формирователя циклов обмена, а |Д третьего элемента И соединяется с ,ом направление передачи магиет- ного приемопередатчика.

Анализ известных технических решений не выявил решений, содержащих отличительные признаки заявляемого технического решения.

Сущность заявляемого способа измере- ния частоты заключается в увеличении быстродействия за смет сокращения времени поиска наиболее вероятного значения частоты, при этом сокращается требуемый объем 1амяти. Перемещение сформированной области накопления до момента обнаружения наибольшей суммы и корректировка ве- лимшы смещения позволяет сузить полдиапазон измерения, размещая его в заданном адресном пространстве что, соот- вет ггвенно уменьшает время измерения.

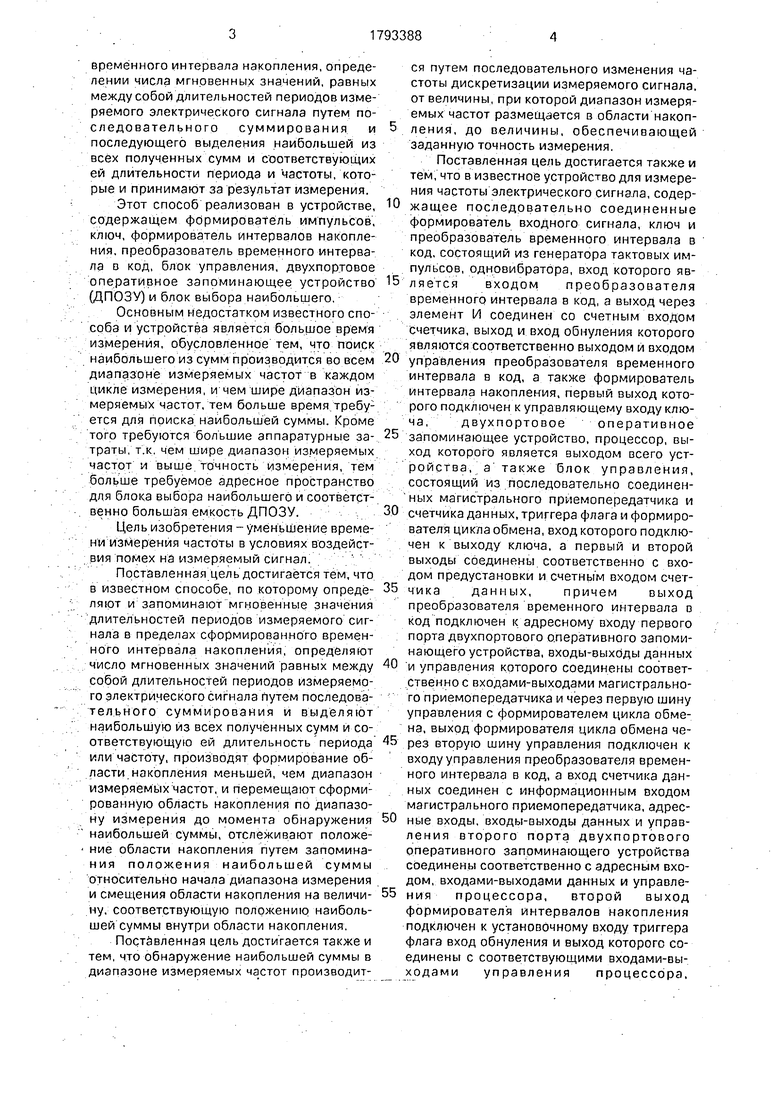

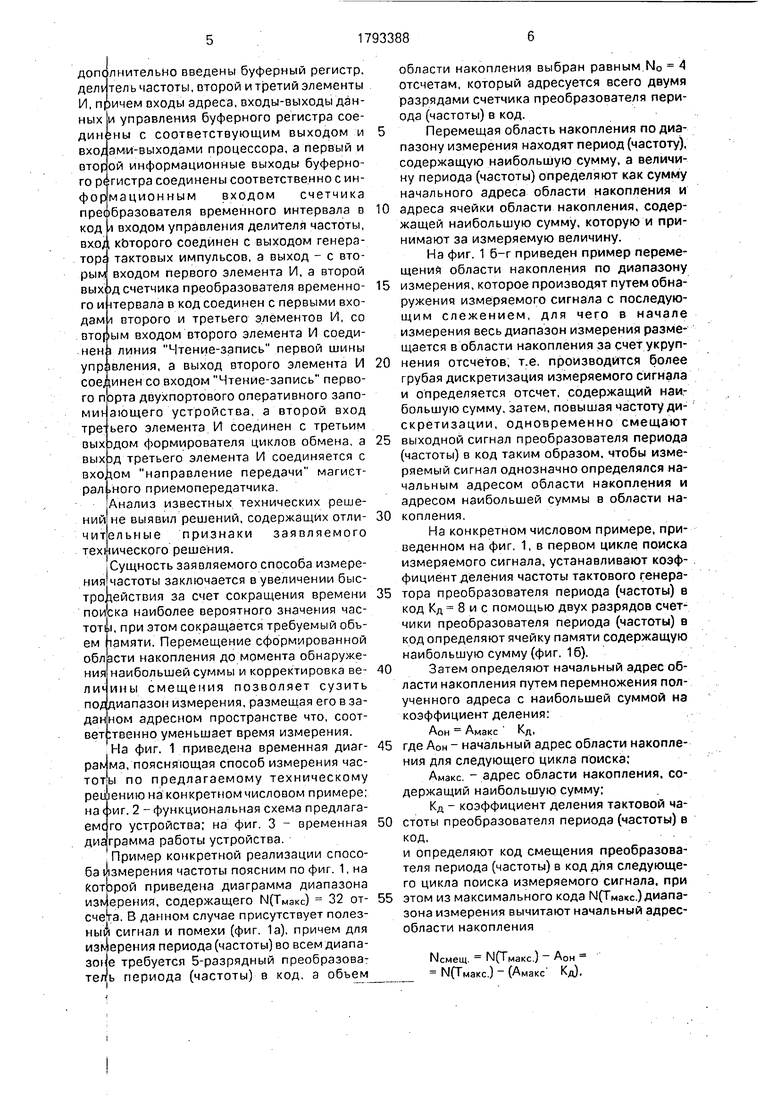

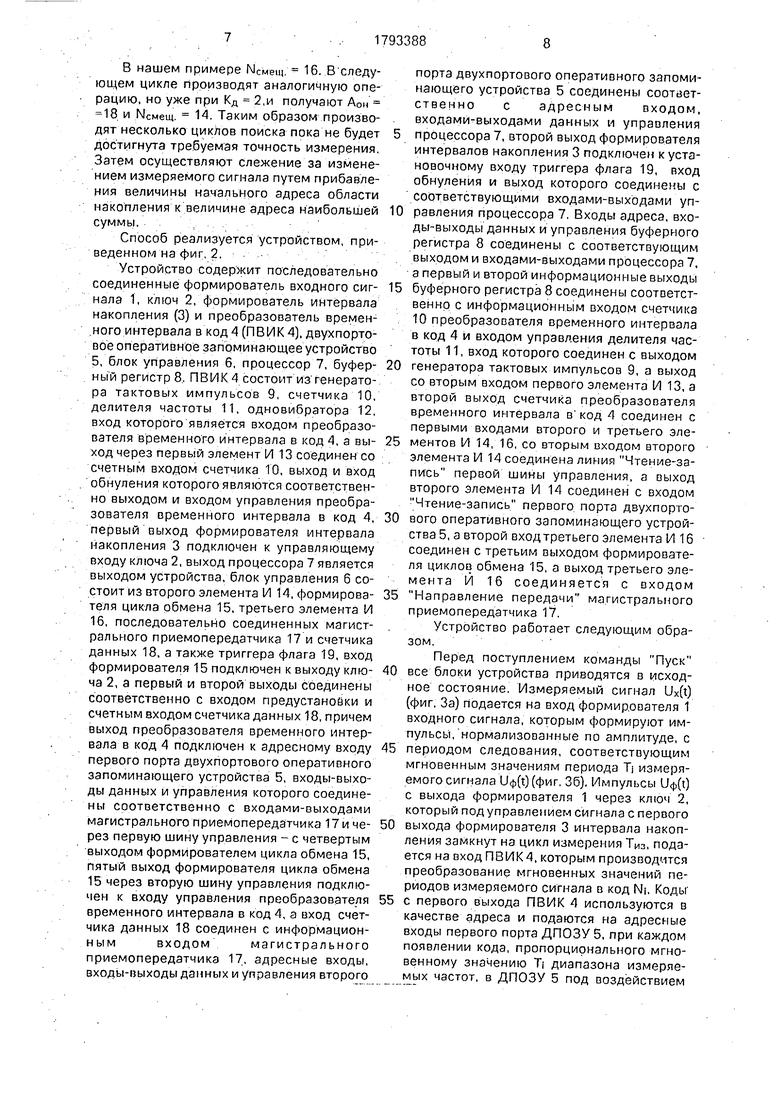

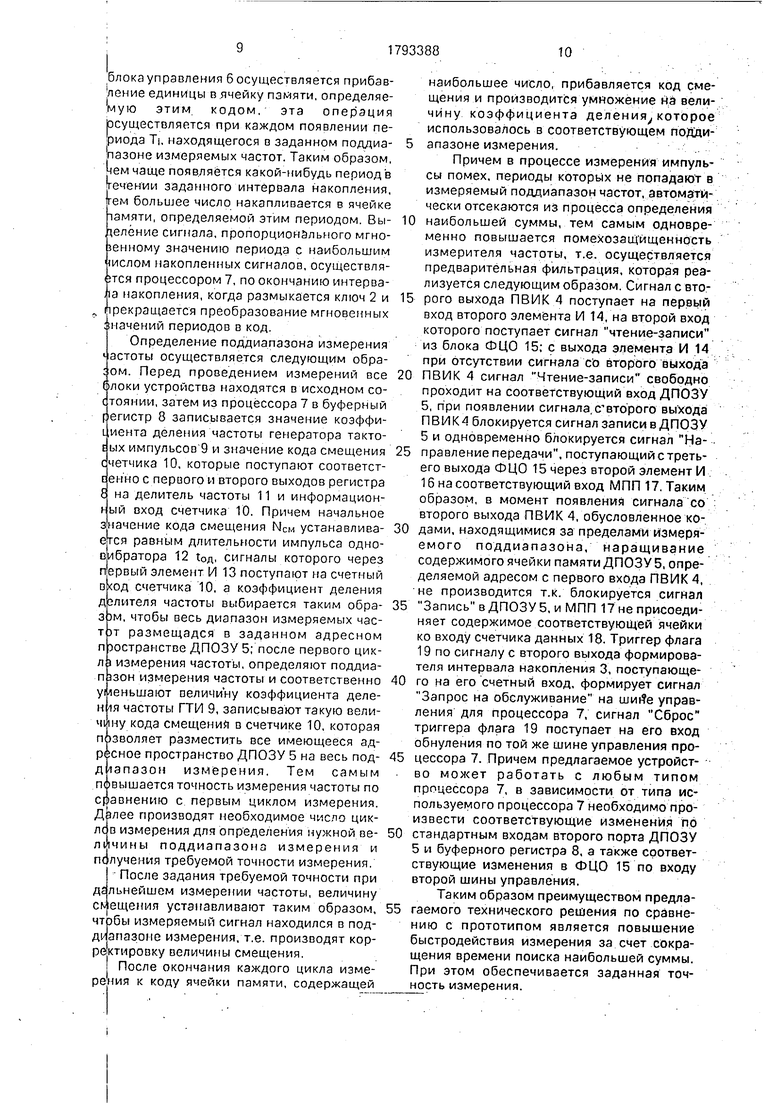

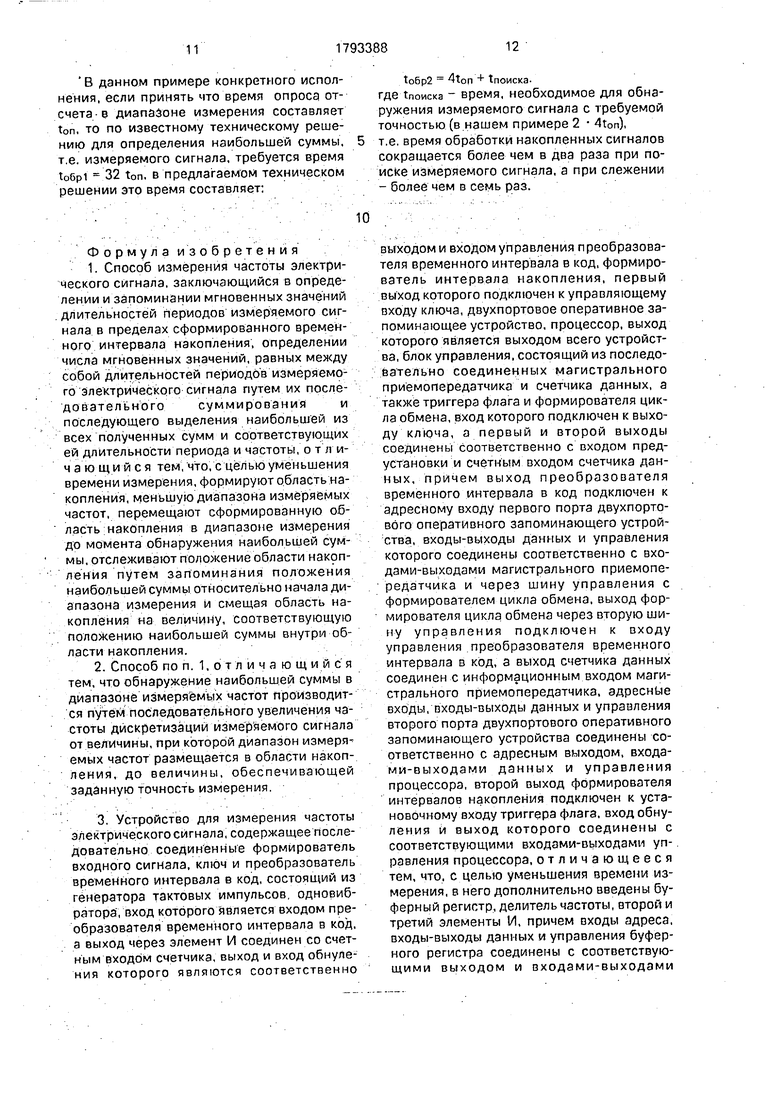

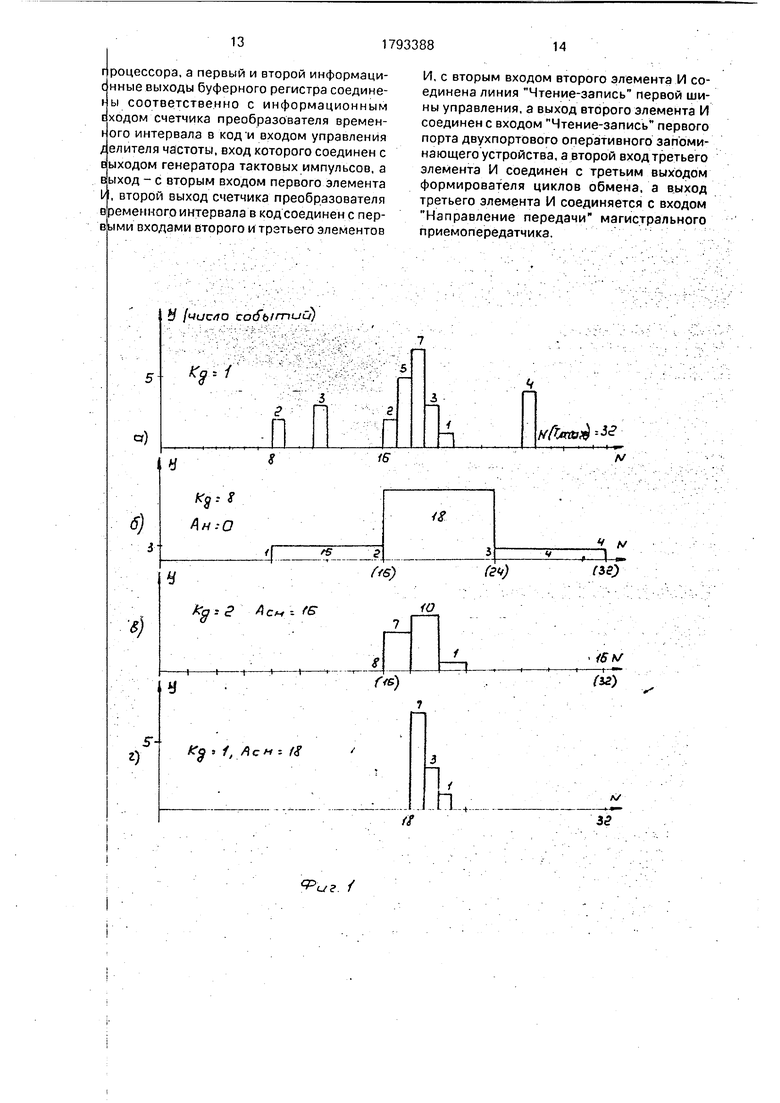

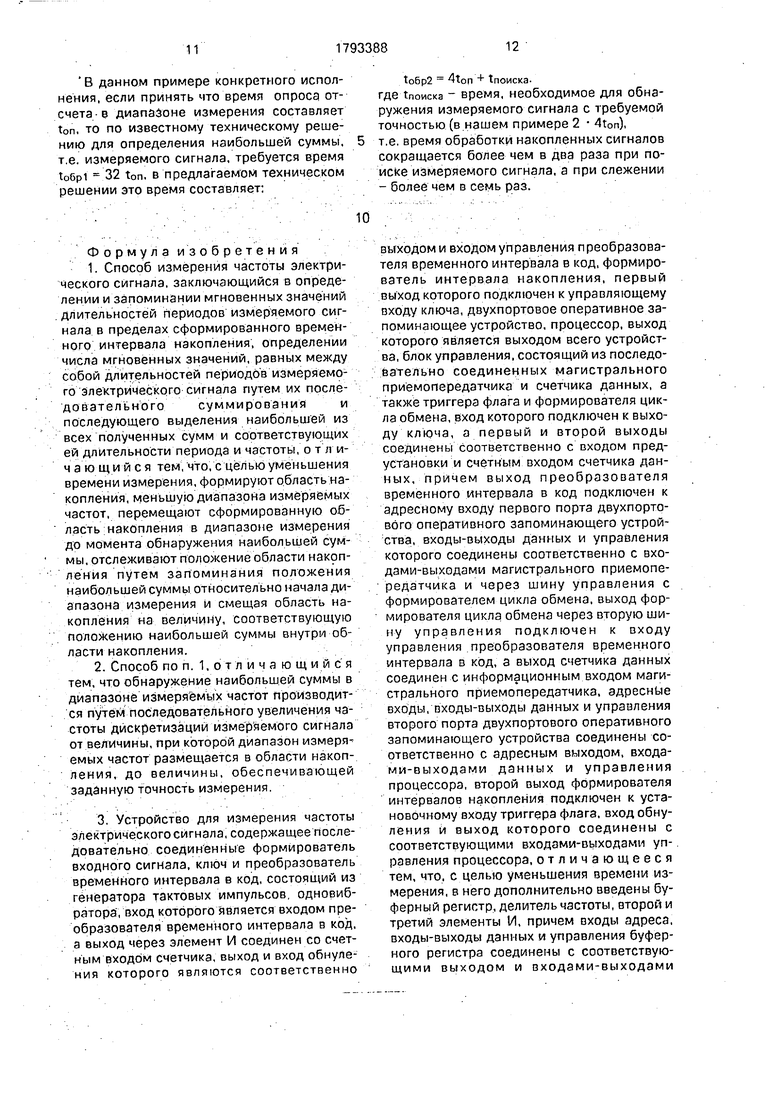

:На фиг. 1 приведена временная диаграмма, поясняющая способ измерения частоты по предлагаемому техническому решению на конкретном числовом примере; на иг. 2 - функциональная схема предлага- емс го устройства; на фиг. 3 - временная диаграмма работы устройства.

Пример конкретной реализации способа измерения частоты поясним по фиг. 1, на кот эрой приведена диаграмма диапазона измерения, содержащего М(ТМэкс) 32 отсчета. В данном случае присутствует полезный сигнал и помехи (фиг. 1а), причем для измерения периода (частоты) во всем диапазоне требуется 5-разрядный преобразователь периода (частоты) в код, а объем

области накопления выбран равным.N0 A отсчетам, который адресуется всего двумя разрядами счетчика преобразователя периода (частоты) в код.

5Перемещая область накопления по диапазону измерения находят период (частоту), содержащую наибольшую сумму, а величину периода (частоты) определяют как сумму начального адреса области накопления и

10 адреса ячейки области накопления, содержащей наибольшую сумму, которую и принимают за измеряемую величину.

На фиг. 1 б-г приведен пример перемещений области накопления по диапазону

5 измерения, которое производят путем обнаружения измеряемого сигнала с последующим слежением, для чего в начале измерения весь диапазон измерения размещается в области накопления за счетукруп0 нения отсчетов, т.е. производится более грубая дискретизация измеряемого сигнала и определяется отсчет, содержащий наибольшую сумму, затем, повышая частоту дискретизации, одновременно смещают

5 выходной сигнал преобразователя периода (частоты) в код таким образом, чтобы измеряемый сигнал однозначно определялся начальным адресом области накопления и адресом наибольшей суммы в области на0 копления.

На конкретном числовом примере, приведенном на фиг. 1, в первом цикле поиска измеряемого сигнала, устанавливают коэф- . фициент деления частоты тактового генера5 тора преобразователя периода (частоты) в код Кд 8 и с помощью двух разрядов счетчики преобразователя периода (частоты) в код определяют ячейку памяти содержащую наибольшую сумму (фиг. 16).

0Затем определяют начальный адрес области накопления путем перемножения полученного адреса с наибольшей суммой на коэффициент деления:

Аон Амакс Кд,

5 где Аон - начальный адрес области накопления для следующего цикла поиска;

Амакс. - адрес области накопления, содержащий наибольшую сумму;

Кд - коэффициент деления тактовой ча0 стоты преобразователя периода (частоты) в код, . . и определяют код смещения преобразователя периода (частоты) в код для следующего цикла поиска измеряемого сигнала, при

5 этом из максимального кода Ы(ТМакс.) диапазона измерения вычитают начальный адрес- области накопления

Мсмещ. М(Тмакс.) АОН N(TMaKC.) - (Амакс Кд).

В нашем примере Мсмещ. 16. В следующем цикле производят аналогичную операцию, но уже при Кд 2,и получают А0н 18 и Мсмещ. 14. Таким образом производят несколько циклов поиска пока не будет достигнута требуемая точность измерения. Затем осуществляют слежение за изменением измеряемого сигнала путем прибавления величины начального адреса области накопления к величине адреса наибольшей суммы. - ::. ...

Способ реализуется устройством, приведенном на фиг. 2.

Устройство содержит последовательно соединенные формирователь входного сигнала 1, ключ 2, формирователь интервала накопления (3) и преобразователь времен- .ного интервала в код 4 (П В И К 4), двухпортовое оперативное запоминающее устройство 5, блок управления 6, процессор 7, буферный регистр 8.. ПВИК 4 состоит из генератора тактовых импульсов 9, счетчика 10, делителя частоты 11, одновибратора 12, вход которого является входом преобразователя временного интервала в код 4, а выход через первый элемент И 13 соединен со счетным входом счетчика ТО, выход и вход обнуления которого являются соответственно выходом и входом управления преобразователя временного интервала в код 4, первый выход формирователя интервала накопления 3 подключен к управляющему входу ключа 2, выход процессора 7 является выходом устройства/блок управления 6 состоит из второго элемента И 14, формирователя цикла обмена 15, третьего элемента И 16, последовательно соединенных магистрального приемопередатчика 17 и счетчика данных 18, а также триггера флага 19, вход формирователя 15 подключен к выходу ключа 2, а первый и второй выходы соединены соответственно с входом предустаноеки и счетным входом счетчика данных 18, причем выход преобразователя временного интервала в код 4 подключен к адресному входу первого порта двухпортового оперативного запоминающего устройства 5, входы-выходы данных и управления которого соединены соответственно с входами-выходами магистрального приемопередатчика 17 и через первую шину управления - с четвертым выходом формирователем цикла обмена 15, пятый выход формирователя цикла обмена 15 через вторую шину управления подключен к входу управления преобразователя временного интервала в код 4, а вход счетчика данных 18 соединен с информационнымвходом магистрального приемопередатчика 17. адресные входы, входы-выходы данных и управления второго

порта двухпортового оперативного запоминающего устройства 5 соединены соответственно с адресным входом, входами-выходами данных и управления

процессора 7, второй выход формирователя интервалов накопления 3 подключен к установочному входу триггера флага 19, вход обнуления и выход которого соединены с соответствующими входами-выходами уп0 равления процессора 7. Входы адреса, входы-выходы данных и управления буферного регистра 8 соединены с соответствующим выходом и входами-выходами процессора 7, а первый и второй информационные выходы

5 буферного регистра 8 соединены соответственно с информационным входом счетчика 10 преобразователя временного интервала в код 4 и входом управления делителя частоты 11, вход которого соединен с выходом

0 генератора тактовых импульсов 9, а выход со вторым входом первого элемента И 13, а второй выход счетчика преобразователя временного интервала в код 4 соединен с первыми входами второго и третьего эле5 ментов И 14, 16, со вторым входом второго элемента И 14 соединена линия Чтение-запись первой шины управления, а выход второго элемента И 14 соединен с входом Чтение-запись первого порта двухпорто0 вого оперативного запоминающего устройства 5, а второй вход третьего элемента И 16 соединен с третьим выходом формирователя циклов обмена 15, а выход третьего элемента И 16 соединяется с входом

5 Направление передачи магистрального приемопередатчика 17.

Устройство работает следующим образом.

Перед поступлением команды Пуск

0 все блоки устройства приводятся в исходное состояние. Измеряемый сигнал Ux(t) (фиг. За) подается на вход формирователя 1 входного сигнала, которым формируют импульсы, нормализованные по амплитуде, с

5 периодом следования, соответствующим мгновенным значениям периода Т) измеряемого сигнала иф(г)(фиг, 36). Импульсы )(t) с выхода формирователя 1 через ключ 2, который под управлением сигнала с первого

0 выхода формирователя 3 интервала накопления замкнут на цикл измерения Тиз, подается на вход ПВИК 4, которым производится преобразование мгновенных значений периодов измеряемого сигнала в код NI. Коды

5 с первого выхода ПВИК 4 используются в качестве адреса и подаются на адресные входы первого порта ДПОЗУ 5, при каждом появлении кода, пропорционального мгновенному значению Т| диапазона измеряемых частот, в ДПОЗУ 5 под воздействием

блока управления 6 осуществляется прибавление единицы в.ячейку памяти, определяе- мую этим кодом, эта операция (осуществляется при каждом появлении периода TI, находящегося в заданном поддиа- пэзоне измеряемых частот. Таким образом, чем чаще появляется какой-нибудь период в течении заданного интервала накопления, тем большее число накапливается в ячейке тамяти, определяемой этим периодом. Выделение сигнала, пропорционального мгно- 5енному значению периода с наибольшим числом накопленных сигналов, осуществляется процессором 7, по окончанию интервала накопления, когда размыкается ключ 2 и прекращается преобразование мгновенных значений периодов в код.

Определение поддиапазона измерения 1 астоты осуществляется следующим обра- :ом. Перед проведением измерений все блоки устройства находятся в исходном состоянии, затем из процессора 7 в буферный регистр 8 записывается значение козффи- L иента деления частоты генератора такто- Е ых импульсов 9 и значение кода смещения счетчика 10, которые поступают соответст- сенно с первого и второго выходов регистра 8 на делитель частоты 11 и информацион- кый вход счетчика 10. Причем начальное значение кода смещения NCM устанавливается равным длительности импульса одно- оибратора 12 Год, сигналы которого через первый элемент И 13 поступают на счетный в код счетчика 10, а коэффициент деления дзлителя частоты выбирается таким обра- з )м, чтобы весь диапазон измеряемых час- т )т размещался в заданном адресном пространстве ДПОЗУ 5; после первого цик- л ) измерения частоты, определяют поддиа- п ззон измерения частоты и соответственно уменьшают величину коэффициента деле- н 1Я частоты ГТИ 9, записывают такую величину кода смещения в счетчике 10, которая позволяет разместить все имеющееся ад- росное пространство ДПОЗУ 5 на весь под- д 1эпазон измерения. Тем самым повышается точность измерения частоты по

ей

авнению с первым циклом измерения.

Далее производят необходимое число циклов измерения для определения нужной величины поддиапазонз измерения и получения требуемой точности измерения. - После задания требуемой точности при дальнейшем измерении частоты, величину смещения устанавливают таким образом, чтобы измеряемый сигнал находился в под- диапазоне измерения, т.е. производят корректировку величины смещения.

После окончания каждого цикла измерения к коду ячейки памяти, содержащей

наибольшее число, прибавляется код смещения и производится умножение на величину коэффициента деления которое использовалось в соответствующем поДди- 5 апазоне измерения...

Причем в процессе измерения импульсы помех, периоды которых не попадают в измеряемый поддиапазон частот, автоматически отсекаются из процесса определения 0 наибольшей суммы, тем самым одновременно повышается помехозащищенность измерителя частоты, т.е. осуществляется предварительная фильтрация, которая реализуется следующим образом. Сигнал свто- 5 рого выхода ПВИК .4 поступает на первый вход второго элемента И 14, на второй вход которого поступает сигнал чтение-записи из блока ФЦО 15; с выхода элемента И 14 при отсутствии сигнала со второго выхода

0 ПВИК 4 сигнал Чтение-записи свободно проходит на соответствующий вход ДПОЗУ 5, при появлении сигнала.с второго выхода П ВЙ К А блокируется сигнал записи в ДПОЗУ 5 и одновременно блокируется сигнал На- 5 правление передачи, поступающий с третьего выхода ФЦО 15 через второй элемент И 16 на соответствующий вход МПП 17. Таким образом, в момент появления сигнала со второго выхода ПВИК 4, обусловленное ко0 дами, находящимися за пределами измеряемого поддиапазона, наращивание содержимого ячейки памяти ДПОЗУ 5, определяемой адресом с первого входа ПВИК 4, не производится т.к. блокируется сигнал

5 Запись в ДПОЗУ 5, и МПП 17 не присоединяет содержимое соответствующей ячейки ко входу счетчика данных 18. Триггер флага 19 по сигналу с второго выхода формирователя интервала накопления 3, поступающе0 го на его счетный вход, формирует сигнал Запрос на обслуживание на шин е управления для процессора 7, сигнал Сброс триггера флага 19 поступает на его вход обнуления по той же шине управления про5 цессора 7. Причем предлагаемое устройство может работать с любым типом процессора 7, в зависимости от типа используемого процессора 7 необходимо произвести соответствующие изменения по

0 стандартным входам Второго порта ДПОЗУ 5 и буферного регистра 8, а также соответствующие изменения в ФЦО 15 по входу второй шины управления.

Таким образом преимуществом предла5 гаемого технического решения по сравнению с прототипом является повышение быстродействия измерения за счет сокращения времени поиска наибольшей суммы. При этом обеспечивается заданная точность измерения.

В данном примере конкретного исполнения, если принять что время опроса отсчета-в диапазоне измерения составляет ton, то по известному техническому решению для определения наибольшей суммы, т.е. измеряемого сигнала, требуется время to6pi .32 ton, в предлагаемом техническом решении это время составляет:

to6p2 - 4ton Поиска.

где tnoHCKa - время, необходимое для обнаружения измеряемого сигнала с требуемой точностью (в нашем примере 2 4ton), т.е. время обработки накопленных сигналов сокращается более чем в два раза при поиске измеряемого сигнала, а при слежении - более чем в семь раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| Цифровой измеритель длительности периода | 1988 |

|

SU1582176A1 |

| Устройство для ввода в электронную вычислительную машину величин измеряемых параметров быстропеременных и пульсирующих потоков жидкости и газа | 1986 |

|

SU1363177A2 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU894860A1 |

| Устройство для ввода в электронную вычислительную машину величин измеряемых параметров быстропеременных и пульсирующих потоков жидкости и газа | 1982 |

|

SU1054824A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

Изобретение относится к электроизме- penv ям и может использоваться для определен я частоты электрического сигнала с повь шенной точностью в условиях воздействия помех. Способ заключается в определен /и и запоминании мгновенных значений длительносчей периодов измеряемого сигнала в пределах сформированного временного интервала накопления, определении числа мгновенных значений равных между собой длительностей периодов измеряемого электрического сигнала путем последовательного суммирования и последующего выделения наибольшей из всех полученных сумм и соответствующих ей длительности периода и частоты, перемещения сформированной области накопления в диапазоне измерения до момента обнаружения наибольшей суммы, отслеживания положения области накопления путем запоминания положения наибольшей суммы относительно начала диапазона измерения и смещения области накопления на величину, соответствующего положению наибольшей суммы внутри области накопления. Устройство содержит: формирователь входного сигнала, ключ, преобразователь временного интервала в код, формирователь интервала накопления, двухпороговое оперативное запоминающее устройство, процессор. блок управления, буферный регистр. 3 ил. со с

. Формула и з обретения

выходом и входом управления преобразователя временного интервала в код, формирователь интервала накопления, первый выход которого подключен к управляющему входу ключа, двухпортовое оперативное запоминающее устройство, процессор, выход которого является выходом всего устройства, блок управления, состоящий из последовательно соединенных магистрального приемопередатчика и счетчика данных, а также триггера флага и формирователя цикла обмена, вход которого подключен к выходу ключа, а первый и второй выходы соединены соответственно с входом пред- установки и счетным входом счетчика данных, причем выход преобразователя временного интервала в код подключен к адресному входу первого порта двухпортового оперативного запоминающего устройства, входы-выходы данных и управления которого соединены соответственно с входами-выходами магистрального приемопередатчика и через шину управления с формирователем цикла обмена, выход формирователя цикла обмена через вторую шину управления подключен к входу управления преобразователя временного интервала в код, а выход счетчика данных соединен с информационным входом магистрального приемопередатчика, адресные входы, входы-выходы данных и управления второго порта двухпортового оперативного запоминающего устройства соединены соответственно с адресным выходом, входами-выходами данных и управления процессора, второй выход формирователя интервалов накопления подключен к установочному входу триггера флага, вход обнуления и выход которого соединены с соответствующими входами-выходами уп-. равления процессора, отличающееся тем, что. с целью уменьшения времени измерения, в него дополнительно введены буферный регистр, делитель частоты, второй и третий элементы 1/1, причем входы адреса, входы-выходы данных и управления буферного регистра соединены с соответствующими выходом и входами-выходами

г роцессора, а первый и второй информаци- с иные выходы буферного регистра соедине- ы соответственно с информационным Еходом счетчика преобразователя времен- юго интервала в код и входом управления / елителя частоты, вход которого соединен с выходом генератора тактовых импульсов, а выход - с вторым входом первого элемента второй выход счетчика преобразователя временного интервала в код соединен с первыми входами второго и третьего элементов

. /

И, с вторым входом второго элемента И соединена линия Чтение-запись первой шины управления, а выход второго элемента И соединен с входом Чтение-запись первого порта двухпортового оперативного запоминающего устройства, а второй вход третьего элемента И соединен с третьим выходом формирователя циклов обмена, а выход третьего элемента И соединяется с входом Направление передачи магистрального приемопередатчика.

I

&. c$

| Лебедка со свободным барабаном | 1934 |

|

SU45052A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-02-07—Публикация

1991-01-08—Подача