сд

Од 00

Изобретение относится к технике измерений и может быть использовано для контроля и диагностики амплитудно-частотной характеристики (АЧХ) усилительного тракта радиотелевизионной аппаратуры.

Цель изобретения - повышение точности контроля.

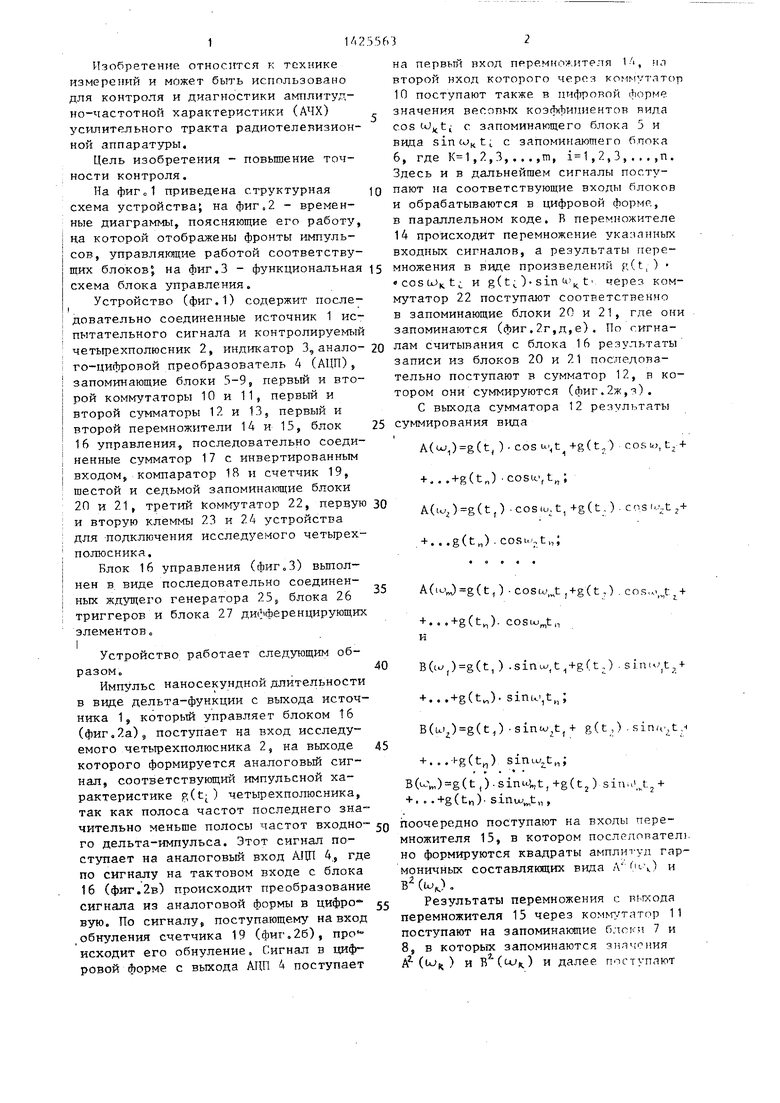

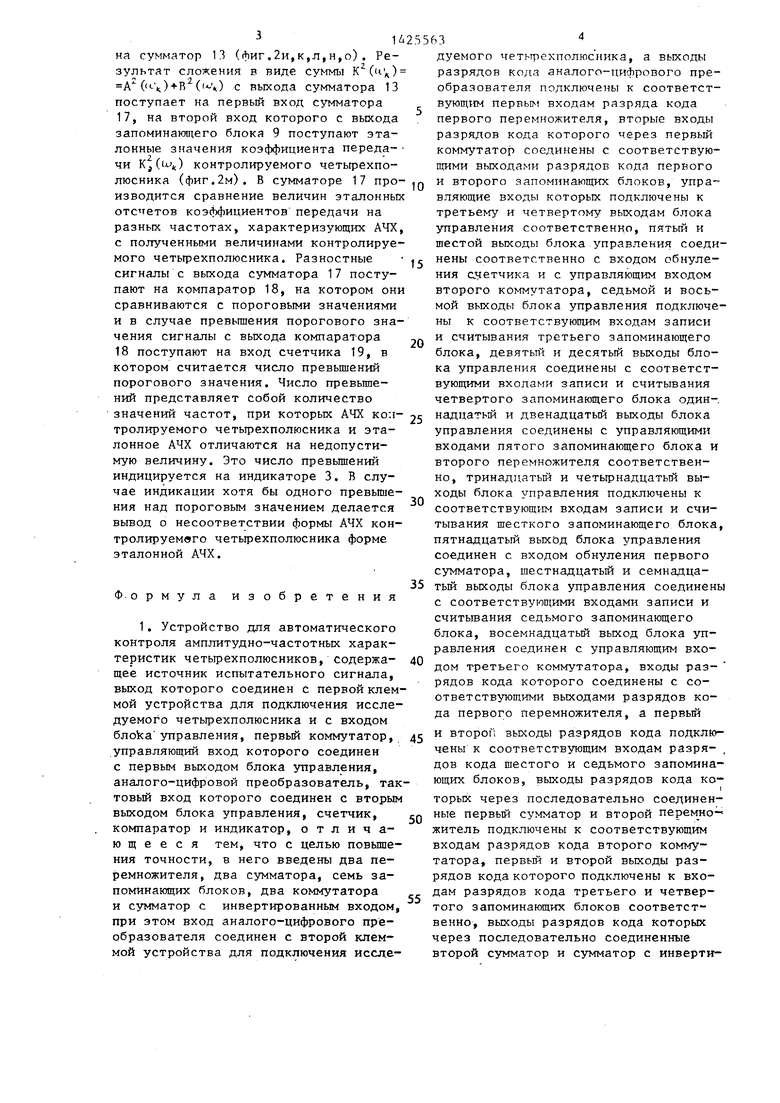

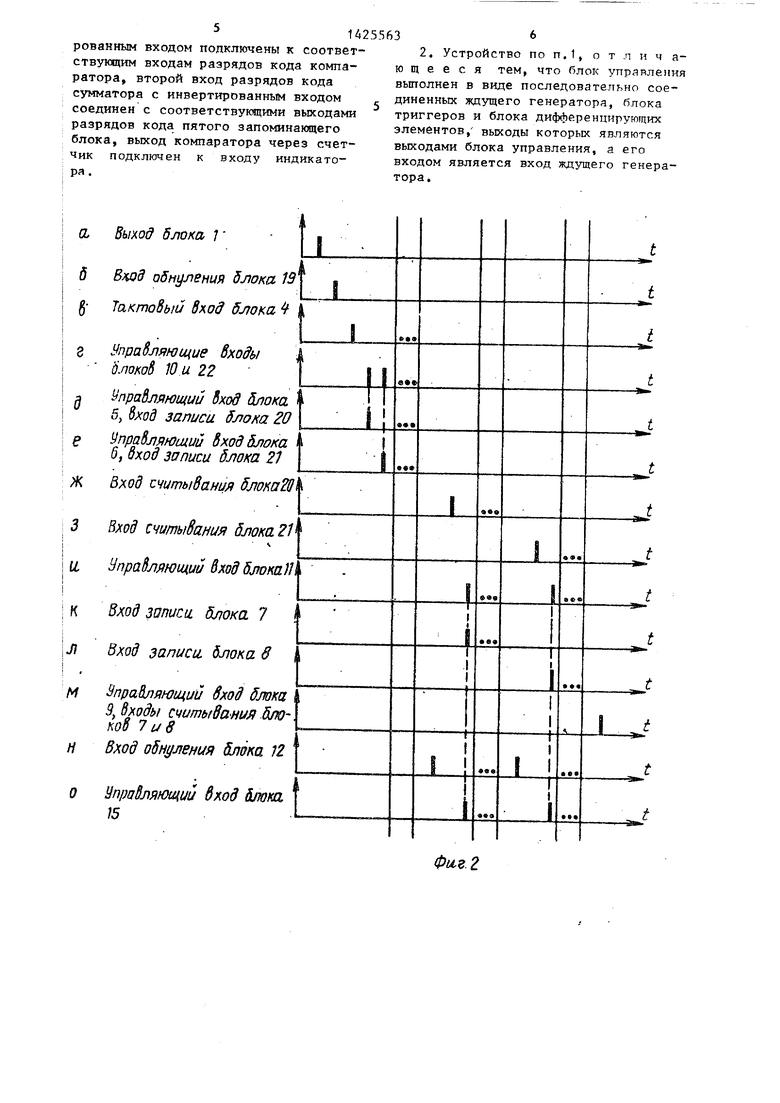

На фиг о 1 приведена структурная схема устройства; на фиг,2 - временные диаграммы, поясняющие его работу, на которой отображены фронты импуль- сов, управлягацие работой соответству- щих блоковJ на фиг.З - функциональная схема блока управления.

Устройство (фиг.1) содержит последовательно соединенные источник 1 испытательного сигнала и контролируемый четырехполюсник 2, индикатор 3, аналого-цифровой преобразователь 4 (АЦП), запоминающие блоки 5-9, первый и второй коммутаторы 10 и 11, первый и второй сумматоры 12 и 13, первый и второй перемножители 14 и 15, блок 16 управления, последовательно соединенные сумматор 17 с инвертированным входом, компаратор 18 и счетчик 19, шестой и седьмой запоминающие блоки 20 и 21, третий Коммутатор 22, первую и вторую клеммы 23 и 24 устройства для подключения исследуемого четырехполюсника.

Блок 16 управления (фиг.З) вьшол- нен в. виде последовательно соединенных ждущего генератора 25 блока 26 триггеров и блока 27 дифференцирующих элементов„ I

Устройство работает следующим образом

Импульс наносекундной длительности в виде дельта-функции с выхода источника 1, который управляет блоком 16 (фиг.2а), поступает на вход исследуемого четьфехполюсника 2, на выходе которого формируется аналоговый сигнал, соответствующий импульсной характеристике g(t;) четырехполюсника, так как полоса частот последнего значительно меньше полосы частот входного дельта-импульса. Этот сигнал поступает на аналоговый вход А1Щ 4., где по сигналу на тактовом входе с блока 16 (фиг.2в) происходит преобразование сигнала из аналоговой формы в цифровую. По сигналу, поступающему на вход обнуления счетчика 19 (фиг,26), происходит его обнуление, Сигнал в цифровой форме с выхода АЦП 4 поступает

на первый вход прремиожителя 1А, цл второй нход которого через коммутатор 10 поступают также в ци(|тровой форме

значения весовых коэф(Ьиииентов яида cos Wv;t С запоминающего блока 5 и вида с запоминающего блока 6, где ,2,3,,..,т, , 2, 3 , . , . ,п . Здесь и в дальнейшем сигналы поступают на соответствующие входы блоков и обрабатываются в цифровой форме., в параллельном коде. В перемножителе 14 происходит перемножение ука:итииых входных сигналов, а результаты перемножения в виде произведений j (t,) cosuj ;t: и g(t ) sin u;, t через коммутатор 22 поступают соответственно в запоминающие блоки 20 и 21, где они запоминаются (фиг.2г,д,е). По ситналам считывания с блока 16 результаты записи из блоков 20 и 21 последовательно поступают в сумматор 12, в котором они суммируются (фиг.2ж,). С выхода сумматора 12 результаты

суммирования вида

A(uj)g(t, ) cos u.t +g(t,,) COS10, t, +

30

f.. .+g(t J Cost ji ;

A(u,)g(t,) .COSlu,t, +g(t.) - COSIv.,t2 +

. + .. .g(t) . cosu.ut,,;

A((t,) . ,+g(t,) . +

+ ...+g(t). COSLo tn

и

B()g(t, ) .sinw,(t-,) . sinu; t.,-t- + .. .+g(t)- sinu ,t,;

B(ui)g(t) . sinw.,tj + g(t,) sinust.H

+ . ,.-i-g(t) ,

B(u.-)g(t,).sini.4,t,+g(tj) sinu j.j + + . . ,+g(tn)- sintu t,,,

поочередно поступают на входы перемножителя 15, в котором послелоиател, но формируются квадраты амплитуд гармоничных составляияцих вида Л ,) и В (ыО ,

Результаты перемножения с вьгхода перемножителя 15 через комьгутатор 11 поступают на запо шнающие блоки 7 и 8j в которых запоминаются знячония А ( ) и B(ujn) и далее поступают

на сумматор 13 (фиг.2и,к,л,н,о). Результат сложения в виде суммы K (u ) А ( )-t-R() с выхода сумматора 13 поступает на первый вход сумматора 17, на второй вход которого с выхода запоминающего блока 9 поступают эталонные значения коэффициента переда- чи K,( контролируемого четьфехпо- люсника (фиг.2м), В сумматоре 17 производится сравнение величин эталонных отсчетов коэффициентов передачи на разньк частотах, характеризующих АЧХ, с полученными величинами контролируемого четырехполюсника. Разностные сигналы с выхода сумматора 17 поступают на компаратор 18, на котором они сравниваются с пороговыми значениями и в случае превышения порогового значения сигналы с выхода компаратора 18 поступают на вход счетчика 19, в котором считается число превышений порогового значения. Число превышений представляет собой количество

0

5

0

дуемого четьгрехполюсника, а выходы разрядов кода аналого-цифрового преобразователя подключены к соответствующим первым входам разряда кода первого перемножителя, вторые входы разрядов кода которого через первый KONfMyTaTop соединены с соответствующими выходами разрядов кода первого и второго запоминающих блоков, управляющие входы которых подключены к третье гу и четвертому выходам блока управления соответственно, пятый и шестой выходы блока управления: соединены соответственно с входом обнуления счетчика и с управляющим входом второго коммутатора, седьмой и восьмой въкоды блока управления подключены к соответствующим входам записи и считывания третьего запоминающего блока, девятьш и десятый выходы блока управления соединены с соответствующими входами записи и считывания четвертого запоминающего блока один-.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1989 |

|

SU1608591A1 |

| Устройство для автоматического измерения амплитудно-частотных характеристик | 1986 |

|

SU1379749A1 |

| Устройство для контроля параметров | 1988 |

|

SU1665390A1 |

| Измеритель частотных характеристик четырехполюсника | 1988 |

|

SU1661679A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1635273A1 |

| Устройство для измерения частотных характеристик четырехполюсника | 1988 |

|

SU1661680A1 |

| Устройство для определения амплитудно-частотных характеристик электроэнергетических объектов | 1983 |

|

SU1320772A2 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

Изобретение может быть использовано для автоматического контроля и диагностики амплитудно-частотной характеристики (АЧХ) усилительного тракта радиотелевизионной аппаратуры. Устройство содержит источник 1 исполнительного сигнала, исследуемый четырехполюсник 2, коммутаторы 10,11, 22, аналого-цифровой преобразователь 4, счетчик 19, компаратор 18, индикатор 3, переменожители 14,15, сумматоры 12,13, запоминакяцие блоки 5-9, 20 и 21, сумматор 17 интертированным входом, блок 16 управления электрическая схема которого приведена в описании изобретения. Разностные сигналы с сумматора 17 поступают на компаратор 18, где сравниваются с пороговыми значениями. В случае превышения пороговых значений сигналы поступают на счетчик 19, в котором считывается число превьшений пороговьк значений. Число превьшений представляет количество значений частот, при которых АЧХ исследуемого четьфехпо- люсника и эталонное значение АЧХ отличаются на недопустимую величину, Число индуцируется на индикаторе 3, В случае индикации хотя бы одного превьшения над пороговым значением делается вывод о несоответствии формы АЧХ контролируемого четырехполюсника форме эталонной АЧХ. Устройство имеет повьшенную точность контроля. 1 3.п.ф-лы, 3 ил. с (Л

значений частот, при которых АЧХ коп- 25 надцатый и двенадцатый выходы блока

тролируемого четырехполюсника и эталонное АЧХ отличаются на недопустимую величину. Это число превьшгений индицируется на индикаторе 3. В случае индикации хотя бы одного превышения над пороговым значением делается вывод о несоответствии формы АЧХ контролируемого четырехполюсника форме эталонной АЧХ.

30

управления соединены с управляющими входами пятого запоминающего блока и второго перемножителя соответственно, тринадцатьй и четырнадцатый выходы блока управления подключены к соответствующим входам записи и считывания жесткого запоминающего блока пятнадцатый выход блока управления соединен с входом обнуления первого сумматора, шестнадцатый и семнадца- тьй выходы блока управления соединен с соответствующими входами записи и считывания седьмого запоминающего блока, восемнадцатый выход блока управления соединен с управляющим входом третьего коммутатора, входы разрядов кода которого соединены с соответствующими выходами разрядов кода первого перемножителя, а первый

Ф о рмула изобретения

блoka управления, первьй коммутатор, 45 второй выходы разрядов кода подклю- управляющий вход которого соединен с первым выходом блока управления, аналого-цифровой преобразователь, тактовый вход которого соединен с вторым выходом блока управления, счетчик, сп компаратор и индикатор, отличающееся тем, что с целью повьшхе- кия точности, в него введены два пе-

чены к соответствующим входам разря- , ДОН кода шестого и седьмого запоминающих блоков, выходы разрядов кода которых через последовательно соединенные первый сумматор и второй перем но- житель подключены к соответствующим входам разрядов кода второго коммутатора, первый и второй выходы разрядов кода которого подключены к входам разрядов кода третьего и четвертого запоминающих блоков соответственно, выходы разрядов кода которых через последовательно соединенные второй сумматор и сумматор с инверти-

ремножителя, два сумматора, семь запоминающих блоков, два коммутатора и сумматор с инвертированным входом, при этом вход аналого-цифрового преобразователя соединен с второй клеммой устройства для подключения иссде0

5

0

управления соединены с управляющими входами пятого запоминающего блока и второго перемножителя соответственно, тринадцатьй и четырнадцатый выходы блока управления подключены к соответствующим входам записи и считывания жесткого запоминающего блока, пятнадцатый выход блока управления соединен с входом обнуления первого сумматора, шестнадцатый и семнадца- тьй выходы блока управления соединены с соответствующими входами записи и считывания седьмого запоминающего блока, восемнадцатый выход блока управления соединен с управляющим входом третьего коммутатора, входы разрядов кода которого соединены с соответствующими выходами разрядов кода первого перемножителя, а первый

второй выходы разрядов кода подклю-

чены к соответствующим входам разря- , ДОН кода шестого и седьмого запоминающих блоков, выходы разрядов кода которых через последовательно соединенные первый сумматор и второй перем но- житель подключены к соответствующим входам разрядов кода второго коммутатора, первый и второй выходы разрядов кода которого подключены к входам разрядов кода третьего и четвертого запоминающих блоков соответственно, выходы разрядов кода которых через последовательно соединенные второй сумматор и сумматор с инверти-

51425563

рованным входом подключены к соответствующим входам разрядов кода компаратора, второй вход разрядов кода сумматора с инвертированным входом соединен с соответствугацими выходами разрядов кода пятого запоминающего блока, выход компаратора через счетчик подключен к входу индикатора.

0S бд е

ж

3 и,

j}

I

м

н о

Фи.е.2

t«i

«$

| Устройство для допускового контроля амплитудно-частотных характеристик четырехполюсников | 1980 |

|

SU938205A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-09-23—Публикация

1986-09-30—Подача