СЕ 00

о

Изобретение относится к измерительной технике, конкретно к средствам определения амплитудно-частотной характеристики (АЧХ) и характеристики группового времени запаздывания (ХГВЗ) нелинейных четырехполюсников, и может быть использовано при эксплуатации широкополосных систем связи с частотной модуляцией. Целью изобретения является повышение точности измерения.

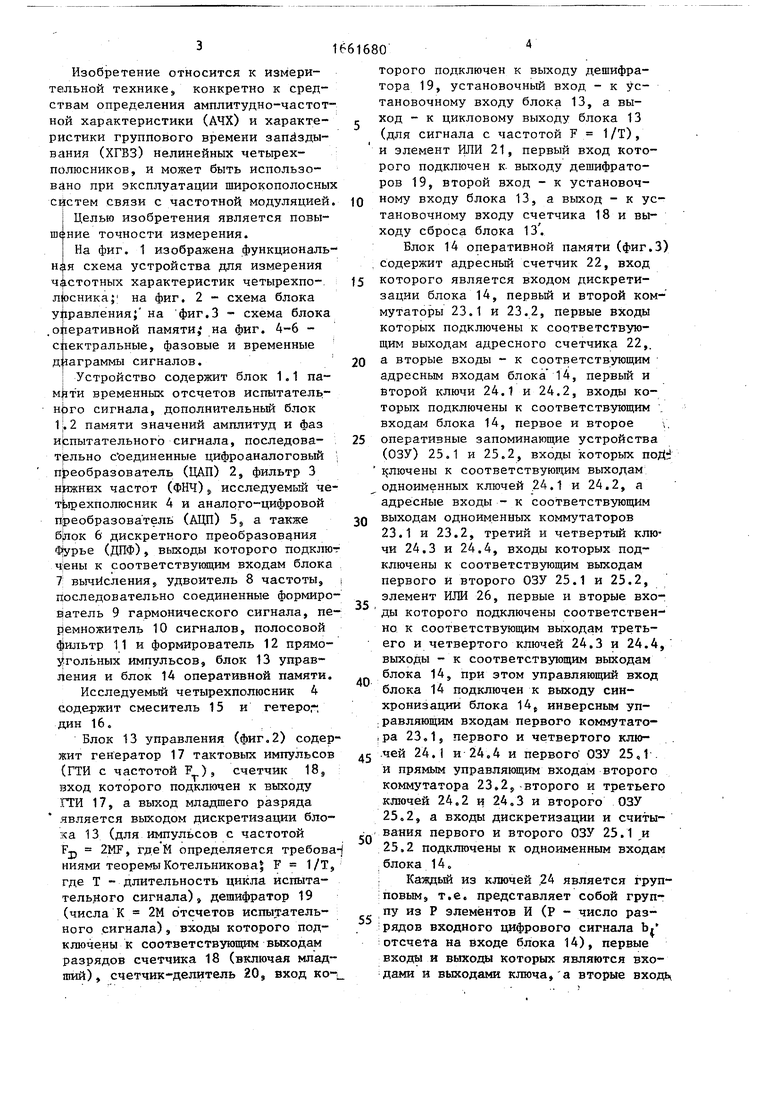

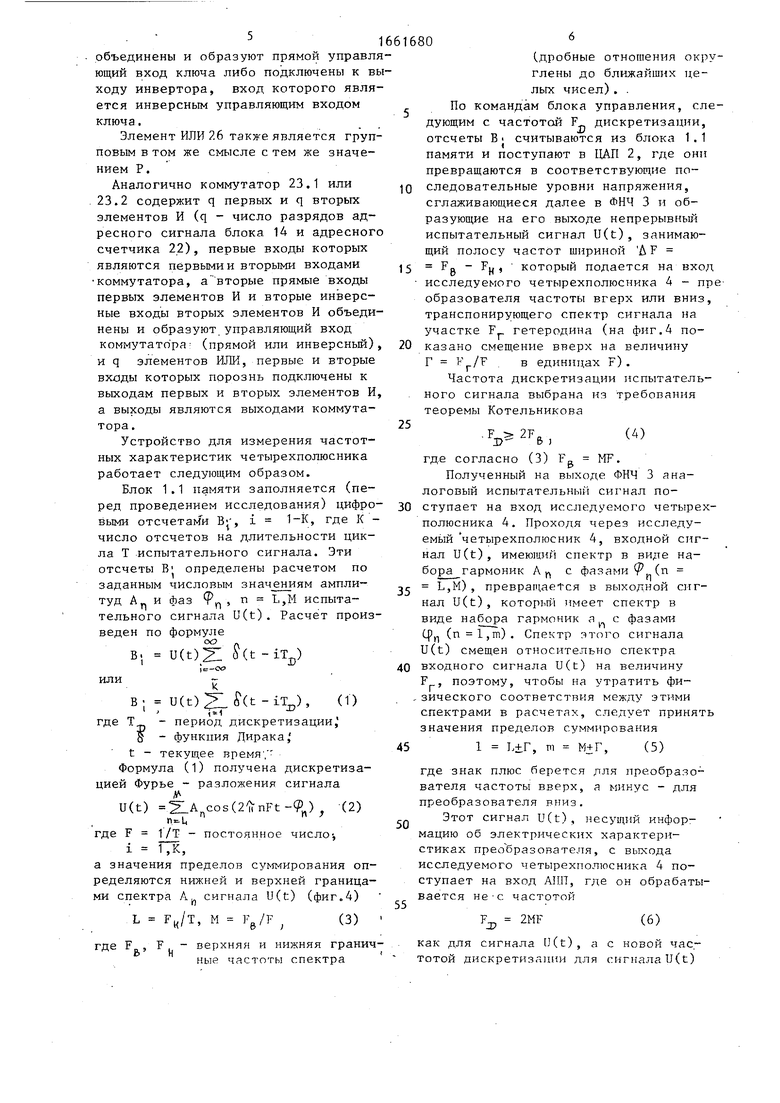

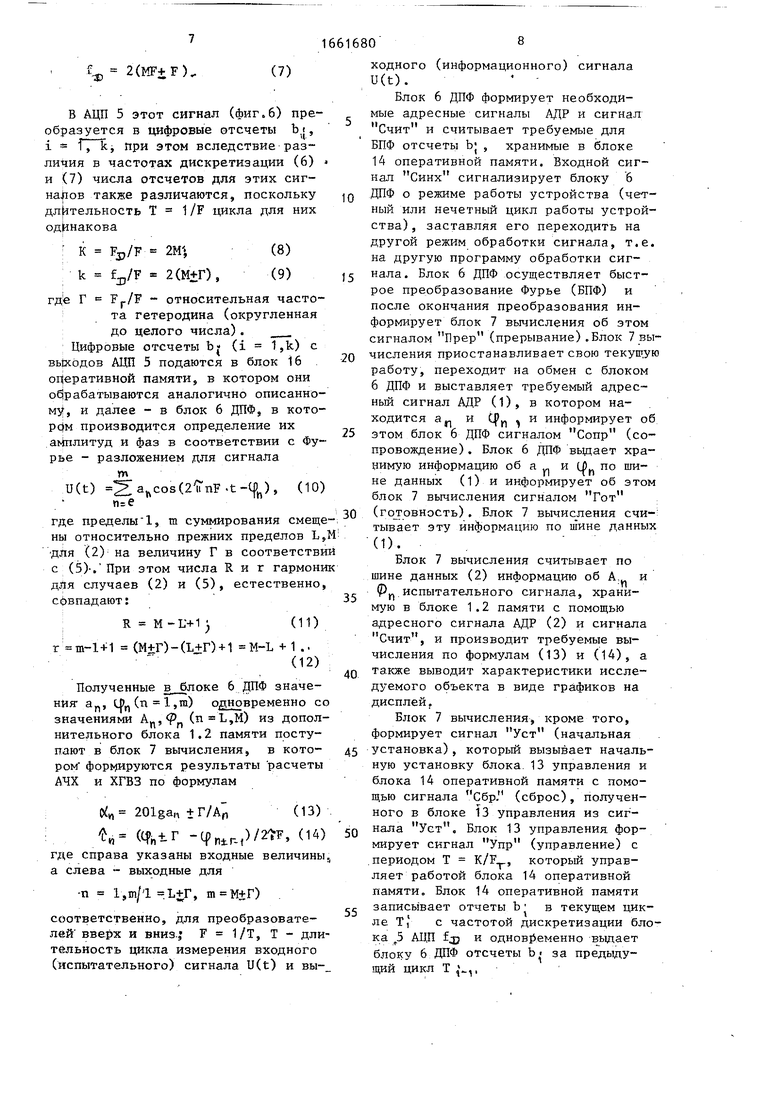

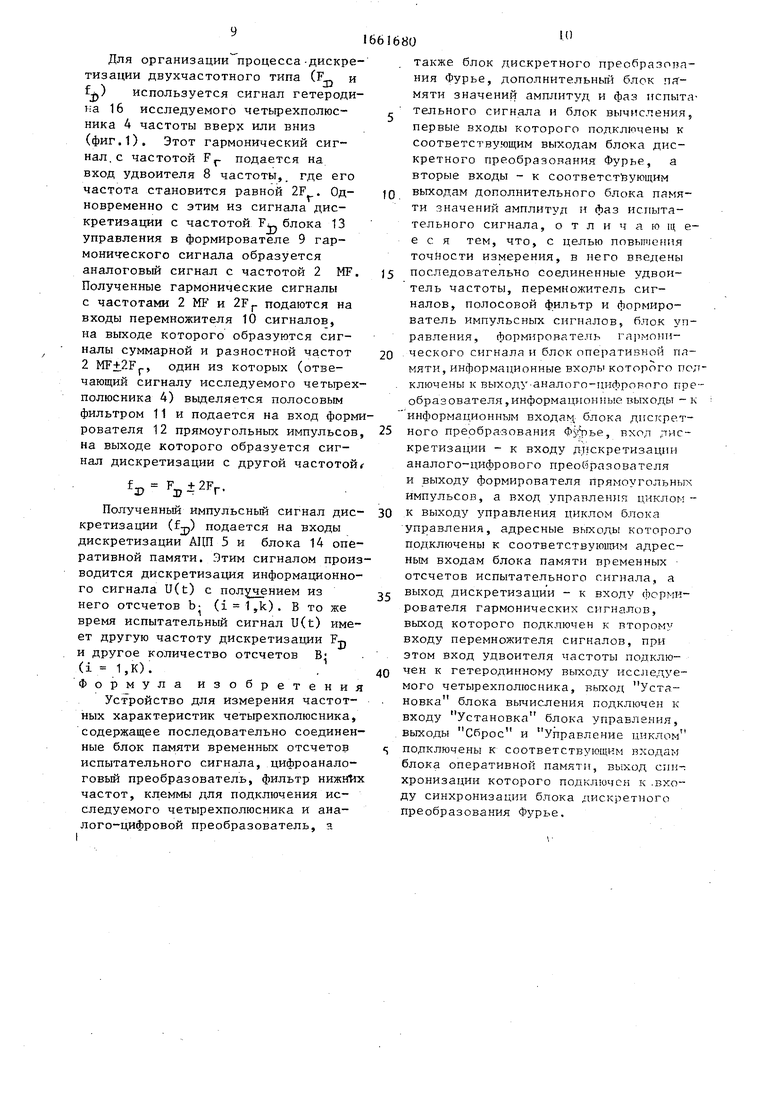

На фиг. 1 изображена функциональная схема устройства для измерения частотных характеристик четырехпо- л осника;1 на фиг. 2 - схема блока управления; на фиг.З - схема блока .оперативной памяти, на фиг. 4-6 - спектральные, фазовые и временные диаграммы сигналов.

Устройство содержит блок 1.1 па- временных отсчетов испытатель- HJDTO сигнала, дополнительный блок 1.2 памяти значений амплитуд и фаз испытательного сигнала, последовательно с оединенные цифроаналоговый преобразователь (ЦАП) 2, фильтр 3 нижних частот (ФНЧ) исследуемый четырехполюсник 4 и аналого-цифровой преобразователь (АЦП) 59 а также блок 6 дискретного преобразования Фурье (ДПФ), выходы которого подключены к соответствующим входам блока 7 вычисления5 удвоитель 8 частоты, последовательно соединенные формирователь 9 гармонического сигнала, перемножитель 10 сигналов, полосовой фильтр 11 и формирователь 12 прямоугольных импульсов, блок 13 управления и блок 14 оперативной памяти.

Исследуемый четырехполюсник 4 содержит смеситель 15 и гетерог, дин 16.

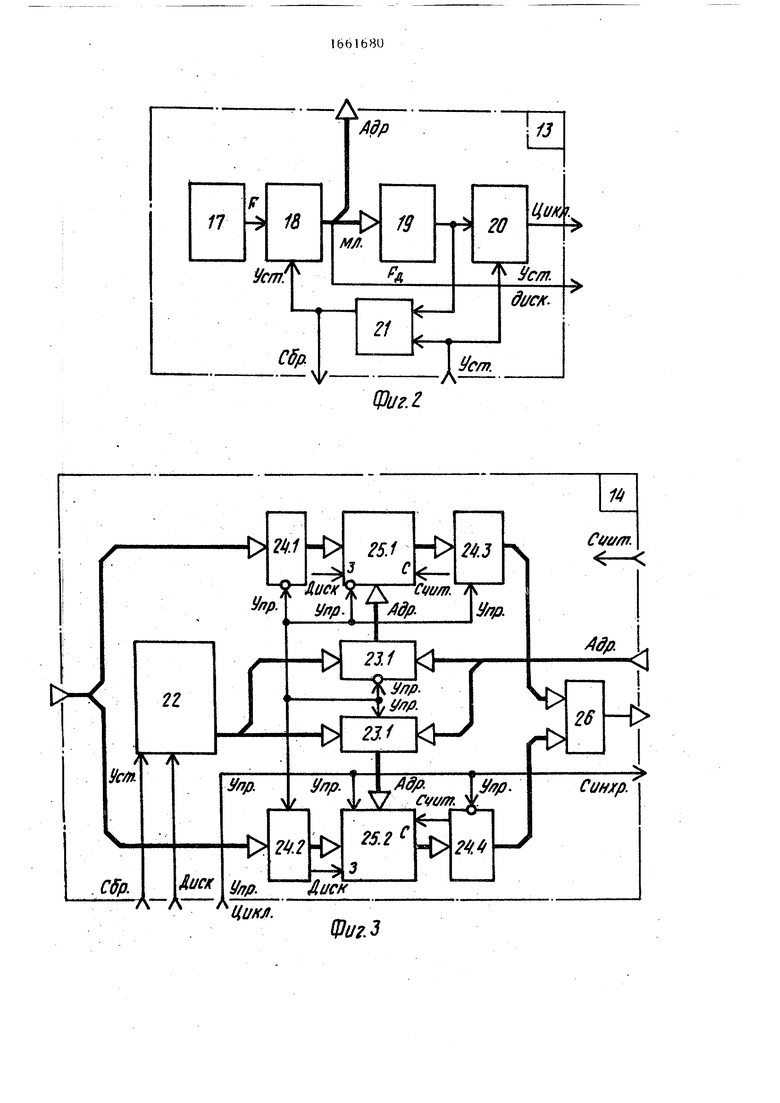

Блок 13 управления (фиг.2) содержит генератор 17 тактовых импульсов (ГТИ с частотой F ), счетчик 18Э вход которого подключен к выходу ГТИ 17, а выход младшего разряда является выходом дискретизации блока 13 (для импульсов с частотой 2MF, где М определяется требова ниями теоремы Котельникова| F 1/Т, где Т - длительность цикла испытательного сигнала), дешифратор 19 (числа К 2М отсчетов испытательного сигнала), входы которого подключены к соответствующим выходам разрядов счетчика 18 (включая младший), счетчик-делитель 209 вход ко

5

0

5

торого подключен к выходу дешифратора 19, установочный вход - к установочному входу блока 13, а выход - к цикловому выходу блока 13 (для сигнала с частотой F 1/Т), и элемент ИЛИ 21, первый вход которого подключен к выходу дешифраторов 19, второй вход - к установочному входу блока 13, а выход - к установочному входу счетчика 18 и выходу сброса блока 13.

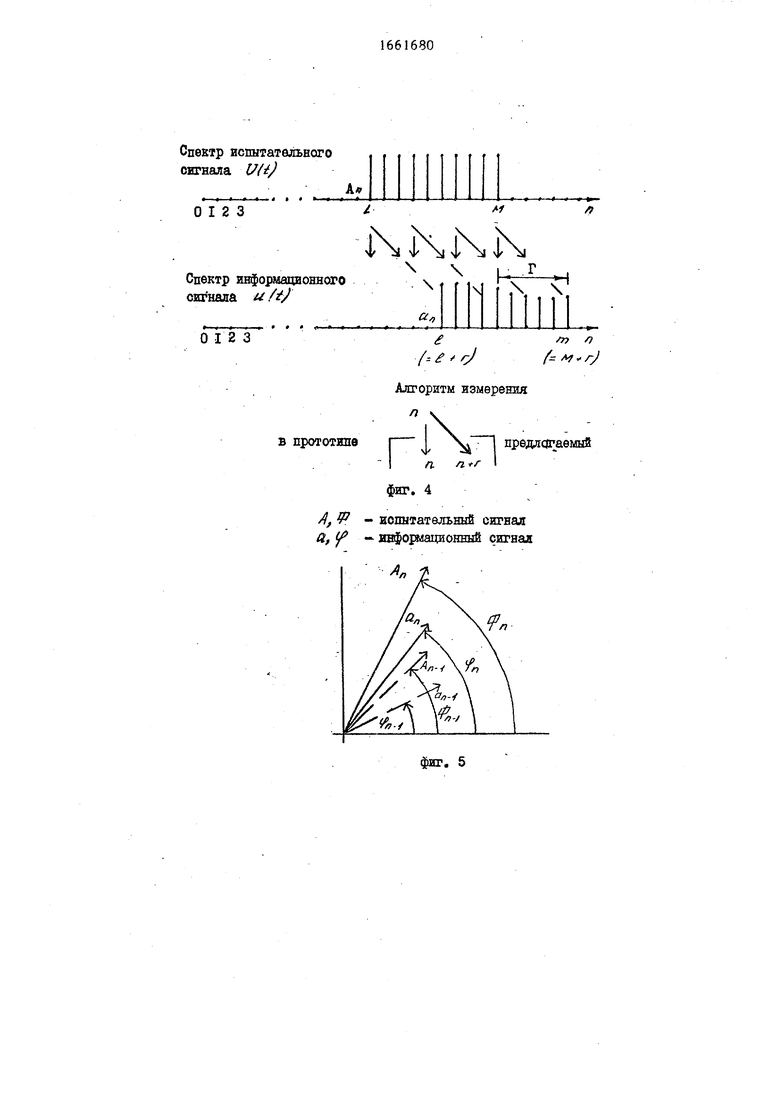

Блок 14 оперативной памяти (фиг.З) содержит адресный счетчик 22, вход которого является входом дискретизации блока 14, первый и второй коммутаторы 23.1 и 23.2, первые входы которых подключены к соответствующим выходам адресного счетчика 22,. а вторые входы - к соответствующим адресным входам блока 14, первый и второй ключи 24.1 и 24.2, входы которых подключены к соответствующим входам блока 14, первое и второе v оперативные запоминающие устройства (ОЗУ) 25.1 и 25.2, входы которых поД ключены к соответствующим выходам одноименных ключей 24.1 и 24.2, а адресные входы - к соответствующим выходам одноименных коммутаторов

23.1и 23.2, третий и четвертый ключи 24.3 и 24.4, входы которых подключены к соответствующим выходам первого и второго ОЗУ 25.1 и 25.2, элемент ИЛИ 26, первые и вторые входы которого подключены соответственно к соответствующим выходам третьего и четвертого ключей 24.3 и 24.4, выходы - к соответствующим выходам блока 14, при этом управляющий вход блока 14 подключен к выходу синхронизации блока 14„ инверсным управляющим входам первого коммутато-

,ра 23.1, первого и четвертого клю- 45 чей 24.1 и 24.4 и первого ОЗУ 25,1 и прямым управляющим входам второго коммутатора 23.2, второго и третьего ключей 24.2 и 24.3 и второго ОЗУ 25,2, а входы дискретизации и считывания первого и второго ОЗУ 25.1 и

25.2подключены к одноименным входам блока 14.

Каждый из ключей 24 является групповым, т.е. представляет собой группу из Р элементов И (Р - число разрядов входного цифрового сигнала bj отсчета на входе блока 14), первые входы и выходы которых являются входами и выходами ключа, а вторые входц

0

5

0

50

55

объединены и образуют прямой управлющий вход ключа либо подключены к входу инвертора, вход которого является инверсным управляющим входом ключа.

Элемент ИЛИ 26 также является групповым в том же смысле с тем же значением Р.

Аналогично коммутатор 23.1 или 23.2 содержит q первых и q вторых элементов И (q - число разрядов адресного сигнала блока 14 и адресног счетчика 22), первые входы которых являются первыми и вторыми входами коммутатора, а вторые прямые входы первых элементов И и вторые инверсные входы вторых элементов И объединены и образуют управляющий вход коммутатора (прямой или инверсный) и q элементов ИЛИ, первые и вторые входы которых порознь подключены к выходам первых и вторых элементов И а выходы являются выходами коммутатора.

Устройство для измерения частотных характеристик четырехполюсника работает следующим образом.

Блок 1.1 памяти заполняется (перед проведением исследования) цифровыми отсчетами В, I 1-К, где К - число отсчетов на длительности цикла Т испытательного сигнала. Эти отсчеты В1 определены расчетом по заданным числовым значениям амплитуд АП и

фаз фп , п 1,,М испытап

тельного сигнала U(t). Расчет произведен по формуле

00 ( В- U(t)ZI oCt-iV

илиВгде Т

U(t)

Ј(t-ir), (1)

Ј

- период дискретизации, g - функция Дирака, t - текущее время1, Формула (1) получена дискретизацией Фурье - разложения сигнала

U(t) LA cos(2ftnFt- P), (2)

, где F 1 /Т - постоянное число-,

i 1,К,

а значения пределов суммирования определяются нижней и верхней границами спектра

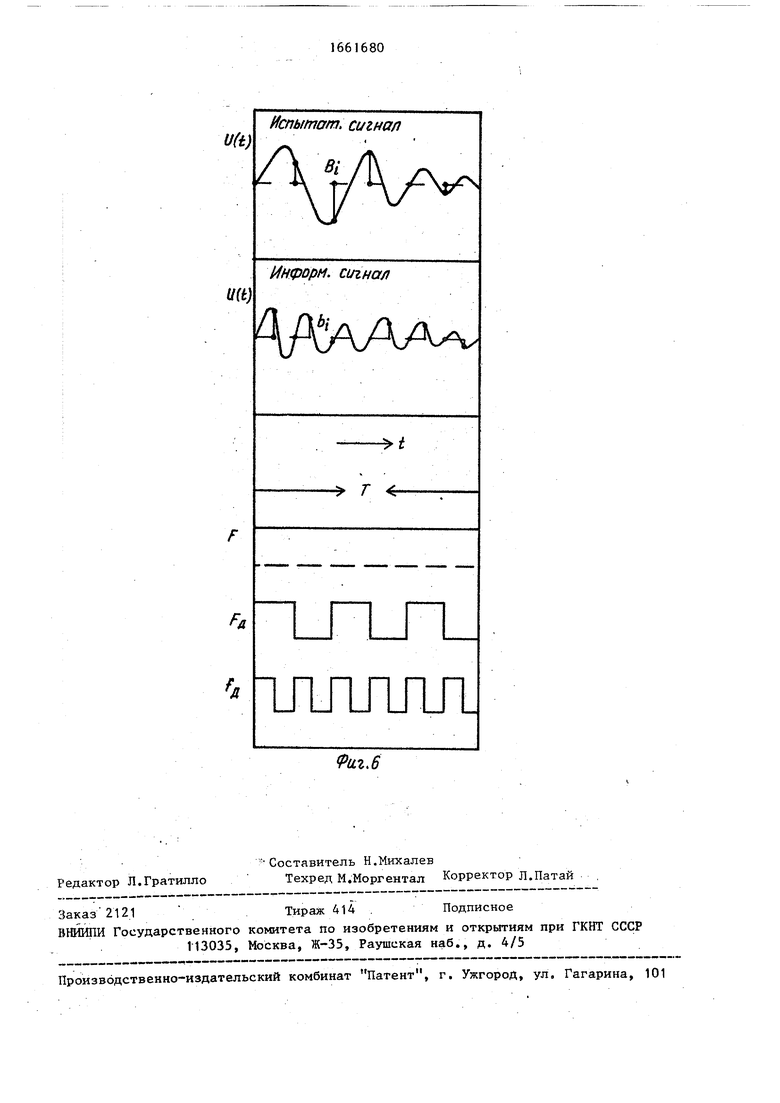

Лй сигнала U(t) (фиг.4)

L FjT, M

F

Б

К %F6/F

(3)

верхняя и нижняя граничные частоты спектра

0

5

(.дробные отношения округлены до ближайших целых чисел). .

По командам блока управления, следующим с частотой F дискретизации, отсчеты В- считываются из блока 1.1 памяти и поступают в ЦАП 2, где они превращаются в соответствующие последовательные уровни напряжения, сглаживающиеся далее в ФНЧ 3 и образующие на его выходе непрерывный испытательный сигнал U(t), занимающий полосу частот шириной Д F Fg - Гц, который подается на вход исследуемого четырехполюсника 4 - пре образователя частоты вгерх или вниз, транспонирующего спектр сигнала на участке F гетеродина (на фиг.4 показано смещение вверх на величину Г Fr/F в единицах F).

Частота дискретизации испытательного сигнала выбрана из требования теоремы Котельникова

2F,

(4)

-D 6 J

где согласно (3) Vu MF.

р

Полученный на выходе ФНЧ 3 аналоговый испытательный сигнал поступает на вход исследуемого четырехполюсника 4. Проходя через исследуемый четырехполюсник 4, входной сигнал U(t), имеющий спектр в виде набора гармоник А

п

с фазами Р (п

L,M), превращается в выходной сигнал U(t), который имеет спектр в виде набора гармоник а с фазами Cfn (,m). Спектр этого сигнала U(t) смещен относительно спектра входного сигнала U(t) на величину F , поэтому, чтобы на утратить физического соответствия между этими спектрами в расчетах, следует принять значения пределов суммирования

1 L+Г, тч М±Г, (5)

где знак плюс берется для преобразователя частоты вверх, а минус - для преобразователя вниз.

Этот сигнал U(t), несущий информацию об электрических характеристиках преобразователя, с выхода исследуемого четырехполюсника 4 поступает на вход AII1T, где он обрабатывается не с частотой

РЛ 2MF

как для сигнала U(t), a тотой дискретизации для

Гф 2(MF±Fb

(7)

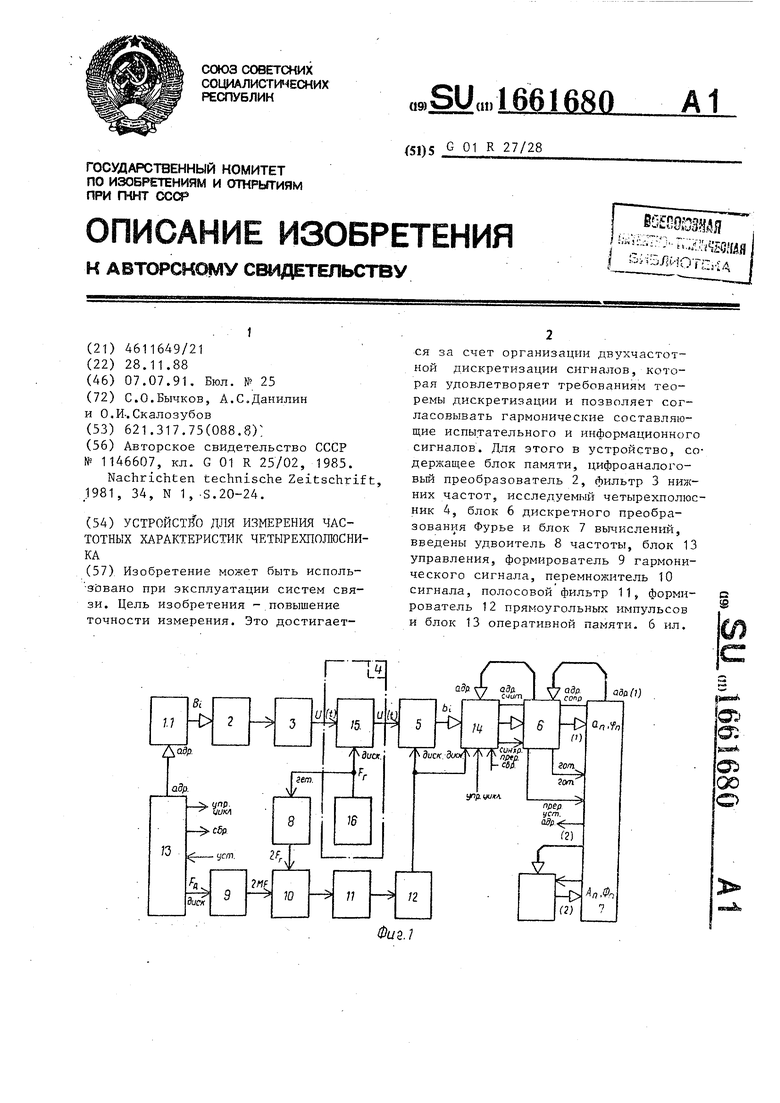

В АЦП 5 этот сигнал (фиг.6) преобразуется в цифровые отсчеты Ь(|, i Г, k, при этом вследствие различия в частотах дискретизации (6) и (7) числа отсчетов для этих сиг- на.ров также различаются, поскольку длительность Т 1/F цикла для них одинакова

(8) (9)

10

к FP/F 2щ

k f-p/F - 2(М±Г), где Г

15

Fr/F - относительная частота гетеродина (округленная

до целого числа)..

Цифровые отсчеты b« (i 1,k) с выходов АЦП 5 подаются в блок 16 оперативной памяти, в котором они обрабатываются аналогично описанному, и далее - в блок 6 ДПФ, в кото- ро|м производится определение их амплитуд и фаз в соответствии с Фурье - разложением для сигнала

w

U(t) a cosUfinF.t-Cp,,), (10)

где пределы 1, m суммирования смещены относительно прежних пределов L,M для (2) на величину Г в соответствии с (5)-. При этом числа R и г гармоник для случаев (2) и (5), естественно, совпадают:

6616808

ходного (информационного) сигнала U(t).

Блок 6 ДПФ формирует необходимые адресные сигналы АДР и сигнал Счит и считывает требуемые для БПФ отсчеты Ь , хранимые в блоке 14 оперативной памяти. Входной сигнал Синх сигнализирует блоку 6 ДПФ о режиме работы устройства (четный или нечетный цикл работы устройства) , заставляя его переходить на другой режим обработки сигнала, т.е. на другую программу обработки сигнала. Блок 6 ДПФ осуществляет быстрое преобразование Фурье (БПФ) и после окончания преобразования информирует блок 7 вычисления об этом сигналом Прер (прерывание) „Блок 7 вычисления приостанавливает свою текушую работу, переходит на обмен с блоком 6 ДПФ и выставляет требуемый адресный сигнал АДР (1), в котором находится а и и информирует об 25 этом блок 6 ДПФ сигналом Сопр (сопровождение) . Блок 6 ДПФ выдает хранимую информацию об а к Ц) по шине данных (1) и информирует об этом блок 7 вычисления сигналом Гот (готовность). Блок 7 вычисления считывает эту информацию по шине данных

(1).

Блок 7 вычисления считывает по

20

30

R M -U+1 )

(11)

т т-1-М (М+Г)-(Ь+Г)-М «M-L + 1 ..

(12)

Полученные в блоке 6 ДПФ значения- ап, (п 1,т) одновременно со значениями An,Pn (,M) из дополнительного блока 1.2 памяти поступают в блок 7 вычисления, в котором формируются результаты расчеты АЧХ и ХГВЗ по формулам

„ 201gan ±Г/А„(13)

„- ( , (14)

где справа указаны входные величины,, а слева - выходные для

п i,m/ l Ь+Г, m M+F)

соответственно, для преобразователей вверх и вниз, F 1/Т, Т - длительность цикла измерения входного (испытательного) сигнала U(t) и вы40

шине данных (2) информацию об А и ..г Рп испытательного сигнала, хранимую в блоке 1.2 памяти с помощью адресного сигнала АДР (2) и сигнала Счит, и производит требуемые вычисления по формулам (13) и (14), а также выводит характеристики исследуемого объекта в виде графиков на дисплей f

Блок 7 вычисления, кроме того, формирует сигнал Уст (начальная 45 установка), который вызывает начальную установку блока 13 управления и блока 14 оперативной памяти с помощью сигнала Сбр. (сброс), полученного в блоке 13 управления из сигнала Уст. Блок 13 управления формирует сигнал Упр (управление) с периодом Т K/FT, который управляет работой блока 14 оперативной памяти. Блок 14 оперативной памяти -с записывает отчеты b в текущем цикле Т,1 с частотой дискретизации блока 5 А1Ш fjj и одновременно выдает блоку 6 ДПФ отсчеты Ь за предыдущий цикл Т {,,

50

Для организации процесса-дискретизации двухчастотного типа (F и 10) используется сигнал гетероди- ьа 16 исследуемого четырехполюсника 4 частоты вверх или вниз (фиг.1). Этот гармонический сигнал, с частотой Fr подается на вход удвоителя 8 частоты, где его частота становится равной 2F . Одновременно с этим из сигнала дискретизации с частотой F- блока 13 управления в формирователе 9 гармонического сигнала образуется аналоговый сигнал с частотой 2 MF. Полученные гармонические сигналы с частотами 2 MF и 2Fr подаются на входы перемножителя 10 сигналов, на выходе которого образуются сигналы суммарной и разностной частот 2 MFi.Fr, один из которых (отвечающий сигналу исследуемого четырехполюсника 4) выделяется полосовым фильтром 11 и подается на вход формирователя 12 прямоугольных импульсов, на выходе которого образуется сигнал дискретизации с другой частотойг

f3 Fs±2Fr.

Полученньй импульсный сигнал дискретизации (f.p) подается на входы дискретизации АЦП 5 и блока 14 оперативной памяти. Этим сигналом производится дискретизация информационного сигнала U(t) с полу чением из него отсчетов b- (i 1,k). В то же время испытательный сигнал U(t) имеет другую частоту дискретизации F-p

В:

и другое количество отсчетов

(i 1,К).

Формула изобретения Устройство для измерения частотных характеристик четырехполюсника, содержащее последовательно соединенные блок памяти временных отсчетов испытательного сигнала, цифроанало- говый преобразователь, фильтр нижних частот, клеммы для подключения исследуемого четырехполюсника и аналого-цифровой преобразователь, ч

10

15

661680 °

также блок дискретного преобразования Фурье, дополнительный блок памяти значений амплитуд и фаз испытательного сигнала и блок вычисления, первые входы которого подключены к соответствующим выходам блока дискретного преобразования Фурье, а вторые входы - к соответствующим выходам дополнительного блока памяти значений амплитуд и фаз испытательного сигнала, отличающееся тем, что, с целью повышения точности измерения, в него введены последовательно соединенные удвоитель частоты, перемножитель сигналов, полосовой фильтр и формирователь импульсных сигналов, бпок управления, формирователь iармопн- ческого сигнала и блок оперативной памяти, информационные входы которого подключены к выходу аналого-цифрового преобразователя,информационные выходы - к информационным входам блока дискретного преобразования , вход дискретизации - к входу дискретизации аналого-цифрового преобразователя и выходу формирователя прямоугольны импульсов, а вход управление циклом - к выходу управления циклом бпока управления, адресные выходы которого подключены к соответствующим адресным входам блока памяти временных отсчетов испытательного сигнала, а выход дискретизации - к входу Формирователя гармонических сигналов, выход которого подключен к втором входу перемножителя сигналов, при этом вход удвоителя частоты подключен к гетеродинному выходу исследуемого четырехполюсника, выход Уста20

25

30

35

40

новка блока вычисления подключен к входу Установка блока управления, выходы Сброс и Управление циклом подключены к соответствующим входа - блока оперативной памяти, выход синхронизации которого подключен к входу синхронизации блока дискретного преобразования Фурье,

(Риг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель частотных характеристик четырехполюсника | 1988 |

|

SU1661679A1 |

| Устройство для временного и спектрального анализа сигналов | 1990 |

|

SU1793445A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1501085A1 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Цифровой панорамный измеритель частоты | 1985 |

|

SU1296955A1 |

| Устройство для определения частотных характеристик четырехполюсников | 1985 |

|

SU1308941A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1727131A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

Изобретение может быть использовано при эксплуатации систем связи. Цель изобретения - повышение точности измерения. Это достигается за счет организации двухчастотной дискретизации сигналов, которая удовлетворяет требованиям теоремы дискретизации и позволяет согласовать гармонические составляющие испытательного и информационного сигналов. Для этого в устройство, содержащее блок памяти, цифроаналоговый преобразователь 2, фильтр 3 нижних частот, исследуемый четырехполюсник 4, блок 6 дискретного преобразования Фурье и блок 7 вычислений, введены удвоитель 8 частоты, блок 13 управления, формирователь 9 гармонического сигнала, перемножитель 10 сигнала, полосовой фильтр 11, формирователь 12 прямоугольных импульсов и блок 13 оперативной памяти. 6 ил.

Щи.3

Спектр испытательного сигнала U(4}

0123

Спектр информационного сигнала и /tj

в

0123

в прототипе

Af Ф - испытательный сигнал и, (/ - информационный сигнал

f-1

а«

Ј

(-;

Алгоритм измерения

/7

sr О + rj

I п. п+г I

предлагаемый

фиг. 4

Р

фиг 5

U(t)

Испытат. сигнал

Инфйрм. сигнал

ед

ДАА/w

-5 Т ишллл

| Устройство для измерения группового времени запаздывания тракта промежуточной частоты понижающих преобразователей частоты СВЧ диапазона | 1982 |

|

SU1146607A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Nachrichten technische Zeitschrift, ,1981, 34, N 1 , S.20-24. | |||

Авторы

Даты

1991-07-07—Публикация

1988-11-28—Подача