О5

о

о

vJ

соИзобретение относится к измери- тельной технике, конкретно к средствам определения амплитудно-частотной характеристики (АЧХ) и ха- рактеристики группового времени запаздывания (ХГВЗ) нелинейных четырехполюсников, и может быть исполь- зовано при эксплуатации широкополосных систем связи с частотной мо- дуляцией.

Целью изобретения является повы- Ление точности измерения за счет Организации двухчастотной дискретизации сигналов, которые удовлетво- ряют требованиям теоремы КотельникоН Ва и позволяют физически согласовать .Гармонические составляющие испытательного и информационного сигналов.

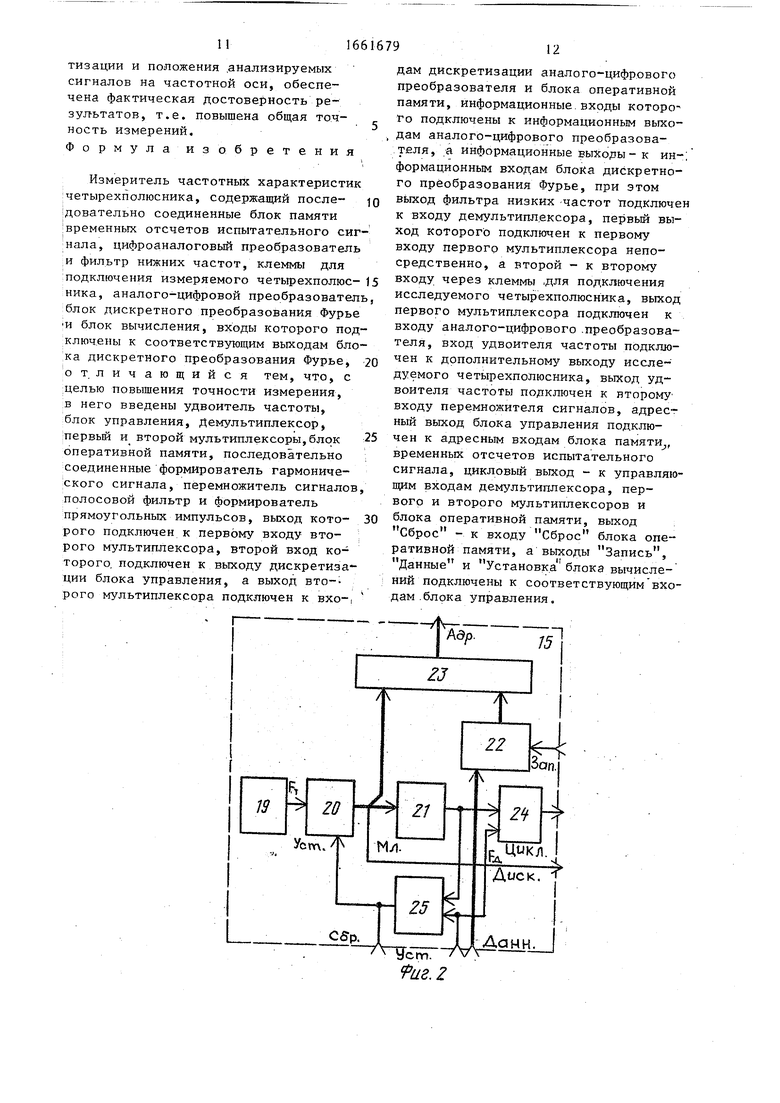

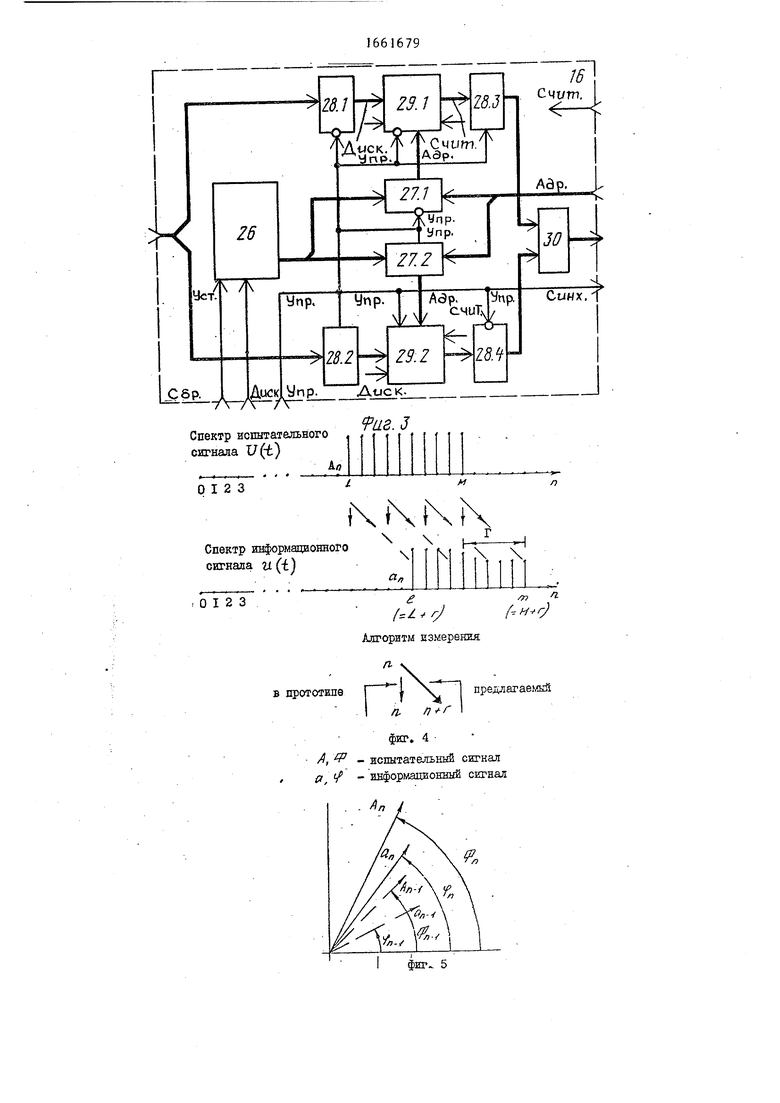

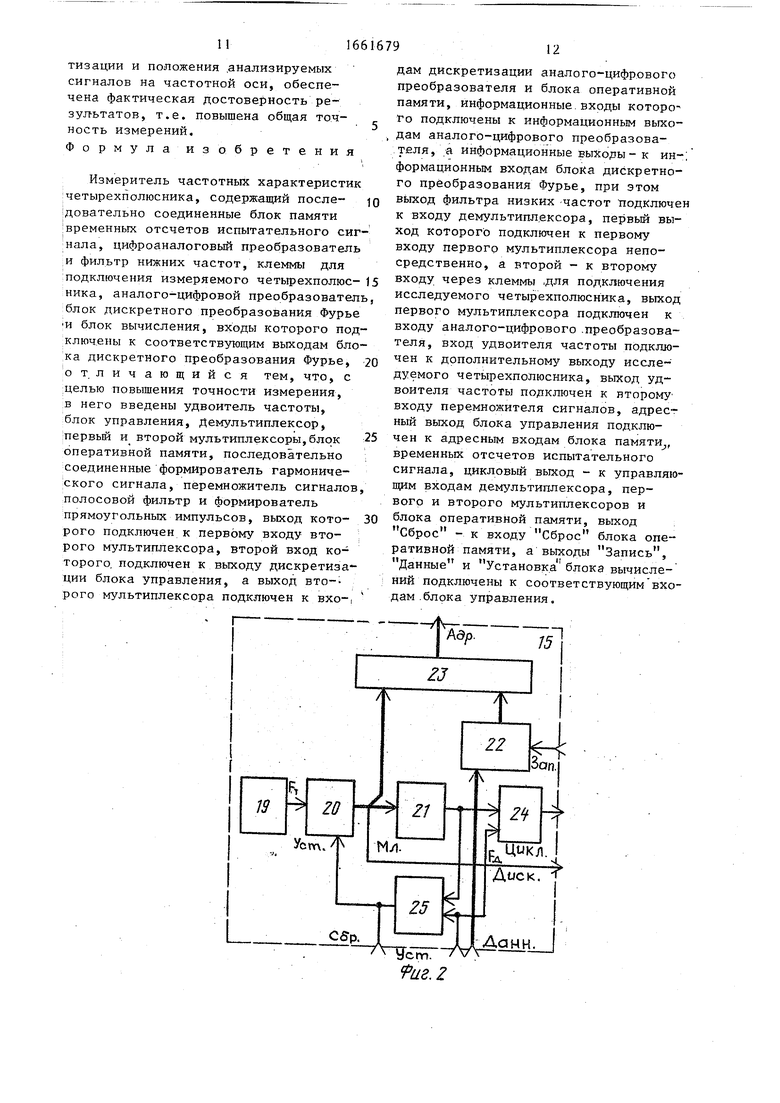

На фиг. 1 изображена функциональ- пая схема предлагаемого измерителя частотных характеристик четырехполюсника ; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока опе- ративной памяти; на фиг.4-6 - спект- ральные, фазовые и временные диаграммы сигналов.

Устройство содержит последователь-1- но-соединенные блок 1 памяти,- временных отсчетов-испытательного сигнала, цифроаналоговый преобразователь (ЦАП) 2 и фильтр 3 нижних частот (ФНЧ), следуемый четырехполюсник 4, аналого-цифровой преобразователь (АЦП) 5, блок 6 дискретного преобразования Фу )Эье (ДПФ) и блок 7 вычисления, входы которого подключены к соответствующим выходам блока 6 ДП, удвоитель 8 час- toTbi, последовательно соединенные формирователь 9 гармонического сигнала, перемножитель 10 сигнала, полосовой фильтр 11 и формирователь 12 прямоугольных импульсов, демультиплексор 13, первый 14.1 и второй 14.2 мультиплексоры, а также блок 15 управления, .адресные выходы которого подключены к адресным входам блока 1 памяти, блок 16 оперативной памяти, информа- дионные входы которого подключены к информационным выходам АЦП 5, а ин- формапионные выходы - к информационным входам блока 6 ДПФ.

Исследуемый четырехполюсник 4 содержит смеситель 17 и гетеродин 18,

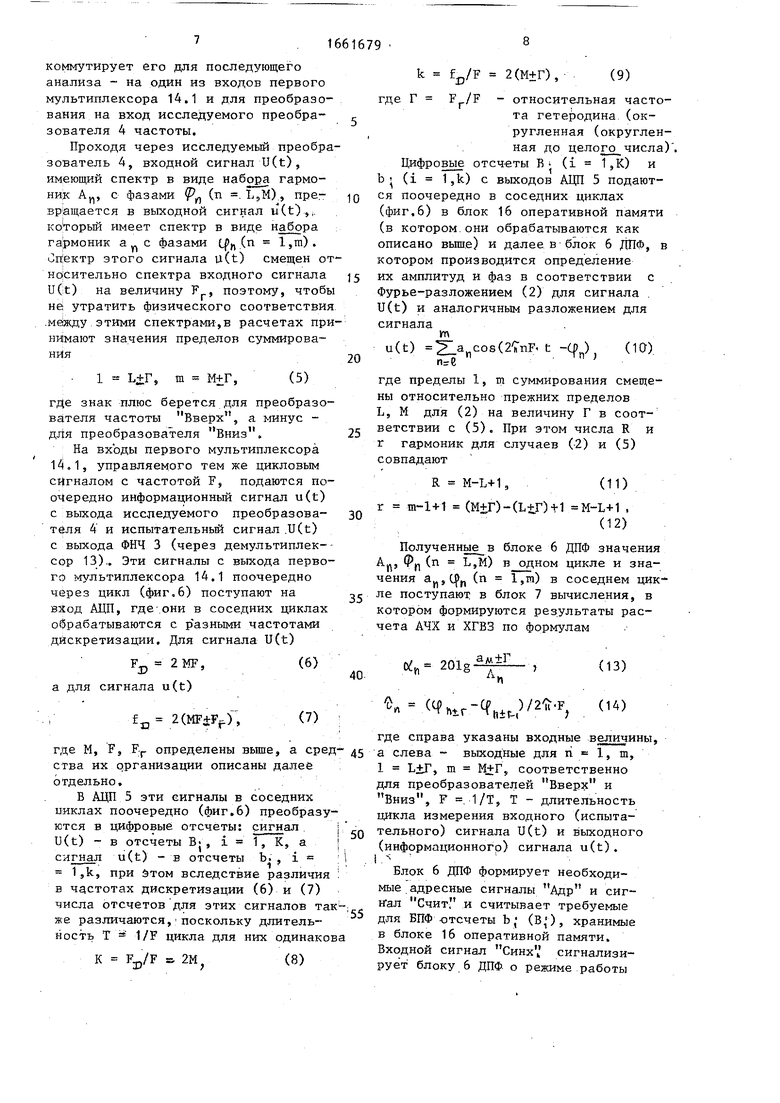

Блок 15 управления (фиг.2) содержит генератор 19 тактовых импульсов (ГТИ с частотой Fr), счетчик 20, вход которого подключен к выходу

ГТИ 19, а выход младшего разряда является выходом дискретизации блока 15 (для импульсов с частотой Ґ0 - 2 MF, где М определяется требованиями теоремы Котельникова F 1/T, Т - цикл измерения), дешифратор 21 (числа К отсчетов испытательного сигнала (К 2М), входы которого подключены к соответствующим выходам разрядов счетчика 20 (включая младший) , параллельный регистр 22, входы которого подключены к соответствующим входам данных блока 15, а вход записи - к входу записи блока 15, сумматор 23, первые входы которого подключены к соответствующим выходам разрядов счетчика 20 (включая младший), вторые входы - к выходам регистра 22, а выходы - к адресным выходам блока 15, счетчик-делитель 24 на два, вход которого подключен к выходу дешифратора 21, а выход - к цикловому выходу блока 15, и элемент ИЛИ 25, первый вход которого подключен к выходу дешифратора 21 второй вход вме- оте с установочным входом счетчика- делителя 24 - к установочному входу блока 15, а выхрд - к установочному входу счетчика 20 и к выходу сброса блока 15.

Блок 16 оперативной памяти (фиг.З) содержит адресный счетчик 26, вход и установочный вход которого подключены соответственно к входу дискретизации и входу сброса блока 16, первый и второй коммутаторы 27.1 и 27.2, первые входы которых подключены к соответствующим выходам адресного счетчика 26, а вторые входы - к соответствующим адресным входам блока 16, первый и второй ключи 28.1 и 28,2, входы которых подключены к соответствующим входам блока 16, первый и второй оперативные запоминающие устройства (ОЗУ) 29,1 и 29.2, входы которых подключены к соответствующим выхода одноименных ключей 28,1 и 28.2, а адресные входы - к соответствующим выходам одноименных коммутаторов 25.1 и 25.2, третий и четвертый ключи 28.3 и 28.4, входы которых подключены к соответствующим выходам первого и второго ОЗУ 29.1 и 29.2, соответственно, элемент ИЛИ 30, первые и вторые входы кото-( рого подключены соответственно к соответствующим выходам третьего и четвертого ключей 28.3 и 28.4, a i

э

выходы - к соответствующим выходам

блока 16, при этом управляющий вход блока 16 подключен к выходу Цикл блока 15, инверсным управляющим входам первого коммутатора 29.1, первого и четвертого ключей 28.1 и 28. и первого ОЗУ 29.1 и прямым управляющим входам второго коммутатора 29.2, второго и третьего ключей 28.2 и 28.3 и второго ОЗУ 27.2, а входы дискретизации и считывания первого и второго ОЗУ 29.1 и 29.2 пключены к одноименным входам блока 16. ,

Каждый из ключей 28 является груповым, т.-е. представляет собой группу из Р элементов И (где Р - число разрядов входного цифрового сигнала bj(B ) отсчета на входе блока 16), первые входы и выходы которых являются входами и выходами ключа, а вторые входы объединены и образуют прямой управляющий вход ключа, либо подключены к выходу инвертора, вход которого является инверсным управляющим входом ключа.

Элемент ИЛИ 29 также является групповым в том же смысле с тем же значением P. f

Аналогично коммутатор 27,1 или 27.2 содержит q первых и q вторых элементов И (где q - число разрядов адресного сигнала блока 16 и адресного счетчика 26), первые входы которых являются первыми и вторыми входами коммутатора, вторые прямые входы первых элементов И и вторые инверсные входы вторых элементов И объединены и образуют управляющий вход коммутатора (прямой или инверсный) , и q элементов ИЛИ, первые и вторые входы которых порознь подключены к выходам первых и вторых элементов И, а выходы являются выхода- ми коммутатора.

Измеритель частотных характеристик четырехполюсника работает следующим образом (далее в пояснениях заглавными символами обозначаются величины, относящиеся к испытательному сигналу, а строчными - соответствующие величины для информационного сигнала).

Блок 1 памяти заполняется (перед проведением исследования) цифровыми

отсчетами В-, i 1, К, где К - число отсчетов на длительности выбран- | ного цикла Т испытательного сигна0

679

5

ла (фиг.6), Эти отсчеты BJ определены расчетом по заданным ЧИСПОРЫМ значениям амплитуд А и фаз Фп , n L,M испытательного сигнала U(t), Расчет произведен по формуле оо

я.

О)

Ј V

- V

В; U(t)Z.Ј(t

,- или в данном случае

в; и(о Јо

где Т - период дис ретизации;

& - функция Др-рака, которая получена дискретизацией Фурье-разложения сигнала

АЛ U(t) A,.cos(2/n . nF t -0),

h 1 rlГ

-U

где F 1 /Т - постоянное число j

i ,

а значения пределов суммирования определяются нижней F. и верхней Fg границами спектра Ап сигнала

(2)

5 U(t) (фиг.4)

L FH/F, M F6/F

(3)

(здесь и дапее в аналогичных равенствах дробные отношения округлены до ближайших целых чисел).

По адресным сигналам блока 15 управления, следующим с частотой F. дискретизации, эти отсчеты В считываются из блока 1 памяти и поступают в ЦАП 2, где они превращаются в соответствующие последовательные уровни напряжения, сглаживающиеся далее в ФНЧ 3 и образующие на выходе непрерывный испытательный сигнал U(t) (фиг.6), занимающий полосу частот шириной ЛР FB-F4) который подается на вход исслед е- мого четырехполюсника - преобразователя 4 частоты Вверх или Вниз, транспонирующего спектр сигнала на частоту показано

F гетеродина (на фиг.4 смешение вверх на величину

F Fr/F в единицах F).

Частота дискретизации испытательного сигнала выбрана из требования теоремы Котельникова

(4) (3)

FDfe 2FB

FK MF.

где, согласно vo, г к

Полученный на выходе ЬНЧ J аналоговый испытательный сигнал U(t) поступает на вход демультиплексора 13S который под действием циклового сигнала поочередно с частотой F циклов

коммутирует его для последующего анализа - на один из входов первого мультиплексора 14.1 и для преобразования на вход исследуемого преобра- зователя 4 частоты.

Проходя через исследуемый преобразователь 4, входной сигнал U(t), имеющий спектр в виде гармоник АП, с фазами rt (и 1,М), пре- вращается в выходной сигнал и (О,, который имеет спектр в виде набора гармоник ас фазами Ifn (п 1,т). Спектр этого сигнала u(t) смещен относительно спектра входного сигнала U(t) на величину F , поэтому, чтобы не утратить физического соответствия между этими спектрами,в расчетах принимают значения пределов суммирования

1 L+Г, m М+Г, (5)

где знак плюс берется для преобразователя частоты Вверх, а минус - для преобразователя Вниз.

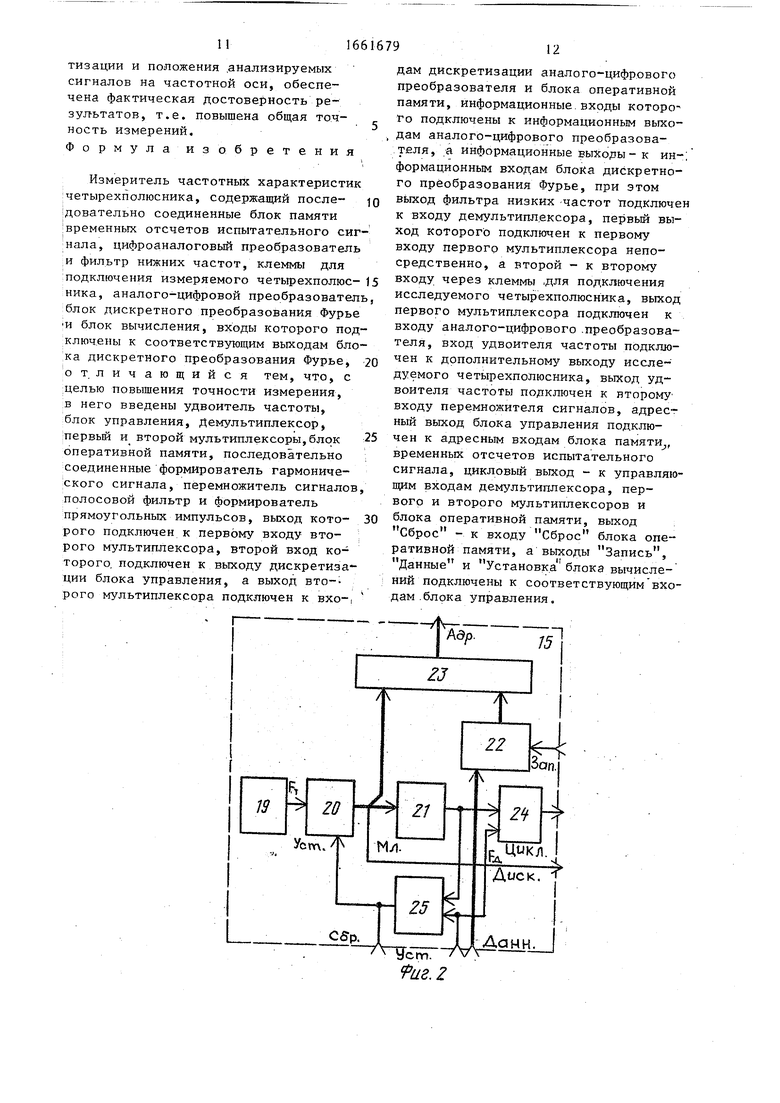

На входы первого мультиплексора 14.1, управляемого тем же цикловым сигналом с частотой F, подаются поочередно информационный сигнал u(t) с выхода исследуемого преобразова- теля 4 и испытательный сигнал U(t) с выхода ФНЧ 3 (через демулътиплек- сор 13). Эти сигналы с выхода первого мультиплексора 14.1 поочередно через цикл (фиг,6) поступают на вход АЦП, где они в соседних циклах обрабатываются с разными частотами дискретизации. Для сигнала U(t)

F 2 W,(6)

/ N

а для сигнала u(t)

f0 2(MP±Ff),

(7)

где M, F, Fr определены выше, а сред- ства их организации описаны далее отдельно.

В АЦП 5 эти сигналы в соседних циклах поочередно (фиг.6) преобразуются в цифровые отсчеты: сигнал U(t) - в отсчеты В«, i 1, К, а

сигнал u(t) - в отсчеты b. , i

i-i

1, к., при этом вследствие различия

в частотах дискретизации (6) и (7) числа отсчетов для этих сигналов также различаются, поскольку длительность Т - 1/F цикла для них одинакова

К 2М

(8)

k f /F 2(М±Г),

(9)

где Г F /F - относительная частота гетеродина (округленная (округленная до целого числа Цифровые отсч-еты В- (i 1,K) и b (i 1,k) с выходов АЦП 5 подаются поочередно в соседних циклах (фиг,6) в блок 16 оперативной памяти (в котором они обрабатываются как описано выше) и далее в блок 6 , в котором производится определение их амплитуд и фаз в соответствии с Фурье-разложением (2) для сигнала U(t) и аналогичным разложением для сигнала

т

(10)

u(t) 2 cos(27nF. t 4f ) n-V,

где пределы 1, m суммирования смещены относительно прежних пределов L, М для (2) на величину Г в соответствии с (5). При этом числа R и т гармоник для случаев (2) и (5) совпадают

R M-L+1, tn-1-H (М+Г)-(Ь+Г)+1

(11)

M-L+1, (12)

Полученные в блоке 6 ДПФ значения Afi, Фп(n L,M) в одном цикле и знаЧ( чения а

(п 1,ш) в соседнем цикле поступают в блок 7 вычисления, в котором формируются результаты расчета АЧХ и ХГВЗ по формулам

, и

(13)

0

5

«- Mr-W2, (14)

где справа указаны входные величины, а слева - выходные для п « 1, т, 1 L±T, т М+Г, соответственно для преобразователей Вверх и Вниз, F 1/Т, Т - длительность цикла измерения входного (испытательного) сигнала U(t) и выходного

(информационного) сигнала u(t). I Блок 6 ДПФ формирует необходимые адресные сигналы Адр и сигнал Счит, и считывает требуемые для БПФ отсчеты b; (В,1), хранимые в блоке 16 оперативной памяти. Входной сигнал сигнализирует блоку 6 ДПФ о режиме работы

измерителя (калибровка, измерение) . Получив этот сигнал, блок 6 ДПФ переходит на соответствующий режим обработки входного сигнала. После окончания преобразования блок 6 ДПФ информирует об этом блок 7 вычисления с помощью сигнала Прер (прерывание) , обменивается с ним обработанной информацией (Aft, ар и ) . Блок 7 вычисления приостанавливает свою текущую работу и выставляет требуемый адрес Адр, в котором хранится обработанная блоком 6 ДПФ информация, и сигнализирует об этом сигналом , (сопровождение) . Блок 6 ДПФ в ответ на это выдает хранимую информацию (Аи, а, п и Ср) и сигнал Гот, (готовность) , информируя блок 7 вычисления об этом. После обмена блок 7 вычисления производит требуемые вычисления по формулам (13) и (14) и выводит исследуемые характеристики в виде графиков на дисплей. С блока 7 вычисления можно изменить форму испытательного сигнала с помощью клавиатуры дисплея, входящего в состав блока 7.

Блок 7 вычисления формирует для этого информационные сигналы Данн (данные) и сигнал записи Зап 1, которые поступают на блок 15 управления и изменяют начальный адрес считывания испытательного сигнала на величину -вводимых данных, тем самым изменяется сам испытательный сигнал разные формы которого находятся в разньЕх областях блока 1 памяти.Блок 7 вычисления, кроме того, формирует сигнал Уст, который осуществляет начальную установку счетчика адреса блока управления, который, в свою очередь, вызывает начальную установку блока 16 оперативной памяти с помощью сигнала СбрГ, как при включении измерителя, так и вначале каждого цикла.

Блок 15 управления формирует сигнал Упр. (управления) с периодом Т K/FT, который управляет работой демультиплексора 13, мультиплексоров 14.1 и 14.2 и блока 16 оперативной памяти, при этом на вход-блока 5 АЦП испытательный сигнал в нечетных циклах проходит минуя исследуемый четырехполюсник, а в четных циклах проходит через него. Блок 5 АЦП и блок 16 оперативной памяти работают0

5

0

5

0

синхронно с частотой Fj, 2MF в нечетном цикле и fд, 2(MF+Fr) в четном цикле. Блок 1.6 оперативной памяти осуществляет одновременно з-шись входных отсчетов Ъ текущего цикла и выдачу блоку 6 ДПФ отсчетов В за предыдущий цикл.

Для организации процесса дискретизации двухчастотного типа (F и fj,) используется сигнал гетеродина 13 исследуемого преобразователя 4 частоты Вверх или Вниз (фиг.1). Этот гармонический сигнал с частотой Fr подается на вход удвоителя 8 частоты, где его частота становится равной 2Fr. Одновременно с этим из сигнала дискретизации с частотой F блока 15 управления в формирователе 9 гармонического сигнала образуется аналоговый сигнал с частотой 2№. Полученные гармонические сигналы с частотами 2MF и 2F г подаются на входы перемножителя 10 сигналов, на выходе которого образуются сигналы суммарной и разностной частоты 2MF+2Fr, один из которых, отвечающий сигналу исследуемого преобразователя 4, выделяется полосовым фильтром 11 и подается на вход формирователя 12 прямоугольных импульсов, на выходе которого образуется сигнал дискретизации с другой частотой fjj F-p +2F г.

Полученные импульсные сигналы двух5

0

5

0

5

частотной дискретизации F и

fD подаются на входы второго мультиплексора 14.2, который управляется импульсным цикловым сигналом с частотой F синхронно с коммутацией аналоговых сигналов в демультиплексорс 13 и первом мультиплексоре 14.1 (фиг.6).

Такая раздельная двухчастотная дискретизация частотой Кр для сиг-

т

нала U(t) и частотой Ј.,, для сигнала

u(t) позволяет при-вести в соответствие фазо-частотный анатнз сигналов U(t) и u(t) с их физической природой, т.е. с расположением в фазо- частотном пространстве сигналов. Если исследуемый четырехполюсник имеет разночастотные вход и выход (как в преобразователях частоты), то в известном это соответствие нарушено, что приводит к потере точности (вернее достоверности) испотьзованного в нем обычного фазо-частотного анализа (с одночастотной дискретизацией).

В предлагаемом измерителе обеспечено соответствие частот днскре-

7 Уст.

Риг. 2

ш

29.1

т

WK. t Смит/4

5

АЭр.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частотных характеристик четырехполюсника | 1988 |

|

SU1661680A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1501085A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1727131A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1429125A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для вычисления дискретного преобразования Фурье и свертки | 1988 |

|

SU1573459A1 |

Изобретение может быть использовано при эксплуатации широкополосных систем связи с частотной модуляцией. Цель изобретения - повышение точности измерения. Это достигается за счет организации двухчастотной дискретизации сигналов, которая удовлетворяет требованиям теоремы Котельникова и позволяет физически согласовать гармонические составляющие испытательного и информационного сигналов. Для этого в устройство, содержащее блок 1 памяти, цифроаналоговый преобразователь 2, фильтр 3 нижних частот, исследуемый четырехполюсник 4, аналого-цифровой преобразователь 5, блок 6 дискретного преобразования Фурье и блок 7 вычисления, введены удвоитель 8 частоты, блок 15 управления, последовательно соединенные формирователь 9 гармонических сигналов, перемножитель 10 сигналов, полосовой фильтр 11 и формирователь 12 прямоугольных импульсов, демультиплексор 13, первый 14.1 и второй 14.2 мультиплексоры и блок 16 оперативной памяти. 6 ил.

Спектр испытательного сигнала U(-fc)

Ая

0123

Спектр информационного сигнала и (i)

,0123

в прототипе

фиг. 4

А, Р - испытательный сигнал 0r f - информацвонннй сигнал

Йиг. J

м

К

а

fff

(Н+г}

Ф

Л

фиг 5

№

Исль/тательнбгй сигнал

Bi

utt)

Информационный с угнал

Щи®

Испытательный сигнал

Ъ

тлллшшлшшл.

ъ.ь

1 П П ШШЛЛЛ

в,Информационны /

сигнал

| Устройство для измерения группового времени запаздывания тракта промежуточной частоты понижающих преобразователей частоты СВЧ диапазона | 1982 |

|

SU1146607A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Kachrichten tentechnische Zeit- schrift, 1981,-34, N 1, s | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

Авторы

Даты

1991-07-07—Публикация

1988-11-28—Подача