(21)4197382/24-24

(22)23.02.87

(46) 23.09.88. Бюл. № 35

(72) С.В. Архипов

(53) 681.335(088.8)

(56) Патент США № 3584209,

кл. G 06 G 7/18, 1971.

Ноултон. Точный интегратор с не- прерывньм сбр осом V - Электроника, 1972. № 18, с. 61.

(54) АНАЛОГОВЫЙ ИНТЕГРАТОР (57) Изобретение относится к измери-. тельной и аналоговой вычислительной технике, предназначено для получения периодической последовательности значений интеграла аналогового сигнала на заданном интер вале интегрирования и может быть использовано, например, для накопления аналогового сигнала при вьщелении сигнала из

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Измерительный преобразователь интегральных характеристик сигналов | 1990 |

|

SU1739316A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Интегратор с весовым усреднением сигналов | 1987 |

|

SU1583859A1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Аналого-цифровое интергрирующее устройство | 1985 |

|

SU1339591A1 |

| Способ измерения относительной разности амплитуд двух гармонических напряжений | 1988 |

|

SU1732287A1 |

| Устройство для контроля параметров элементов сложных электрических цепей | 1984 |

|

SU1290198A1 |

| Устройство для измерения динамических магнитных характеристик | 1987 |

|

SU1497595A1 |

4 Ю

сл 1 ю

4;:

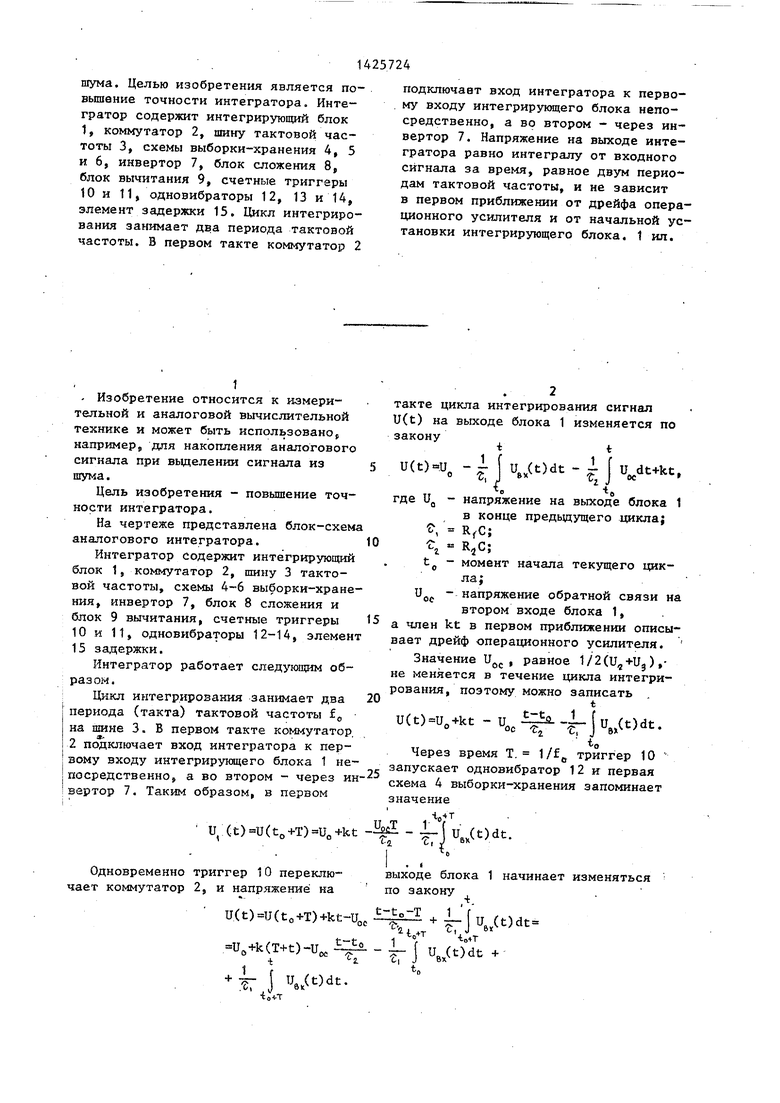

шума. Целью изобретения является повышение точности интегратора. Интегратор содержит интегрирующий блок 1, коммутатор 2, шину тактовой частоты 3, схемы выборки-хранения 4, 5 и 6, инвертор 7, блок сложения 8, блок вычитания 9, счетные триггеры 10 и 11, одновибраторы 12, 13 и 14, элемент задержки 15. Цикл интегрирования занимает два периода тактовой частоты. В первом такте коммутатор 2

1

- Изобретение относится к измерительной и аналоговой вычислительной технике и может быть использовано, например, для накопления аналогового сигнала при выделении сигнала из 5 шума.

Цель изобретения - повышение точности интегратора.

На чертеже представлена блок-схема аналогового интегратора.10

Интегратор содержит интегрирующий блок 1, коммутатор 2, шину 3 тактовой частоты, схемы 4-6 выборки-хранения, инвертор 7, блок 8 сложения и блок 9 вычитания, счетные триггеры 15 10 и 11, одновибраторы 12-14, элемент 15 задержки.

Интегратор работает следуквдим образом.

Цикл интегрирования занимает два 20 периода (такта) тактовой частоты f

на шине 3. В первом такте коммутатор, 2 подключает вход интегратора к пер- вому входу интегрирукяцего блока 1

посредственно, а во втором - через вертор 7. Таким образом, в первом

и :(:t)U(t.,+T)U«fkt -%

а

Одновременно триггер 10 переключает коммутатор 2, и напряжение на

U(t)-U(),

U(,+k(T+t)-U

t

J Ue,(t)dt

-te-t-T

подключает вход интегратора к перво- му входу интегрирующего блока непосредственно, а во втором - через инвертор 7. Напряжение на выходе интегратора равно интегралу от входного сигнала за время, равное двум периодам тактовой частоты, и не зависит в первом приближении от дрейфа операционного усилителя и от начальной установки интегрирующего блока. 1 ил.

5

10

15т

20

25

U(t)U, и

ОС

t -%

такте цикла интегрирования сигнал U(t) на выходе блока 1 изменяется по закону

i (u,,(t)dt-ljU dtH-kt,

где UQ - напряжение на выходе блока 1

в конце предьщущего цикла; , г

t - момент начала текущего цикла;- напряжение обратной связи на

втором входе блока 1, а член kt в первом приближении описывает дрейф операционного усилителя. Значение U. , равное 1/2(),- не меняется в течение цикла интегрирования, поэтому можно записать

t

)U,-kt - и,, - j Ujt)dt.

о

Через время Т. 1/f триггер 10 запускает одновибратор 12 и первая схема 4 выборки-хранения запоминает значение

а

- ij ..

л

(t)dt.

выходе блока 1 начинает изменяться по закону

t-tp-T

.r

J

.,

io+T

Ujt)dt

Jv

В конце второго такта триггер 11 и с некоторой задержкой триггер 10 переходят в исходное состояние, запуская одновибраторы 1 3 и 1 4 . При этом третья схема 6 выборки-хранения запоминает напряжение U, го хранилось во второй ки-хранения, а эта пос запоминает сигнал конц ла, равный г.+т

(t,+2T)U,+2kT-24,, - j U,(t)dt +

I I j.

J

и (t)dt,

ox

iefT

Таким образом, на выходе блока 8 сложения, реализующего функцию Ugj 1/2(Uj + Uj), по окончании циклаJ5 интегрирования получают напряжение обратной связи для следующего цикла интегрирования,, равное

Т 1 U.-fkT - и

21:,

jujOdt 20

Г 1

-J .

J

а на выходе блока 9 ряжение

вычитания - напt« 2T

нала на выходе интегри равна нулю, а при раз ной связи (cj 00 ) д возможной работу схемы ние ограничено погр грирования, которую вн этой .величины вследств коэффициента усиления усилителя.

Формула изоб Аналоговьй интеграт 25 двухвходовой интегриру схемы выборки-хранения щийся тем, что, с ния точности интеграто дены третья схема выбо два. счетных триггера, тора, блоки сложения и элемент задержки, инве тор, первый информацио рого непосредственно, инвертор соединены с в тора, выход коммутатор первому входу двухвход рующего блока, второй соединен с выходом бло выход подключен к инфо дам первой и второй сх нения, вход первого сч через элемент задержки ной тактовой частоты, подключен к управляюще мутатора и через первы к управляющег у входу п выборки-хранения, выхо динен с первым входом выход которого являетс гратора, а второй вход ходу блока сложения, и первого счетного тригг рой одновибратор подкл

ьь., 1 в.

Отсюда видно, что напряжение на выходе интегратора равно интегралу от входного сигнала за время, равное двум периодам тактовой частоты, и не зависит в первом приближении от дрейфа операционного усилителя и от начальной установки интегрирующего блока.

Обратная связь с выхода блока 8 сложения на второй вход интегрирующего блока 1 обеспечивает работу интегрирующего блока в оптимальном диапазоне выходных йапряжений. Критерием оптимальности здесь служит условие близости к нулю одной из границ диапазона; Эта граница, определяется значением напряжения Uj в i-м цикле интегрирования. Учитьшая, что Uj, U2 , а Uoc f 1/2(112 + u), можна записать для и :

U,Uo 1

-Ът

(/i

-(ur +u )+2kT j и,, (t)dt - j u,(t)dt

Lt,.

В стационарном режиме- при UexCt)

50

Формула изобретения Аналоговьй интегратор, содержащий 25 двухвходовой интегрирующий блок, две схемы выборки-хранения, отличающийся тем, что, с целью повышения точности интегратора, в него вве-: дены третья схема выборки-хранения, два. счетных триггера, три одновибра- тора, блоки сложения и вычитания, элемент задержки, инвертор -и коммутатор, первый информационный вход которого непосредственно, а второй через инвертор соединены с входом интегратора, выход коммутатора подключен к первому входу двухвходового интегрирующего блока, второй вход которого соединен с выходом блока сложения, а выход подключен к информационным входам первой и второй схем выборки-хранения, вход первого счетного триггера через элемент задержки соединен с щи- ной тактовой частоты, прямой выход подключен к управляющему входу коммутатора и через первый одновибратор - к управляющег у входу первой схемы выборки-хранения, выход которой соединен с первым входом блока вычитания, выход которого является выходом интегратора, а второй вход подключен к выходу блока сложения, инверсный выход первого счетного триггера через второй одновибратор подключен к управляюconst интегралы в квадратных скоб- щему входу второй схемы выборки-хране. в; л. тт - 7т1 TjTjcr Tat. Vi -«/-IQ TTTJUQ tr / гтлпти-Л/

ках равны между coбoй а U2 Uz

т -г

Ulj, поэтому имеют U k tj

Отсюда видно, что в отсутствие дрейфа (k 0) граница диапазона сигния, выход которой соединен с первым входом блока сложения и информационным входом третьей схемы выборки-хранения, выход которой подключен к вто-

минает напряжение U, которое до этого хранилось во второй схеме 5 выборки-хранения, а эта последняя схема запоминает сигнал конца текущего цикла, равный г.+т

,, - j U,(t)dt +

нала на выходе интегрирующего блока 1 равна нулю, а при разорванной обратной связи (cj 00 ) дрейф делает невозможной работу схемы. Снизу значение ограничено погрешностью интегрирования, которую вносит уменьщение этой .величины вследствие конечности коэффициента усиления операционного усилителя.

0

0

5

Формула изобретения Аналоговьй интегратор, содержащий 5 двухвходовой интегрирующий блок, две схемы выборки-хранения, отличающийся тем, что, с целью повышения точности интегратора, в него вве-: дены третья схема выборки-хранения, два. счетных триггера, три одновибра- тора, блоки сложения и вычитания, элемент задержки, инвертор -и коммутатор, первый информационный вход которого непосредственно, а второй через инвертор соединены с входом интегратора, выход коммутатора подключен к первому входу двухвходового интегрирующего блока, второй вход которого соединен с выходом блока сложения, а выход подключен к информационным входам первой и второй схем выборки-хранения, вход первого счетного триггера через элемент задержки соединен с щи- ной тактовой частоты, прямой выход подключен к управляющему входу коммутатора и через первый одновибратор - к управляющег у входу первой схемы выборки-хранения, выход которой соединен с первым входом блока вычитания, выход которого является выходом интегратора, а второй вход подключен к выходу блока сложения, инверсный выход первого счетного триггера через второй одновибратор подключен к управляю0

5

TjTjcr Tat. Vi -«/-IQ TTTJUQ tr / гтлпти-Л/

ния, выход которой соединен с первым входом блока сложения и информационным входом третьей схемы выборки-хранения, выход которой подключен к вто-

5U257246

рому входу блока сложения, а управ- счетного триггера, вход которого под- лякяций вход через третий одновибратор ; ключей к шине тактовой частоты инте- соединен с инверсным выходом второго гратора.

Авторы

Даты

1988-09-23—Публикация

1987-02-23—Подача