Изобретение относится к автоматике и вычислительной технике и может найти применение при построении гибридных вычислительных устройств, информационно-измерительных и вычислительных систем и комплексов.

Цель изобретения - расширение динамического диапазона интегрируемых сигналов.

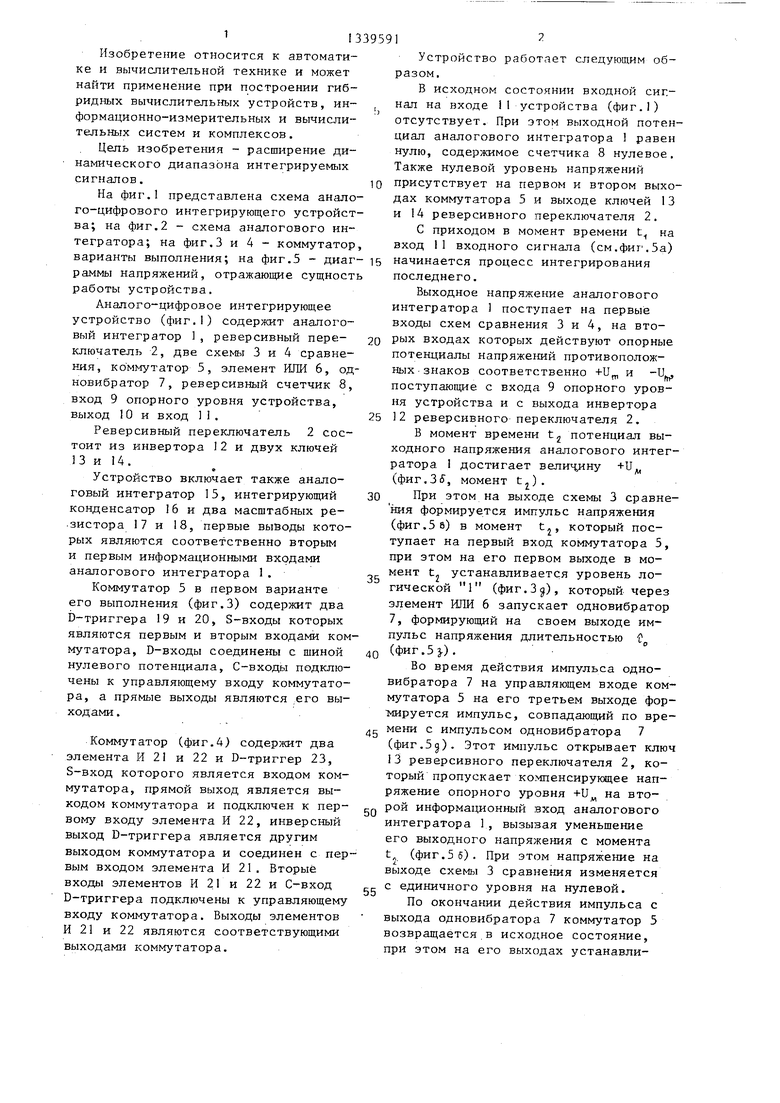

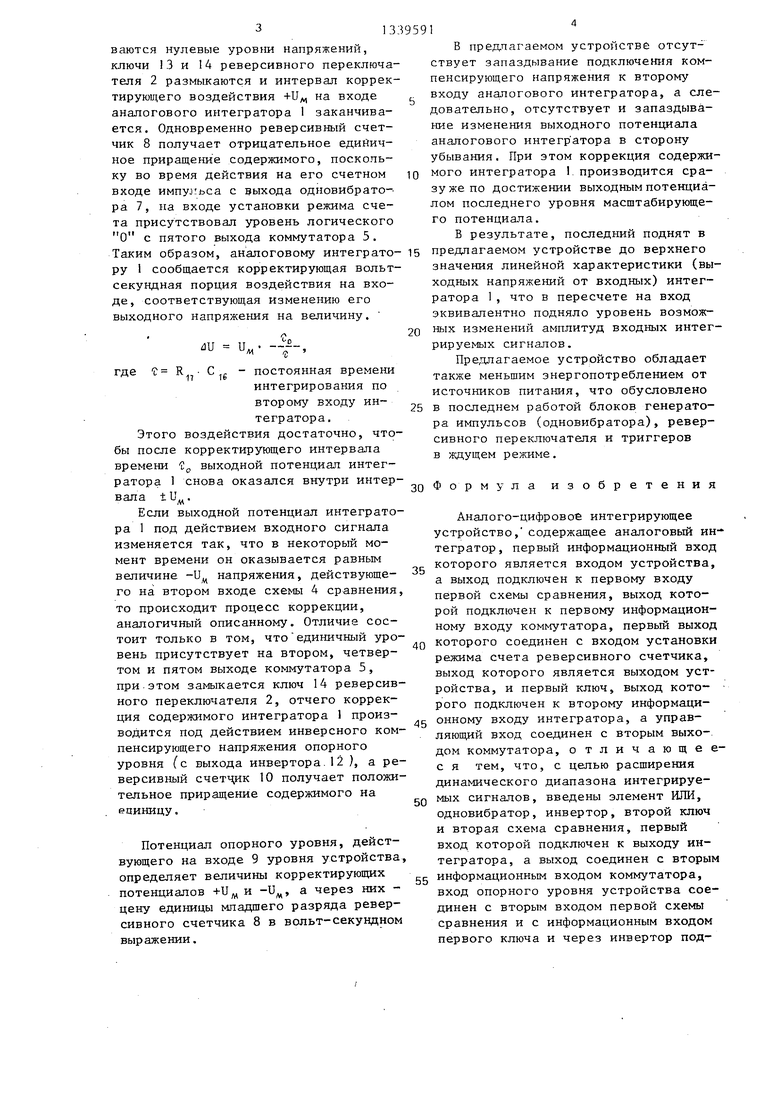

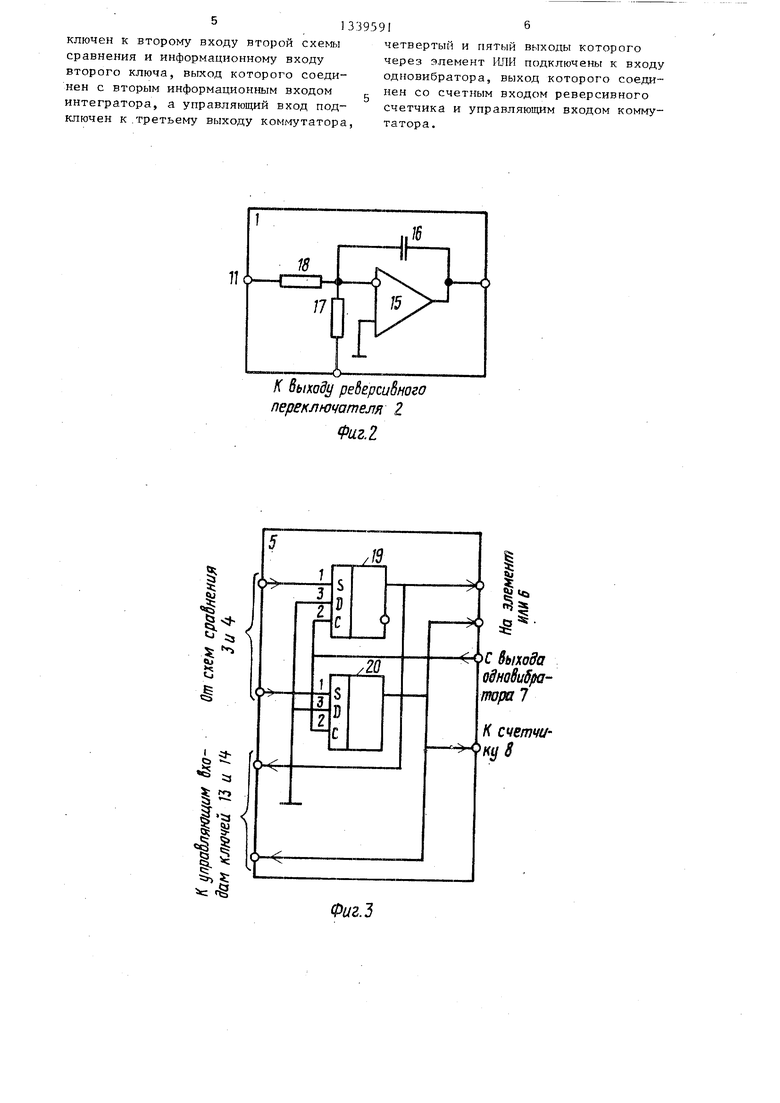

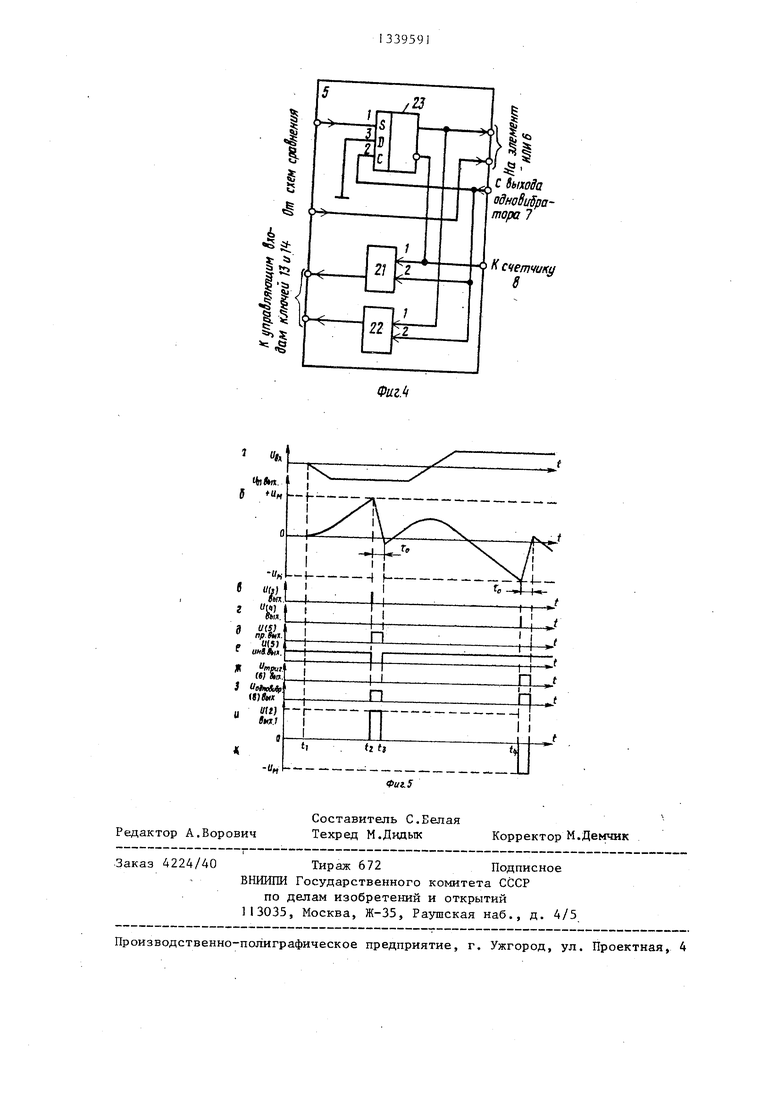

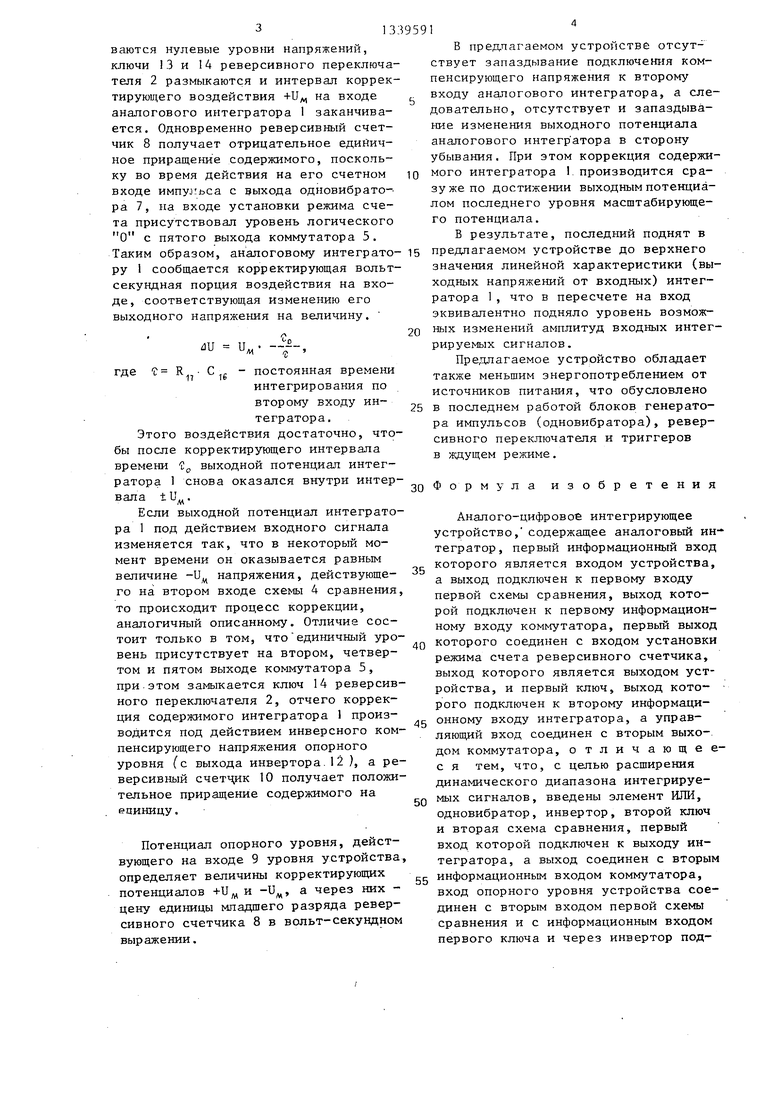

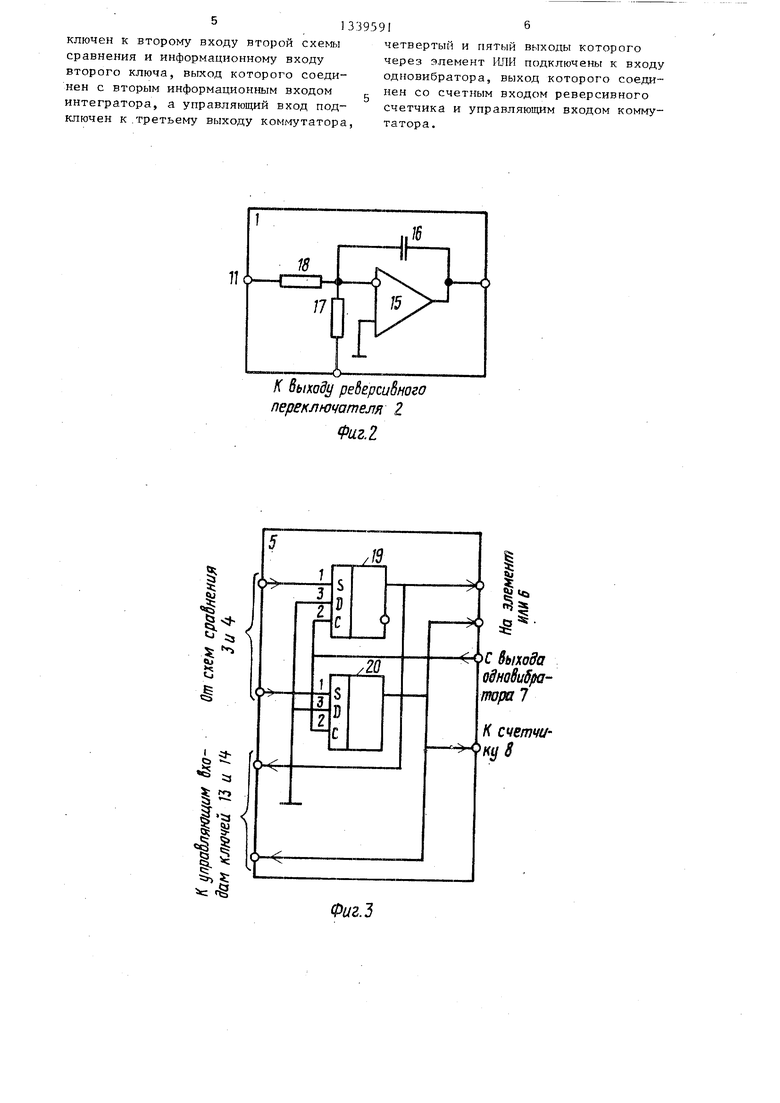

На фиг.1 представлена схема аналого-цифрового интегрирующего устройства; на фиг.2 - схема аналогового интегратора; на фиг.З и 4 - коммутатор варианты выполнения; на фиг.З - диаграммы напряжений, отражающие сущност работы устройства.

Аналого-цифровое интегрирующее устройство (фиг.1) содержит аналоговый интегратор 1, реверсивный переключатель 2, две схемы 3 и 4 сравнения, коммутатор 5, элемент ИЛИ 6, од новибратор 7, реверсивный счетчик 8, вход 9 опорного уровня устройства, выход 10 и вход II.

Реверсивный переключатель 2 состоит из инвертора 12 и двух ключей 13 и 14.

9

Устройство включает также аналоговый интегратор 15, интегрирующий конденсатор 16 и два масштабных ре- .зистора 17 и 18, первые выводы которых являются соответственно вторым и первым информационными входами аналогового интегратора I.

Коммутатор 5 в первом варианте его выполнения (фиг.З) содержит два Ь-триггера 19 и 20, S-входы которых являются первым и вторым входами коммутатора, D-входы соединены с шиной нулевого потенциала, С-входы подключены к управляющему входу коммутатора, а прямые выходы являются его выходами .

Коммутатор (фиг.4) содержит два элемента И 21 я 22 и D-триггер 23, S-вход которого является входом коммутатора, прямой выход является выходом коммутатора и подключен к первому входу элемента И 22, инверсный выход D-триггера является другим выходом коммутатора и соединен с первым входом элемента И 21. Вторые входы элементов И 21 и 22 и С-вход D-триггера подключены к управляющему входу коммутатора. Выходы элементов И 21 и 22 являются соответствующими выходами коммутатора.

5

0

Устройство работает следующим образом.

В исходном состоянии входной сигнал на входе 11 устройства (фиг.1) отсутствует. При этом выходной потенциал аналогового интегратора 1 равен нулю, содержимое счетчика 8 нулевое. Также нулевой уровень напряжений присутствует на первом и втором выходах коммутатора 5 и выходе ключей 13 и 14 реверсивного переключателя 2.

С приходом в момент времени t на вход 11 входного сигнала (см.фиг .За) начинается процесс интегрирования последнего.

Выходное напряжение аналогового интегратора 1 поступает на первые входы схем сравнения 3 и 4, на вторых входах которых действуют опорные потенциалы напряжений противополож5

0

5

0

5

0

5

ных знаков соответственно +11 и

-и,

V

поступающие с входа 9 опорного уровня устройства и с выхода инвертора

12реверсивного переключателя 2.

В момент времени t потенциал выходного напряжения аналогового интегратора I достигает величину +U, (фиг,, момент tj).

При этом на выходе схемы 3 сравне- ния формируется импульс напряжения (фиг.5 и) в момент tj, который поступает на первый вход коммутатора 5, при этом на его первом выходе в момент tj устанавливается уровень логической 1 (фиг.З), который через элемент ИЛИ 6 запускает одновибратор 7, формирующий на своем выходе импульс напряжения длительностью f (фиг.5).

Во время действия импульса одно- вибратора 7 на управляющем входе коммутатора 5 на его третьем выходе фор- мируется импульс, совпадающий по времени с импульсом одновибратора 7 (фиг.З). Этот импульс открывает ключ

13реверсивного переключателя 2, который пропускает компенсирукяцее напряжение опорного уровня +Uj, на второй информационный вход аналогового интегратора 1, вызывая уменьщение его выходного напряжения с момента

t (фиг.55). При этом напряжение на выходе схемы 3 сравнения изменяется с единичного уровня на нулевой.

По окончании действия импульса с выхода одновибратора 7 коммутатор 3 возвращается,в исходное состояние, при этом на его выходах устанавли313

ваются нулевые уровни напряжений, ключи 13 и 14 реверсивного переключателя 2 размыкаются и интервал корректирующего воздействия +U на входе аналогового интегратора 1 заканчивается. Одновременно реверсивный счетчик 8 получает отрицательное единичное приращение содержимого, поскольку во время действия на его счетном входе импуо ьса с дыхода одновибрато-- ра 7, на входе установки режима счета присутствовал уровень логического О с пятого выхода коммутатора 5, Таким образом, аналоговому интеграто- ру 1 сообщается корректирующая вольт- секундная порция воздействия на входе, соответствующая изменению его выходного напряжения на величину.

dU и.

I D

где С R,- С.,. - постоянная времени

17 I b

интегрирования по второму входу интегратора.

Этого воздействия достаточно, чтобы после корректирующего интервала времени 1 выходной потенциал интегратора 1 снова оказался внутри интервала t Ь .

ЛЛ

Если выходной потенциал интегратора 1 под действием входного сигнала изменяется так, что в некоторый момент времени он оказывается равньм величине -U напряжения, действующе- го на втором входе схемы 4 сравнения то происходит процесс коррекции, аналогичный описанному. Отличие состоит только в том, что единичный уровень присутствует на втором, четвертом и пятом выходе коммутатора 5, при.этом замыкается ключ 14 реверсивного переключателя 2, отчего коррекция содержимого интегратора 1 производится под действием инверсного компенсирующего напряжения опорного уровня (с выхода инвертора. 12 ), а реверсивный счетчик 10 получает положительное приращение содержимого на единицу.

Потенциал опорного уровня, действующего на входе 9 уровня устройства, определяет величины корректирующих потенциалов +U и -U, а через них - цену единицы младшего разряда реверсивного счетчика 8 в вольт-секундном выражении.

5

В предлагаемом устройстве отсутствует запаздывание подключения компенсирующего напряжения к второму входу аналогового интегратора, а следовательно, отсутствует и запаздывание изменения выходного потенциала аналогового ннтегр атора в сторону убывания. При этом коррекция содержимого интегратора 1 производится сразу же по достижении выходным потенциалом последнего уровня масштабирующего потенциала.

В результате, последний поднят в предлагаемом устройстве до верхнего значения линейной характеристики (выходных напряжений от входных) интегратора 1 , что в пересчете на вход эквивалентно подняло уровень возможных изменений амплитуд входных интегрируемых сигналов.

Предлагаемое устройство обладает также меньшим энергопотреблением от источников питания, что обусловлено в последнем работой блоков генератора импульсов (одновибратора), реверсивного переключателя и триггеров в ждущем режиме.

30 Формула изобретения

0

Аналого-цифровое интегрирующее устройство, содержащее аналоговый интегратор, первый информационный вход которого является входом устройства, а выход подключен к первому входу первой схемы сравнения, выход которой подключен к первому информационному входу коммутатора, первый выход которого соединен с входом установки режима счета реверсивного счетчика, выход которого является выходом устройства, и первый ключ, выход которого подключен к второму информационному входу интегратора, а управ- ляюпщй вход соединен с вторым выхо-. дом коммутатора, отличающее- с я тем, что, с целью расширения динамического диапазона интегрируемых сигналов, введены элемент ИЛИ, одновибратор, инвертор, второй ключ и вторая схема сравнения, первый вход которой подключен к выходу интегратора, а выход соединен с вторым информационным входом коммутатора, вход опорного уровня устройства соединен с вторым входом первой схемы сравнения и с информационным входом первого ключа и через инвертор под5

0

5

ключей к второму входу второй схемы сравнения и информационному входу второго ключа, выход которого соединен с вторым информадионным входом интегратора, а управляющий вход подключен к .третьему выходу коммутатора,

четвертый и пятый выходы которого через элемент ИЛИ подключены к входу одповибратора, выход которого соединен со счетным входом реверсивного счетчика и управляющим входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| ПРЕЦИЗИОННЫЙ ИМИТАТОР РЕАЛИЗАЦИЙ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099785C1 |

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для интегрирования электрического сигнала | 1982 |

|

SU1115066A1 |

| Интегратор с весовым усреднением сигналов | 1987 |

|

SU1583859A1 |

Изобретение относится к автоматике и вычислительной технике и мо- жет быть использовано в приборостроении, в гибридных вычислительных устройствах для интегрирования сигналов, когда требуются большие постоянные времени интегрирования. Цель изобретения - расширение динамического диапазона интегрируемых сигналов. Устройство содержит аналоговый интегратор 1, реверсивный переключатель 2, схемы сравнения 3 и 4, коммутатор 5, элемент ИЛИ 6, одновибратор 7 и реверсивный счетчик 8. Устройство имеет более широкий по амплитуде динамический диапазон интегрируемых сигналов, обусловленный тем, что отсутствует запаздывание подключения компенсирующего напряжения к аналоговому интегратору, а следовательно, отсутствует запаздывание изменения выходного потенциала аналогового интегратора в сторону убывания. При этом коррекция содержимого интегратора 1 производится сразу же по достижении выходным потенциалом последнего уровня масштабируюш;его потенциала. 5 ил. (Л 6 - 7 -j СО СО СП СО «J XD 2Zir фиг.

Л Bbixodi/ ре8Ерси8ного nepeклнJ /ameJ7я 2

Фиг.2

It

s

g

i

Фиг.З

й««.

o§HoSu5fa mpal

К C4emW KijS

5

«г 5

|t5

| 5i Л &J

il ftj

4224/40

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU389515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-10-21—Подача