4

N3

114293U

Изобретение относится к импульсной Iтехнике, а именно к многозначным элеiментам с инжекционным питанием, и может быть использовано для построения цифровых логических устройств.

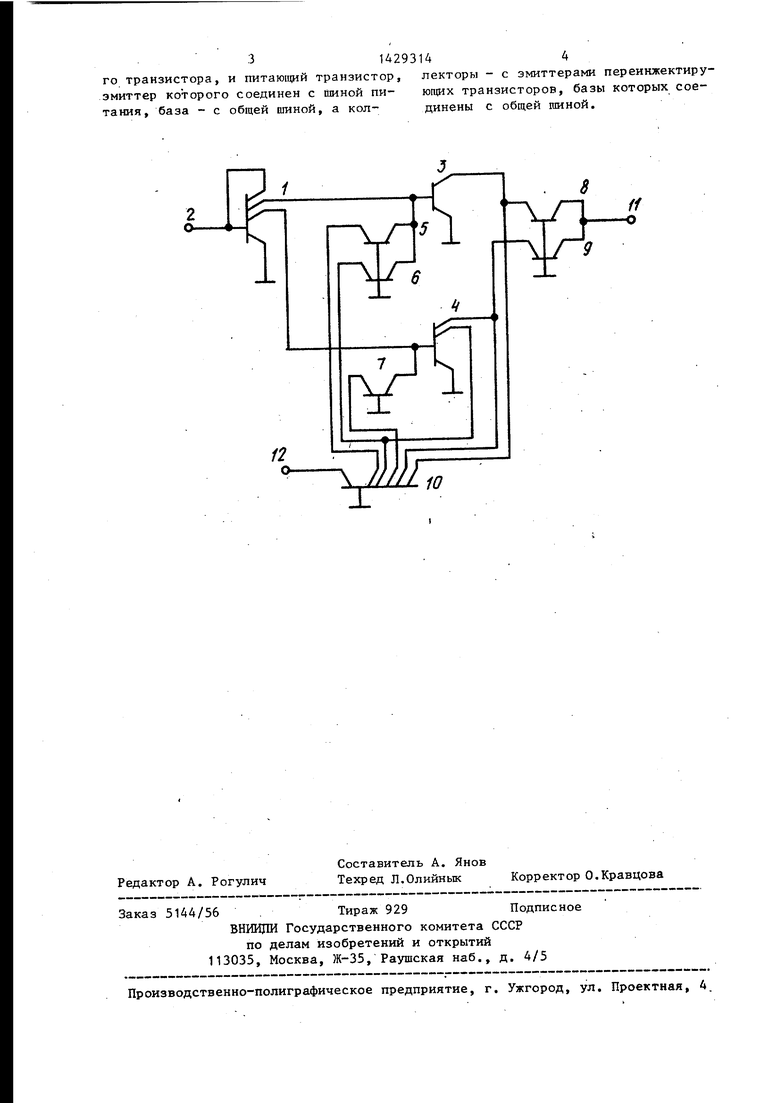

Цель изобретения - сокращение площади при реализации на.кристалле и уменьшение потребляемой мощности. На чертеже приведена электричес-

Iкая функциональная схема нормапизато1ра уровня.

I Нормализатор уровня содержит входной транзистор 1f включенный по схеме токового отражения, эмиттер которого соединен с общей дюнной, один коллектор соединен с базой и входной шиной 2, транзисторь 3 и 4, включенные по схеме порогового детектора, эмиттеры

Если входной ток ,51, входной транзистор 1 отводит не весь ток, задаваемый в базы транзисторов 3 и 4, которые открыты, поэтому отводят токи задаваемые питающим транзистором 10 в эмиттеры транзисторов 8 и 9, послед ни е закрыты. В выходе устройства нулевой уровень тока.

Если входной ток 0,51об ,5I, транзистор 4 открыт, шунтирует транзисторы 6 и 9, а транзистор 3 закрыт, так как ток 0,51, задаваемый в его базу транзистором 5, полностью отводится входным транзистором 1. Транзистор 8 открыт и задает в выходную шину ток, равный l.

Если входной ток 1,51о ,51 транзистор 4 закрыт, а транзистор 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехуровневый триггер | 1982 |

|

SU1056268A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Нормализатор уровня | 1983 |

|

SU1088129A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132358A2 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 1995 |

|

RU2074492C1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| Устройство для определения наличия металла | 1990 |

|

SU1837152A1 |

Изобретение относится к импульсной технике, а именно к многозначным элементам с инжекционным питанием, и .может быть использовано для построения цифровых логических устройств, Цель изобретения - сокращение площади при реализации на кристалле и уменьшение потребляемой мощности. Нормализатор уровня содержит входной транзистор, включенный по схеме токового отражателя, два транзистора, включенных по схеме порогового Детектора, пять переинжектирую1цих транзисторов и питающий транзистор. Питающий транзистор задает в эмиттеры пере- инжектируюп{их транзисторов соответственно 0,5 1„, 2 1„, 1,5 1„, 1 и 2 IP , где (, - единичный уровень тока. Введение переинжектирующих тран- зисгоров с соответствующими величина- 3 ми змиттерных токов позволяет обеспечить работоспособность нормализатора уровня при меньшем количестве компонентов. 1 ил.

ры 5 и 6 задают суммарный ток 2,51о, и шунтируют транзистор 8, последний закрыт. Открытый транзистор 9 задает в выходную шину ток, равньй 21„.

Если входной ток I.,г

ел

2,51,

транзисторы 3 и 4 закрыты, а транзисторы 8 и 9 открыты и задают в выходную шину 11 суммарный ток, равный 31р.

г

30 Фор мула изобретения

которых соединены с общей шиной, базы 20 открыт, так как в его базу транзисто1 соединены с первым и вторым коллекто| рами входного транзистора 1, пять

переинжектирующих транзисторов 5-9

и питающий транзистор ГО, базы которых объединены с общей шиной, коллекторы 25 транзисторов 5 и 6 соединены с базой транзистора 3, коллектор транзистора 7 соединен с базой транзистора 4, коллекторы транзисторов 8 и 9 - с выходной НИНОЙ 11, эмиттеры транзисторов 8, 9 и 6 соединены с коллектором транзистора 3, с первым и вторым кол; лектором транзистора 4 соответственно, соответствуинцйе коллекторы тран: зистора 10 соединены с соответствующими эмиттерами транзисторов 5-9, а эмиттер транзистора 10 - с шиной 12 питания.

Нормализатор работает следующим образом.

Входной транзистор 1, включенный по схеме токового отражения, имеет коэффициент усиления, равный единице. Это обеспечивается соотношением площадей областей выходного коллектора и коллектора обратной связи. Питающий транзистор 10 задает в эмиттеры переинжектирующих транзисторов 5-9 и со35

40

..45

Нормализатор уровня, содержаш €й входной транзистор, включенный по схеме токового отражения, база которого соединена с входной шиной, а эмиттер - с общей шиной, первый и второй транзисторы, включенные по схеме порогового детектора, эмиттеры которых соединены с общей шиной, причем коллекторы входного транзистора соединены соответственно с базами первого и второго транзисторов, от - л и чающийся тем, что, с целью сокращения площади при реализации на кристалле и умен ьшения потребляемой мощности, в него введены первый и второй переинжектирукхцие транзисторы, коллекторы которых соединены с базой первого транзистора, третий переинжектирующий транзистор коллек - тор которого соединен с базой второго транзистора,- четвертый и пятый пере- . инжектируюире транзисторы, коллекторы которых соединены с выходной шиной, а эмиттеры - с коллектором первого и первым коллектором второго транзистора соответственно, второй коллектор второго транзистора соединен с эмиттером второго переинжектирующеответственно 0,51, 21, 1,5l,, Тд и 21,

где

1 единичный уровень тока.

„ 50

Это обеспечивается геометрией и вза имным расположением эмиттера и коллекторов питающего транзистора 10.

При подаче входного тока в входную шину 2 устройства в зависимости от его величины: О,51о, (0,5-1,5)1й,

55

2,51о, на выходе нормасоответствует OIos

21

о)

ры 5 и 6 задают суммарный ток 2,51о, и шунтируют транзистор 8, последний закрыт. Открытый транзистор 9 задает в выходную шину ток, равньй 21„.

Если входной ток I.,г

ел

2,51,

транзисторы 3 и 4 закрыты, а транзисторы 8 и 9 открыты и задают в выходную шину 11 суммарный ток, равный 31р.

г

Фор мула изобретения

открыт, так как в его базу транзисто

2

е. ийе35

40

..45

и

ка.

„ 50

ую

55

ма)

Нормализатор уровня, содержаш €й входной транзистор, включенный по схеме токового отражения, база которого соединена с входной шиной, а эмиттер - с общей шиной, первый и второй транзисторы, включенные по схеме порогового детектора, эмиттеры которых соединены с общей шиной, причем коллекторы входного транзистора соединены соответственно с базами первого и второго транзисторов, от - л и чающийся тем, что, с целью сокращения площади при реализации на кристалле и умен ьшения потребляемой мощности, в него введены первый и второй переинжектирукхцие транзисторы, коллекторы которых соединены с базой первого транзистора, третий переинжектирующий транзистор коллек - тор которого соединен с базой второго транзистора,- четвертый и пятый пере- . инжектируюире транзисторы, коллекторы которых соединены с выходной шиной, а эмиттеры - с коллектором первого и первым коллектором второго транзистора соответственно, второй коллектор второго транзистора соединен с эмиттером второго переинжектирующе314293144

го транзистора, и питаю1ций транзистор, лекторы - с эмиттерами переинжектиру- эмиттер которого соединен с шиной пи- ющих транзисторов, базы которых сое- тания, база - с общей шиной, а кол-динены с общей шиной.

| Tich Dao Treshold PL and its applications to binary symme trie functions and multivalued logicjIEEE, Journal off Solid - State Cireuits, Г977, V | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| РУЧНОЙ СТАНОК ДЛЯ ФОРМОВКИ ПУСТОТЕЛЫХ КАМНЕЙ РАЗЛИЧНОЙ ФОРМЫ | 1922 |

|

SU470A1 |

| Нормализатор уровня | 1983 |

|

SU1088129A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-17—Подача