Щена площадь, на кристалле, чность схемы. занимаемая устройством электртеских связей уменьшено и улучшена технологи- число межсоединений в 2,5 раза, За счет введения: новых 2 ил. 1269253

| название | год | авторы | номер документа |

|---|---|---|---|

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Компаратор | 1978 |

|

SU790257A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

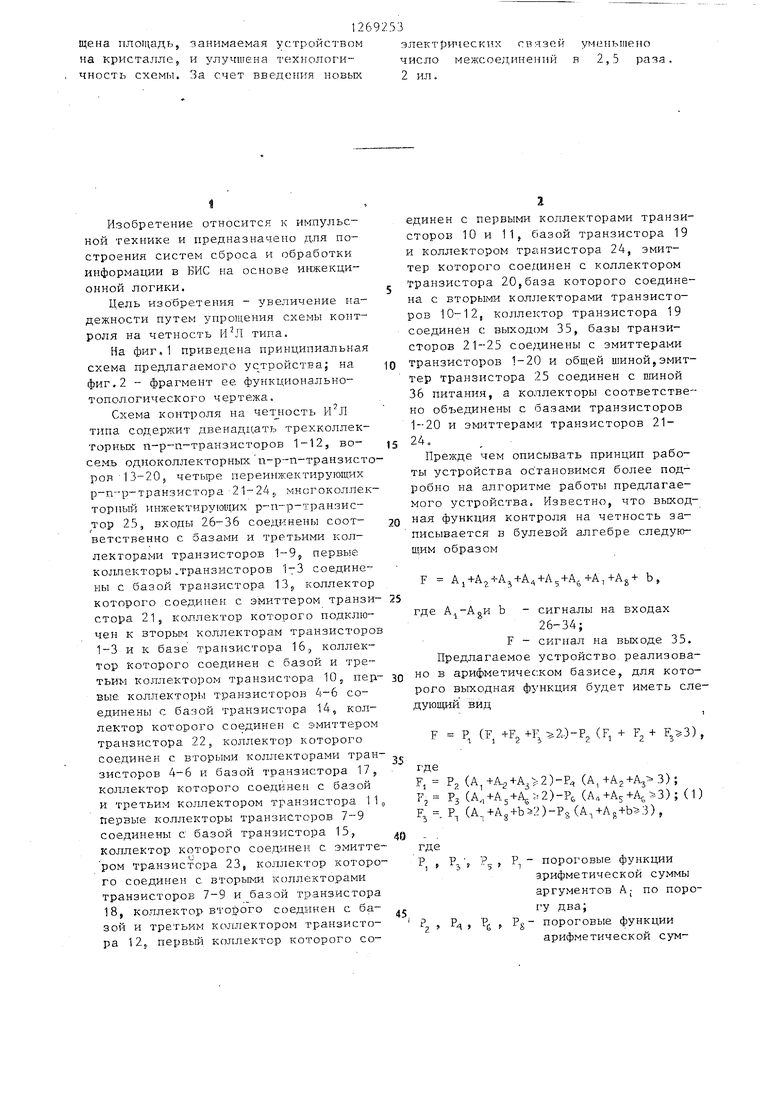

Изобретение относится к импульсной технике, предназначено для построения систем сброса и обработки информации в БИС на основе инжекционной логики. Цель изобретения - увеличение надежности путем упрощения схемы контроля на четность типа. Для этого в устройство дополнительно введены четыре переинжектирующих р-п-р-транзистора, 21-24 и новые функциональные связи. Устройство также содержит двенадцать трехколлекторйых п-р-п-транзисторов 1-12, восемь одноколлекторных S п-р-п-транзисторов 13-20, многокол(Л лекторный инжектирующий р-п-р-транзистор, входы 26-36. При этом сокра

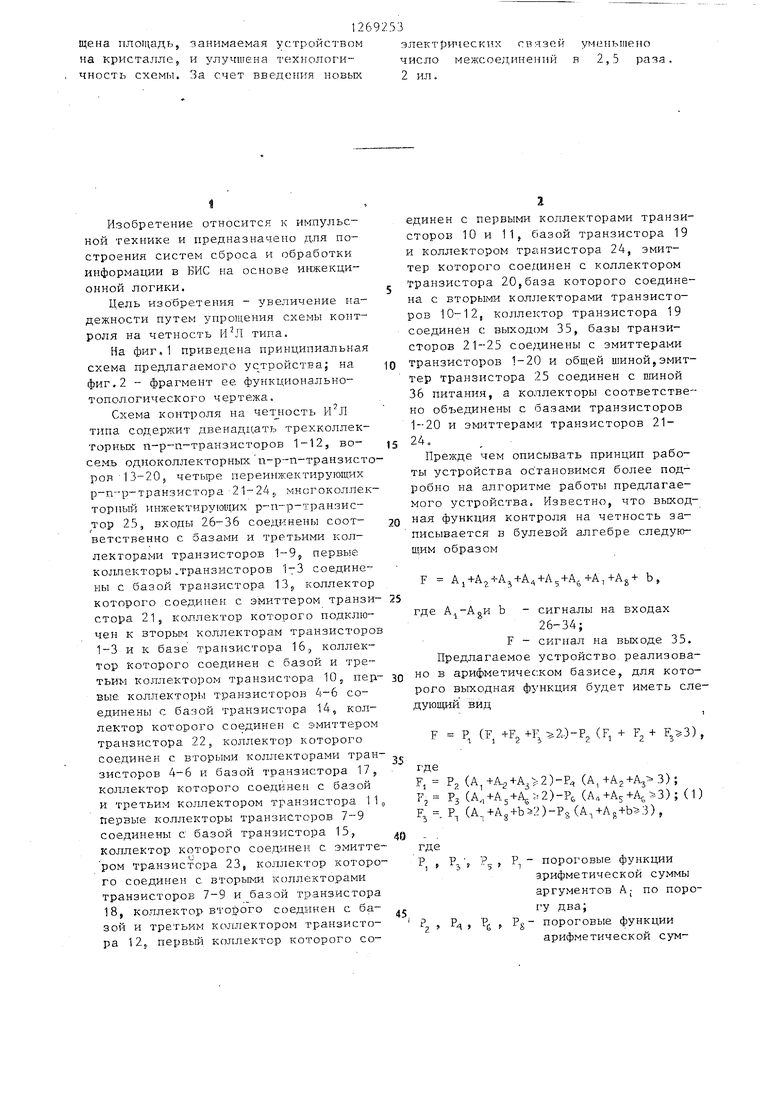

Изобретение относится к импульсной технике и предназначено для построения систем сброса и обработки информации в БИС на основе инжекционной логики. Цель изобретения - увеличение надежности путем упрощения схемы контроля на четность ИЛ типа. На фиг,1 приведена принципиальная схема предлагаемого ус тройства; на фиг,2 - фрагмент ее функциональнотопологического чертежа. Схема контроля на че1чюсть ил типа содержит двенадцать трехколлекторных п-р-п-транзисторов 1-12, восемь одноколлекторных п-р-п-транзисто ров Ч 3-20, четыре переинжектирующих р-П-р-транзистора -21-24,, многоколлек торный инжектируювщх р-п-р-транзистор 25, входы 26-36 соединены соответственно с базами и третьими коллекторами транзисторов 1-9, первь е коллекторы.транзисторов 1-3 соединены с базой транзистора 13,, коллектор которого соединен с эмиттером транзи стора 21, коллектор которого подключен к вторым коллекторам транзисторо 1-3 и к базе транзистора Тб, коллектор Которого соединен с базой и третьим коллектором транзистора 10, пер вые коллекторы транзисторов 4-6 соединены с базой транзистора 14, коллектор которого соединен с эмиттером транзистора 22, коллектор которого соединен с вторыми коллекторами тран зисторов 4-6 и базой транзистора М, коллектор которого соединен с базой и третьим коллектором транзистора 1 первые коллекторы транзисторов 7-9 соединены с базой транзрютора 15, коллектор которого соединен с эмитте ром транзистора 235 коллектор которо го соединен с вторыми коллекторами транзисторов 7-9 и базой транзистора 18, коллектор второго соединен с базой и третьим коллектором транзистора 12., первый коллектор которого соединен с первыми коллекторами транзисторов 10 и 11, базой транзистора 19 и коллектором транзистора 24, змиттер которого соединен с коллектором транзистора 20,база которого соединена с вторыми коллекторами транзисторов 10-12, коллектор транзистора 19 соединен с выходом 35, базы транзисторов 21-25 соединены с эмиттерами транзисторов 1-20 и общей шиной,эмиттер транзистора 25 соединен с шиной 36 питания, а коллекторы соответствено объединены с базами транзисторов 1-20 и эмиттерами транзисторов 2124. . Прежде чем описывать принцип работы устройства остановимся более подробно на алгоритме работы предлагаемого устройства. Известно, что выходная функция контроля на четность записывается в булевой алгебре следующим образом F А;+А.,+Аз,+А4+Л5+А,+А,+Ag+ b, где b - сигналы на входах 26-34; F - сигнал на выходе 35. Предлагаемое устройство реализовано в арифметичес;ком базисе, для которого выходная функция будет иметь следующий вид F Р (F, +F2 +Г, -)-Р2 (Fl + г + з) , F. РЗ (А,+.А.,)-Р (A,+A2+Aj 3); 2 РЗ (А.,)-Рб (А4+А5+А 3); (1) РЪ - РТ (A.,+Ag+b52)-Pg(A,+Ag+b 3), Р, 5 РЗ 5 1 пороговые функции арифметической суммы аргументов А; по порогу два; PJ 5 Р , Pg , Pg - пороговые функции арифметической суммы аргументов А, по порогу три. (-) - операция арифметиче ского вычитания. Таким образом, чтобы реализовать искомую функцию F необходимо исполь зовать элементы, выполняющие арифме тические функции и необходим порого вьй элемент, кроме того, требуется задавать на входы элементов схемы нужные весовые значения токов. Известно, что в инжекционной лог ке в качестве элементов,вьтолняющих арифметические операции суммировани и вычитания, используются токовые повторители (транзисторы 1-12 в предлагаемой схеме) и транзисторы с перехватом тока (транзисторы 21-24) В Качестве пороговых элементов используются инверторы (в рассматриваемой схеме функцию пороговых элементов вьтолняют транзисторы 13-20) Весовые коэффициенты или требуемое соотношение между входными токами транзисторов задается путем изменения геометрических размеров между ба зовыми р-областями п-р-п или эмиттер ными р-областями переинжектирующих р-п-р-транзисторов. В предлагаемой схеме, чтобы не загромождать чертеж и облегчить понимание принципа работы схемы (на фиг.1), связь между коллекторами инжектирующего транзистора 25 с элементами схемы показана условно стрелками, с указанием значения Тока,инжектируемого в данный транзистор, согласно выражению (1), Причем для определенности срабатывания пороговых элементов в их базы инжектируются токи на 0,5 дискрете меньше требуемого значения. В эми теры переинжектирующих транзисторов 21-24 инжектируются такие значения тока, с учетом коэффициентов передачи по току, при которых их коллектор ные токи равны двум дискретным, одна ко на чертеже считается, что их коэф фициенты передачи по току равны единице. На фиг.2 приводится топологический чертеж фрагмента схемы, вклю чающий транзисторы 1, 2, 3, 13, 21, 16, 10, 19, 20,,24 и 25. Схема контроля и четность реализует функцию четности в зависимости от значения контрольного разряда в следующим образом ри в 1, F 1 при четном числе 1 F О при нечетном числе .Vi,.. при в о реализуется функция нечетности F 1 при нечетном числе 1.. В дальнейшем мы будем рассматривать принцип работы схемы при В 1. Предположим, что на входы 26-34 устройства задается следующая входная комбинация входных сигналов (четное число единиц) AI А 1; А,, 0; А,, А АЬ А 1, Ag 0; в 1. В этом случае, коллекторные токи транз исторов 1,2, 4, 5, 6, 7, и9 . равны входным токам (единице),так как токовые повторители имеют коэффициенты передачи равные единице по всем коллекторам, а транзисторы 3 и 8 закрыты, так как их входные токи отбираются входными шинами. Следовательно с баз транзисторов 13 и 16 коллекторами входных транзисторов 1-9 будет отбираться два дискрета тока, с баз транзисторов 14, 17 - три дискрета тока, а с баз транзисторов 15 и 18 - два дискрета тока. Так как в базы транзисторов 13-15 инжектируются транзистором 25 1,5 дискрета тока, то они все три закроются, запирание этих транзисторов приведет к тому,что в базы транзисторов 16 18 через транзисторы 21-23 будут инжектироваться дополнительно, по два дискрета тока, а в сумме по 2,5 дискретна тока, а с учетом значений отбираемых с их входов значений тока, транзистор 16 откроется (входной ток равен 0,5 дискрета), транзистор 17 закроется (входной ток равен нулю), а транзистор 18 будет открыт. Так как транзисторы 16 и 18 открыты, то транзисторы 10 и 12 закроются, а так как транзистор 17 закрыт, то коллекторный ток транзисто- ра 11 равен одному дискрету тока, поггтому с баз транзисторов 19 и 20 будет отбираться один дискрет тока. В этом случае, транзистор 20 откроется (входной ток равен 0,5 дискрета) и отбирает через свой коллектор эмиттерный ток транзистора 24, следовательно, в базу транзистора 19 будет инжектироваться транзистором 24 ток равный 0,5 дискрета, которьй буг дет полностью отбираться через коллектор транзистора 11, поэтому на выходе 35 получим выходной сигнал равньш F 1. Если на входы 26-34 устройства подать входную комбинацию с нечетным числом единицы, например А, 1; 2 ъ 1 5 А 1, То при такой комбинации .входных сигналов транзисторы 13 и 14 будут насыщены и через свои коллекторы отберут токи, инжектируемые транзистором 25 в эмиттеры транзисторов 21 и 22, поэтому в .базы транзисторов 16 и 17 будут инжектировать ся токи по 0,5 дискрета, а транзистор15 будет закрыт, так как с ег8 входа транзисторами 7-9 будет отбираться 3 дискрета тока. Запирание транзистора 15 приведет к тому, что в базу транзистора 18 будет .инжектироваться ток 2, 5 дискрета, который однако будет полностью отбираться че рез коллекторы открытых транзисторов 7-9. Следовательно транзисторы 16 и 18будут закрыты, а транзистор 17 насыщен. Поэтому транзистор 1 1 закроется, а транзисторы 10 и 12 через свои коллекторы с баз транзисторов 19и 20 будут.отбираться по одному дискрету тока, что приведет к запира нию транзистора 20, а как следствие этого, к инжекции в базу транзистора 19, транзистором 25 через транзистор 24 двух-дискретов тока, поэтом суммарный ток, которьш инжектировал в базу транзистора 19, будет равен 2,5 дискрета. Однако с учетом токов отбираемых транзисторами 10 и 12 с базы транзистора 19, его базовый ток будет равен 0,5 дискрета, транзистор 19 откроется и на выходе 35 установится сигнал F 0. Таким образом, предлагаемое устр ство реализует требуемую функцию ко тропя на четность. Формула изобретени Схема контроля на четность И Л т па, содержащая двенадцать трехколле торных, Восемь одноколлекторньп ; транзисторов и многоколлекторньш ин жектирующий р-п-р-транз;истор, эмитт которого соединен с шиной питания. первые двадцать кол;1е.ктороп сг:единеньг с базами п-р-п-транзисторов, а база - с эмиттерами п-р-п-транзисторов иобщей шиной, причем базы девяти трехколлекторных транзисторов соединены с cooтвeтcтвyющиIvIи девятью входами, первые коллекто ры первого, второго, третьего,, затем четвертого, пятого, шестого,а также седьмого, вось-п транзисторов объединены соответственно с базами первого, затем второго, а также третьего одноколлекторных п-р-п-транзисторов, вторые коллекторы первого, второго, третьего, затем четвертого, пятого, шестого, а также седьмого, восьмого, девятого трехколлекторных п-р-п-транзисторов объединены соответственно с базами четвертого, затем п.ятого, а также шестого одноколлекторных п-р-п-транзисторов, первые и соответственно вторые коллекторы десятого, одиннадцатого и двенадцатого трехколлекторных п-р-п-транзисторов соединены с базами седьмого и соответственно восьмого одноколлекторных п-р-п-транзисторов, о т .л и-ч а ю щ а яс я тем, что,, с целью увеличения надежности, в нее введены четьфе переинжектирующих р-п р-транзистора, базы которых соединены с общей шиной, а эмиттеры - соответственно -с коллекторами первого, второго, третьего и восьмого одноколлекторных п-р-п-транзисторов и двадцать первьну, двадцать вторым, двадцать третьим и двадцать четвертым коллекторами инжектирующегб р-п-р-транзистора, а коллекторы соединены соответственно с базами четвертого, пятого, шестого и седьмого .одноколлекторных п-р-п-транзисторов,третий коллектор каждого из трехколлек- , Торных п-р-п-транзисторов соединен с базой этого же транзистора,коллекторы четвертого., пятого и шестого одноколлекторных транзисторов подключены соответственно к базам десятого, одиннадцатого и двенадцатого трехколлек- . торных п-р-п-транзксторов, коллектор седьмого одноколлекторого п-р-п-тоан. зистора подклЕочен в: выходу.

| Орлов И.А | |||

| и др | |||

| Основы эксплуатации и ремонта ЭВМ | |||

| М., Энергоиздат, 1981, с.74, рис.5-3 | |||

| Шагурин И.И, и др | |||

| Руководство по схемотехническому проектированию цифровых БИС и сверх БИС на базе интегральной инжекционной логики | |||

| Отчет по научно-исследовательской работе инв | |||

| № 6801544, номер гос.регистрации 75026815, М., 1979, с.66, рис.42. |

Авторы

Даты

1986-11-07—Публикация

1985-05-12—Подача