со

5 СП

: Изобретение относится к средствам формирования и управления случайным Процессом с заданными спектральными сарактеристиками и может быть использовано в качестве задающей части цифровых систем автоматического управления широкополосной случайной вибрацией, а также в системах имитационного моделирования сложных объектов.

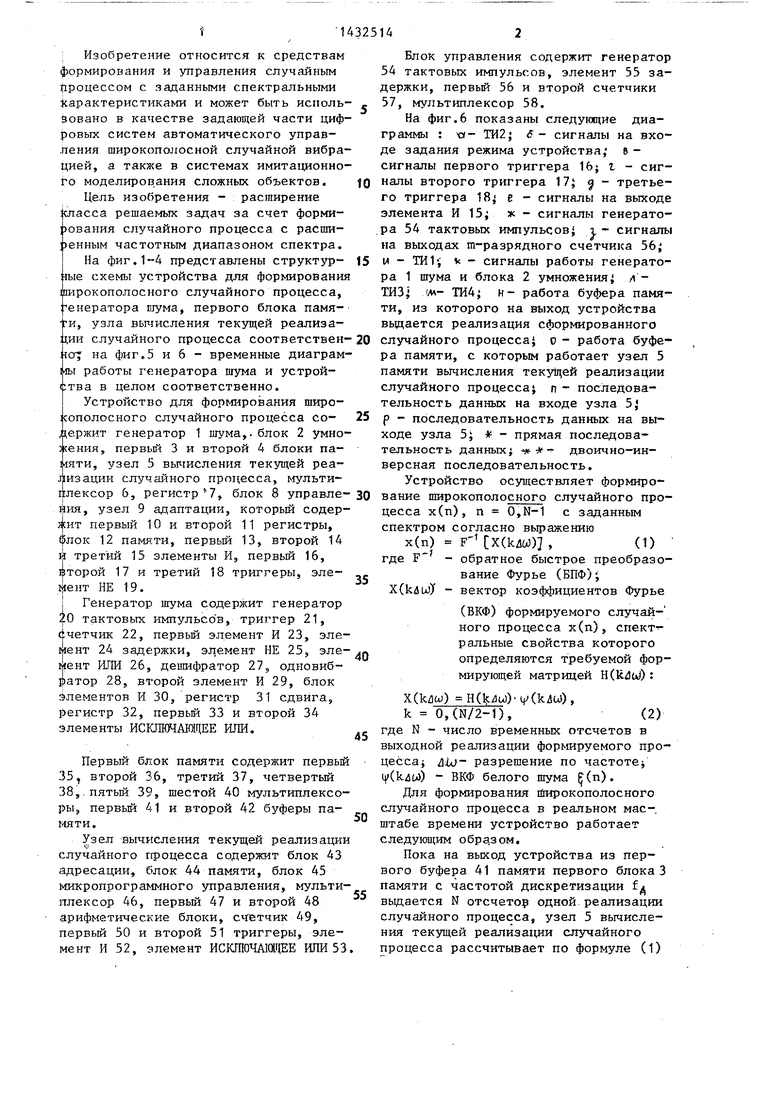

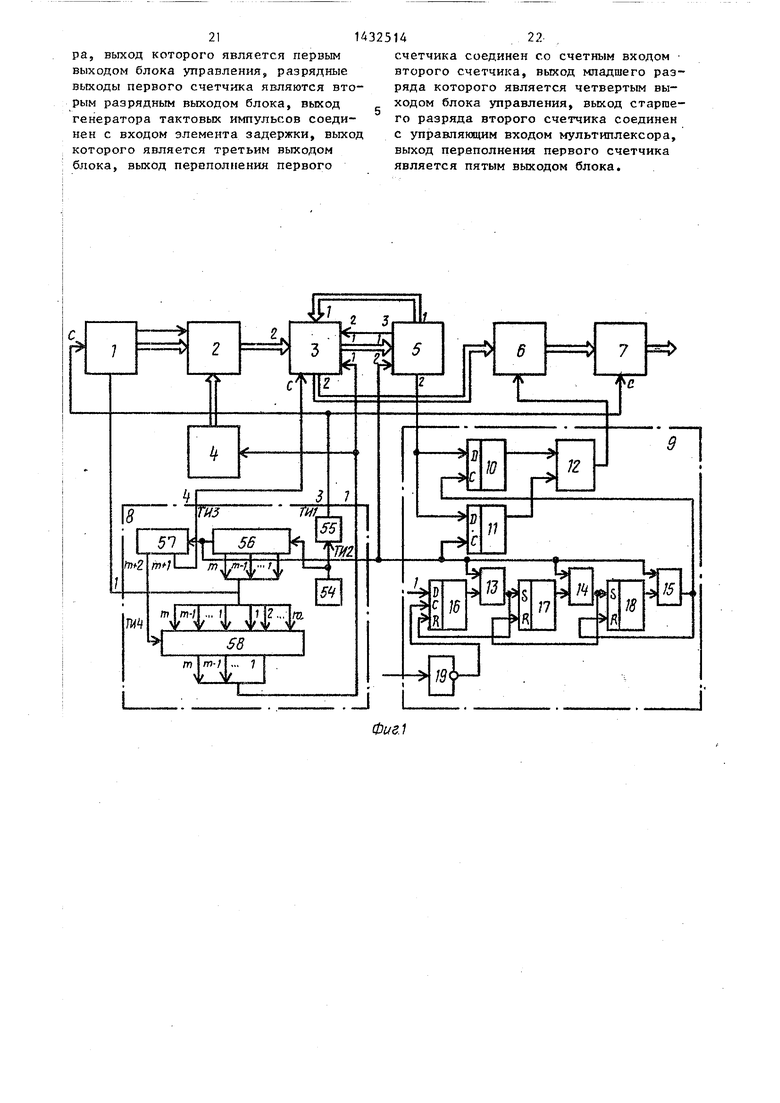

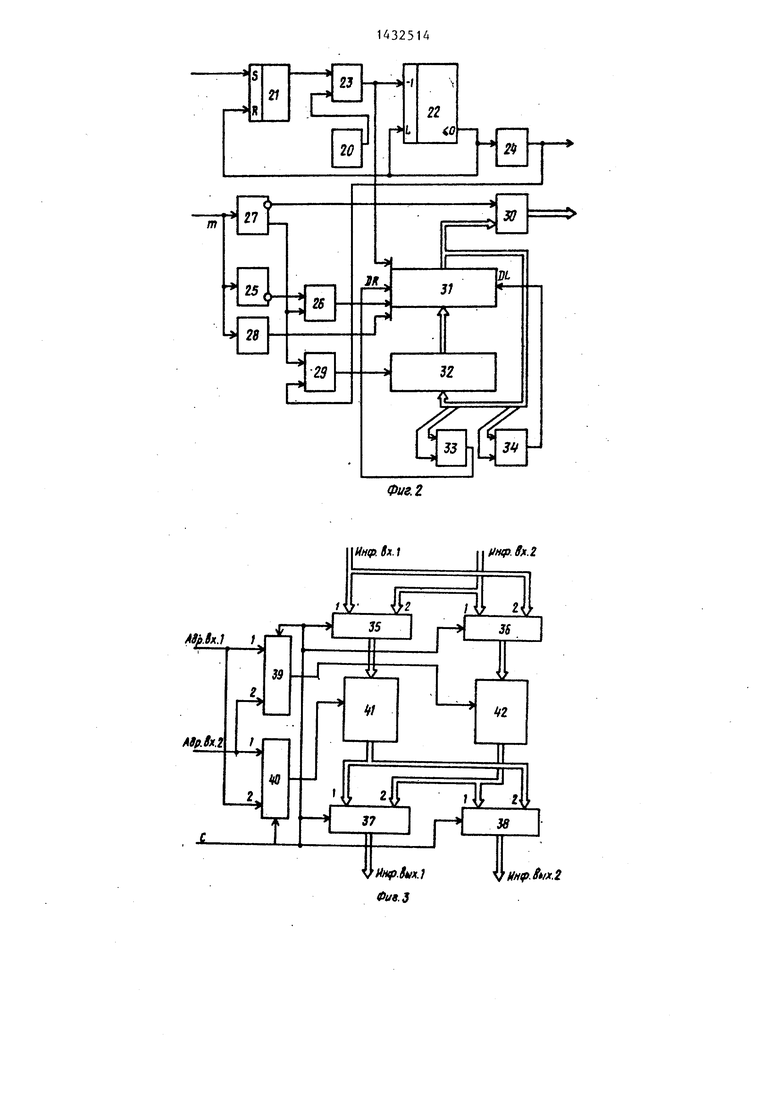

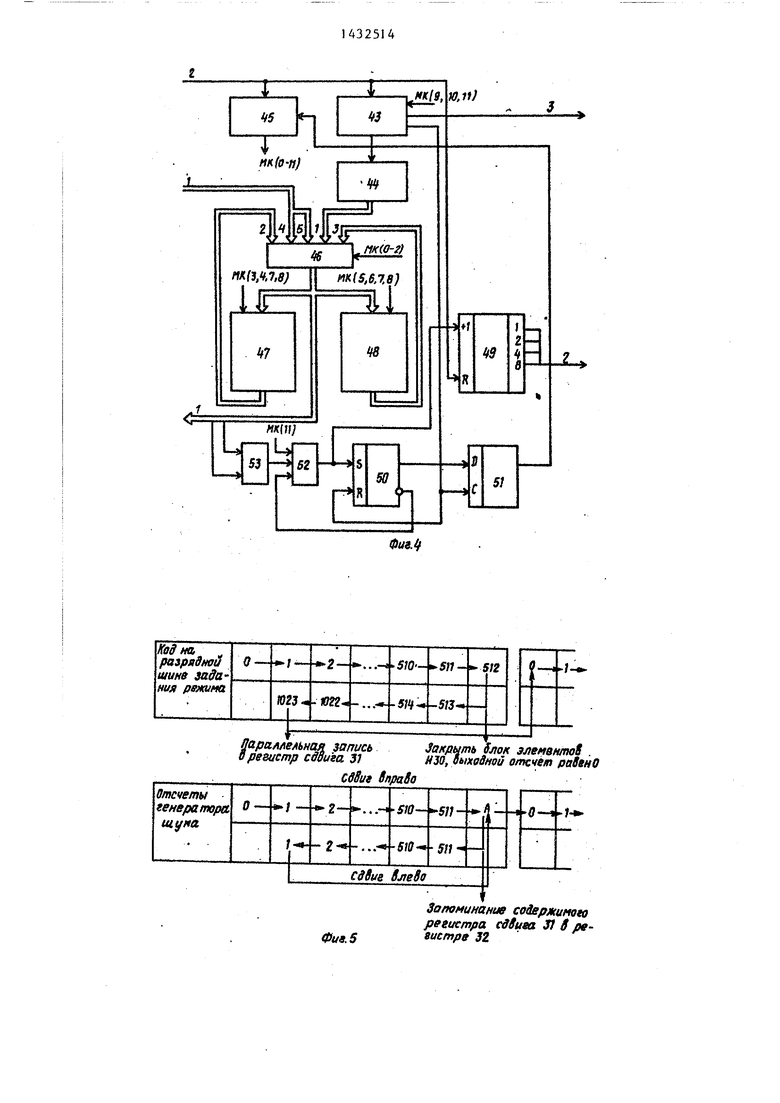

Цель изобретения - расширение jcnacca решаемых задач за счет форми- |эования случайного процесса с расширенным частотным диапазоном спектра, I На фиг.1-4 представлены структур- рые схемы устройства для формирования 1рокополосного случайного процесса, : енератора птума, первого блока памяти, узла вычисления текущей реализации случайного процесса соответствен- ист на фиг,5 и 6 - временные диаграм- иы работы генератора шума и устройства в целом соответственно.

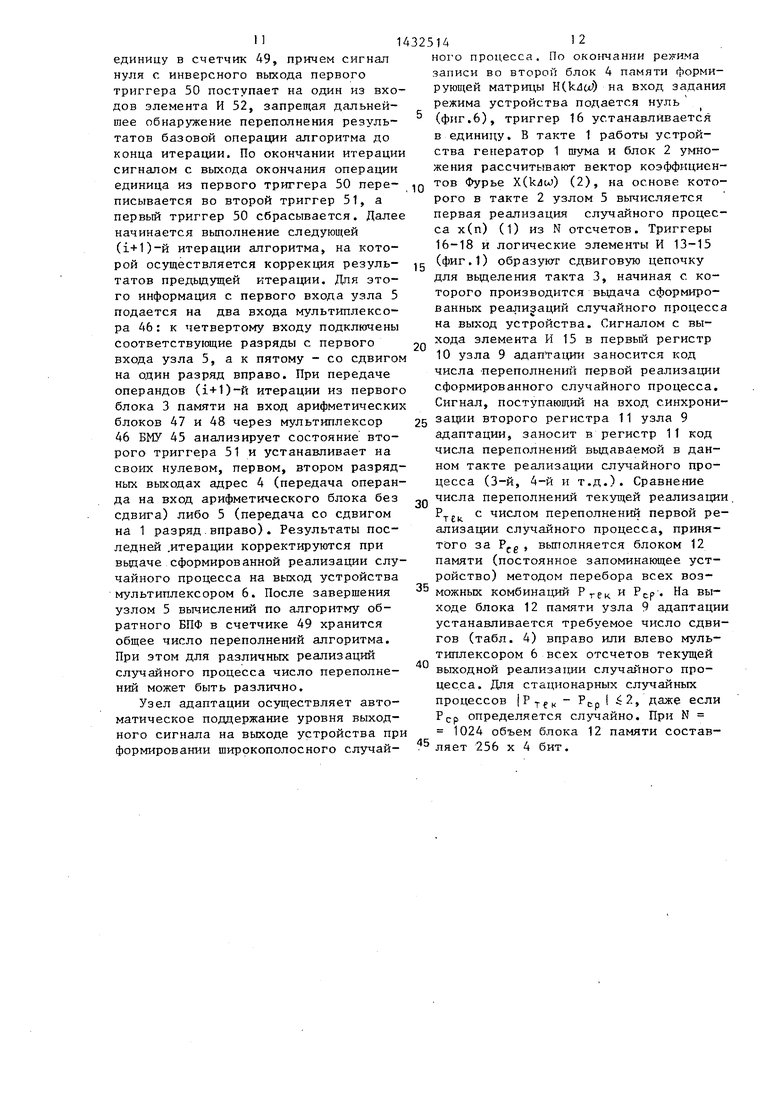

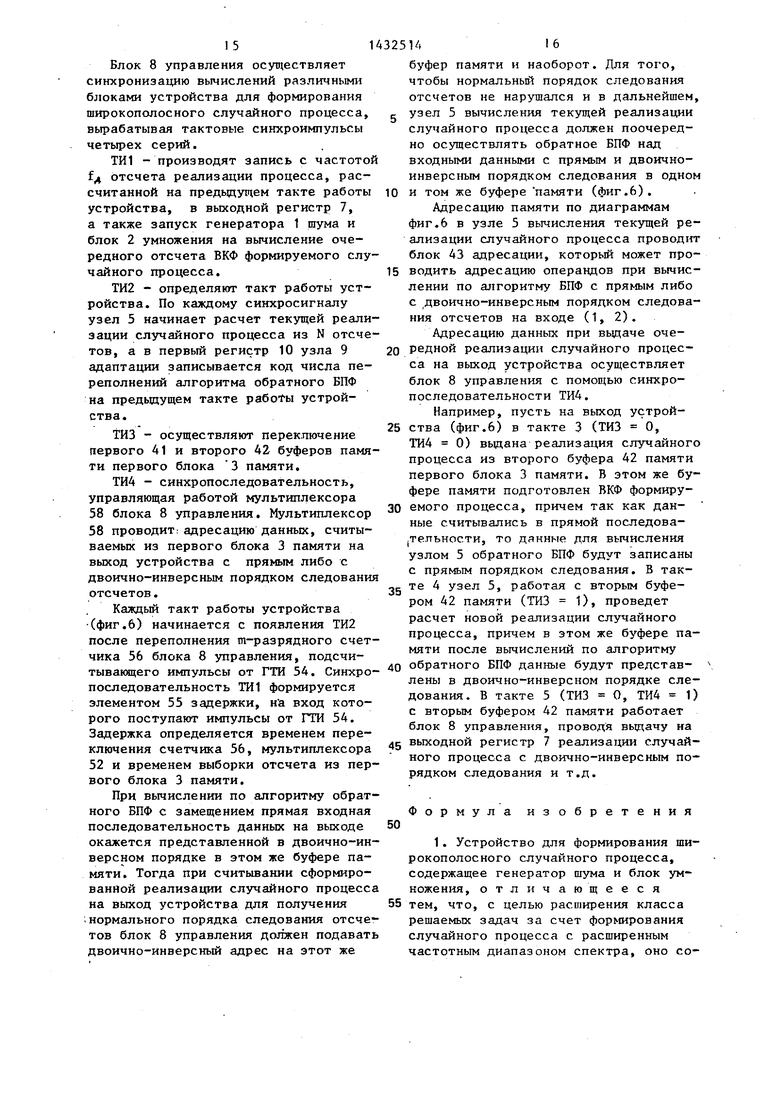

Устройство для формирования широ- 1СОПОЛОСНОГО случайного процесса содержит генератор 1 шума,, блок 2 умно- зкения, первьй 3 и второй 4 блоки памяти, узел 5 вычисления текущей реализации случайного процесса, мультиплексор 6, регистр 7, блок 8 управле- $ия, узел 9 адаптации, которьй содер- ит первый 10 и второй 11 регистры, флок 12 памя:ти, первьш 13, второй 14 $ третий 15 элементы И, первьй 16, торой 17 и третий 18 триггеры, эле- фент НЕ 19.

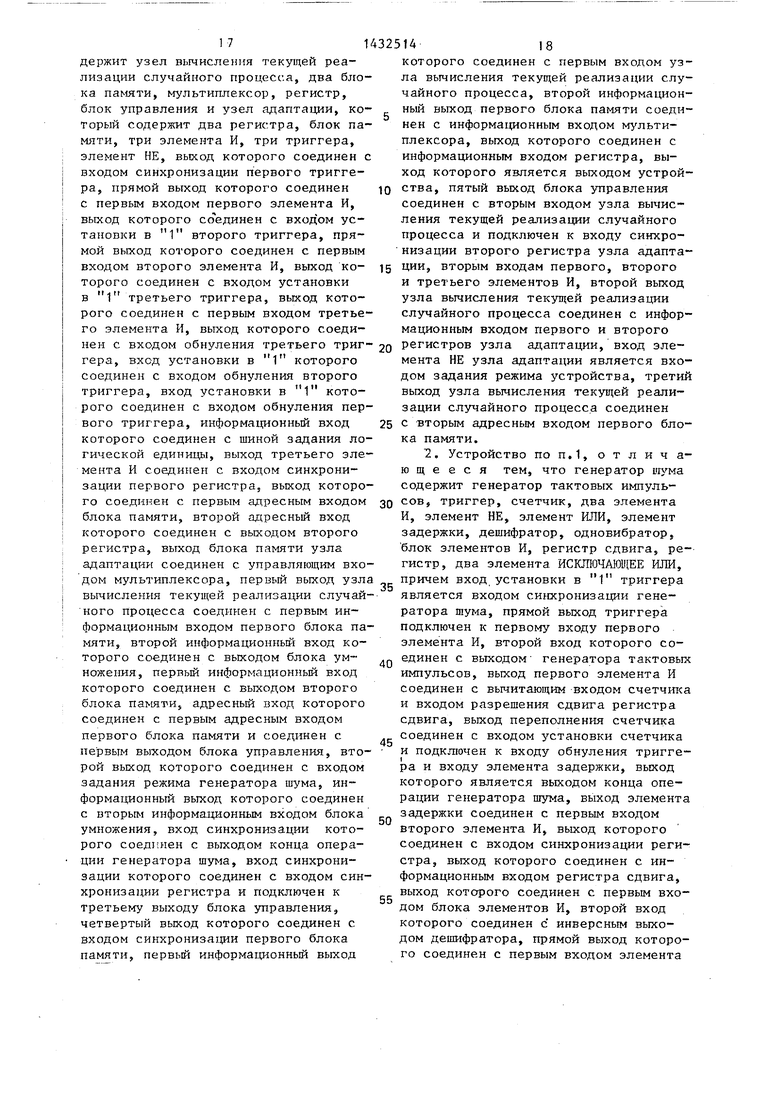

I Генератор шума содержит генератор 0 тактовых импульсо в, триггер 21, йчетчик 22, первьй элемент И 23, эле- ijieHT 24 задержки, элемент НЕ 25, эле- ijieHT ИЛИ 26, дешифратор 27,, одновиб- ратор 28, второй элемент И 29, блок элементов И 30, регистр 31 сдвига, регистр 32, первьй 33 и второй 34 элементы ИСКЛШАМЦЕЕ ИЛИ,

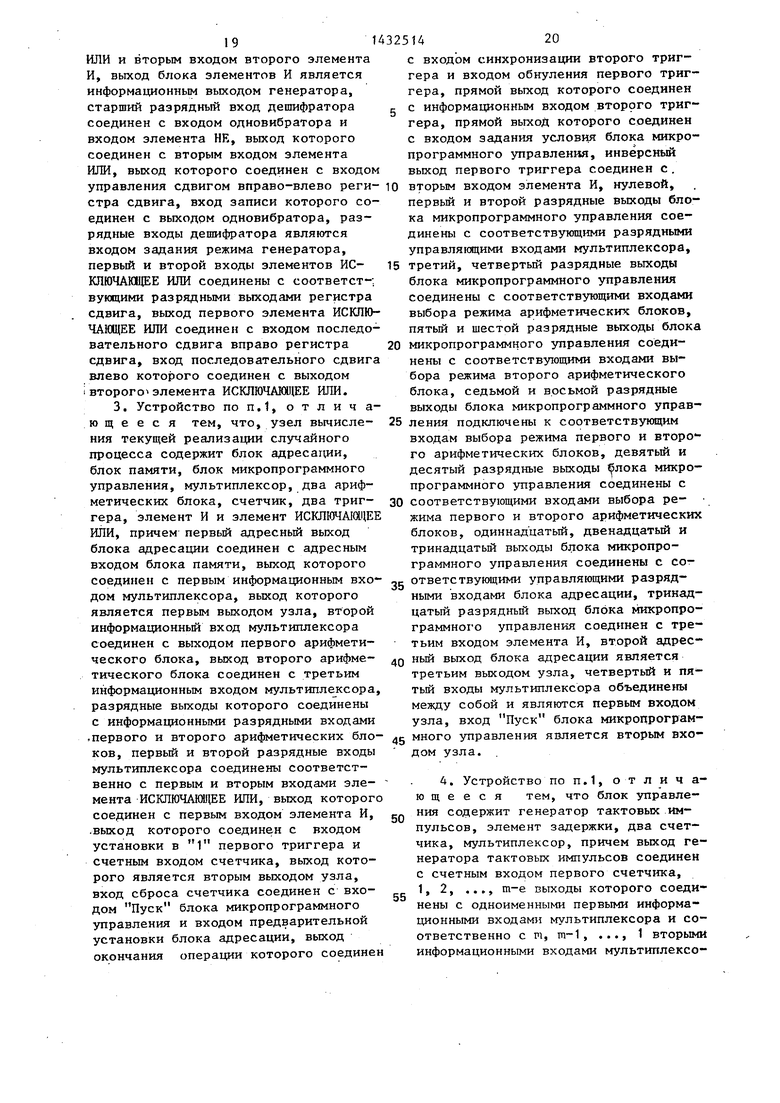

Первый блок памяти содержит первый 35, второй 36, третий 37, четвертый 38,.пятьй 39, шестой 40 мультиплексоры, первьй 41 и второй 42 буферы .

Узел вычисления текущей реализации случайного гфоцесса содержит блок 43 адресации, блок 44 памяти, блок 45 1чикропрограммного управления, мультиплексор 46, первый 47 и второй 48 арифметические блоки, счетчик 49, первый 50 и второй 51 триггеры, эле мент И 52, ;и1емент ИСКШОЧАКХЦЕЕ ИЛИ 53

0

5

0

5

0

5

0

5

Блок управления содержит генератор 54 тактовых импульсов, элемент 35 задержки, первьй 56 и второй счетчики 57, мультиплексор 58.

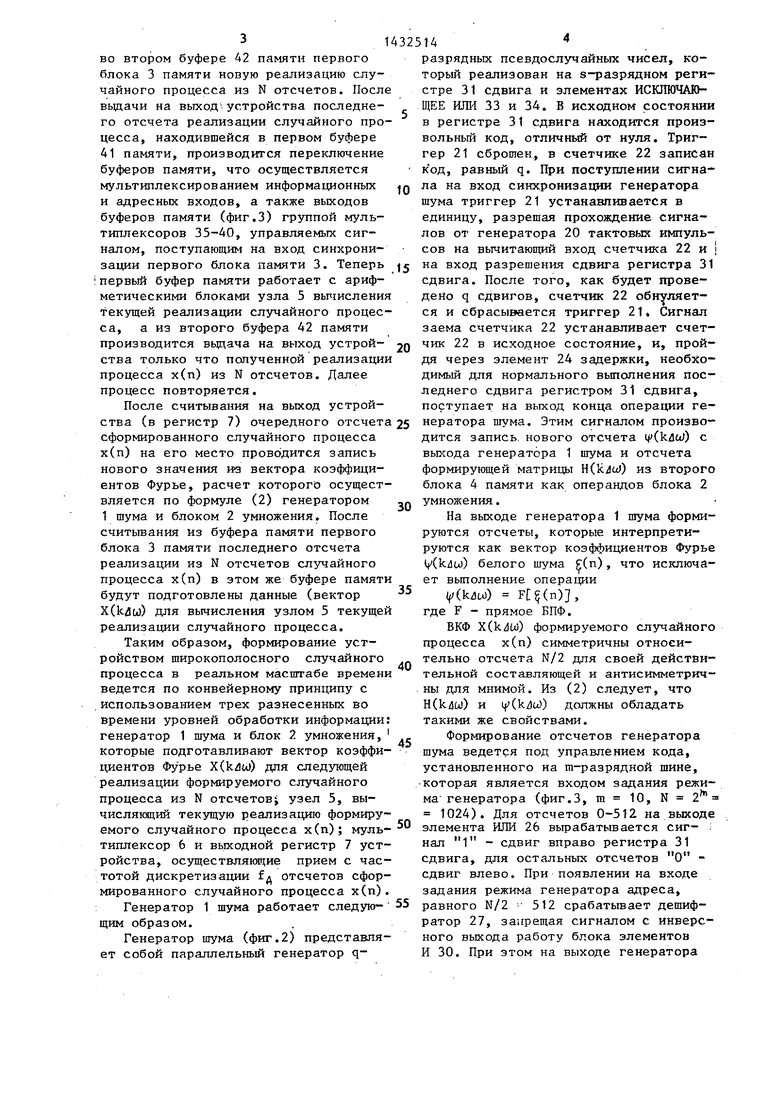

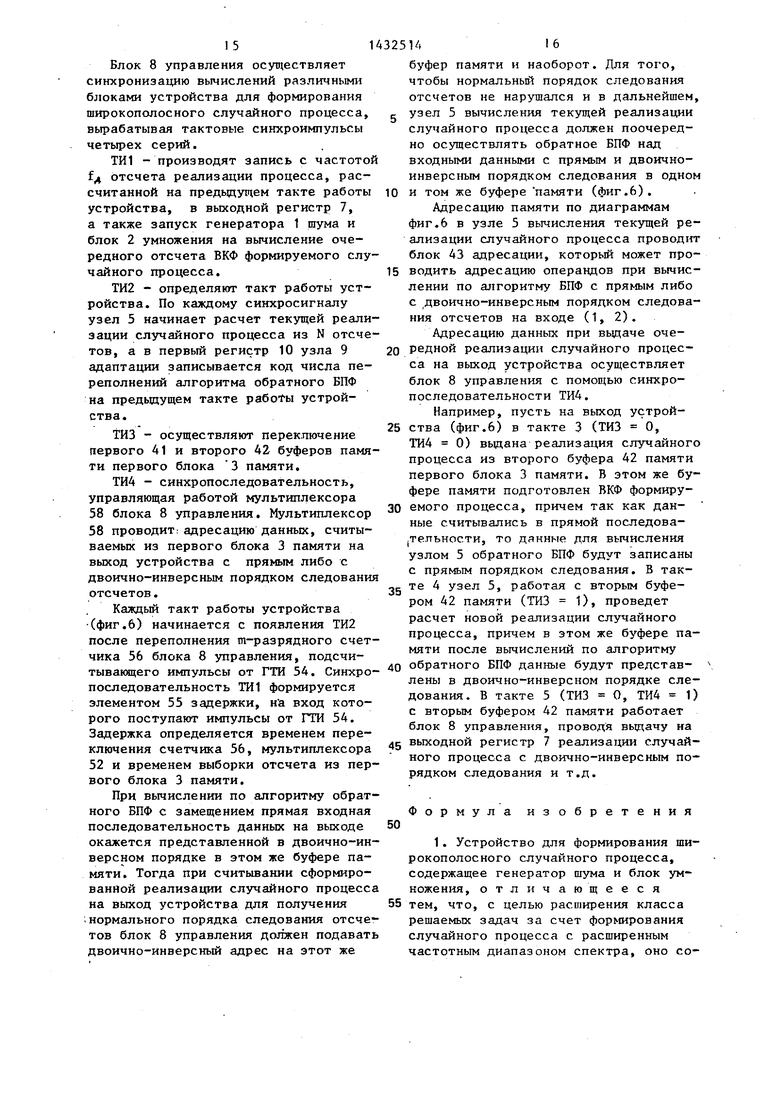

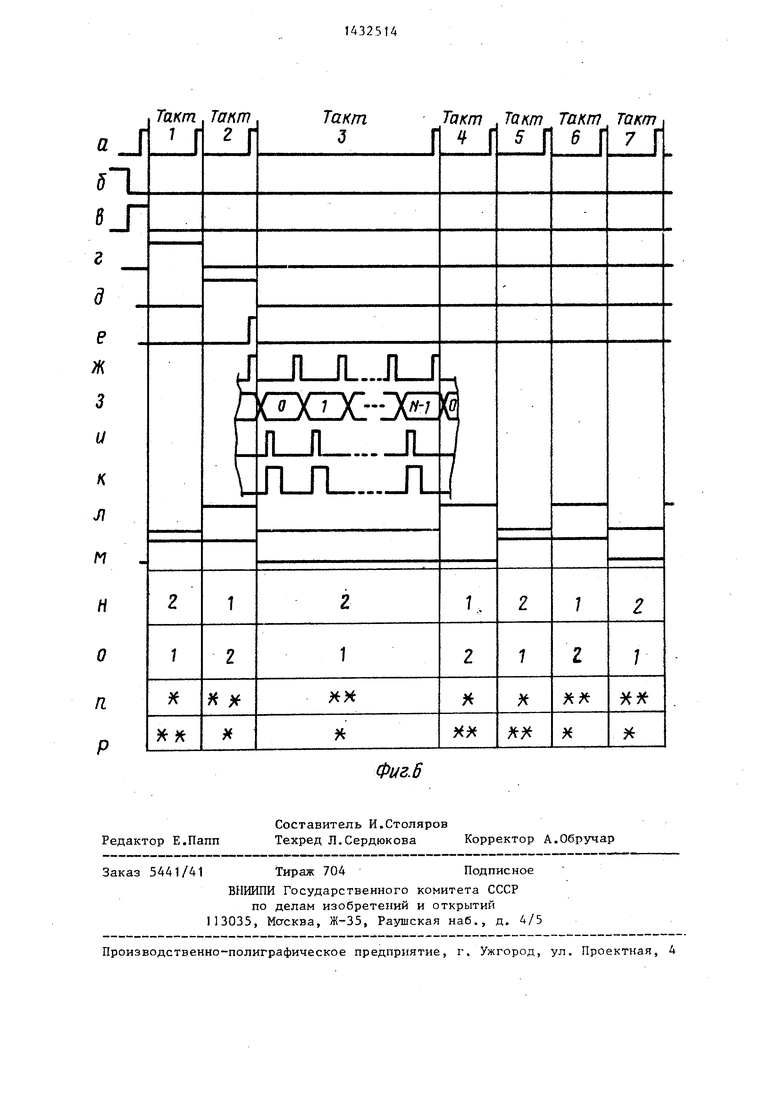

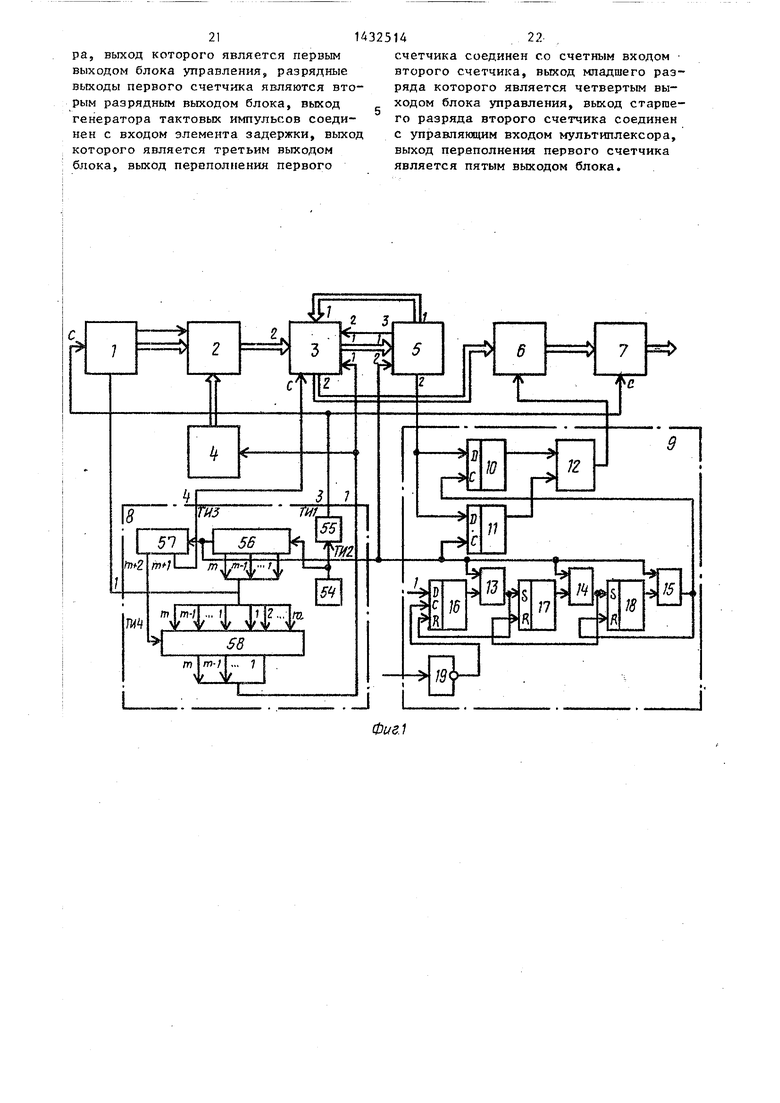

На фиг.6 показаны следующие диаграммы : «- ТИ2; - сигналы на входе задания режима устройства,- в - сигналы первого триггера 16j г - сигналы второго триггера 17J - третьего триггера 18 е - сигналы на выходе элемента И 15; ж - сигналы генерато- .ра 54 тактовых импульсов} г- сигналы на выходах т-разрядного счетчика 56 и - ТИ1-; к - сигналы работы генератора 1 шума и блока 2 умножения; л- TH3i W- ТИ4; к- работа буфера памяти, из которого на выход устройства вьщается реализация сформированного случайного процессаJ о - работа буфера памяти, с которым работает узел 5 памяти вычисления теку1цей реализации случайного процессаJ п - последовательность данных на входе узла 5j р - последовательность данных на выходе узла 5; - прямая последовательность данных - - двоично-инверсная последовательность.

Устройство осуществляет формирование широкополосного случайного процесса х(п), п 0,N-1 с заданным спектром согласно выражению

х(п) F Сх(МбО) , (1) где F - обратное быстрое преобразование Фурье (БПФ); X(kdu)) - вектор коэффициентов Фурье

(ВКФ) формируемого случай- ного процесса х(п), спект- ральные свойства которого определяются требуемой формирующей матрицей H(lt4oJ):

X(kda)) H()- ц(Ш) ,

k 0,(N/2-1),(2)

где N - Х1ИСЛО временных отсчетов в выходной реализации формируемого процесса j ЛИ(} разрешение по частоте j lyCk/itA)) - ВКФ белого шума (п).

Для формирования йирокополосного случайного процесса в реальном мае-, штабе времени устройство работает следующим обра,зом.

Пока на выход устройства из первого буфера 41 памяти первого блока 3 памяти с частотой дискретизации fд вьщается N отсчетор одной реализации случайного процесса, узел 5 вычисления текущей реализагщи случайного процесса рассчитывает по формуле (1)

во втором буфере 42 памятн первого блока 3 памяти новую реализацию случайного процесса из N отсчетов. После вьщачи на выход-устройства последнего отсчета реализации случайного процесса, находившейся в первом буфере 41 памяти, производится переключение буферов памяти, что осуществляется мультиплексированием информационных и адресных входов, а также выходов буферов памяти (фиг.З) группой мультиплексоров 35-40, управляемых сигналом, поступающим на вход синхронизации первого блока памяти 3. Теперь первый буфер памяти работает с арифметическими блоками узла 5 вычисления текущей реализации случайного процесса, а из второго буфера 42 памяти производится вьщача на выход устрой- ства только что полученной реализации процесса х(п) из N отсчетов. Далее процесс повторяется.

После считывания на выход устрой-

10

20

32514

разрядных псевдослучайных чисел, который реализован на s-разрядном регистре 31 сдвига и элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 33 и 34. В исходном состоянии в регистре 31 сдвига находится произвольный код, отличный от нуля. Триггер 21 сброшен, в счетчике 22 записан к од, равный q. При поступлении сигнала на вход синхронизации генератора шума триггер 21 устанавливается в единицу, разрешая прохождение сигналов от генератора 20 тактовых шшуль- сов на вычитающий вход счетчика 22 и | на вход разрешения сдвига регистра 31 сдвига. После того, как будет проведено q сдвигов, счетчик 22 обнуляется и сбрасывается триггер 21. Сигнал заема счетчика 22 устанавливает счетчик 22 в исходное состояние, и, пройдя через элемент 24 задержки, необходимый для нормального вьшолнения последнего сдвига регистром 31 сдвига, поступает на выход конца операции ге15

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор вибросейсмических данных | 1989 |

|

SU1665326A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для адресации процессора быстрого преобразования Фурье | 1985 |

|

SU1298765A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве задающей части цифровых систем автоматического управления. Цель изобретения - расширение класса решаемых задач за счет формирования случайного процесса с расширенным частотным диапазоном спектра. Устройство содержит генератор шума, блок умножения, два блока памяти, узел вычисления текущей реализации случайного процесса, мультиплексор, три регистра, три элемента И, три триггера, элемент ИЛИ, блок управления. Поставленная цель достигается за счет введения новых блоков с соответствующими функциональными связями. 3 з.п. ф-лы, 6 ил., 4 табл. с ® (Л

30

ства (в регистр 7) очередного отсчета 25 нератора пгума. Этим сигналом произво- сформированного случайного процесса х(п) на его место проводится запись нового значения з вектора коэффициентов Фурье, расчет которого осуществляется по формуле (2) генератором 1 шума и блоком 2 умножения. После считьшания из буфера памяти первого блока 3 памяти последнего отсчета реализации из N отсчетов слз айного процесса х(п) в этом же буфере памяти будут подготовлены данные (вектор )) для вычисления узлом 5 текущей реализации случайного процесса.

Таким образом, формирование устройством широкополосного случайного процесса в реальном масштабе времени ведется по конвейерному принципу с ,использованием трех разнесенных во времени уровней обработки информации: генератор 1 шума и блок 2 умножения, которые подготавливают вектор коэффициентов Фурье X(k4U)) для следующей реализации формируемого случайного процесса из N отсчетовj узел 5, вычисляющий текущую реализацию формируемого случайного процесса х(п); муль- тиштексор 6 и выходной регистр 7 устройства, осуществляющие прием с частотой дискретизации f отсчетов сформированного случайного процесса х(п).

40

45

дится запись, нового отсчета ((kuu)) с выхода генератора 1 шума и отсчета формирующей матрицы H(k/ltd) из второго блока 4 памяти как операьздов блока 2 умножения.

На выходе генератора 1 шума формируются отсчеты, которые интерпретируются как вектор коэффициентов Фурье V(kilu)) белого шума г(п), что исключает выполнение операции

V(k4W) F(n), где F - прямое БПФ.

ВКФ X(kjw) формируемого случайного процесса х(п) симметричны относительно отсчета N/2 для своей действительной составляющей и антисимметричны для мнимой. Из (2) следует, что H(k/3ut) и if Ck cO) должны обладать такими же свойствами.

Формирование отсчетов генератора шума ведется под управлением кода, установленного на т-разрядной шине, -которая является входом задания режима генератора (фиг.З, m 10, N 2 1024). Для отсчетов 0-512 на выходе элемента ИЛИ 26 вырабатывается сигнал 1 - сдвиг вправо регистра 31 сдвига, для остальных отсчетов О - сдвиг влево. При появлении на входе задания режима генератора адреса.

Генератор 1 шума работает следую- 55 равного N/2 512 срабатывает дешифщим образом.

Генератор шума (фиг.2) представляет собой параллельный генератор q0

5 нератора пгума. Этим сигналом произво-

0

5

дится запись, нового отсчета ((kuu)) с выхода генератора 1 шума и отсчета формирующей матрицы H(k/ltd) из второго блока 4 памяти как операьздов блока 2 умножения.

На выходе генератора 1 шума формируются отсчеты, которые интерпретируются как вектор коэффициентов Фурье V(kilu)) белого шума г(п), что исключает выполнение операции

V(k4W) F(n), где F - прямое БПФ.

ВКФ X(kjw) формируемого случайного процесса х(п) симметричны относительно отсчета N/2 для своей действительной составляющей и антисимметричны для мнимой. Из (2) следует, что H(k/3ut) и if Ck cO) должны обладать такими же свойствами.

Формирование отсчетов генератора шума ведется под управлением кода, установленного на т-разрядной шине, -которая является входом задания режима генератора (фиг.З, m 10, N 2 1024). Для отсчетов 0-512 на выходе элемента ИЛИ 26 вырабатывается сигнал 1 - сдвиг вправо регистра 31 сдвига, для остальных отсчетов О - сдвиг влево. При появлении на входе задания режима генератора адреса.

ратор 27, запрещая сигналом с инверсного выхода работу блока элементов И 30. При этом на выходе генератора

514

появляется отсчет, равный нулю. После проведения последнего сдвига вправо содержимое регистра 31 сдвига запоминается в регистре 32. С этого сое- тояния начинается работа генератора шума при формировании очередной сек- 1ЩИ V(kju). Далее начинается сдвиг содержимого регистра 31 сдвига в обратном направлении (влево), т.е. от- счеты группируются симметрично относительно отсчета N/2 (фиг.5). После формирования последнего отсчета в секции адрес на входе задания режима генератора изменяется с 1024 на О,

Блок 2 умножения предназначен для вычислений по формуле (2). По сигна- jny, поступагадему на вход синхрониза- ии, блок умножения производит вьшол- нение операции умножения над операндами, установленными на первом и втором информа;ционных входах. По оконча- ии вычислений результат выдается на

1 + 1

,Af + B,W а,. (b,.w,,

В

i + i

- bifW.) ч- Jla. + (b,w,. + b,,.Wj.)J;

Ы

Ai -BiW . a,,- - ( „.-b j-W2() + ,- - (bi,-w,; + bt,-w,-) ,

где A- avj + ja,. , W w,. + jw.

B;,

11

Ч- jb

It

- комплексные входпредьщущему результату и запоминаются в накопительном регистре (HP). На :ные числа и поворачивающие множители 40 первом арифметическом блоке 47 вьтис- соответственно, i 1 ,m,ляются действительные значения Re (А

Основу узла 5 (фиг.4) составляют и Re(B ,4i), а на втором блоке 48 - два идентичных арифметических блока мнимые 1т(А;+,) и Im(B,), в следу- 47 и 48, осуществляющих операцию умно- ющей последовательности, задаваемой жения последовательно с анализом двух 45 блоком 45 микропрограммного управле- разрядов регистра множителя, причем ния (ЕМУ). Результаты приведены в частичные произведения добавляются к табл. 2.

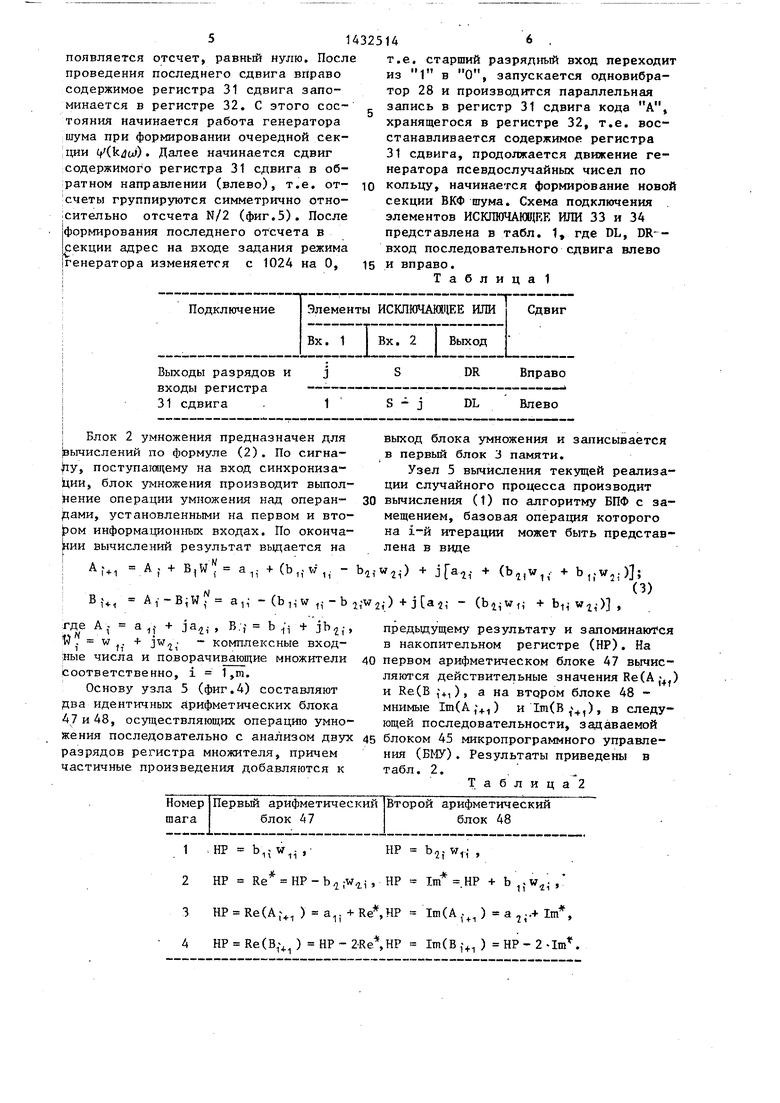

Т а б л и ц а 2

Номер Первьй арифметический

шага

блок 47

HP b,,. w. ,

HP Re , , HP HP Re(A, a.. + Re,HP

+ b,jw. ,

1i

Im(A,.J a,,..+ Im, HP Re(B,v, ) HP 2 Re ,HP Im(B ,-+ ) HP - 2 -Im.

1+1

146 ,

т.е. старший разрядный вход переходи из 1 в О, запускается одновибра- тор 28 и производится параллельная запись в регистр 31 сдвига кода А, хранящегося в регистре 32, т.е. восстанавливается содержимое регистра 31 сдвига, продолжается движение генератора псевдослучайных чисел по кольцу, начинается формирование ново секции ВКФ шума. Схема подключения элементов ИСКЛЮЧАЩЕЕ ИЛИ 33 и 34 представлена в табл. 1, где DL, DR-- вход последовательного сдвига влево и вправо.

Таблица 1

выход блока умножения и записывается в первый блок 3 памяти.

Узел 5 вычисления текущей реализации случайного процесса производит 30 вычисления (1) по алгоритму БПФ с замещением, базовая операция которого на 5.-Й итерации может быть представлена в виде

Второй арифметический блок 48

HP bo. w,,. ,

+ b,jw. ,

714

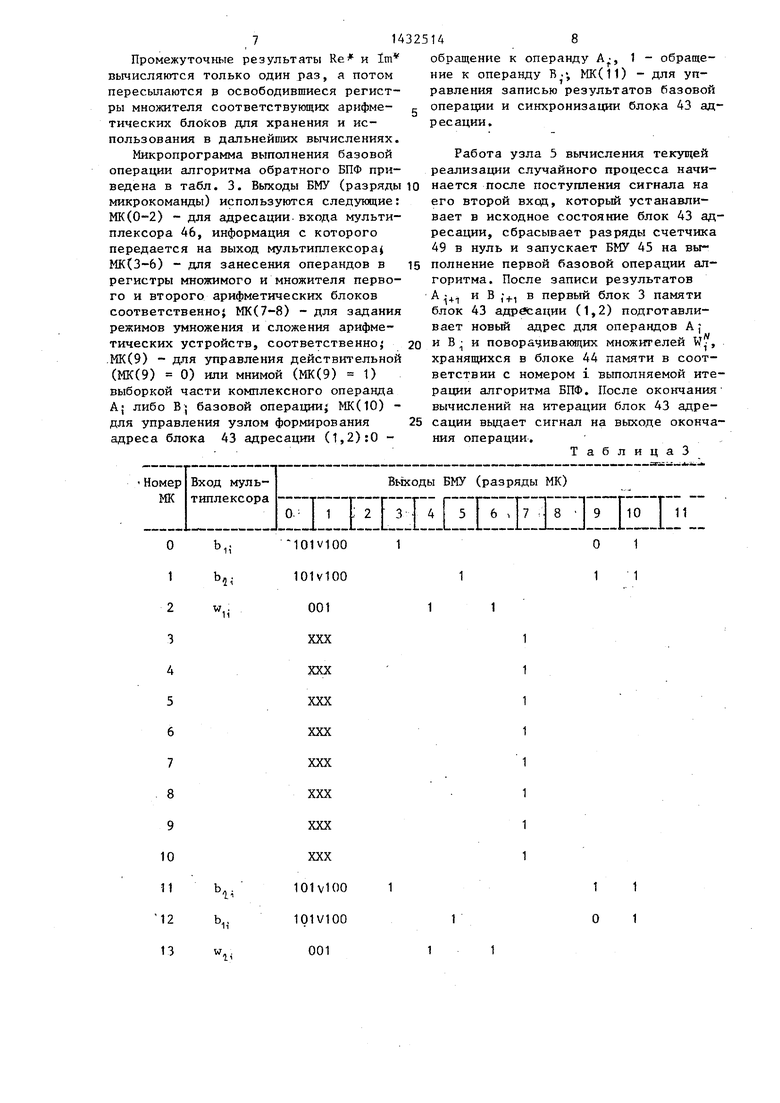

Промежуточные результаты Re и Im вычисляются только один раз, а потом пересылаются в освободившиеся регистры множителя соответствующих арифме- тических блоков для хранения и использования в дальнейших вычислениях. Микропрограмма выполнения базовой операции алгоритма обратного БПФ приведена в табл. 3. Выходы ЕМУ (разряды микрокоманды) используются следующие: МК(0-2) - для адресации.входа мультиплексора 46, информация с которого передается на выход мультиплексораj МК(З-б) - для занесения операндов в регистры множимого и множителя первого и второго арифметических блоков соответственно} МК(7-8) - для задания режимов умножения и сложения арифметических устройств, соответственноj ,МК(9) - Д.ПЯ управления действительной (МК(9) 0) или мнимой (МК(9) 1) выборкой части комплексного операнда А; либо В; базовой операции; МК(10) - для управления узлом формирования адреса блока 43 адресации (1,2):0 Номер

МК

Вход мультиплексора

Вь1ходы БМУ (разряды МК)

Ы311 - 11 1И1ТГ- --П1 П

bi

N

li

lOlvtOO lOlvlOO

001

XXX

XXX XXX XXX XXX XXX

Ч.

г

XXX

XXX

lOlvlOO 101V100

001

148

обращение к операнду А

1 - обращение к операнду В.; МК(11) - для управления записью результатов базовой операции и синхронизации блока 43 адресации.

Работа узла 5 вычисления текущей реализации случайного процесса начинается после поступления сигнала на его второй вход, который устанавливает в исходное состояние блок 43 адресации, сбрасывает разряды счетчика 49 в нуль и запускает БМУ 45 на выполнение первой базовой операции алгоритма. После записи результатов А: и В ;., в первый блок 3 памяти блок 43 адресации (1,2) подготавливает новый адрес для операндов А; и В и поворачивающих множителей W, хранящихся в блоке 44 памяти в соответствии с номером i вьтолняемой итерации алгоритма БПФ. После окончания вычислений на итерации блок 43 адресации вьщает сигнал на выходе окончания операции.

ТаблицаЗ

Вь1ходы БМУ (разряды МК)

0

1

1 1

0 1

Н3251А

Re Im

r

11

Re(A,v, ) Im(A;,P

Re()

ImCBj)

XXX XXX XXX XXX XXX XXX XXX XXX 010

oil

101V100 lOIVtOO

XXX

010

oil

XXX 010

oil

Примечание, в остальных разрядах микрокоманды (МК), не указанных в приведенной микропрограмме, записываются нули. X - безразличное состояние сигнала j.

Узлом 5 вычисления текущей реализации случайного процесса реализуется ллетод адаптивного масштабирования При вычислении по алгоритму БПФ для минимизации дисперсии ошибки, обусловленной конечной разрядностью арифметических блоков. Входные комплекс- Иые числа представляются в памяти модифицированными кодами. Если на i-й итерации произошло переполнение, то

10 Продолжение табл. 3

0 0

0 0

1 1

1 1

результаты вычисления базовой операции записываются в первый блок 3 памяти нескорректированным сигналом с одиннадцатого разрядного выхода БМУ 45. Этот же сигнал стробирует элемент И 52, Так как на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 53 при переполнении будет ypoBellb единшф 1, то сигнал с выхода элемента И 52 устанавливает первый триггер 50 и добавляет

1

единицу в счетчик 49, причем сигнал нуля с инверсного выхода первого триггера 50 поступает на один из входов элемента И 52, запрещая дальнейшее обнаружение переполнения результатов базовой операции алгоритма до конца итерации. По окончании итерации сигналом с выхода окончания операции единица из первого триггера 50 переписывается во второй триггер 51, а первый триггер 50 сбрасывается. Далее начинается выполнение следующей (1+1)-й итерации алгоритма, на которой осуществляется коррекция результатов предьщущей итерации. Для этого информация с первого входа узла 5 подается на два входа мультиплексора 46 : к четвертому входу подключены соответствующие разряды с первого входа узла 5, а к пятому - со сдвигом на один разряд вправо. При передаче операндов (1+1)-й итерации из первого блока 3 памяти на вход арифметических блоков 47 и 48 через мультиплексор 46 БМУ 45 анализирует состояние второго триггера 51 и устанавливает на своих нулевом, первом, втором разрядных выходах адрес 4 (передача операнда на вход арифметического блока без сдвига) либо 5 (передача со сдвигом на 1 разряд.вправо). Результаты последней .итерации корректируются при вьщаче сформированной реализации случайного процесса на выход устройства мультиплексором 6. После завершения узлом 5 вычислений по алгоритму обратного БПФ в счетчике 49 хранится общее число переполнений алгоритма. При этом для различных реализаций случайного процесса число переполнений может быть различно.

Узел адаптации осуществляет автоматическое поддержание уровня выходного сигнала на выходе устройства при формировании широкополосного случай

10

43251412

кого процесса. По окончании записи во второй блок 4 памяти формирующей матрицы E(ku(jJ) на вход задания режима устройства подается нуль (фиг.6), триггер 16 устанавливается в единицу. В такте 1 работы устройства генератор 1 шума и блок 2 умножения рассчить вают вектор коэффициентов Фурье X(kdu)) (2), на основе которого в такте 2 узлом 5 вычисляется первая реализация случайного процесса х(п) (1) из N отсчетов. Триггеры 16-18 и логические элементы И 13-15 (фиг.1) образуют сдвиговую цепочку для вьщеления такта 3, начиная с которого производится выдача сформированных реализаций случайного процесса на выход устройства. Сигналом с выхода элемента И 15 в первьм регистр 10 узла 9 адаптацш заносится код числа -переполнентг первой реализации сформированного случайного процесса. Сигнал, поступающий на вход синхрони- 25 зации второго регистра 11 узла 9 адаптации, заносит в регистр 11 код числа переполнений выдаваемой в данном такте реализации случайного процесса (3-й, 4-й и т.д.). Сравнение числа переполнений текущей реализации.

15

20

30

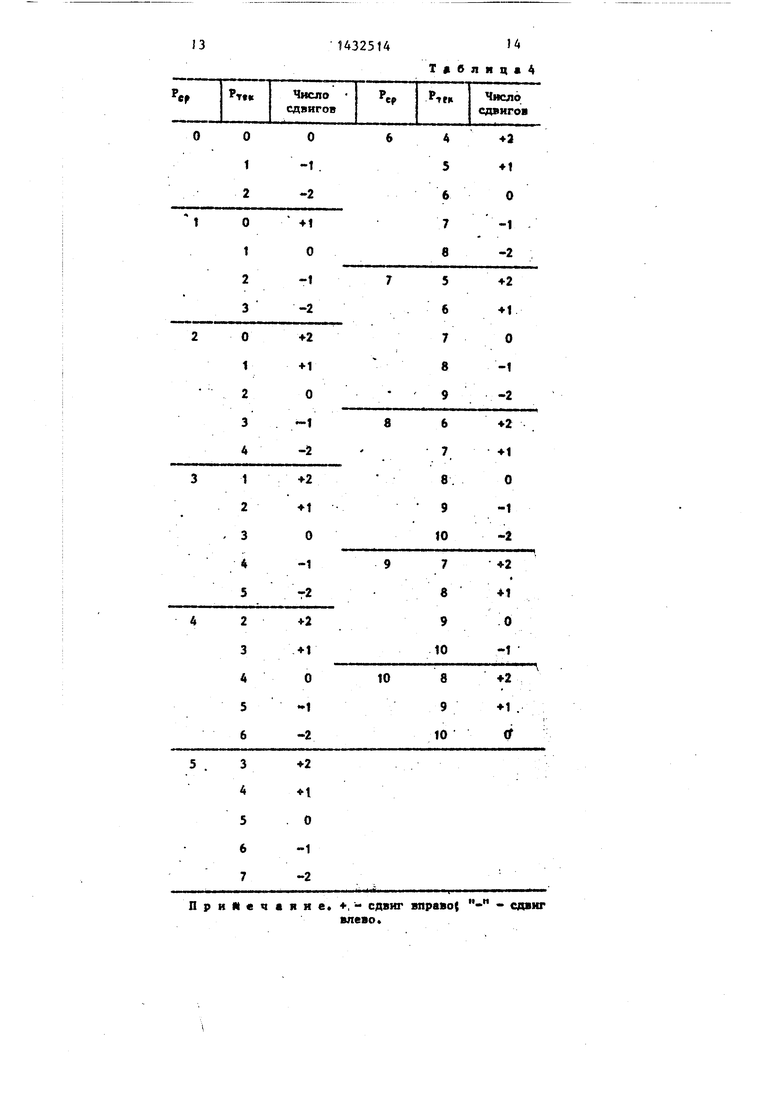

Cj С числом переполнений первой реализации случайного процесса, принятого за Pfg, выполняется блоком 12 памяти (постоянное запоминающее устройство) методом перебора всех воз можных комбинаций ср вь1- ходе блока 12 памяти узла 9 адаптации устанавливается требуемое число сдвигов (табл. 4) вправо или влево мультиплексором 6 всех отсчетов текущей выходной реализации случайного процесса. Для стационарных случайных процессов IP те к ср , даже если Ррр определяется случайно. При N 1024 объем блока 12 памяти состав ляет 256 X 4 бит.

40

J3

1432514

ПриМечаяие. «, - сдвиг - - сдвиг

влеао«

ТсблицжА

5

Блок 8 управления осуществляет синхронизацию вычислений различными блоками устройства для формирования широкополосного случайного процесса, вьфабатывая тактовые синхроимпульсы четьфех серий.

ТИ1 - производят запись с частотой д отсчета реализации процесса, рассчитанной на предьщущем такте работы устройства, в выходной регистр 7, а также запуск генератора 1 шума и блок 2 умножения на вычисление очередного отсчета ВКФ формируемого случайного процесса.

ТИ2 - определяют такт работы устройства. По каждому синхросигналу узел 5 начинает расчет текущей реализации случайного процесса из N отсчетов, а в первый регистр 10 узла 9 адаптации записывается код числа переполнений алгоритма обратного БПФ на предьщущем такте работы устройства.

ТИЗ - осуществляют переключение первого 41 и второго 42 буферов памяти первого блока 3 памяти.

ТИ4 - синхропоследовательность, управляющая работой мультиплексора 58 блока 8 управления. Мультиплексор 58 проводит: адресацию данных, считываемых из первого блока 3 памяти на выход устройства с прямым либо с двоично-инверсным порядком следования отсчетов.

Каждый такт работы устройства (фиг.6) начинается с появления ТИ2 после переполнения т-разрядного счет1

Например, пусть на выход устройства (фиг.6) в такте 3 (ТИЗ О, ТИ4 0) вьщана реализация случайного процесса из второго буфера 42 памяти первого блока 3 памяти. В этом же буфере памяти подготовлен ВКФ формируемого процесса, причем так как данные считывались в прямой последова- |Те,пьности, то данные для вычисления узлом 5 обратного БПФ будут записаны с прямым порядком следования. В такте 4 узел 5, работая с вторым буфером 42 памяти (ТИЗ 1), проведет расчет новой реализации случайного процесса, причем в этом же буфере памяти после вычислений по алгоритму

чика 56 блока 8 управления, подсчитывающего импульсы от ГТИ 54. Синхро- 40 обратного БПФ данные будут представлены в двоично-инверсном порядке следования. В такте 5 (ТИЗ О, ТИ4 1) с вторым буфером 42 памяти работает блок 8 управления, проводя выдачу на 45 выходной регистр 7 реализации случайного процесса с двоично-инверсным попоследовательность ТИ1 формируется элементом 55 задержки, н а вход которого поступают импульсы от ГТИ 54. Задержка определяется временем переключения счетчика 56, мультиплексора 52 и временем выборки отсчета из первого блока 3 памяти.

При вычислении по алгоритму обратного БПФ с замещением прямая входная последовательность данных на выходе окажется представленной в двоично-инверсном порядке в этом же буфере памяти. Тогда при считывании сформированной реализации случайного процесса на выход устройства для получения нормального порядка следования отсчетов блок 8 управления должен подавать двоично-инверсный адрес на этот же

рядком следования и т.д.

Формула изобретения 50

10

15

43251416

буфер памяти и наоборот. Для того, чтобы нормальный порядок следования отсчетов не нарушался и в дальнейшем, узел 5 вычисления текущей реализации случайного процесса должен поочередно осуществлять обратное БПФ над входными данными с прямым и двоично- инверсным порядком следования в одном и том же буфере памяти (фиг.6).

Адресацию памяти по диаграммам фиг.6 в узле 5 вычисления текущей реализации случайного процесса проводит блок 43 адресации, который может проводить адресацию операндов при вычислении по алгоритму БПФ с прямым либо с двоично-инверсным порядком следования отсчетов на входе (1, 2).

Адресацию данных при выдаче очередной реализации случайного процесса на выход устройства осуществляет блок 8 управления с помощью синхро- последовательности ТИ4.

Например, пусть на выход устройства (фиг.6) в такте 3 (ТИЗ О, ТИ4 0) вьщана реализация случайного процесса из второго буфера 42 памяти первого блока 3 памяти. В этом же буфере памяти подготовлен ВКФ формируемого процесса, причем так как данные считывались в прямой последова- |Те,пьности, то данные для вычисления узлом 5 обратного БПФ будут записаны с прямым порядком следования. В такте 4 узел 5, работая с вторым буфером 42 памяти (ТИЗ 1), проведет расчет новой реализации случайного процесса, причем в этом же буфере памяти после вычислений по алгоритму

20

25

30

35

рядком следования и т.д.

Формула изобретения 50

соединен с вторым входом узла вычисления текущей реализации случайного процесса и подключен к входу синхронизации второго регистра узла адапта- 15 ции, вторым входам первого, второго и третьего элементов И, второй выход узла вычисления текул ей реализации случайного процесса соединен с информационным входом первого и второго ней с входом обнуления третьего триг- 2о Регистров узла адаптации, вход эле- гера, вход установки в 1 которого мента НЕ узла адаптации является вхосоединен с входом обнуления второго триггера, вход установки в 1 которого соединен с входом обнуления первого триггера, информа1щонный вход 25 которого соединен с шиной задания логической единицы, выход третьего элемента И соединен с входом синхронизации первого регистра, выход которого соединен с первым адресным входом зо блока памяти, второй адресный вход которого соединен с выходом второго регистра, выход блока памяти узла адаптации соединен с управляющим входом задания режима устройства, третий выход узла вычисления текущей реализации случайного процесса соединен с вторым адресным входом первого бло ка памяти.

2, Устройство ПОП.1, отлича ющееся тем, что генератор ь гума содержит генератор тактовых импульсов, триггер, счетчик, два элемента И, элемент НЕ, элемент ИЛИ, элемент задержки, дешифратор, одновибратор, блок элементов И, регистр сдвига, ре

40

гистр, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

дом мультиплексора, первый выход узла причем вход установки в 1 триггера

j5 вычисления текущей реализации случаи- является входом синхронизации гене-

ного процесса соединен с первым ин- ратора шума, прямой выход триггера формационным входом первого блока па- подключен к первому входу первого мяти, второй информациопньш вход которого соединен с выходом блока умножения, первьй информационньй вход которого соединен с выходом второго блока памяти, адресный вход которого соединен с первым адресным входом первого блока памяти и соединен с первым выходом блока управления, второй выход которого соединен с входом задания режима генератора uiyMa, информационный выход которого соединен с вторым информационным входом блока

45

50

элемента И, второй вход которого соединен с ВЫХОДОМ генератора тактовых импульсов, выход первого элемента И соединен с вычитающим входом счетчик и входом разрешения сдвига регистра сдвига, выход переполнения счетчика соединен с входом установки счетчика и подключен к входу обнуления тригге ра и входу элемента задержки, выход которого является выходом конца операции генератора шума, выход элемента задержки соединен с первым входом второго элемента И, выход которого соединен с входом синхронизации регистра, выход которого соединен с информационным входом регистра сдвига, выход которого соединен с первым входом блока элементов И, второй вход которого соединен с инверсным выходом дешифратора, прямой выход которого соединен с первым входом элемента

умножения, вход синхронизации которого соединен с выходом конца операции генератора шума, вход синхронизации которого соединен с входом синхронизации регистра и подключен к третьему выходу блока управления, четвертый выход которого соединен с входом синхронизации первого блока памяти, первый информационньй выход

которого соединен с первым входом узла вычисления текущей реализации случайного процесса, второй информацион- ньй выход первого блока памяти соединен с информационным входом мультиплексора, выход которого соединен с информационным входом регистра, выход которого является выходом устрой- ства, пятый выход блока управления

дом задания режима устройства, третий выход узла вычисления текущей реализации случайного процесса соединен с вторым адресным входом первого блока памяти.

2, Устройство ПОП.1, отличающееся тем, что генератор ь гума содержит генератор тактовых импульсов, триггер, счетчик, два элемента И, элемент НЕ, элемент ИЛИ, элемент задержки, дешифратор, одновибратор, блок элементов И, регистр сдвига, ре0

ратора шума, прямой выход триггера подключен к первому входу первого

45

0

55

элемента И, второй вход которого соединен с ВЫХОДОМ генератора тактовых импульсов, выход первого элемента И соединен с вычитающим входом счетчика и входом разрешения сдвига регистра сдвига, выход переполнения счетчика соединен с входом установки счетчика и подключен к входу обнуления триггера и входу элемента задержки, выход которого является выходом конца операции генератора шума, выход элемента задержки соединен с первым входом второго элемента И, выход которого соединен с входом синхронизации регистра, выход которого соединен с информационным входом регистра сдвига, выход которого соединен с первым входом блока элементов И, второй вход которого соединен с инверсным выходом дешифратора, прямой выход которого соединен с первым входом элемента

191А3251420

ИЛИ и вторым входом второго элемента И, вьпсод блока элементов И является информационным выходом генератора, старший разрядный вход дешифратора соединен с входом одновибратора и входом элемента НЕ, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с входом управления сдвигом вправо-влево реги- ю вторым входом элемента И, нулевой, стра сдвига, вход записи которого со- первьй и второй разрядные выходы бло- единен с выходом одновибратора, раз- ка микропрограммного управления сое- рядные входы дешифратора являются динены с соответствующими разрядными

с входом синхронизации второго триггера и входом обнуления первого триггера, прямой выход которого соединен с информационным входом второго триг гера, прямой выход которого соединен с входом задания условия блока микропрограммного управления, инверсный выход первого триггера соединен с.

входом задания режима генератора, первьй и второй входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с соответст-: вующими разрядными выходами регистра сдвига, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом последовательного сдвига вправо регистра сдвига, вход последовательного сдвига влево которого соединен с выходом iвторого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

3, Устройство поп,1, отличающееся тем, что, узел вычисления текущей реализации случайного процесса содержит блок адресации, блок памяти, блок микропрограммного управления, мультиплексор, два арифметических блока, счетчик, два триггера, элемент И и элемент ИСКЛЮЧА1аЦЕЕ ИЛИ, причем первый адресный выход блока адресации соединен с адресным входом блока памяти, выход которого

соединен с первым информационным вхо- -g ответетвующими управляющими разряддом мультиплексора, выход которого является первым выходом узла, второй информационный вход мультиплексора соединен с выходом первого арифметического блока, выход второго арифметического блока соединен с третьим информационным входом мультиплексора, разрядные выходы которого соединены с информационными разрядными входами

ными входами блока адресации, тринад цатый разрядный выход блока микропро граммно1 о управления соединен с тре тьим входом элемента И, второй адрес 40 ный выход блока адресации является третьим выходом узла, четвертый и пя тый входы мультиплексора объединены между собой и являются первым входом узла, вход Пуск блока микропрограм

,первого и второго арифметических бло- g много управления является вторым вхоков, первый и второй разрядные входы мультиплексора соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАНШЩЕ ИЛИ, выход которого соединен с первым входом элемента И, .выход которого соединен с входом установки в 1 первого триггера и счетным входом счетчика, выход которого является вторым выходом узла, вход сброса счетчика соединен с входом Пуск блока микропрограммного управления и входом предварительной установки блока адресации, выход окончания операции которого соединен

50

55

дом узла. .

с входом синхронизации второго триггера и входом обнуления первого триггера, прямой выход которого соединен с информационным входом второго триг гера, прямой выход которого соединен с входом задания условия блока микропрограммного управления, инверсный выход первого триггера соединен с.

управляющими входами мультиплексора,

третий, четвертый разрядные выходы блока микропрограммного управления соединены с соответствующими входами выбора режима арифметических блоков, пятый и шестой разрядные выходы блока

микропрограммного управления соединены с соответствующими входами выбора режима второго арифметического блока, седьмой и восьмой разрядные выходы блока микропрограммного управения подключены к соответствунщим входам выбора режима первого и второ го арифметических блоков, девятый и есятый разрядные выходы блока микропрограммного управления соединены с

соответствующими входами выбора режима первого и второго арифметических блоков, одиннадцатый, двенадцатый и тринадцатый выходы блока микропрограммного управления соединены с соными входами блока адресации, тринадцатый разрядный выход блока микропро- граммно1 о управления соединен с тре тьим входом элемента И, второй адрес- 40 ный выход блока адресации является третьим выходом узла, четвертый и пятый входы мультиплексора объединены между собой и являются первым входом узла, вход Пуск блока микропрограм0

5

дом узла. .

pa, выход которого является первым выходом блока управления, разрядные выходы первого счетчика являются вторым разрядным выходом блока, выход генератора тактовых импульсов соединен с входом элемента задержки, выход которого является третьим выходом блока, выход первполнения первого

1422

счетчика соединен со счетным входом второго счетчика, выход младшего разряда которого является четвертым выходом блока управления, выход старгае- го разряда второго счетчика соединен с управляющим входом мультиплексора, выход переполнения первого счетчика является пятым выходом блока.

Чнср. 8я. 1

fimp. л. 2

К

L I

fff4J.gta.J Фи9.3

Ннд.8их.1

0U9.S

CdSut tnpaBo

Запоминание содержимого регистра cdSuaa 31 9 регистра 32

| Устройство для адресации процессора быстрого преобразования фурье | 1982 |

|

SU1040491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ФУНКЦИЙ | 0 |

|

SU386390A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-09-26—Подача