Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах специализированных процессоров для цифровой обработки сигналов.

Целью изобретения является расширение функциональных возможностей устройства для цифровой обработки сигналов за счет выполнения фильтрации и Z-преобразования.

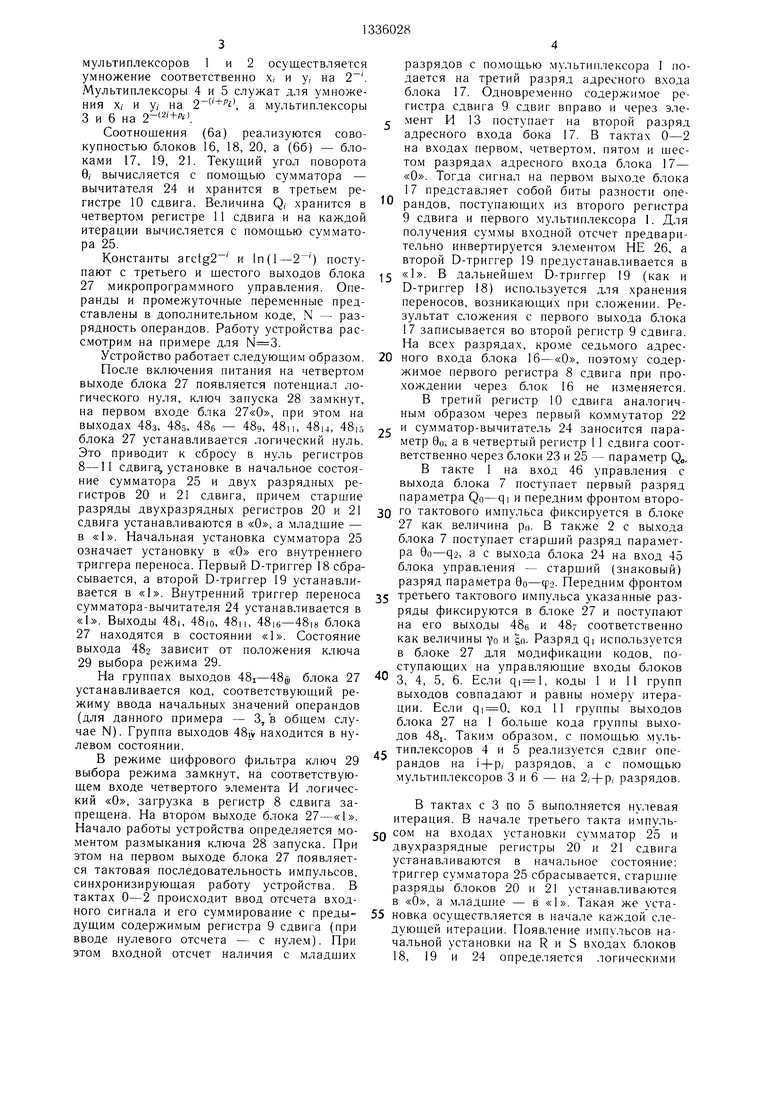

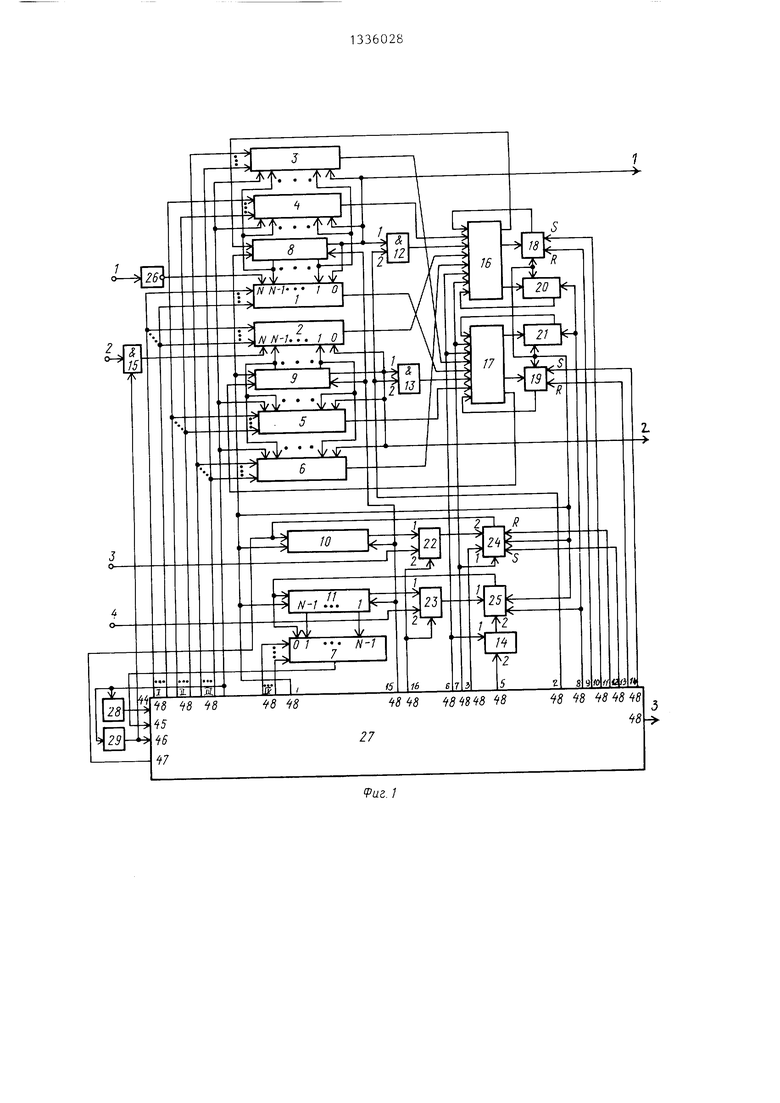

На фиг. 1 изображена структурная схема устройства для цифровой обработки сигналов; на фиг. 2 - функциональная схе- .ма блока микропрограммного управления.

Устройство для цифровой обработки сигналов содержит (фиг. 1) семь мультиплексоров 1-7, четыре регистра 8-11, сдвига, четыре элемента И 12-15, два блока 16 и 17 постоянной памяти, два D-триггера 18 и 19, два двухразрядных регистра 20 и 21 сдвига, два коммутатора 22, 23, сумматор-вычита- тель 24, сумматор, элемент НЕ 26, блок 27 микропрограммного управления, ключи запуска 28 и выбора режима 29.

Блок микропрограммного управления (фиг. 2) содержит генератор 30 тактовых импульсов, два D-триггера 31 и 32, счетчик 33, элементы И 34-37, элемент ИЛИ 38, узел 39 постоянной памяти, регистры 40-42, дешифратор 43, вход 44 запуска, первый 45, второй 46 и третий 47 входы логических условий, выходы 48:-48|7 и группы выходов 48|-48ivУстройство может использоваться в двух режимах: как цифровой рекурсивный фильтр и как вычислитель для БПФ и Z-преобразования. В режиме цифрового фильтра устройство реализует звено второго порядка и работает в соответствии со следующими соотношениями

у2(п) Гу2(п-1 )С05ф+Гу1 (П-1)51Пф;(1а)

у, (п) гу|(п -l)cos(p-гу2(п-1)51пф;(1б) yi(n)yi(n)+x(n),(1в)

где х(п), yi(n) - отсчеты входного и выходного сигналов фильтра; У (п), у2(п) - вспомогательные переменные.

Параметры г и ф определяют передаточную функцию фильтра.

(2). режиме БПФ или Z-преобразования устройство выполняет умножение на «поворачивающий множитель

B| (2)

гдеW exp(-j- VN);

г - вещественное число, причем для преобразования Фурье для - преобразования внутри единичной окружности; B x-|-jy - комплексное число; п, k - целые. В основе выражений (1) и (2) лежат операция гюворота вектора в комплексной плоскости на угол ф (на угол в выражении (2) и умножения на вещественное

(4)

число г. Данные операции реализуются в заявленном устройстве на основе итерационных алгоритмов «цифра за цифрой.

Поворот вектора осуществляется в из- вестном устройстве в соответствии с алгоритмом

х;+| х,-+Е,,-;

у,+ ,(;

9, +, e,4arctg2- ;

; signe;; ,l,...,N-1, 0 где N - разрядность операндов.

После выполнения N итераций координаты х„, у„ отличаются от исковых в К,/ раз,

где Коррекция результата в известном устройстве требует дополнитель- 5 ных временных затрат. Пусть . Представим Г| в следующем виде о

г, п( 1+7,2),.

Uo

где 1 или 1.

Алгоритм представления Г| в виде (4) 0 соответствует операции вычисления экспоненциальной функции по алгоритму «цифра за цифрой

,-f Y,x,

,-ln(l-7/2- );(5)

5 Y/ signQ/

при начальных условиях , , ,0,l,l,...,N-1.

Недостатком алгоритма (5) является необходимость «двойных шагов и двойной набор констант. Воспользуемся тем, что 0 и . Для этого случая предлагается модифицированный алгоридм. В двоичном представлении числа -Q, на каждой i-й итеризации анализируют два разряда: qv-i-i и , и модифицируют уравнения (5) следующим образом: 5 х,-+, х,-Y/x,2- + i ;

Q,+ , ln(l-Y/2- + )+Q,-;

7-ejit logs ( + Q() q.N-i-/;

P,q.,-;

, Qo -Inr,, ,l,2,...,N-1.

Тогда после N итераций , У . Совмещая операции (3) и (5), получают алгоритм вращения вектора по любой наперед, заданной траектории: х,+, х,-+,2- y,-V 2 6,T/2- + v (ба) у,.+, у,-,2-- х,-v/2- + y, + |,т/2 2 + .х,; 5 е/+| е,-E,arctg2- ;Сбб)

g,signe, ;(6fe)

Q,+ , ln(,-2- + ))+Qt;(g)

V, (-f Q;)qN-i,. P,q«2-,, ,l,2,...,N-l;

Для режима цифровой фильтрации на- 0 чальные условия в (6)

(п-1); (n-1);

(r/kd); .

Для умножения на

,

(r/X,); .

Первый 8 и второй 9 регистры сдвига предназначены для хранения текущих значений X; и у, соответственно. С помощью

мультиплексоров 1 и 2 осуществляется умножение соответственно х; и у, на . Мультинлексоры 4 и 5 служат для умножения X; и у/ на , а мультиплексоры 3 и 6 на

Соотношения (6а) реализуются совокупностью блоков 16, 18, 20, а (66) - блоками 17, 19, 21. Текущий угол поворота 0/ вычисляется с помощью сумматора - вычитателя 24 и хранится в третьем регистре 10 сдвига. Величина Q, хранится в четвертом регистре 11 сдвига и на каждой итерации вычисляется с номощью сумматора 25.

Константы arctg2 и 1п() поступают с третьего и щестого выходов блока 27 микропрограммного управления. Операнды и промежуточные переменные представлены в дополнительном коде, N - разрядность операндов. Работу устройства рассмотрим на примере для .

разрядов с помощью мультиплексора I подается на третий разряд адресного входа блока 17. Одновременно содержимое регистра сдвига 9 сдвиг вправо и через эле- с мент И 13 поступает на второй разряд адресного входа бока 17. В тактах О-2 на входах первом, четвертом, пятом и шестом разрядах адресного входа блока 17- «О. Тогда сигнал на первом выходе блока 17 представляет собой биты разности операндов, поступающих из второго регистра 9 сдвига и первого мультиплексора 1. Для получения суммы входной отсчет предварительно инвертируется элементом НЕ 26, а второй D-триггер 19 предустанавливается в «1. В дальнейщем D-триггер 19 (как и D-триггер 18) используется для хранения переносов, возникающих при сложении. Результат сложения с первого выхода блока 17 записывается во второй регистр 9 сдвига. На всех разрядах, кроме седьмого адресУстройство работает следующим образом. 20 ного входа блока 16-«О, поэтому содер- После включения питания на четвертомжимое первого регистра 8 сдвига при провыходе блока 27 появляется потенциал логического нуля, ключ запуска 28 замкнут, на первом входе блка 27«0, при этом на выходах 48з, 48,5, 48б - 489, 48|ь 48i4, 48|.5 блока 27 устанавливается логический нуль. Это приводит к сбросу в нуль регистров 8-11 сдвига, установке в начальное состояние сумматора 25 и двух разрядных регистров 20 и 21 сдвига, причем старшие

хождении через блок 16 не изменяется. В третий регистр 10 сдвига аналогичным образом через первый коммутатор 22 2с и сумматор-вычитатель 24 заносится параметр 9о, а в четвертый регистр 11 сдвига соответственно через блоки 23 и 25 - параметр Q,. В такте I на вход 46 управления с выхода блока 7 поступает первый разряд параметра Qo-qi и передним фронтом второразряды двухразрядных регистров 20 и 21 30 о тактового импульса фиксируется в блоке

27 как величина ро. В также 2 с выхода блока 7 поступает старщий разряд параметра 9о-q2, а с выхода блока 24 на вход 45 блока управления - старщий (знаковый) разряд параметра Эо-ф2. Передним фронтом

вается в «1. Внутренний триггер переноса 35 третьего тактового импульса указанные раз- сумматора-вычитателя 24 устанавливается вряды фиксируются в блоке 27 и поступают

на его выходы 48б и 48- соответственно как величины уо и с,о. Разряд qi используется в блоке 27 для модификации кодов, поступающих на управляющие входы блоков

сдвига устанавливаются в «О, а младшие - в «1. Начальная установка сумматора 25 означает установку в «О его внутреннего триггера переноса. Первый D-триггер 18 сбрасывается, а второй D-триггер 19 устанавли«I. Выходы 48|, 48|о, 48||, 48i6-48i8 блока 27 находятся в состоянии «1. Состояние выхода 482 зависит от положения ключа 29 выбора режима 29.

На группах выходов 48i-48ji блока 27 40 з, 4, 5, 6. Если , коды 1 и 11 групп устанавливается код, соответствующий ре-выходов совпадают и равны номеру итеражиму ввода начальных значений операндовции. Если , код 11 группы выходов

(для данного примера -- 3, в общем слу-блока 27 на 1 больще кода группы выходов 48i. Таким образом, с помощью муль- дг типлексоров 4 и 5 реализуется сдвиг операндов на i + p, разрядов, а с помощью

чае N). Группа выходов 48rv находится в нулевом состоянии.

В режиме цифрового фильтра ключ 29 выбора режима замкнут, на соответствующем входе четвертого элемента И логический «О, загрузка в регистр 8 сдвига запрещена. На втором выходе блока 27-«1.

мультиплексоров 3 и 6 - на 2, + р, разрядов.

В тактах с 3 по 5 выполняется нулевая итерация. В начале третьего такта импульНачало работы устройства определяется мо- Q сом на входах установки сумматор 25 и ментом размыкания ключа 28 запуска. Придвухразрядные р егистры 20 и 21 сдвига

этом на первом выходе блока 27 появляет-устанавливаются в начальное состояние:

ся тактовая последовательность импульсов,триггер сумматора 25 сбрасывается, старшие

синхронизирующая работу устройства. Вразряды блоков 20 и 21 устанавливаются

тактах 0-2 происходит ввод отсчета вход-в «О, а младщие - в «1. Такая же устаного сигнала и его суммирование с преды- 55 новка осуществляется в начале каждой следующей итерации. Появление импульсов начальной установки на R и S входах блоков 18, 19 и 24 определяется логическими

дущим содержимым регистра 9 сдвига (при вводе нулевого отсчета - с нуле.м). При этом входной отсчет наличия с младщих

разрядов с помощью мультиплексора I подается на третий разряд адресного входа блока 17. Одновременно содержимое регистра сдвига 9 сдвиг вправо и через эле- мент И 13 поступает на второй разряд адресного входа бока 17. В тактах О-2 на входах первом, четвертом, пятом и шестом разрядах адресного входа блока 17- «О. Тогда сигнал на первом выходе блока 17 представляет собой биты разности операндов, поступающих из второго регистра 9 сдвига и первого мультиплексора 1. Для получения суммы входной отсчет предварительно инвертируется элементом НЕ 26, а второй D-триггер 19 предустанавливается в «1. В дальнейщем D-триггер 19 (как и D-триггер 18) используется для хранения переносов, возникающих при сложении. Результат сложения с первого выхода блока 17 записывается во второй регистр 9 сдвига. На всех разрядах, кроме седьмого адресного входа блока 16-«О, поэтому содер- жимое первого регистра 8 сдвига при прохождении через блок 16 не изменяется. В третий регистр 10 сдвига аналогичным образом через первый коммутатор 22 и сумматор-вычитатель 24 заносится параметр 9о, а в четвертый регистр 11 сдвига соответственно через блоки 23 и 25 - параметр Q,. В такте I на вход 46 управления с выхода блока 7 поступает первый разряд параметра Qo-qi и передним фронтом втородов 48i. Таким образом, с помощью муль- типлексоров 4 и 5 реализуется сдвиг операндов на i + p, разрядов, а с помощью

мультиплексоров 3 и 6 - на 2, + р, разрядов.

функциями fg, fio,...,fH В нзчале каждой итерации. На управляюш,их входах блоков 22 и 23 «О, информация с выходов регистров 10 и 11 сдвига поступает на вторые входы сумматора-вычитателя 24 и сумматора 25 соответственно. Одновременно с выхода 48 блока 27, начиная с младших разрядов на первый вход сумматора-вычитателя 24 поступает константа Со. Тип операции в блоке 24 определяется уровнем сигнала на его управляющем входе. При «1 осуществляется сложение, при «О - вычитание. Результат по битам возвращается в регистр 10 сдвига. Фронтом 6-го тактового импульса старший (знаковый) разряд фиксируется в блоке 27 и поступает на его выход 47 как величина |i. Код «00 на I группе выходов в течение итерации обеспечивает поступление на выходы блоков I и 2 операндов, хранящихся в регистрах 8 и 9 сдвига соответственно, начиная с нулевого разряда. Код И и III групп выходов равен 00 или 01 в течение третьего и четвертого тактов, что определяется значением разряда qi. На пятом такте на группах выходов 48 и 48 код 00, что связано с необходимостью осуществлять арифметический сдвиг операндов. По- следвательность смены состояний на группах выходов 48fi и 48в| блока 27 обеспечивает поступление на выходы мультиплексоров 3-6 операндов начиная либо с нулевого (при ), либо с первого (при qi 0) разрядов. В последнем случае на выходы блоков 3-6 в 4 и 5 тактах поступает знаковый разряд. С входов соответствующих мультиплексоров информация поступает на адресные входы блока 16 и блока 17, где реализуются соотношения (6а) и (66).. Младшие разряды результатов с первых входов блоков 16 и 17 на каждом такте возвращаются соответственно в регистры 8 и 9 сдвига, а переносы, формируемые на втором и третьем выходах блоков 16 и 17, записываются соответственно в D-триггеры 18 и 19 и двухразрядные регистры 20 и 21 сдвига. Таким образом переносы, сформированные на вторых выходах ПЗУ, в третьем такте поступают на входы О блоков 16 и 17 на четвертом такте, а переносы с третьих выходов попадают на седьмые разряды адресных входов блков 16 и 17 на пятом такте. Код 01 группы выходов 48л блока 27 в тактах 3-5 обеспечивает подключение второго выхода четвертого регистра 11 сдвига через мультиплексор 7 к входу 47 блока 27. С выхода 485 блока 27 в тактах 3-5 поступают, начиная с младшего, разряды константы Со(() при ). При 1 на первом входе третьего элемента И 14 константа Со поступает на сумматор 25 и складывается с содержимым регистра

10

15

20

25

30

35

40

45

50

27 и используется как Р: на следующей итерации. Передним фронтом шестого тактового импульса разряд qo фиксируется в блоке 27 и поступает на его шестой выход как величина ji.

В течение нулевой итерации информация из второго регистра 9 сдвига поступает на второй выход устройства и тактируется импульсами на третьем выходе устройства. Работа устройства на первой и второй итерациях происходит аналогично. После завершения второй итерации устройство переходит к вводу очередного отсчета, и процесс повторяется. Остановка устройства производится замыканием ключа 28, при этом все блоки устанавливаются в начальное состояние. Описанный алгоритм работы легко распространить на произвольную разрядность N. При этом для вычисления одного отсчета потребуется N+1 итераций по N тактов.

При использовании устройства для вычисления БПФ или Z-преобразования ключ 29 разомкнут. Устройство начинает работать при размыкании ключа 28 запуска. При разомкнутом ключе 29 на соответствующем входе четвертого элемента И 15 логическая «1 и загрузка в первый регистр 8 сдвига разрешена. На вторых входах первого и второго элементов И 12 и 13 логический «О, что соответствует вводу операндов. Ввод осуществляется в тактах О-2. При этом на выходах первого и второго элементов И 12 и 13 и мультиплексоров 3-6 логический «О. В тактах О-2 результат предыдущих вычислений хранится в первом и втором регистрах 8 сдвига и 9, поступает на выходы устройства и сопровождается тактовыми импульсами на его третьем входе. Одновременно с первого и второго входов устройства через первый и второй мультиплексоры, блоки 17 и 16 операнды заносятся соответственно во второй 9 и первый 8 регистры сдвига, а с третьего и четвертого входов через блоки 22 и 24, 23 и 25, в третий 10 и четвертый 11 регистры сдвига записываются коэффициенты 9о и QQ.

В начале третьего такта на выходе 2 блока 27 управления появляется «1 и далее нулевая, первая и вторая итерации вый- полняются описанным образом. Для произвольной разрядности умножение на «поворачивающий множитель требует (N-|-1)N тактов.

Формула изобретения

1. Устройство для цифровой обработки сигналов, содержащее два мультиплексора, три регистра сдвига, три элемента И,

11 сдвига. Результат операции возвращает- eg сумматор-вычитатель, ключ запуска и блок

ся в блок 11. Фронтом пятого тактового импульса разряд результата qoo, поступающий с выхода блока 7, фиксируется в блоке

микропрограммного управления, причем разрядные выводы первого регистра сдвига соединены с информационными входами

5

0

5

0

5

0

5

0

27 и используется как Р: на следующей итерации. Передним фронтом шестого тактового импульса разряд qo фиксируется в блоке 27 и поступает на его шестой выход как величина ji.

В течение нулевой итерации информация из второго регистра 9 сдвига поступает на второй выход устройства и тактируется импульсами на третьем выходе устройства. Работа устройства на первой и второй итерациях происходит аналогично. После завершения второй итерации устройство переходит к вводу очередного отсчета, и процесс повторяется. Остановка устройства производится замыканием ключа 28, при этом все блоки устанавливаются в начальное состояние. Описанный алгоритм работы легко распространить на произвольную разрядность N. При этом для вычисления одного отсчета потребуется N+1 итераций по N тактов.

При использовании устройства для вычисления БПФ или Z-преобразования ключ 29 разомкнут. Устройство начинает работать при размыкании ключа 28 запуска. При разомкнутом ключе 29 на соответствующем входе четвертого элемента И 15 логическая «1 и загрузка в первый регистр 8 сдвига разрешена. На вторых входах первого и второго элементов И 12 и 13 логический «О, что соответствует вводу операндов. Ввод осуществляется в тактах О-2. При этом на выходах первого и второго элементов И 12 и 13 и мультиплексоров 3-6 логический «О. В тактах О-2 результат предыдущих вычислений хранится в первом и втором регистрах 8 сдвига и 9, поступает на выходы устройства и сопровождается тактовыми импульсами на его третьем входе. Одновременно с первого и второго входов устройства через первый и второй мультиплексоры, блоки 17 и 16 операнды заносятся соответственно во второй 9 и первый 8 регистры сдвига, а с третьего и четвертого входов через блоки 22 и 24, 23 и 25, в третий 10 и четвертый 11 регистры сдвига записываются коэффициенты 9о и QQ.

В начале третьего такта на выходе 2 блока 27 управления появляется «1 и далее нулевая, первая и вторая итерации вый- полняются описанным образом. Для произвольной разрядности умножение на «поворачивающий множитель требует (N-|-1)N тактов.

Формула изобретения

1. Устройство для цифровой обработки сигналов, содержащее два мультиплексора, три регистра сдвига, три элемента И,

g сумматор-вычитатель, ключ запуска и блок

микропрограммного управления, причем разрядные выводы первого регистра сдвига соединены с информационными входами

первого мультиплексора, разрядные выходы второго регистра сдвига соединены с информационными входами второго мультиплексора, выходы последовательной выдачи первого и второго регистров сдвига подключены к первым входам соответственно первого и второго элементов И и являются соответственно первым и вторым информационными выходами устройства, выход суммато- ра-вычитателя подключен к информационному входу третьего регистра сдвига, первый выход блока микропрограммного управления подключен к входам синхронизации первого, второго и третьего регистров сдвига и сумматора-вычитателя, второй выход блока микропрограммного управления подключен к вторым входам первого и второго элементов И, третий выход блока микропрограммного управления подключен к входу синхронизации сумматора-вычитателя, четвертый выход блока микропрограммного управления подключен к управляющему входу запуска, выходы первой группы блока микропрограммного управления подключены к управляющим входам первого и второго мультиплексоров, а выход ключа запуска подключен к входу запуска блока микропрограммного управления, отличающееся тем, что с целью расширения функциональных возможностей за счет выполнения фильтрации и Z-преобразования, в него введены третий, четвертый, пятый, шестой и седьмой мультиплексоры, два блока постоянной памяти, два D-триггера, два двухразрядных регистра сдвига, два коммутатора, четвертый регистр сдвига, сумматор, элемент НЕ, четвертый элемент И и ключ выбора режима, причем разряднь1е выходы первого регистра сдвига подключены к информационным входам третьего и четвертого мультиплексоров, а разрядные выходы второго регистра сдвига подключены к информационным входам пятого и шестого мультиплексоров, выходы второго и первого мультиплексоров подключены к первым разрядам адресных входов соответственно первого и второго блоков постоянной памяти, первые выходы которых подключены к информационным входам соответственно первого и второго регистров сдвига, выходы первого и второго элементов И подключены к вторым разрядам адресных входов соответственно первого и второго блоков постоянной памяти, вторые выходы которых подключены к входам соответственно первого и второго D-триг- геров, выходы которых подключены к третьим разрядам входов соответственно первого и второго блоков постоянной памяти, третьи выходы которых подключены к информационным входам соответственно первого и второго двухразрядных регистров сдвига, выходы которых подключены к четвёртым разрядам адресных входов соответственно первого и второго блоков постоянной памяти, пятые разряды адресных входов ко10

15

0

5

0

5

0

5

0

5

торых подключены к выходам соответственно третьего и шестого мультиплексоров, шестые разряды адресных входов первого и второго блоков постоянной памяти подключены к выходам соотетственно четвертого и пятого мультиплексоров, выход третьего регистра сдвига подключен к первому информационному входу первого коммутатора, выход которого подключен к первому информационному входу сумматора-вычитателя. выход которого подключен, к первому входу логических условий блока микропрограммного управления, разрядные выходы четвертого регистра сдвига подключены к информационным входам седьмого мультиплексора, выход последовательной выдачи четвертого регистра сдвига подключен к первому информационному входу второго коммутатора, выход которого подключен к первому информационному входу сумматора, выход которого подключен к информационному входу четвертого регистра сдвига и дополнительному информационному входу седьмого мультиплексора, выход которого подключен к второму входу логических условий блока микропрограммного управления, выход третьего элемента И подключен к второму информационному входу сумматора, выход элемента НЕ подключен к информационному входу первого мультиплексора, выход четвертого элемента И подключен к информационному входу второго мультиплексора, первый выход блока микропрограммного управления подключен к входам синхронизации четвертого регистра сдвига, первого и второго Ь-триггеров, первого и второго двухразрядных регистров сдвига и сумматора, четвертый выход блока микропрограммного управления подключен к управляюшим входам мультиплексоров с третьего по шестой и управляюшим входом ключа выбора режимов, выход которого подключен к третьему входу логического условий блока микропрограммного управления, первому входу четвертого элемента И, пятый выход блока микропрограммного управления подключен к первому входу третьего элемента И, шестой выход блока микропрограммного управления подключен к второму входу третьего элемента И и седьмым разрядам адресных входов первого и второго блоков постоянной памяти, седьмой выход блока микропрограммного управления подключен к управляюше- му входу сумматора-вычитателя и восьмым- разрядам адресных входов первого и второго блоков постоянной памяти, восьмой выход блока микропрограммного управления подключен к установочным входам сумматора, первого и второго двухразрядных регистров сдвига, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый выводы блока микропрограммного управления подключены соответственно к R- входу первого D-триггера, S-входу первого D-триггера, S-входу первого D-триггера, входу обнуления сумматора-вычитателя, установочному входу сумматора-вычитателя, R-входу второго D-триггера и S-входу второго D-триггера, пятнадцатый выход блока микропрограммного управления подключен к входам сброса регистров сдвига с первого по четвертый, шестнадцатый выход блока микропрограммного управления подключен к управляющим входам первого и второго коммутаторов, семнадцатый выход блока микропрограммного управления является выходом окончания вычислений устройства, первым информационным входом которого является вход элемента НЕ, вторым, третьим и четвертым информаду четвертого элемента И, инверсный выход первого D-триггера подключен к третьему входу дешифратора и второму входу элемента ИЛИ, выход которого подключен к

5 установочному входу счетчика и R-входу второго D-триггера, выход и вход синхронизации которого подключены соответственно к второму адресному входу блока постоянной памяти и выходу третьего элемента И, выход второго элемента И подключен

10 к тактовому входу третьего регистра, R-вход и D-вход первого D-триггера соединены и являются входом запуска блока, первым входом логических условий которого является первый разряд информационного входа

ционными входами устройства являются соот- третьего регистра, нулевой разряд информа- ветственно второй вход четвертого элемен-ционного входа которого соединен с D-BXOдом второго D-триггера и является втота И, вторые информационные входы первого и второго коммутаторов, выходы второй группы блока микропрограммного управления подключены к управляющим входам четвертого и пятого мультиплексоров, выходы третьей группы блока микропрограммного управления подключены к управляющим входам третьего и шестого мультиплексоров, а выходы четвертой группы блока микропрограммного управления подключены к управляющим входам седьмого мультиплексора.

2. Устройство по п. 1, отличающееся тем, что блок микропрограммного управления содержит три регистра, узел постоянной памяти, дещифратор, два D-триггера, счетчик, четыре элемента И, элемент ИЛИ и генератор тактовых импульсов, выход которого подключен к входу синхронизации первого D-триггера, тактовым входам первого и второго регистров, первому входу перво25

рым входом логических условий блока, третьим входом логических условий которого является третий адресный вход узла по- 20 стоянной памяти, выход первого элемента И, выходы седьмого и шестого разрядов второго регистров являются соответственно первым, вторым и третьим выходами блока, четвертый выход которого соединен с входом задания логического нуля устройства, выход пятого разряда второго регистра является пятым выходом блока, шестой и седьмой выходы которого соединены соответственно с четвертым и пятым входами дещиф- ратора и подключены к выходам соответственно первого и второго разрядов третьего регистра, выходы с первого по седьмой дешифратора являются выходами соответственно с восьмого по четырнадцатый блок, пятнадцатый выход которого соединен с вторым входом первого элемента

30

элемента И, первому входу второго 35 подключен к прямому выходу первого

го

элемента И, выход которого подключен к первым входам третьего и четвертого элементов И, первому входу дешифратора и счетному входу счетчика, информационный выход которого подключен к первому адресному входу узла постоянной памяти, первый и второй выходы которого подключены к информационным входам соответственно первого и второго регистров, выходы нулевого, первого, второго, третьего, четвертого и девятого разрядов второго регистра подключены соответственно к установочному входу третьего регистра, первому входу элемента ИЛИ, второму входу третьего элемента И, второму входу второго элемента И, второму входу дешифратора и второму вхо40

45

D-триггера, выход восьмого разряда второго регистра является шестнадцатым выходами блока, семнадцатым и восемнадцатым выходами которого являются соответственно третий вход логических условий блока и выход четвертого элемента И, выходы семнадцатого и шестнадцатого разрядов первого регистра являются выходами первой группы блока, выходами второй группы которого являются выходы четырнадцатого и пятнадцатого разрядов первого регистра, выходы двенадцатого и тринадцатого разрядов которого являются выходами третьей группы блока, выходами четвертой группы которого являются выходы десятого и одиннадцатого разрядов первого регистра.

ду четвертого элемента И, инверсный выход первого D-триггера подключен к третьему входу дешифратора и второму входу элемента ИЛИ, выход которого подключен к

установочному входу счетчика и R-входу второго D-триггера, выход и вход синхронизации которого подключены соответственно к второму адресному входу блока постоянной памяти и выходу третьего элемента И, выход второго элемента И подключен

к тактовому входу третьего регистра, R-вход и D-вход первого D-триггера соединены и являются входом запуска блока, первым входом логических условий которого является первый разряд информационного входа

5

рым входом логических условий блока, третьим входом логических условий которого является третий адресный вход узла по- 0 стоянной памяти, выход первого элемента И, выходы седьмого и шестого разрядов второго регистров являются соответственно первым, вторым и третьим выходами блока, четвертый выход которого соединен с входом задания логического нуля устройства, выход пятого разряда второго регистра является пятым выходом блока, шестой и седьмой выходы которого соединены соответственно с четвертым и пятым входами дещиф- ратора и подключены к выходам соответственно первого и второго разрядов третьего регистра, выходы с первого по седьмой дешифратора являются выходами соответственно с восьмого по четырнадцатый блок, пятнадцатый выход которого соединен с вторым входом первого элемента

0

подключен к прямому выходу первого

D-триггера, выход восьмого разряда второго регистра является шестнадцатым выходами блока, семнадцатым и восемнадцатым выходами которого являются соответственно третий вход логических условий блока и выход четвертого элемента И, выходы семнадцатого и шестнадцатого разрядов первого регистра являются выходами первой группы блока, выходами второй группы которого являются выходы четырнадцатого и пятнадцатого разрядов первого регистра, выходы двенадцатого и тринадцатого разрядов которого являются выходами третьей группы блока, выходами четвертой группы которого являются выходы десятого и одиннадцатого разрядов первого регистра.

4-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

Изобретение относится к вычислительной технике и может быть нсно.тьзовано в ариф.метических устройствах сиециа. ш- зированных процессоров для цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет вьнтолнеиия фильтрации и Z-нреобразо- вания. йоставленная цель достигается за счет того, что в состав устройства входят мультиилексоры, регистры сдвига, э, 1емент1 1 и, блоки иостоянной памяти, D-триггеры, двухразрядные регистры сдвига, коммутаторы, сумматор-вычитатель, сумматор, элемент НЕ, блок микропрограммного управления, ключ запуска и ключ выбора режима. 1 з.п. ф-лы, 2 ил. S ел со со О5 О to 00

| Устройство для выполнения быстрого преобразования фурье | 1978 |

|

SU752348A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Despain А | |||

| М | |||

| Fourier Transform Computer using CORDIC Iterations | |||

| - IEEE Trans, on Computers, p | |||

| Счетный полукруг для расчета радиосетей | 1921 |

|

SU993A1 |

| , 10, | |||

Авторы

Даты

1987-09-07—Публикация

1985-11-01—Подача