Изобретение относится к радиолокации и может быть использовано в системах поиска и измерения параметров сигналов, скрытых помехами, например в связи, радионавигации, в том числе в приемнике навигационной системы "Омега".

Целью изобретения является повышение точности определения фазы принимаемых сигналов.

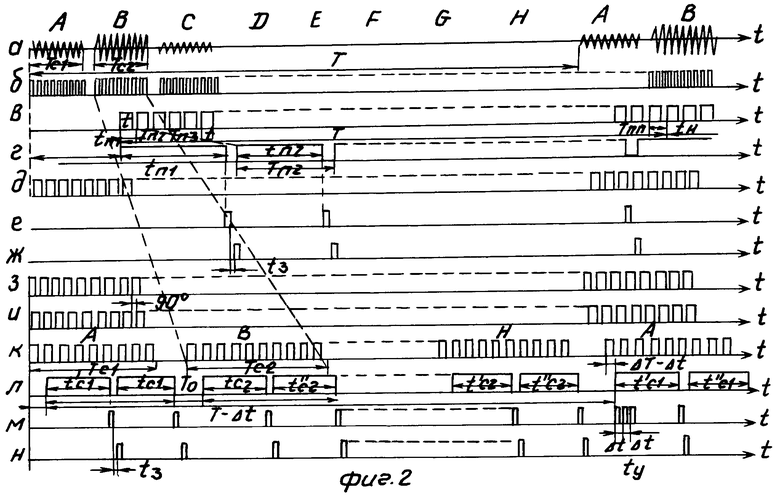

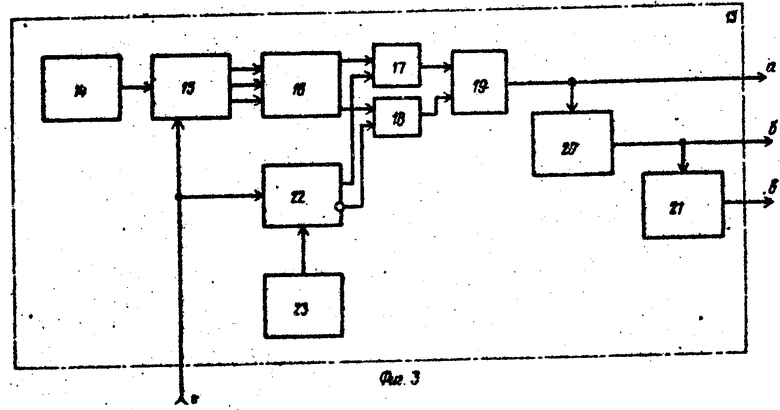

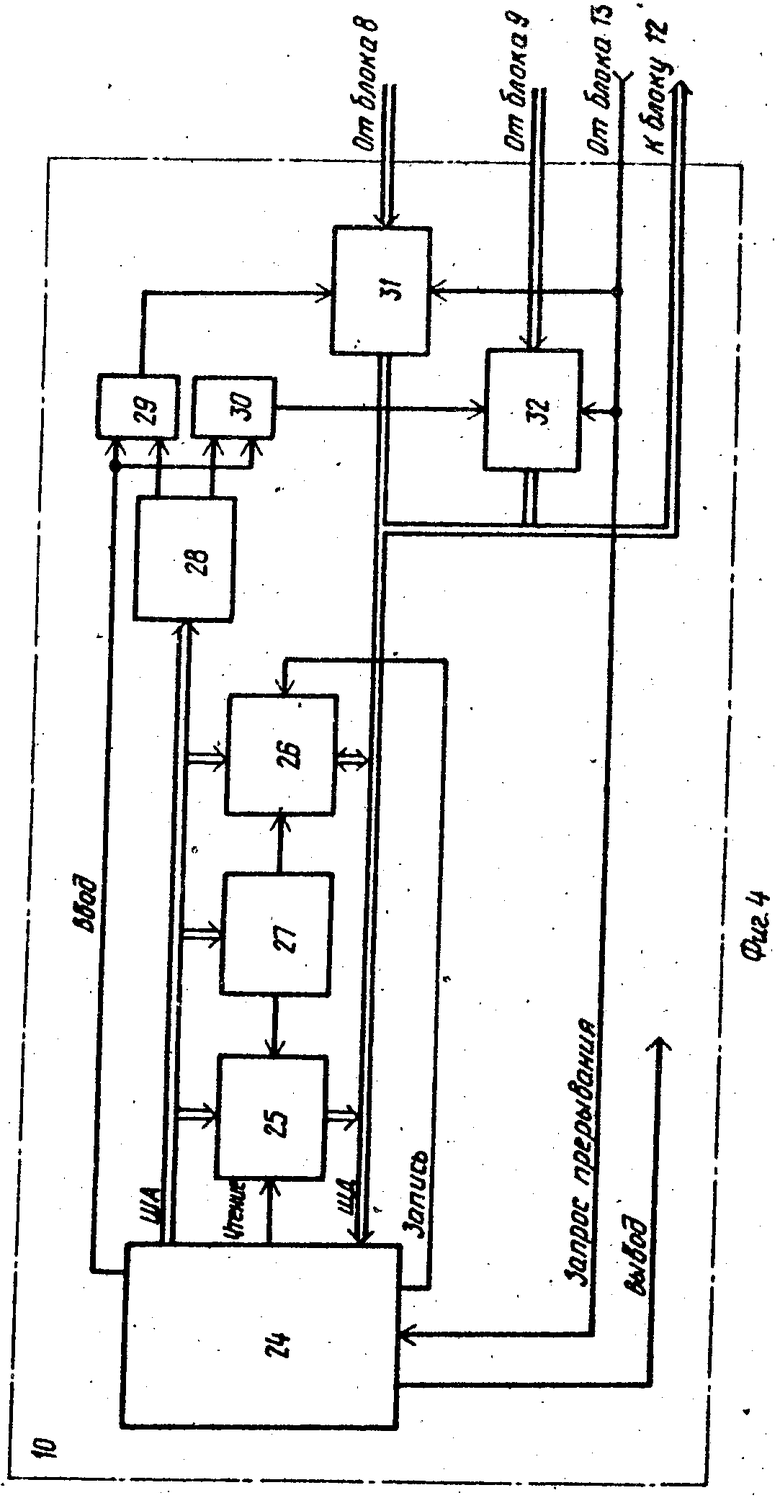

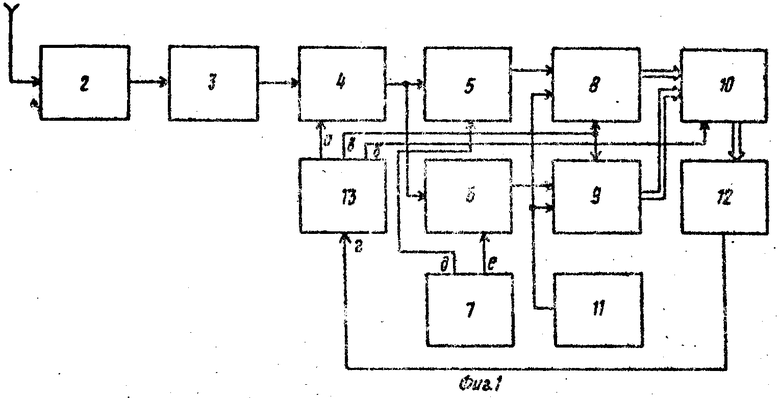

На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 временные диаграммы, поясняющие его работу; на фиг. 3 структурная электрическая схема формирователя стробов; на фиг. 4 структурная электрическая схема цифрового процессора.

Устройство содержит антенну 1, приемник 2, ограничитель 3, элемент совпадения 4, два элемента равнозначности 5 и 6, эталонный генератор 7, два счетчика 8 и 9, цифровой процессор 19, генератор 11 импульсов, формирователи сброса 12 и стробов 13.

Формирователь 13 стробов содержит тактовый генератор 14, счетчик 15 адреса, блок 16 памяти, два элемента И 17 и 18, элемент ИЛИ 19, формирователь 20 импульсов, блок задержки 21, триггер 22, элемент сброса 23. Цифровой процессор 10 содержит вычислитель 24, блок 25 постоянной памяти, блок 26 оперативной памяти, два дешифратора 27 и 28, два элемента И 29 и 30 и два регистра 31 и 32.

Устройство работает следующим образом.

Рассмотрим работу предлагаемого устройства при использовании его в приемоиндикаторе навигационной системы "Омега" для обнаружения и измерения фазы принятых сигналов известных частот.

Входные сигналы устройства, представляющие собой смесь сигналов, подлежащих измерению, и помех, принимаются антенной 1, фильтруются, преобразуются по частоте, усиливаются в приемнике 2 и поступают на вход ограничителя 3 (см. фиг. 2а). Как известно в навигационной системе "Омега" излучаются сигналы от восьми передающих станций (A, B, C, D, E, F, G, H) по способу разделения во времени на одной и той же частоте (см. фиг. 2а). Длительность Т цикла излучения системы составляет 10 с (Т=10 с), продолжительность времени излучения сигнала одной станцией Тсизменяется от 0,9 до 1,2 с (Тс=0,9-1,2 с). Ограничитель 3 преобразует сигнал с выхода приемника 2 (см. фиг. 2а) в прямоугольные импульсы, нормированные по амплитуде (см. фиг. 2б), которые поступают на элемент совпадения 4.

По включении устройства первоначально выполняется режим поиска сигнала. При этом на второй вход элемента совпадения 4 от формирователя 13 в течение цикла Т (см. фиг. 2в) поступают импульсные последовательности длительностью tn и периодом Tn (см. фиг. 2в), причем  =n целое число выбирается из условия обеспечения выбирается из условия обеспечения заданной точности режима поиска. В течение длительности th1(см. 2в, г) элемент совпадения 4 открывается и импульсные сигналы с выхода ограничителя 3 (см. фиг. 2б) поступают на элементы равнозначности 5 и 6.

=n целое число выбирается из условия обеспечения выбирается из условия обеспечения заданной точности режима поиска. В течение длительности th1(см. 2в, г) элемент совпадения 4 открывается и импульсные сигналы с выхода ограничителя 3 (см. фиг. 2б) поступают на элементы равнозначности 5 и 6.

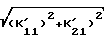

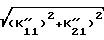

Эталонный генератор 7 вырабатывает два прямоугольных квадратурных колебания (см. фиг. 2з, и) (на фиг. 2г 2н масштаб по оси времени увеличен по сравнению с масштабом фиг. 2а -2в). Первое колебание поступает на элемент равнозначности 5 (см. фиг. 2з), второе, сдвинутое на 90о относительно первого, на элемент равнозначности 6. Элементы равнозначности 5 и 6 обеспечивают выполнение операций перемножения сигналов равных частот с выхода элемента совпадения 4 (см. фиг. 2д) с эталонными колебаниями генератора 7 соответственно фиг. 2з, и. Импульсные последовательности с выходов элементов равнозначности 5 и 6 используются для управления режимами работы счетчиков 8 и 9, которые обеспечивают подсчет количества импульсов высокой частоты генератора 11 за длительность интервала tn. По окончании каждого интервала tn1 (см. фиг. 2г) цифровой процессор 10, получив от формирователя 13 сигнал управления (см. фиг. 2е), переписывает в свои регистры выходную информацию счетчиков 8 и 9 (для tn1 коды чисел К11 и К12соответственно). После чего сигналом с формирователя 13 (см. фиг. 2ж) счетчики 8 и 9 обнуляются и готовы для работы в следующем интервале Тn(см. фиг. 2г). Цифровой процессор 10 производит вычисление параметра принятого сигнала по формуле

R1=

Во втором интервале Тn2 (см. фиг. 2в, г), в соответствии с описанной выше работой, в счетчиках 8 и 9 будут накоплены коды чисел К21и К22, которые затем переписываются в цифровой процессор 10, где вычисляется величина R2

R2=

В описанном режиме устройство работает в течение всего цикла системы Т (см. фиг. 2в). При этом определяются величины R1, R2, Ri и т.д. до Rn, поскольку в длительности цикла Т укладываются n периодов

Tn·Ri=  где i номер интервала tni от начала цикла Т, формируемого в формирователе 13 (см. фиг. 2в).

где i номер интервала tni от начала цикла Т, формируемого в формирователе 13 (см. фиг. 2в).

По окончании цикла Т (момент времени tn на фиг. 2в) в цифровом процессоре 10 будут накоплены модули Ri (n значений), по которым в цифровом процессоре 10 вычисляются n значений взаимно корреляционной функции относительно опорной временной последовательности системы по формуле

Nj=  Ri·Wi-j где Wi-j опорная последовательность, сдвинутая относительно начала цикла Т (см. фиг. 2а) принимаемого сигнала на j шагов (интервалов Tn), последовательность Wi-j повторяет с интервалом Tn огибающую сигнала системы, там, где значение огибающей отлично от нуля Wi-j=1, при отсутствии излучения Wi-j=0.

Ri·Wi-j где Wi-j опорная последовательность, сдвинутая относительно начала цикла Т (см. фиг. 2а) принимаемого сигнала на j шагов (интервалов Tn), последовательность Wi-j повторяет с интервалом Tn огибающую сигнала системы, там, где значение огибающей отлично от нуля Wi-j=1, при отсутствии излучения Wi-j=0.

Затем в цифровом процессоре 10 определяется номер интервала j, в котором вычисленное значение взаимно корреляционной функции Ni имеет максимальное значение. Максимальное значение Njмакс взаимно корреляционной функции соответствует совпадению по времени опорной последовательности устройства и огибающей принимаемого сигнала, характеризуемой величинами Ri.

Таким образом, начало цикла Т принимаемого сигнала (см. фиг. 2а) с погрешностью ±Tn/3 будет определено. Для завершения режима поиска сигнала, т. е. для совмещения начала цикла Т принимаемого сигнала (см. фиг. 2а) с началом цикла Т, формируемого формирователем 13 (см. фиг. 2в), в цифровом процессоре 10 формируется код управляющего сигнала, который в момент времени tу выполнения условия i=n-j выдается из цифрового процессора 10 в формирователь 12. В формирователе 12 формируется при этом импульсный сигнал, который поступает в формирователь 13, устанавливая его в исходное (нулевое) состояние, и с этого момента времени в формирователе 13 начинается формирование нового цикла Т, который с погрешностью Tn/2 совпадает с началом цикла принимаемого сигнала Т (см. фиг. 2а) На этом режим поиска сигнала, заключающийся в идентификации принимаемых сигналов и установке правильного порядка фазовых измерений, заканчивается и устройство переходит в режим слежения за сигналом и измерения фазовых сдвигов принимаемых сигналов.

Момент времени ty определяется в цифровом процессоре 10, например, путем подсчета количества импульсов управления (см. фиг. 2е), поступающих от формирователя стробов 13 в цифровой процессор 10 с момента времени tн (см. фиг. 2в), и при выполнении условия i=n-j цифровой процессор 10 формирует сигнал управления для установки формирователя 13 в исходное (начальное) состояние (см. фиг. 2в).

В реальных условиях работы, при приеме сигнала с высоким уровнем помех, накопление в цифровом процессоре 10 информации об огибающей принимаемого сигнала (величины R1) может осуществляться в течение нескольких (m) циклов излучения системы в соответствии с описанным алгоритмом, что позволяет повысить вероятность правильного обнаружения сигнала.

В режиме слежения за сигналом на выходах формирователя стробов 13 сигналом от формирователя сброса 12 устанавливаются новые импульсные последовательности с периодом повторения Т (см. фиг. 2л, м, н). Начало первой импульсной последовательности формирователя 13 с точностью до величины ΔТ совпадает с началом цикла Т излучения системы (ΔТмакс=±<N>Тn/2), сигналы приема которой формируются на выходе ограничителя 3 в прямоугольные импульсы (см. фиг. 2к). Особенность первой выходной импульсной последовательности формирователя 13 (см. фиг. 2л) заключается в том, что длительность времени Тс приема каждой станции разбивается на две равные части t'c=t"c (см. фиг. 2л). При этом для принимаемых станций (l станций) в течение цикла излучения Т на второй вход элемента совпадения 4 поступает первая импульсная последовательность (см. фиг. 2л), открывая его. Так, в течение длительности tIc1 (см. фиг. 2л) элемент совпадания 4 отрывается, и импульсные сигналы с выхода ограничителя 3 (см. фиг. 2к) поступают на элементы равнозначности 5 и 6. По окончании интервала t'c1 цифровой процессор 10, получив от формирователя 13 сигнал управления (см. фиг. 2м), переписывает в свои регистры выходную информацию, накопленную в счетчиках 8 и 9 за время t'c1 (коды числе К'11 и K'21 соответственно). Затем сигналом с формирователя 13 (см. фиг. 2н) счетчики 8 и 9 обнуляются и готовы для работы следующем измерительном интервале t"c. По окончании интервала t"c1 в цифровой процессор 10 переписываются по сигналу управления (см. фиг. 2м) коды чисел K"11 и K"21, накопленные в счетчиках 8 и 9 соответственно за время t"c1, а счетчики 8 и 9 обнуляются сигналом от формирователя стробов 13 (см. фиг. 2н). Цифровой процессор 10 производит вычисление параметров принятого сигнала для интервалов t'c1 и t"c1 по формулам

V

V

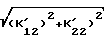

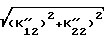

Аналогично работает устройство при приеме сигнала второй станции (интервалы накопления информации t'c2 и t"c2, коды чисел, поступившие в цифровой процессор 10, соответственно K'12, K'22 и K"12, K"22. Вычисленные параметры

V

V

В описанном режиме устройство работает в течение всего цикла системы Т, обрабатывая сигналы от l станций. Таким образом по окончании интервалов t'cl и t"cl в цифровом процессоре 10 определяются параметры

V

V

а затем вычисляются величины

а затем вычисляются величины

V′=  V

V и V″

и V″  V

V

По результатам сравнения величин V" и V''' в цифровом процессоре 10 принимается решение о сдвиге опорной импульсной последовательности формирователя стробов 13 (см. фиг. 2л), а также (см. фиг. 2м, н) в сторону опережения или в сторону отставания (при условии V'>V") относительно принимаемых сигналов устройства на величину дискрета Δt.

Сдвиг импульсных последовательностей формирователя 13 (фиг. 2л-н) может осуществляться следующим образом. В цифровом процессоре 10 по окончании вычислений величины V', V" и определения условий V1>V2 или V'< V" формируется код управляющего сигнала, который в момент времени tу(см. фиг. 2м) выдается из цифрового процессора 10 в формирователь 12. В формирователе 12 формируется при этом импульсный сигнал, который поступает в формирователь 13, устанавливая его в исходное состояние, и с этого момента времени в формирователе 13 начинается формирование нового цикла Т, который смещается на величину Δt относительно начала цикла принимаемого сигнала Т (см. фиг. 2м, л).

Момент времени tу (см. фиг. 2м) определяется в цифровом процессоре 10, например, путем подсчета количества импульсов управления δ(см. фиг. 2м), поступающих от формирователя 13 в цифровой процессор 10 по окончании интервала работы l-й станции в цикле системы Т. При выполнении условия, например, V'>V" и условия δ=1 цифровой процессор 10 формирует сигнал управления для установки формирователя стробов 13 в исходное состояние (см. фиг. 2м), и формирование нового цикла Т начинается в формирователе 13 раньше на величину Δt по сравнению с предыдущим циклом Т. Для количества импульсов управления формирование нового цикла Т происходит без смещения относительно предыдущего цикла Т (это соответствует совпадению с точностью до величины Δt начала первой импульсной последовательности формирователя 13 с началом цикла Т излучения системы фиг. 2к, л). При выполнении условий V'< V", δ=3 формирование нового цикла Т в формирователе 13 начинается с задержкой на величину Δt по сравнению с предыдущим циклом Т.

В случае организации режима программного таймера в цифровом процессоре 10 три импульса управления по окончании работы l-й станции могут отсутствовать, а момент времени tу (см. фиг. 2м), соответствующий смещению формирования начала нового цикла Т, определяется программно в цифровом процессоре 10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой стробоскопический преобразователь повторяющихся электрических сигналов | 1986 |

|

SU1386913A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ R-ЗУБЦА ЭЛЕКТРОКАРДИОСИГНАЛА | 1989 |

|

RU2012226C1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| УСТРОЙСТВО РАЗЛИЧЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 1982 |

|

SU1841009A1 |

| Устройство для усреднения импульсной последовательности | 1988 |

|

SU1524071A1 |

| Измеритель неравномерности группового времени запаздывания | 1982 |

|

SU1046739A1 |

| Цифровой фазометр | 1986 |

|

SU1337815A1 |

| Устройство для измерения амплитуды и фазы радиосигнала | 1989 |

|

SU1665811A1 |

| Цифровой стробоскопический преобразователь электрических сигналов | 1982 |

|

SU1049815A1 |

| Устройство для ультразвукового измерения характеристик внутричерепной гемоликвородинамики | 1987 |

|

SU1507334A1 |

Изобретение относится к радиолокации и может использоваться в системах поиска и измерения параметров сигналов, скрытых помехами, например в навигационной системе "Омега". Цель изобретения повышение точности определения фазы сигнала. Устройство содержит антенну 1, приемник 2, ограничитель 3, элемент совпадения 4, элементы равнозначности (ЭР) 5, 6, эталонный генератор 7, 4сч 0етчики 8, 9, цифровой процессор (ЦП) 10, генератор 11 импульсов, формирователи сброса 12 и стробов 13. В навигационной системе "Омега" за один цикл Т излучаются сигналы восьми передающих станций по способу разделения во времени на одной и той же частоте. При приеме этих сигналов устройство сначала работает в режиме поиска сигнала. В этом режиме принятый сигнал равной частоты, прошедший через элемент совпадения 4, перемножается в ЭР 5, 6 с квадратурными прямоугольными колебаниями эталонного генератора 7. Импульсы с ЭР 5, 6 управляют работой соотв. счетчиков 8, 9, подсчитывающих импульсы генератора 11 на эти интервалы. По окончании каждого интервала ti по сигналу формирователя 13 ЦП 10 получает информацию со счетчиков 8, 9 и вычисляет параметры Ri. По окончании цикла Т в ЦП 10 по всем n параметрам Ri вычисляются n значений взаимно корреляционной функции взаимно корреляционной функции Nj относительно опорной временной последовательности системы и определяется номер интервала с макс. значением Nj Т обр. определяется начало цикла Т принимаемого сигнала. Заканчивается режим поиска сигнала формированием в ЦП 10 управляющего сигнала, по которому совмещается начало цикла Т, формируемого формирователем 13, с началом цикла Т принимаемого сигнала. После этого устройство переходит в режим слежения за сигналом и измерения фазовых сдвигов принимаемого сигнала. 2 з.п. ф-лы, 4 ил.

| АЭРОЗОЛЬНЫЙ ФИЛЬТР | 2009 |

|

RU2417116C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-07-25—Публикация

1986-06-18—Подача