Изобретение относится к электротехнике и может быть использовано в качестве источников электропитания электротехнической и радиоэлектронной аппаратуры.

Цель изобретения - расширение функциональных возможностей за счет сохранения постоянным периода коммутации силовых преобразовательных ячеек при изменении числа работающих ячеек.

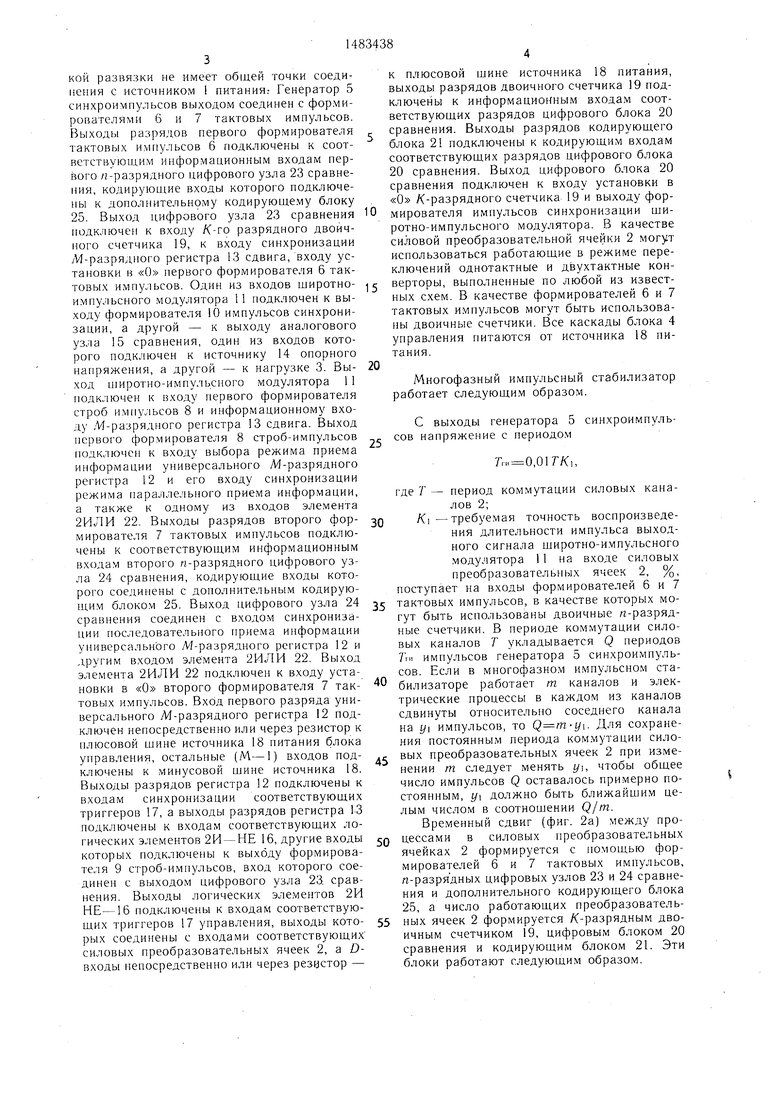

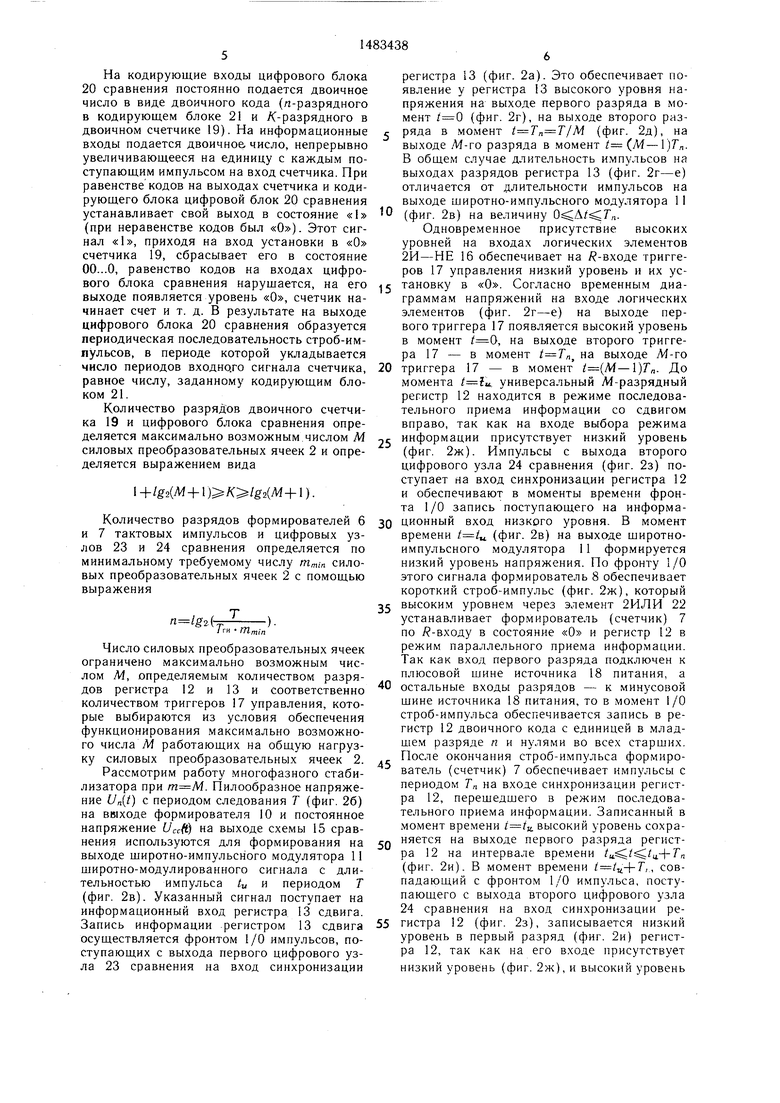

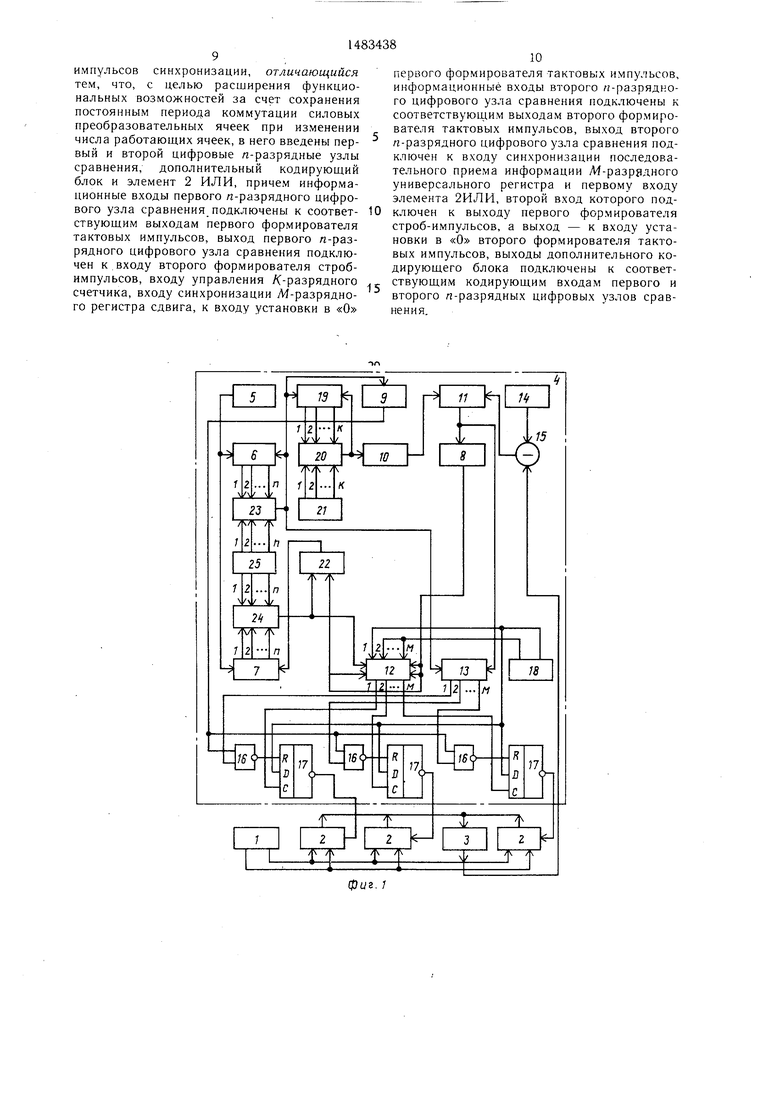

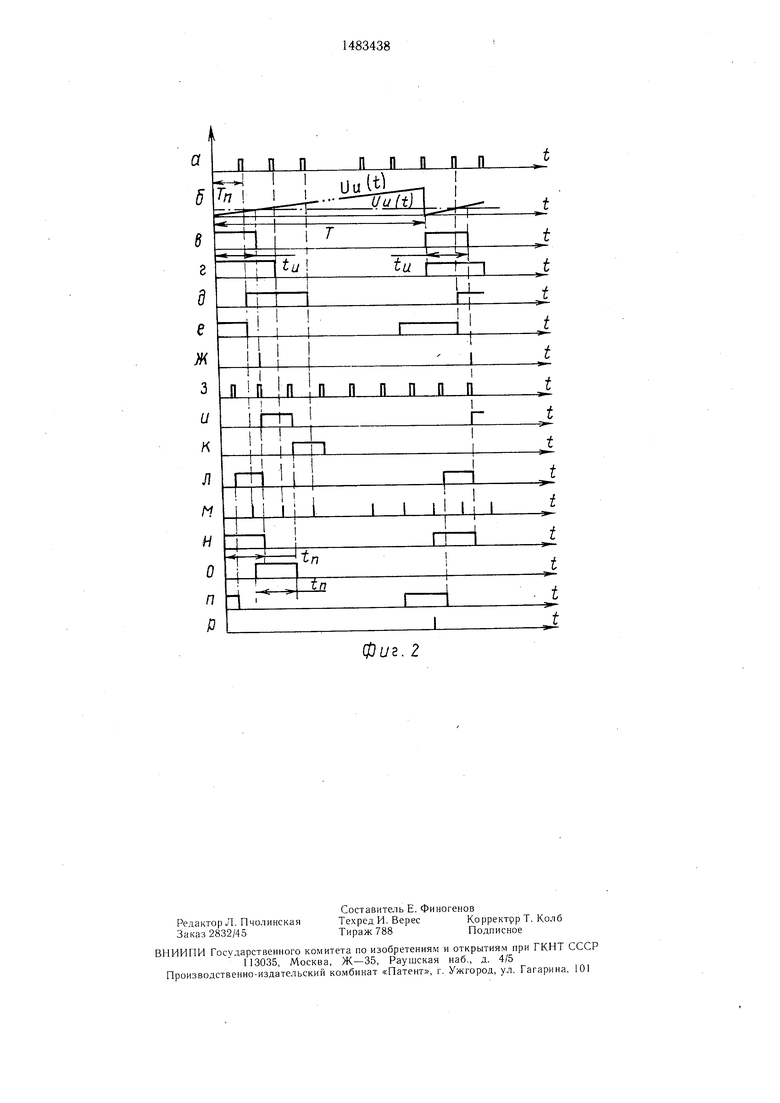

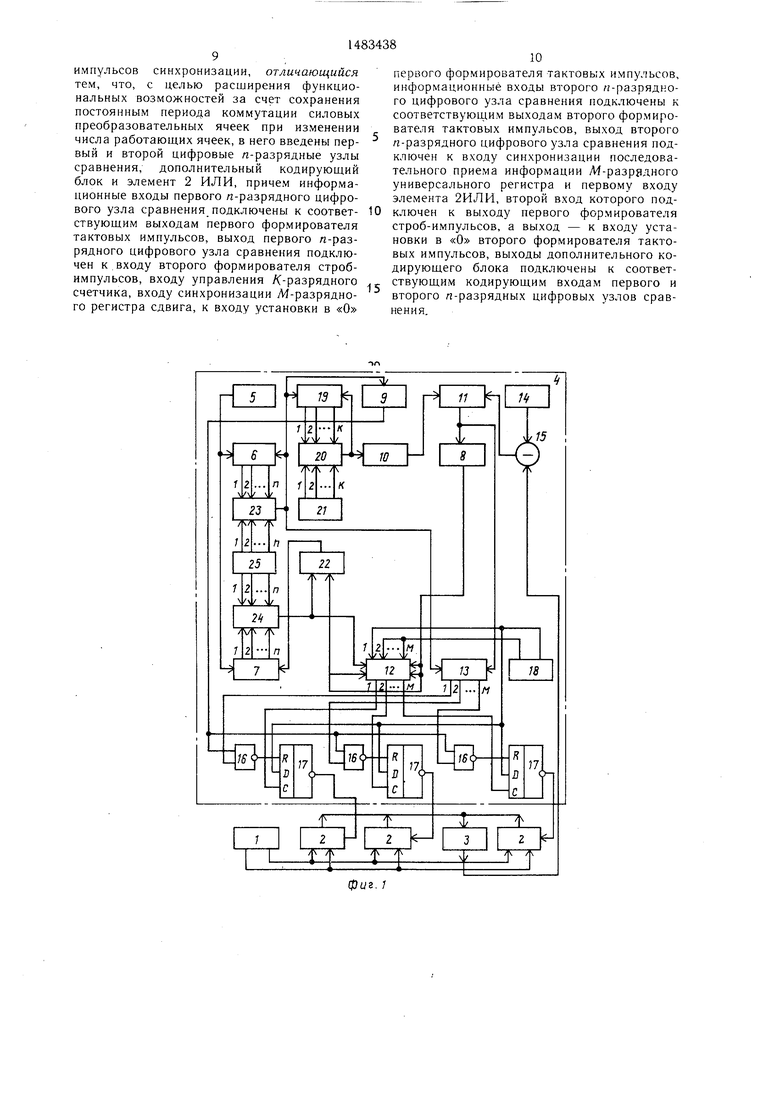

На фиг. 1 приведена схема многофазного импульсного стабилизатора напряжения; на фиг. 2 - эпюры напряжений, поясняющие работу схемы.

Многофазный импульсный стабилизатор напряжения, входные выводы которого соединены с выходом источника 1 питания, состоит из силовых преобразовательных ячеек 2, выходные выводы которых подключены к нагрузке 3 параллельно или последовательно, и блока 4 управления, содержащего генератор 5 синхроимпульсов, первый 6 и второй 7 формирователи тактовых импульсов, первый 8 и второй 9 формирователи строб-импуль- сов, формирователь 10 импульсов синхронизации широтно-импульсного модулятора 11, универсальный М-разрядный регистр 12, Л/разрядный регистр 13 сдвига, источник 14 опорного напряжения, аналоговый узел 15 сравнения, М-логических элементов 2И- НЕ 16, М-триггеров 17 управления, источник 18 питания блока управления, /(-разрядный двоичный счетчик 19, /(-разрядный цифровой блок 20 сравнения, кодирующий блок 21, элемент 2ИЛИ 22, первый 23 и второй 24 n-разрядные цифровые узлы сравнения и дополнительный кодирующий блок 25.

Источник 1 питания и силовые преобразовательные ячейки 2 имеют две общие шины. Нагрузка 3 в случае гальваничесоо со Ј оо ос

кой развязки не имеет общей точки соединения с источником 1 питания; Генератор 5 синхроимпульсов выходом соединен с формирователями 6 и 7 тактовых импульсов. Е ыходы разрядов первого формирователя тактовых импульсов 6 подключены к соответствующим информационным входам первого /г-разрядного цифрового узла 23 сравнения, кодирующие входы которого подключены к дополнительному кодирующему блоку 25. Выход цифрового узла 23 сравнения подключен к входу К-го разрядного двоичного счетчика 19, к входу синхронизации /М-разрядного регистра 13 сдвига, входу установки в «О первого формирователя 6 тактовых импульсов. Один из входов широтно- импульсного модулятора 11 подключен к выходу формирователя 10 импульсов синхронизации, а другой - к выходу аналогового узла 15 сравнения, один из входов которого подключен к источнику 14 опорного напряжения, а другой - к нагрузке 3. Вы- ход широтно-импульсного модулятора 11 подключен к входу первого формирователя строб импульсов 8 и информационному входу М-разрядного регистра 13 сдвига. Выход первого формирователя 8 строб-импульсов подключен к входу выбора режима приема информации универсального /И-разрядного регистра 12 и его входу синхронизации режима параллельного приема информации, а также к одному из входов элемента 2ИЛИ 22. Выходы разрядов второго фор- мирователя 7 тактовых импульсов подключены к соответствующим информационным входам второго «-разрядного цифрового узла 24 сравнения, кодирующие входы которого соединены с дополнительным кодирующим блоком 25. Выход цифрового узла 24 сравнения соединен с входом синхронизации последовательного приема информации универсального М-разрядного регистра 12 и другим входом элемента 2ИЛИ 22. Выход элемента 2ИЛИ 22 подключен к входу установки в «О второго формирователя 7 тактовых импульсов. Вход первого разряда универсального уИ-разрядного регистра 12 подключен непосредственно или через резистор к плюсовой шине источника 18 питания блока управления, остальные (М-1) входов подключены к минусовой шине источника 18. Выходы разрядов регистра 12 подключены к входам синхронизации соответствующих триггеров 17, а выходы разрядов регистра 13 подключены к входам соответствующих логических элементов 2И-НЕ 16, другие входы которых подключены к выходу формирователя 9 строб-импульсов, вход которого соединен с выходом цифрового узла 23 сравнения. Выходы логических элементов 2И НЕ-16 подключены к входам соответствующих триггеров 17 управления, выходы кото- рых соединены с входами соответствующих силовых преобразовательных ячеек 2, a D- входы непосредственно или через резистор -

к плюсовой шине источника 18 питания, выходы разрядов двоичного счетчика 19 подключены к информационным входам соответствующих разрядов цифрового блока 20 сравнения. Выходы разрядов кодирующего блока 21 подключены к кодирующим входам соответствующих разрядов цифрового блока 20 сравнения. Выход цифрового блока 20 сравнения подключен к входу установки в «О /(-разрядного счетчика 19 и выходу формирователя импульсов синхронизации широтно-импульсного модулятора. В качестве силовой преобразовательной ячейки 2 могут использоваться работающие в режиме переключений однотактные и двухтактные конверторы, выполненные по любой из известных схем. В качестве формирователей 6 и 7 тактовых импульсов могут быть использованы двоичные счетчики. Все каскады блока 4 управления питаются от источника 18 питания.

Многофазный импульсный стабилизатор работает следующим образом.

синхроимпульС выходы генератора 5 сов напряжение с периодом

Г, и 0,0174(1,

где Т - период коммутации силовых каналов 2;

К -требуемая точность воспроизведения длительности импульса выходного сигнала широтно-импульсного модулятора 11 на входе силовых преобразовательных ячеек 2, %, поступает на входы формирователей 6 и 7 тактовых импульсов, в качестве которых могут быть использованы двоичные п-разряд- ные счетчики. В периоде коммутации силовых каналов Т укладывается Q периодов 7п1 импульсов генератора 5 синхроимпульсов. Если в многофазном импульсном стабилизаторе работает т каналов и электрические процессы в каждом из каналов сдвинуты относительно соседнего канала на у импульсов, то . Для сохранения постоянным периода коммутации силовых преобразовательных ячеек 2 при изменении т следует менять у, чтобы общее число импульсов Q оставалось примерно постоянным, у должно быть ближайшим целым числом в соотношении Q/m.

Временный сдвиг (фиг. 2а) между процессами в силовых преобразовательных ячейках 2 формируется с помощью формирователей 6 и 7 тактовых импульсов, n-разрядных цифровых узлов 23 и 24 сравнения и дополнительного кодирующего блока 25, а число работающих преобразовательных ячеек 2 формируется /(-разрядным двоичным счетчиком 19, цифровым блоком 20 сравнения и кодирующим блоком 21. Эти блоки работают следующим образом.

На кодирующие входы цифрового блока 20 сравнения постоянно подается двоичное число в виде двоичного кода («-разрядного в кодирующем блоке 21 и Л -разрядного в двоичном счетчике 19). На информационные с входы подается двоичное число, непрерывно увеличивающееся на единицу с каждым поступающим импульсом на вход счетчика. При равенстве кодов на выходах счетчика и кодирующего блока цифровой блок 20 сравнения устанавливает свой выход в состояние «1 Ю (при неравенстве кодов был «О). Этот сигнал «1, приходя на вход установки в «О счетчика 19, сбрасывает его в состояние 00...О, равенство кодов на входах цифрового блока сравнения нарушается, на его ,с выходе появляется уровень «О, счетчик начинает счет и т. д. В результате на выходе цифрового блока 20 сравнения образуется периодическая последовательность строб-импульсов, в периоде которой укладывается

регистра 13 (фиг. 2а). Это обеспечивает появление у регистра 13 высокого уровня напряжения на выходе первого разряда в момент 0 (фиг. 2г), на выходе второго разряда в момент (фиг. 2д), на выходе М-го разряда в момент il(Af- )Tn. В общем случае длительность импульсов на выходах разрядов регистра 13 (фиг. 2г-е) отличается от длительности импульсов на выходе широтно-импульсного модулятора 11 (фиг. 2в) на величину .

Одновременное присутствие высоких уровней на входах логических элементов 2И-НЕ 16 обеспечивает на / -входе триггеров 17 управления низкий уровень и их установку в «О. Согласно временным диаграммам напряжений на входе логических элементов (фиг. 2г-е) на выходе первого триггера 17 появляется высокий уровень в момент , на выходе второго триггера 17 - в момент на выходе М-го

число периодов входного сигнала счетчика, 20 триггера 17 - в момент t(M-1)Г„. До

25

момента . универсальный М-разрядный регистр 12 находится в режиме последовательного приема информации со сдвигом вправо, так как на входе выбора режима информации присутствует низкий уровень (фиг. 2ж). Импульсы с выхода второго цифрового узла 24 сравнения (фиг. 2з) поступает на вход синхронизации регистра 12 и обеспечивают в моменты времени фронта 1/0 запись поступающего на информаКоличество разрядов формирователей б 30 дионный вход низкого уровня. В момент

времени . (фиг. 2в) на выходе широтноравное числу, заданному кодирующим блоком 21.

Количество разрядов двоичного счетчика 19 и цифрового блока сравнения определяется максимально возможным числом М силовых преобразовательных ячеек 2 и определяется выражением вида

I+/g2(M + l)/Qs/g2().

и 7 тактовых импульсов и цифровых узлов 23 и 24 сравнения определяется по минимальному требуемому числу mmin силовых преобразовательных ячеек 2 с помощью выражения

«-г

(/ги mmin

Число силовых преобразовательных ячеек ограничено максимально возможным числом М, определяемым количеством разрядов регистра 12 и 13 и соответственно количеством триггеров 17 управления, которые выбираются из условия обеспечения функционирования максимально возможного числа М работающих на общую нагрузку силовых преобразовательных ячеек 2.

Рассмотрим работу многофазного стабилизатора при . Пилообразное напряжение Un(t) с периодом следования Т (фиг. 26) на ввиоде формирователя 10 и постоянное напряжение Ucc(t) на выходе схемы 15 сравнения используются для формирования на выходе широтно-импульсного модулятора 11 широтно-модулированного сигнала с длительностью импульса tu и периодом Т (фиг. 2в). Указанный сигнал поступает на информационный вход регистра 13 сдвига. Запись информации регистром 13 сдвига осуществляется фронтом 1/0 импульсов, поступающих с выхода первого цифрового узла 23 сравнения на вход синхронизации

импульсного модулятора 11 формируется низкий уровень напряжения. По фронту 1/0 этого сигнала формирователь 8 обеспечивает короткий строб-импульс (фиг. 2ж), который

35 высоким уровнем через элемент 2ИЛИ 22 устанавливает формирователь (счетчик) 7 по / -входу в состояние «О и регистр 12 в режим параллельного приема информации. Так как вход первого разряда подключен к плюсовой шине источника 18 питания, а

40 остальные входы разрядов - к минусовой шине источника 18 питания, то в момент 1/0 строб-импульса обеспечивается запись в регистр 12 двоичного кода с единицей в младшем разряде п и нулями во всех старших. После окончания строб-импульса формирователь (счетчик) 7 обеспечивает импульсы с периодом Тп на входе синхронизации регистра 12, перешедшего в режим последовательного приема информации. Записанный в момент времени высокий уровень сохраняется на выходе первого разряда регистра 12 на интервале времени (фиг. 2и). В момент времени / /Vf-7,, совпадающий с фронтом 1/0 импульса, поступающего с выхода второго цифрового узла 24 сравнения на вход синхронизации ре55 гистра 12 (фиг. 2з), записывается низкий уровень в первый разряд (фиг. 2и) регистра 12, так как на его входе присутствует низкий уровень (фиг. 2ж), и высокий уровень

45

50

регистра 13 (фиг. 2а). Это обеспечивает появление у регистра 13 высокого уровня напряжения на выходе первого разряда в момент 0 (фиг. 2г), на выходе второго разряда в момент (фиг. 2д), на выходе М-го разряда в момент il(Af- )Tn. В общем случае длительность импульсов на выходах разрядов регистра 13 (фиг. 2г-е) отличается от длительности импульсов на выходе широтно-импульсного модулятора 11 (фиг. 2в) на величину .

Одновременное присутствие высоких уровней на входах логических элементов 2И-НЕ 16 обеспечивает на / -входе триггеров 17 управления низкий уровень и их установку в «О. Согласно временным диаграммам напряжений на входе логических элементов (фиг. 2г-е) на выходе первого триггера 17 появляется высокий уровень в момент , на выходе второго триггера 17 - в момент на выходе М-го

триггера 17 - в момент t(M-1)Г„. До

импульсного модулятора 11 формируется низкий уровень напряжения. По фронту 1/0 этого сигнала формирователь 8 обеспечивает короткий строб-импульс (фиг. 2ж), который

5 высоким уровнем через элемент 2ИЛИ 22 устанавливает формирователь (счетчик) 7 по / -входу в состояние «О и регистр 12 в режим параллельного приема информации. Так как вход первого разряда подключен к плюсовой шине источника 18 питания, а

0 остальные входы разрядов - к минусовой шине источника 18 питания, то в момент 1/0 строб-импульса обеспечивается запись в регистр 12 двоичного кода с единицей в младшем разряде п и нулями во всех старших. После окончания строб-импульса формирователь (счетчик) 7 обеспечивает импульсы с периодом Тп на входе синхронизации регистра 12, перешедшего в режим последовательного приема информации. Записанный в момент времени высокий уровень сохраняется на выходе первого разряда регистра 12 на интервале времени (фиг. 2и). В момент времени / /Vf-7,, совпадающий с фронтом 1/0 импульса, поступающего с выхода второго цифрового узла 24 сравнения на вход синхронизации ре5 гистра 12 (фиг. 2з), записывается низкий уровень в первый разряд (фиг. 2и) регистра 12, так как на его входе присутствует низкий уровень (фиг. 2ж), и высокий уровень

5

0

во второй разряд (фиг. 2к) и далее на М-й разряд (фиг. 2л).

Таким образом, регистр 12 имеет высокий уровень напряжения с длительностью Тп на выходе первого разряда в момент времени , на выходе второго разряда - в момент времени t t-ut- -Tn, на выходе М-го разряда - в момент времени .Jr(M-1)Т„. Так как выходные цепи регистра 12 подключены к входам синхронизации триггеров 17 управления, то в указанные моменты времени фронтом 0/1 переключаются триггеры 17 (на-Д-входе присутствует высокий уровень). Формирователи 6 и 7 имеют одинаковую разрядность и на кодирующих входах цифровых узлов 23 и 24 сравнения присутствует один и тот же код. Это обеспечивает формирование тактовых импульсов с равным периодом следования Т„, но со сдвигом по фазе, так как начальное состояние счетчика 7 синхронизируется в момент времени t-tu.. В результате на выходах триггеров 17 управления получают широтно- модулированные импульсы (фиг. 2н, о, п), равные по длительности сигналу на выходе широтно-импульсного модулятора 11. Их сдвиг во времени на величину Тп обеспечивает сдвиг во времени электрических процессов в силовых преобразовательных ячейках 2. В следующие периоды времени процессы повторяются аналогично описанному.

. Изменение напряжения на нагрузке 3 при воздействии какого-либо возмущающего воздействия приводит к изменению уровня напряжения Ucl(i) на выходе узла 15 сравнения и соответствующему изменению сигнала на выходе широтно-импульсного модулятора 11. Это приводит к изменению (сдвигу) во времени сигналов на выходах регистра сдвига 12, воспроизводящего перепад 1/0 широтно-модулированного сигнала, и к изменению длительности сигналов на выходе триггеров 17 управления и энергии, передаваемой каждой силовой преобразовательной ячейкой 2 в нагрузку 3. Указанные изменения за счет использования отрицательной обратной связи направлены на компенсацию возмущающих воздействия и установлению с заданной точностью напряжения на нагрузке 3.

Изобретение позволяет снизить материальные затраты на производство и настройку многофазных преобразователей напряжения за счет унификации всего устройства путем унификации силовых преобразовательных ячеек и блока управления.

Указанные преимущества достигаются возможностью управления различным количеством преобразовательных ячеек (от 2 до М) при неизменном периоде коммутации силовых ячеек. Подстроечные операции при переходе от одного числа фаз к другому состоят лишь в введении нового кода в коди- оующие блоки.

Формула изобретения

5

0

Многофазный импульсный стабилизатор напряжения, содержащий М силовых преобразовательных ячеек, по входу каждая из которых соединена с входными и по выходу с выходными выводами, блок управления, состоящий из генератора синхроимпульсов, формирователя импульсов синхронизации,

широтно-импульсного модулятора М-разряд- ного регистра сдвига, AJ-триггеров управления, М логических элементов 2И-НЕ, двух /г-разрядных формирователей тактовых импульсов, двух формирователей строб-им5 пульсов, источника опорного напряжения, аналогового узла сравнения, /(-разрядного двоичного счетчика, /(-разрядного цифрового блока сравнения и кодирующего блока, причем аналоговый узел сравнения одним из входов подключен к источнику опорного

0 напряжения, другим - к выходным выводам стабилизатора, а выходом - к одному из входов широтно-импульсного модулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации, выход широтно-импульсного модулятора через первый формирователь строб-импульсов подключен к общей точке соединения входов последовательного приема информации, выбора режима приема информации, синхронизации режима параллельного приема информации универсального М-разрядного регистра сдвига, у которого вход первого разряда параллельного приема информации подключен к плюсовой шине источника питания блока управления, а остальные входы разрядов параллельного приема информации - к минусовой шине указанного источника питания, выходы разрядов - к входам синхронизации соответствующих триггеров управления, у которых выходы подключены к входам управления соответствующих силовых преобразовательных ячеек, / -входы к выходам соответствующих логических элементов 2И-НЕ D-входы к плюсовой шине источника питания блока управления, первые входы М логических элементов 2И-НЕ подключены к выходу второго формирователя строб-импульсов, выход генератора синхроимпульсов подключен к входам первого и второго формирователей тактовых импульсов, вторые входы М логических элементов 2И-НЕ подключены к соответствующим выходам разрядов регистра сдвига, вход после0 довательного приема информации которого подключен к выходу широтно-импульсного модулятора, каждый из К выходов К-раз- рядного счетчика подключен к соответствующим информационным входам /(-разрядного цифрового блока сравнения, кодирующие

5 входы которого подключены к соответствующим выходам кодирующего блока, а выход - ко входу установки в «О /(-разрядного двоичного счетчика и входу формирователя

5

0

импульсов синхронизации, отличающийся тем, что, с целью расширения функциональных возможностей за счет сохранения постоянным периода коммутации силовых преобразовательных ячеек при изменении числа работающих ячеек, в него введены первый и второй цифровые «-разрядные узлы сравнения, дополнительный кодирующий блок и элемент 2 ИЛИ, причем информационные входы первого n-разрядного цифрового узла сравнения подключены к соответствующим выходам первого формирователя тактовых импульсов, выход первого п-раз- рядного цифрового узла сравнения подключен к входу второго формирователя строб- импульсов, входу управления /(-разрядного счетчика, входу синхронизации УИ-разрядно- го регистра сдвига, к входу установки в «О

0

5

первого формирователя тактовых импульсов, информационные входы второго «-разрядного цифрового узла сравнения подключены к соответствующим выходам второго формирователя тактовых импульсов, выход второго «-разрядного цифрового узла сравнения подключен к входу синхронизации последовательного приема информации М-разрядного универсального регистра и первому входу элемента 2ИЛИ, второй вход которого подключен к выходу первого формирователя строб-импульсов, а выход - к входу установки в «О второго формирователя тактовых импульсов, выходы дополнительного кодирующего блока подключены к соответствующим кодирующим входам первого и второго «-разрядных цифровых узлов сравнения.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор напряжения | 1990 |

|

SU1700545A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Многозонный стабилизатор постоянного напряжения | 1990 |

|

SU1700544A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1302255A1 |

Изобретение относится к электротехнике и может быть использовано в качестве источников питания электротехнической и радиоэлектронной аппаратуры. Цель изобретения - расширение функциональных возможностей за счет сохранения постоянным периодом коммутации силовых преобразовательных ячеек при изменении числа работающих ячеек. Устройство содержит M силовых преобразовательных ячеек 2, управление которыми производится при помощи импульсов, подаваемых с выхода блока 4 управления. Для формирования переднего и заднего фронтов управляющих импульсов блок 4 управления выполнен на широтно-импульсном модуляторе 11, М-разрядном универсальном регистре 12, М-разрядном регистре 13 сдвига, К-разрядном двоичном счетчике 19, К-разрядном цифровом блоке 20 сравнения. Число M преобразовательных ячеек 2 ограничивается максимально возможным числом М, определяемым количеством разрядов регистров 12 и 13 и количеством триггеров 17. Поддержание постоянного периода коммутации преобразовательных ячеек 2 обеспечивается формирователями тактовых импульсов 6, 7 N-разрядными цифровыми узлами 23, 24 сравнения и дополнительным кодирующим блоком 25. 2 ил.

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-05-30—Публикация

1987-11-04—Подача