(21) 4034296/24-24 . (22) 21,OJ.86 (46) 15-,1К88. Биш. 42

(71)Пермский политехнический институт

(72)Е.Л.Кон, В.М.Кустов, Н.Н.Матушкин, А.Г.Меркушев и А.А.ЮнсакоВ

(53)681.325(088.8)

(56) Авторское свидетельство СССР 525240, кл. Н 03 М 1/34, 1976. Авторское свидетельство СССР № 706925, кл. Н 03 М 1/34, 15.06.78.

(54)АДАПТИВНЫЙАНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

.(57) Изобретение относится к информационно-измерительной технике, а

также может быть использовано в системах автоматического регулирования и управления в качестве первичного Преобразователя для устройства ввода в ЦВМ. В устройство, содержащее управ ляемый цифровой делитель, счетчик импульсов, ключ, аналого-цифровой преобразователь считывания, элемент управления, блок сравнения, с целью по- вьшения точности преобразования за счет адаптивного изменения числа разрядов преобразователя в зависимости от скорости изменения входного сигнала, введены шифратор, преобразователь погрешности аппроксимации, элемент ввода дискретных сигналов, элемент вывода дискретных сигналов, оперативное запоминающее устройство, постоянное запоминающее устройство. 4 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности (его варианты) | 1983 |

|

SU1144189A1 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Адаптивный коммутатор телеизмерительной системы | 1988 |

|

SU1508260A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2334355C1 |

| Устройство для вычисления параметров трехфазной сети | 1986 |

|

SU1376104A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Устройство для передачи телеметрической информации | 1980 |

|

SU886033A1 |

оо со со

Изобретение относится к информационно-измерительной техникеJ а также может быть использовано в системах автоматического регулирования и уп- равления в качестве первичного преобразователя для устройства ввода в ЦВМ.

Целью изобретения является повышение точности преобразования за счет адаптивного изменения числа разрядов преобразователя в зависимости от скорости изменения входного сигнала

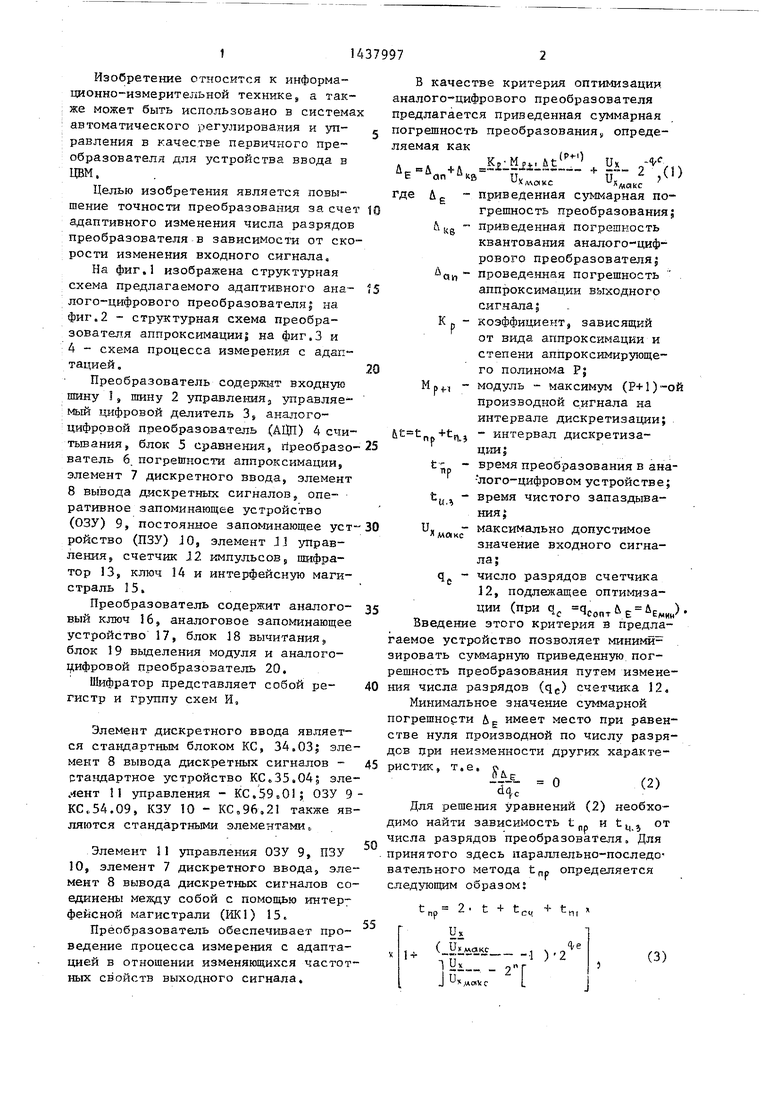

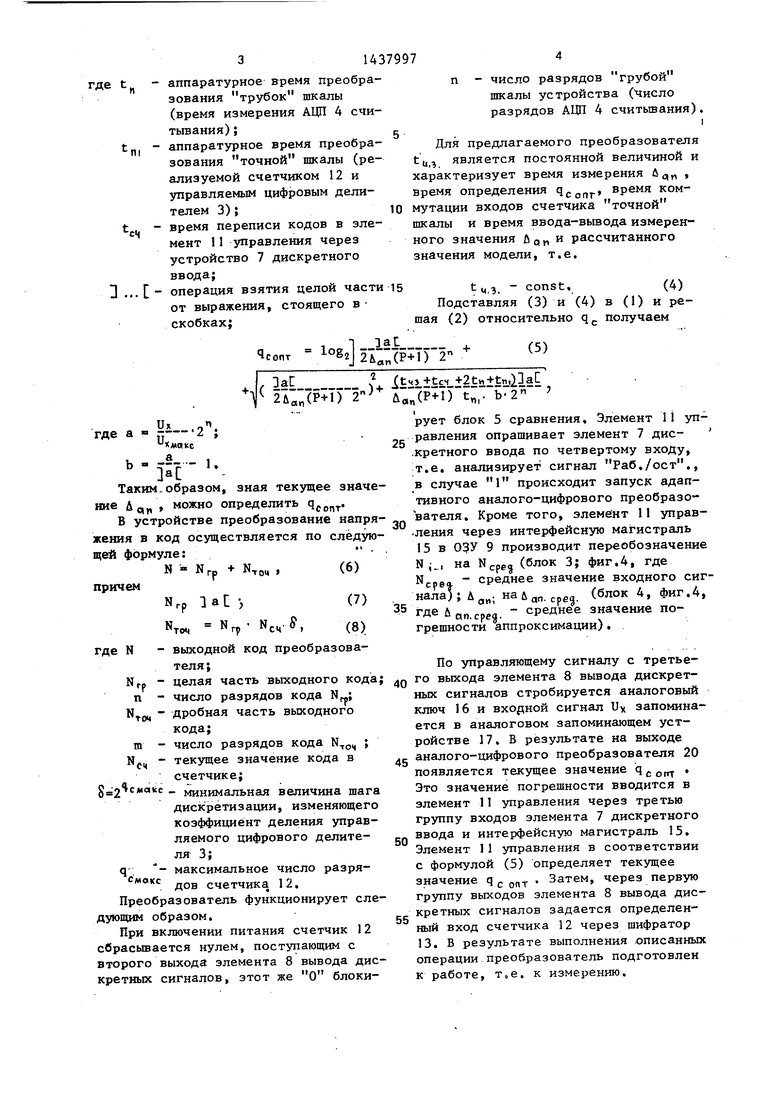

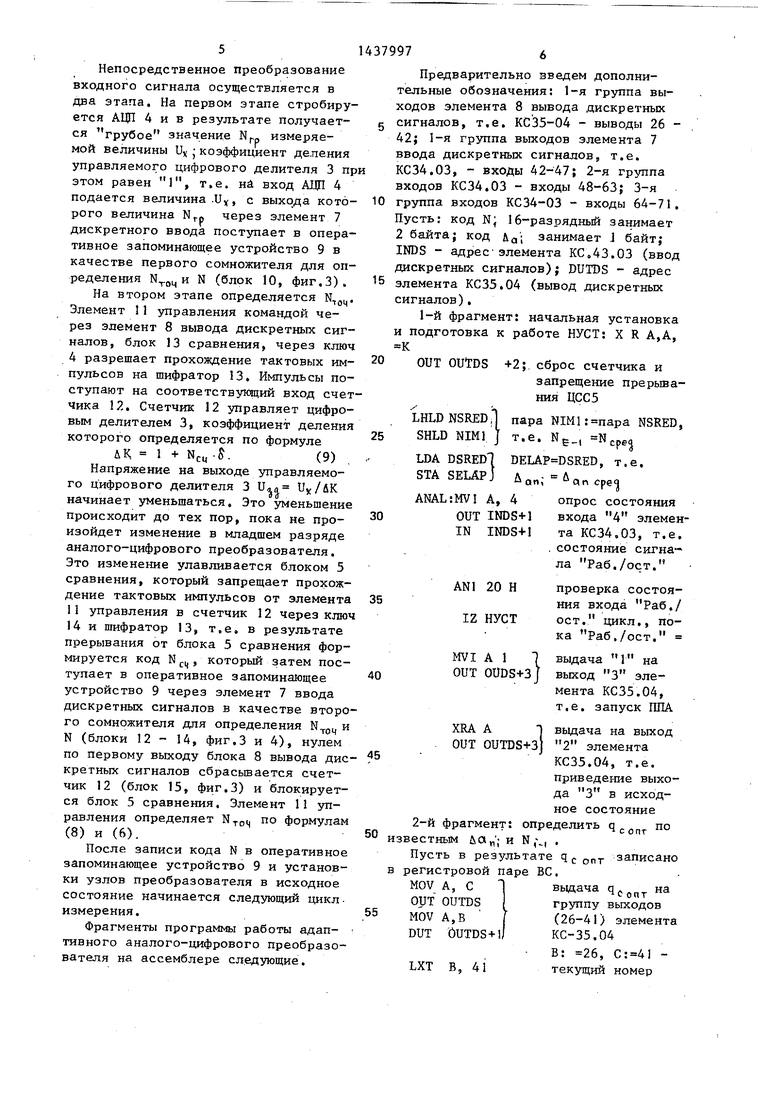

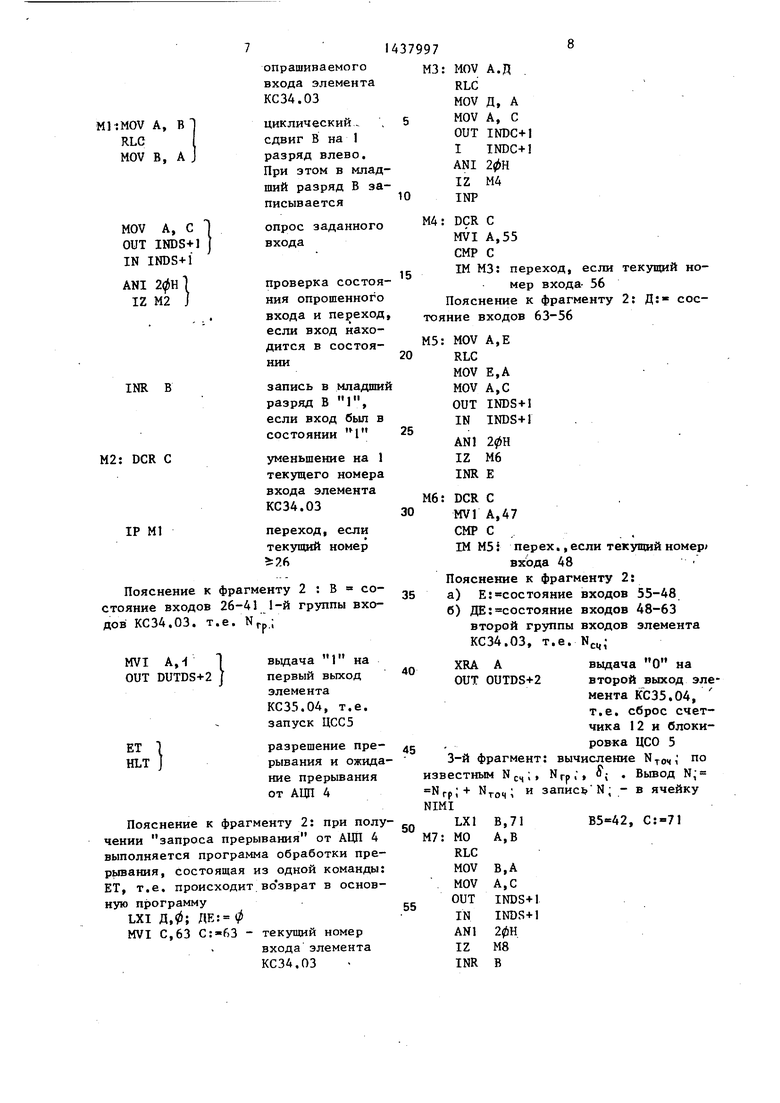

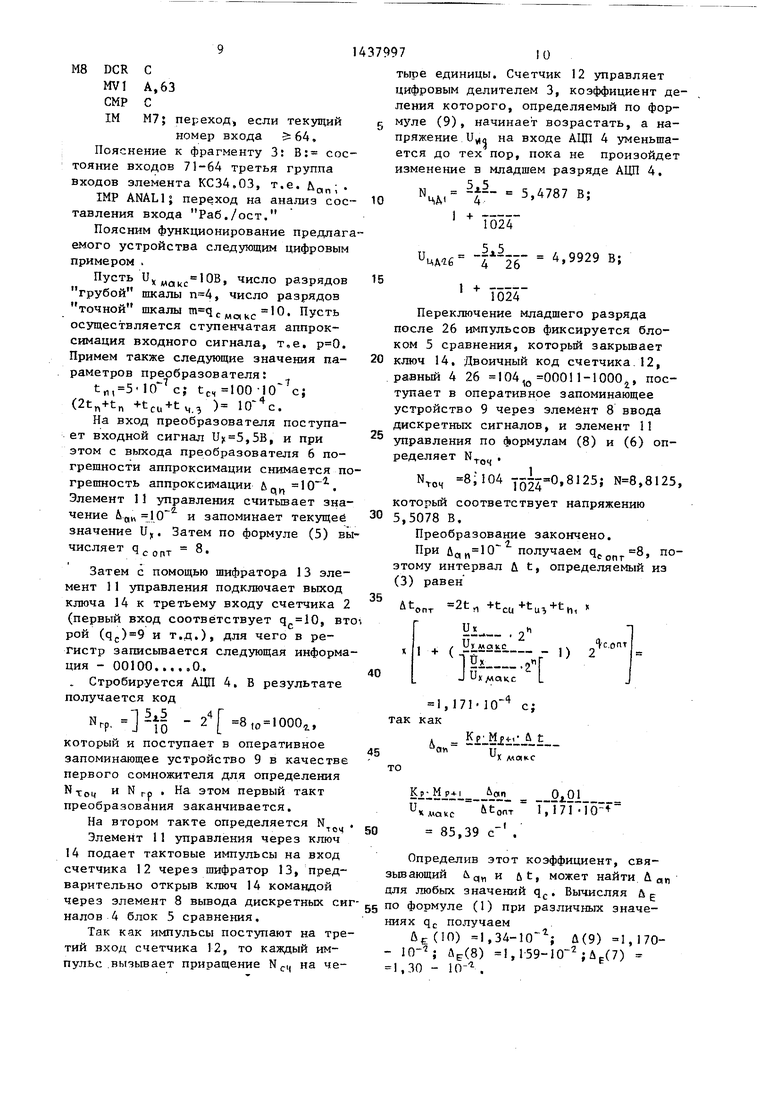

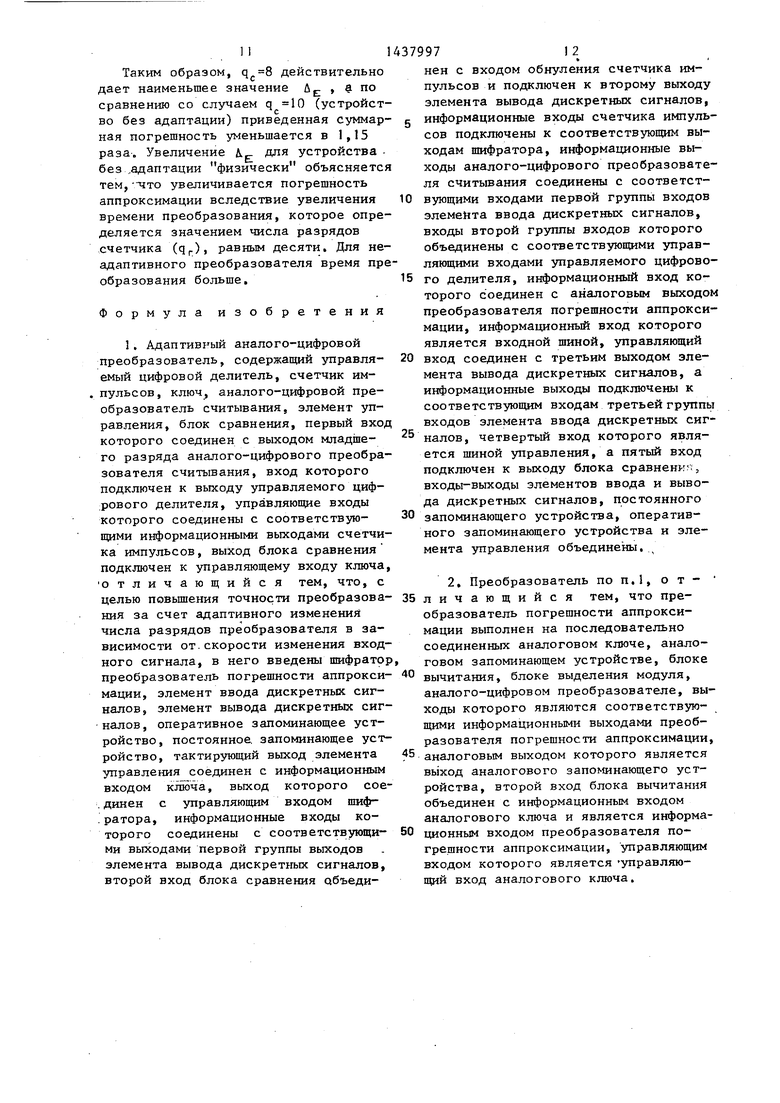

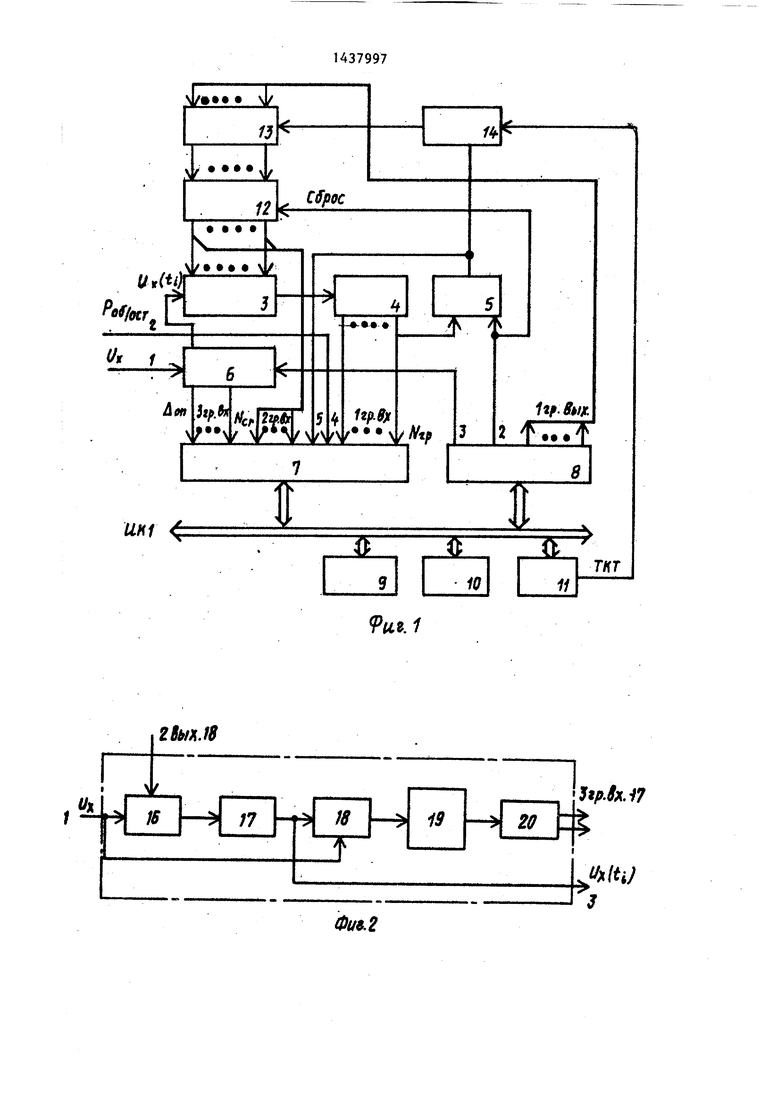

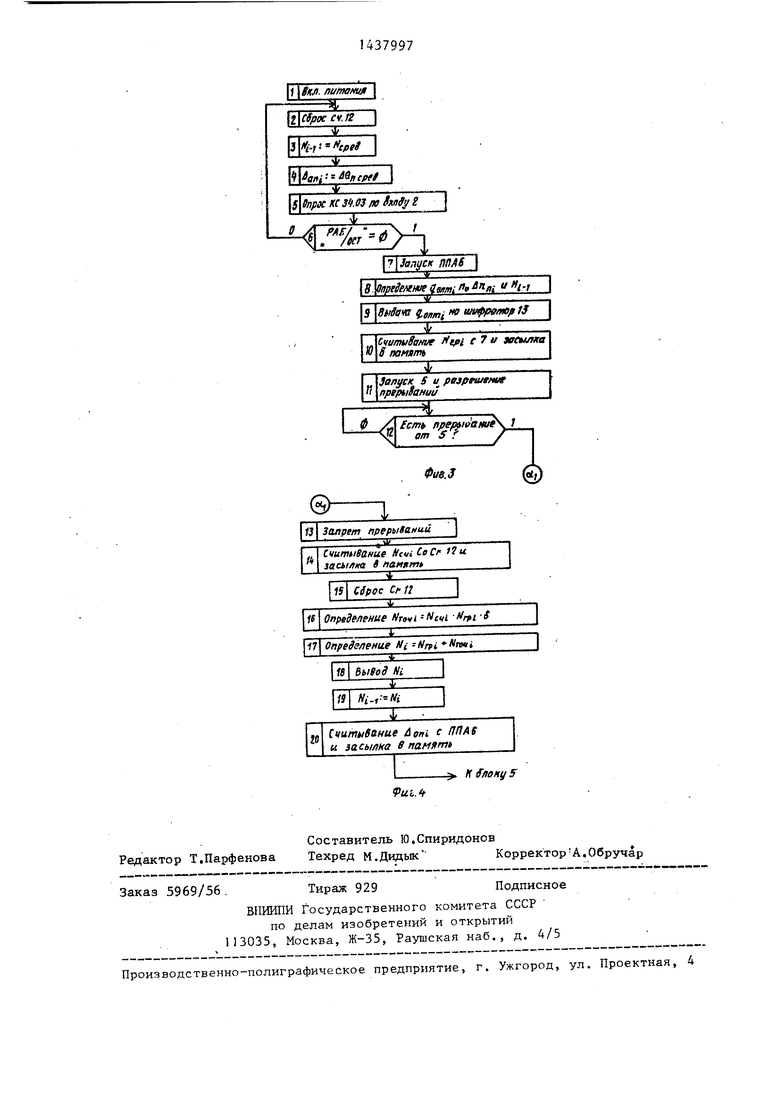

На фиг.1 изображена структурная схема предлагаемого адаптивного ана- лого-цифрового преобразователя на фиг.2 - структурная схема преобразователя аппроксимации; на фиг.З и 4 - схема процесса измерения с адаптацией ,

Преобразователь содержат входную шину I, шину 2 управлення, управляв- мый цифровой делитель 3 аналого- цифровой преобразователь (АЦП) 4 счи- тьшания, блок 5 сравнения, йреобразо- ватель 6 погрейтности аппроксимации, элемент 7 дискретного ввода, элемент 8 вывода дискретных сигналовj оперативное запоминающее устройство (ОЗУ) 9, постоянное запоминающее устройство (ПЗУ) JO, элемент 11 управления, счетчик 12 импульсов, шифратор 13, ключ А и интерфейсную магистраль 15.

Преобразователь содержит аналого- вый ключ 16, аналоговое запоминающее устройство 17, блок 18 вычитания, блок 9 выделения модуля и аналого- цифровой преобразователь 20.

Шифратор представляет собой ре- гистр и группу схем И,

Элемент дискретного ввода является CTai-адартным блоком КС, 34.03| элемент 8 вывода дискретных сигналов стандартное устройство КС.35,04; элемент 11 управления - КС.59 01 | ОЗУ 9 КС..54.09, КЗУ 10 - КС,96.21 также являются стандартными элементами„

Элемент 11 управления ОЗУ 9, ПЗУ 10, элемент 7 дискретного ввода, элемент В вывода дискретных сигналов соединены между собой с помощью интерфейсной магистрали (ИК) 15,

Преобразоватегль обеспечивает проведение процесса измерения с адаптацией в отношении изменяющихся частотных свойств выходного сигнала.

В качестве критерия оптимизации аналого-цифрового преобразователя предлагается приведенная суммарная погрещность преобразования;, определяемая как л . . Кр-Мр, UK ,

д,,,-5 --;---о:: .

где ug - приведенная сз ммарная погрешность преобразования; Q приведенная погрешность квантования аналого-цифрового преобразователя ug - проведенная погрешность аппроксимации выходного сигнала5

К к - коэффициент, зависящий от вида аппроксимации и степени аппроксимирующего полинома Р5

Мр, - модуль - максимум (Р+1)-о производной сигнала на интервале дискретизации; . -t-tf j - интервал дискретизации;t : - время преобразования в аналого-цифровом устройстве; ty - время чистого запаздывания | и - максимально допустимое

значение входного сигнала;

q - число разрядов счетчика 12, подлежащее оптимизации (при q ЧСОПТ Е ЕЛ,ИН Введение этого критерия в предлагаемое устройство позволяет минимй-- зировать суммарную приведенную погрешность Преобразования путем изменения числа разрядов (q) счетчика 12,

Минимальное значение суммарной погрешности ig имеет место при равенстве нуля производной по числу разрядов цри неизменности других характеристик, т.е. о,

0 (2)

Для решения уравнений (2) необходимо найти зависимость t . и от числа разрядов преобразователя. Для принятого здесь параллельно-последо вательного метода определяется следующим образом:

t,p 2. t + tc, + t, X

у,

(„UlMi i.c.1 ),

1 yi.. 2 г

J L

(3)

ni

31437997

де t - аппаратурное &ремя преобразования трубок шкалы (время измерения АЦП 4 счи- тьгаания);

аппаратурное время преобразования точной шкалы (ре- t ализуемой счетчиком 12 и управляемым цифровым делителем 3) ;

- время переписи кодов в элемент 11 управления через устройство 7 дискретного ввода;

- операция взятия целой части 15 от выражения, стоящего в скобках;

1 1 Ч с опт /°g2j2l(P+T)

10

сц

ха вр му шк но зн

ша

flat. i t4j+tcM+2tv,+t«,

ir(

где а

b ..о.

IT

it-r

Таким.образом, зная текние Aqj, , можно определить

В устройстве преобразовжения в код осуществляется щей формуле:

N « N гп + N, причем

Nrp

7 ЗаС

том

N

N,

NC.-,

(8)

де N

N

N

Р п

том

m N

сч

том т

выходной код преобразователя;

целая часть выходного кода; число разрядов кода дробная часть выходного кода;

число разрядов кода N ; текущее значение кода в счетчике;

2 - минимальная величина шага дискретизации, изменяющего коэффициент деления управляемого цифрового делителя 3;

- максимальное число разрядов счетчика 12. Преобразователь функционирует слеующим образом.

При включении питания счетчик 12 брасьтается нулем, поступающим с торого выхода элемента 8 вывода дисретных сигналов, этот же О блокиСмаке

t

п - число разрядов грубой шкалы устройства (число

разрядов АЦП 4 считьшания).

I

Для предлагаемого преобразователя является постоянной величиной и характеризует время измерения Лд,,, , время определения Чсопг Р коммутации входов счетчика точной шкалы и Время ввода-вывода измеренного значения йд„ и рассчитанного значения модели, т.е.

U,.

t ц }. const. Подставляя (3) и (4) шая (2) относительно q

(4)

в (1) и ре- р получаем

(5)

25

30

рует блок 5 сравнения. Элемент П управления опрашивает элемент 7 дис- .кретиого ввода по четвертому входу, т.е. анализирует сигнал Раб./ост., в случае 1 происходит запуск адаптивного аналого-цифрового преобразо- вателя. Кроме того, элемент П управ- ления через интерфейсную магистраль 15 в ОЗУ 9 производит переобозначение N N

;, на N(.pe (блок 3; фиг.4, где

35

- среднее значение входного сиг- (блок 4, фиг.4,

срео. нала) ; л „. на & д„.

где Л an.сред. среднее значение погрешности аппроксимации).

По управл5пощему сигналу с третье- 4Q го выхода элемента 8 вывода дискретных сигналов стробируется аналоговый ключ 16 и входной сигнал Uy запоминается в аналоговом запоминающем устройстве 17. В результате на выходе .g аналого-цифрового преобразователя 20 появляется текущее значение q . Это значение погрешности вводится в элемент 11 управления через третью Группу входов элемента 7 дискретного ввода и интерфейсную магистраль 15. Элемент 11 управления в соответствии с формулой (5) определяет текущее значение q . Затем, через первую группу выходов элемента 8 вывода дискретных сигналов задается определенный вход счетчика 12 через шифратор 13. В результате выполнения .описанных операции преобразователь подготовлен к работе, т,е. к измерению.

50

55

Непосредственное преобразование входного сигнала осуществляется в два этапа. На первом этапе стробиру- ется АЦП 4 и в результате получается грубое значение Nf- измеряемой величины и j коэффициент деления управляемого цифрового делителя 3 пр этом равен 1, т.е. ни вход А1ДП 4 подается величина .Uy, с выхода которого величина через элемент 7 дискретного ввода поступает в оперативное запоминающее устройство 9 в качестве первого сомножителя для определения и N (блок 10, фиг.З).

На втором этапе определяется . Элемент 11 управления командой через элемент 8 вывода дискретных сигналов, блок 13 сравнения, через ключ 4 разрешает прохождение тактовых импульсов на шифратор 13. Импульсы поступают на соответствутоций вход счетчика 12. Счетчик 12 управляет цифровым делителем 3, коэффициент деления которого определяется по формуле ДК 1 + Нсц . (9)

Напряжение на выходе управляемого цифрового делителя 3 U4a Uj(/uK начинает уменьшаться. Это уменьшение происходит до тех пор, пока не произойдет изменение в младшем разряде аналого-цифрового преобразователя. Это изменение улавливается блоком 5 сравнения, который запрещает прохождение тактовых импульсов от элемента 1 управления в счетчик 12 через ключ 14 и шифратор 13, т.е. в результате прерывания от блока 5 сравнения формируется код N (-Ц, который затем поступает в оперативное запоминающее устройство 9 через элемент 7 ввода дискретных сигналов в качестве второго сомножителя для определения и N (блоки 12 - 14, фиг.З и 4), нулем по первому выходу блока 8 вывода дис кретных сигналов сбрасьшается счетчик 12 (блок 15, фиг.З) и блокируется блок 5 сравнения. Элемент 11 управления определяет Н-тц по формулам (8) и (6).

После записи кода N в оперативное запоминающее устройство 9 и установки узлов преобразователя в исходное состояние начинается следующий цикл измерения.

Фрагменты программы работы адаптивного аналого-цифрового преобразователя на ассемблере сл.едующие.

5

Предварительно введем дополнительные обозначения; 1-я группа выходов элемента 8 вывода дискретных

сигналов, т.е. КС35-04 - выводы 26 - . 42; 1-я группа выходов элемента 7 ввода дискретных сигналов, т.е. КС34.03, - входы 42-47; 2-я группа входов КС34.03 - входы 48-63; 3-я

группа входов КС34-03 - входы 64-71. Пусть: код NJ 16-разрядный занимает 2 байта; код Лд ; занимает J байт; INDS - адрес элемента КС,43.03 (ввод дискретных сигналов); DUTDS - адрес

5 элемента КС35.04 (вывод дискретных сигналов).

1-й фрагмент: начальная установка и подготовка к работе НУСТ: X R А,А, К

0 OUT OUtDS +2;. сброс счетчика и

запрещение прерьша- ния ЦСС5

LHLDNSREDil пара NIMl NSRED,

SHLD NIM1 j т.е. Ng, Ncpe

LDA DSRED DELAP DSRED, т.е. STA SELAp

Л 4

an,

0

5

ANALsMVI A,

OUT INDS+1 IN INDS+

ANl 20 H

IZ НУСТ

0

0

5

an cpe опрос состояния входа 4 элемента КС34.03, т.е.

, состояние сигнала Раб./ост.

проверка состояния входа Раб./ ост. цикл., пока Раб./ост.

MVI А 1 1 выдача 1 на OUT OUDS+3J выход 3 элемента КС35.04, т.е. запуск ППА

XRA А 1 выдача на выход . OUT OUTDS+3J 2 элемента КС35.04, т.е. Приведение выхода 3 в исходное состояние

2-й фрагмент: определить Ч с опт ° известным и N,-, .

Пусть в результате q ;. р записано в регистровой паре ВС,

MOV А, С 1 выдача OUT OUTDS 1 группу выходов MOV А,В I (26-40 элемента DUT OUTDS+ll КС-35.04

В: 26, - LXT В, 41 текущий номер

A, В RLC MOV B, A

MOV A, С 1 OUT INDS-H I IN INDS+1

ANI 2ф1{ IZ M2

INK В

2: OCR С

IP Ml

опрашиваемого входа элемента KC34.03

циклический, сдвиг В на 1 разряд влево. При этом в младший разряд В эа- писывается

опрос заданного входа

проверка состояния опрошенного входа и переход, если вход находится в состоянии

запись в младший раэряд В , если вход был в состоянии

уменьшение на 1 текущего номера входа элемента КС34.03

переход, если текущий номер

5:26

Пояснение к фрагменту 2 : В состояние входов 26-41 1-й группы входов КС34.03. т.е. Nrp.;

A,-f 1 DUTDS+2 J

выдача г на первый выход элемента КС35.04, т.е. запуск ЦСС5

разрешение прерывания и ожидание прерывания от АЦП 4

Пояснение к фрагменту 2: при получении запроса прерывания от АЦП 4 выполняется программа обработки прерывания, состоящая из одной команды: ЕТ, т.е. происходит во зврат в основную программу

LXI Д,0;

MVI С, 63 - текущий номер входа элемента КС34.03

-

1437997

МЗ: MOV А.Д RLC

MOV Д, А 5 MOV А, С

OUT INDC+1 I INDC+I

5

ANI 20Н IZ М4 0 INP

М4: DCR С

MVI А,55 СМР С

IM М35 переход, если текущий номер входа- 56 Пояснение к фрагменту 2: Д: состояние входов 63-56

М5: MOV А,Е 0RLC

MOV Е,А MOV А,С OUT INDS+I IN INDS+1

ANI 20H IZ Мб INK E

M6: DCR С MVI A,47 CMP С IM M5i пер ex., если текущий номер

входа 48

Пояснение к фрагменту 2: 5 а) Е:«состояние входов 55-48 б) ДЕ: состояние входов 48-63 второй группы входов элемента КС34.03, т.е. N

5

0

0

XRA А

OUT OUTDS-t-2

5

C4i

выдача О на второй выход эле- мента КС35.04, т.е. сброс счетчика 12 и блокировка ЦСО 5

3-й фрагмент: вычисление N

известным N

Nrp; +

NIMI

сч «

Nrp.-, i

ТОЧ 1

по

Вывод N,

0

и запись N; - в ячейку ,

М7:

55

М8 OCR С

MVI А,63 CMP С

IM М7; переход, если текущий номер входа 5:64,

Пояснение к фрагменту 3: В: состояние входов 71-64 третья группа входов элемента КС34,03, т.е. &,„; .

IMP ANAL1; переход на анализ составления входа Раб./ост.

Поясним функционирование предлагаемого устройства следующим цифровым примером .

Пусть и ,, 10В, число разрядов грубой шкалы , число разрядов точной шкалы мсякс Пусть осуществляется ступенчатая аппроксимация входного сигнала, т,е, . Примем также следующие значения параметров преобразователя:

ГЦ

с; t,

100-10 с

гл 4

( -tcu+tv,, ) 10 с.

На вход преобразователя поступает входной сигнал U(5,5B, и при этом с выхода преобразователя 6 погрешности аппроксимации снимается погрешность аппроксимации &„„ 10. Элемент 11 управления считьшает значение &о„ 10 и запоминает текущее значение U. Затем по формуле (5) вычисляет Ясопт 8.

Затем с помощью шифратора 13 элемент 11 управления подключает выход ключа 14 к третьему входу счетчика 2

(первый вход соответствует , вт рой (qj.)9 и т.д.), для чего в регистр записьтается следующая информация - 001000.

. Стробируется АЦП 4. В результате получается код

N,

15,

J 1

,171 JO так как

45

an

и

X макс

то

50

М р-и &о(п

85,39 с

QiPl

опт |

1,171 10ifp, J lo L О-1000, который и поступает в оперативное запоминающее устройство 9 в качестве первого сомножителя для определения и N гр . На этом первый такт преобразования заканчивается.

На втором такте определяется N

Элемент 11 управления через ключ 14 подает тактовые импульсы на вход счетчика 12 через шифратор 13, предварительно открыв ключ 14 командой для любых значений q.. Вычисляя &g через элемент 8 вывода дискретных сиг- gg по формуле (1) при различных значе- налов 4 блок 5 сравнения.киях q получаем

Так как импульсы поступают на тре- ) 1,34-10 ; Л (9) 1,170- тий вход счетчика 12, то каждый им- йр(8) 1,159-10 ; 4(7) пульс .вызьгоает приращение N,, на че- 1,30 - Ю .

Определив этот коэффициент, свя- зьгоающий и ut, может найти и д

143799710

тыре единицы. Счетчик 12 управляет цифровым делителем 3, коэффициент деления которого, определяемый по фор- g муле (9), начинает возрастать, а напряжение Uy,a на входе АЦП 4 уменьшается до тех пор, пока не произойдет изменение в младшем разряде АЦП 4.

N

ЦА

5i5

5,4787 В;

Т02Г

UuA.6 5929 Б;

15

1 +

1024

Переключение младшего разряда после 26 импульсов фиксируется блоком 5 сравнения, который закрьшает

ключ 14. Двоичный код счетчика.12, равный 4 26 104,д 00011-1000J, поступает в оперативное запоминающее устройство 9 через элемент 8 ввода дискретных сигналов, и элемент 11

управления по формулам (8) и (6) определяет .

N 8;i04 ,8125, который соответствует напряжению 5,5078 В.

Преобразование закончено.

При йд„ 10 получаем qeonr° ° этому интервал U t, определяемый из (3) равен

35

At

+th,

Г О

,1с.опт

,171 JO так как

-4

an

и

X макс

то

50

М р-и &о(п

85,39 с

опт |

для любых значений gg по формуле (1) при киях q получаем

для любых значений q.. Вычисляя &g по формуле (1) при различных значе- киях q получаем

Определив этот коэффициент, свя- зьгоающий и ut, может найти и д

Таким образом, действительно дает наименьшее значение Л,- , по сравнению со случаем q 10 (устройство без адаптации) приведенная суммар- ная погрешность уменьшается в 1,15 раза. Увеличение i,- для устройства - без .адаптации физически объясняется тем, увеличивается погрешность аппроксимации вследствие увеличения Времени преобразования, которое определяется значением числа разрядов счетчика (q), равным десяти. Для неадаптивного преобразователя время преобразования больше,

25

Формула изобретения

35

5

g 0 5

0 0 5.

0

нен с входом обнуления счетчика импульсов и подключен к второму выходу элемента вывода дискретных сигналов, информационные входы счетчика импульсов подключены к соответствующим выходам шифратора, информационные выходы аналого-цифрового преобразователя считывания соединены с соответствующими входами первой группы входов элемента ввода дискретных сигналов, входы второй группы входов которого объединены с соответствующими управляющими входами управляемого цифрового делителя, информационный вход которого соединен с аналоговым выходом преобразователя погрешности аппроксимации, информационный вход которого является входной шиной, управляющий вход соединен с третьим выходом элемента вывода дискретных сигналов, а информационные выходы подключены к соответствующим входам третьей группы входов элемента ввода дискретных сигналов, четвертый вход которого является шиной управления, а пятый вход подключен к выходу блока сравнения, входы-выходы элементов ввода и вывода дискретных сигналов, постоянного запоминающего устройства, оперативного запоминающего устройства и элемента управления объединены.

20 0 5. 0

2, Преобразователь по п,1, о т - 35личающийся тем, что преобразователь погрешности аппроксимации выполнен на последовательно соединенных аналоговом ключе, аналоговом запоминающем устройстве, блоке

вычитания, блоке выделения модуля, аналого-цифровом преобразователе, выходы которого являются соответствующими информационными выходами преобразователя погрешности аппроксимации, аналоговым выходом которого является выход аналогового запоминающего устройства, второй вход блока вычитания объединен с информационным входом аналогового ключа и является информационным входом преобразователя погрешности аппроксимации, управляющим входом которого является управляющий вход аналогового ключа.

/

13

12

Cfpoc

ЫЧ f offotr

/

и, 1

SZIi

AMI

5Е

N Л N li v

Гг/./

UH1

Фиг, 2

f

/

v

Гг/./

fV-Л//.

2

Ж

ж

IL7

пт

fa

11

911г.1

f ДУ/Й7Л1И {

l Cfpoccv.K I

.,i-Hcpfi I

t .-.,/ I

SnpxKC3ifS3ffffg Uffyg

-

13

Запрет прерываний

n

Считивйние Hcvi Се Cf и. в нйнять

i7lJg,7jyc;r/7ff Ti

,iit,ttai и HI-, I

0

/c/77 am S f

Фив.З

Авторы

Даты

1988-11-15—Публикация

1986-01-21—Подача