Изобретение относится к устройствам для исследования прочностных свойств конструкций, в частности крыла воздушного судна, и может быть использовано для контроля его прочности путем замера вибраций консоли крыла непосредственно в полете.

Известен виброметр скорости ИВ-200, который обеспечивает непрерывный контроль скорости вибрации двигателя и выдает сигналы о повышенной и опасной вибрации в случаях превышения ее значения выше установленной нормы [Воробьев В.Г. и др. Авиационные приборы, информационно-измерительные системы и комплексы. Учебник для вузов / В.Г Воробьев. - М.: Транспорт, 1992. - С.104-108] [1].

Главным недостатком его применения является то, что в зависимости от модификации ИВ-200 измеряет либо уровень вибрации, либо скорость вибрации опор роторной машины. Изменение этих показателей является признаком отказа авиадвигателя и предшествует его разрушению.

Прочность крыла невозможно оценивать через показатель скорости вибрации, так как даже при снижении жесткости крыла до критического значения скорость вибрации зависит только от внешних возмущающих факторов. Кроме того, ИВ-200 решает задачу контроля авиадвигателя в полете, тогда как на основе оценки жесткости крыла должна решаться задача о возможности допуска воздушного судна в очередной полет. Таким образом, алгоритм работы, на котором основан ИВ-200, не позволяет решить задачу по оценке жесткости крыла.

Наиболее близким решением к предлагаемому является система контроля прочностных свойств крыла летательного аппарата, предназначенная для измерения колебаний на концах левого и правого крыла [Система контроля прочностных свойств крыла ЛА. Кашковский В.В., Устинов В.В. Полуэктов С.П. Желтухин С.Н. Патент РФ №2348916, от 10.03.2009] [2].

Для этого было предложено установить два дополнительных акселерометра, которые позволяют записать на участке полета от t1 до t1+Тоц, для последующей обработки на земле двух сигналов ускорения, соответственно левого и правого крыла:

и

и  ,

,

где Т - период дискретизации; Тоц - продолжительность работы устройства записи;

- число точек измерения.

- число точек измерения.

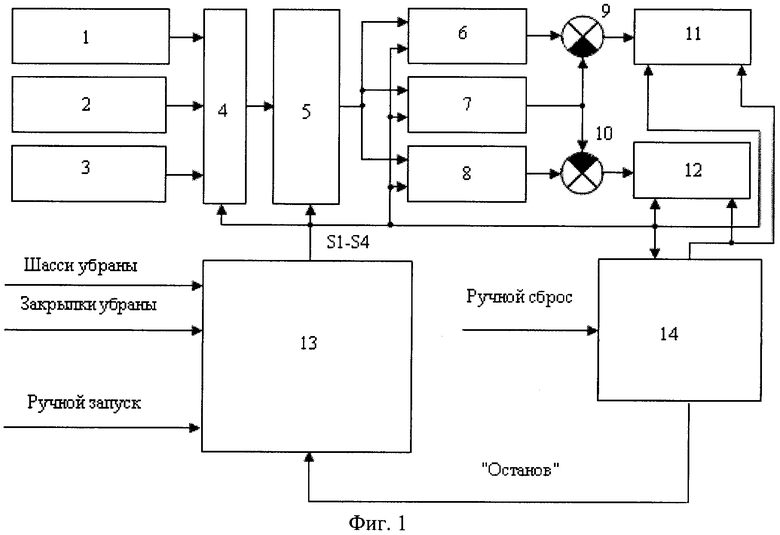

На фиг.1 представлена блок-схема прототипа системы записи сигналов  с сумматора 9 и

с сумматора 9 и  с сумматора 10,

с сумматора 10,  в запоминающие устройства 11 и 12; на фиг.2 - схема устройства управления.

в запоминающие устройства 11 и 12; на фиг.2 - схема устройства управления.

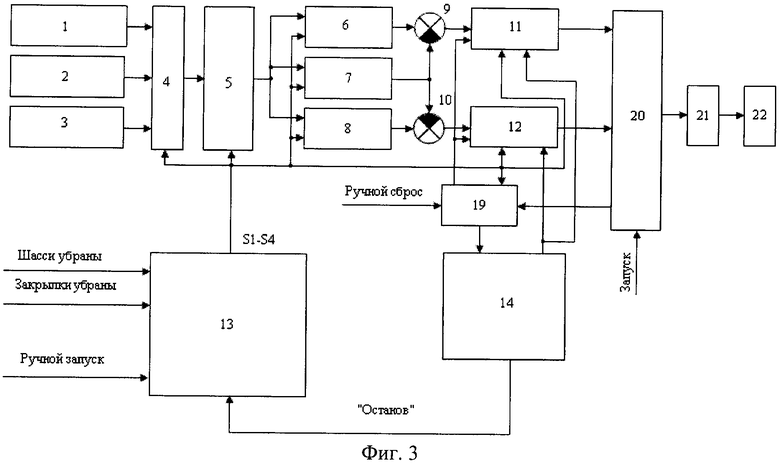

Система включает в себя три датчика вибраций 1, 2 и 3, коммутатор аналоговых сигналов 4 для подключения датчиков к аналогово-цифровому преобразователю, аналогово-цифровой преобразователь 5, три параллельных регистра 6, 7 и 8, два сумматора 9 и 10, два оперативных запоминающих устройства 11 и 12, устройство управления 13 и счетчик модификации адреса 14.

Датчики вибрации 1, 2 и 3 являются стандартными авиационными акселерометрами типа МП-95, применяемых в бортовых устройствах регистрации параметров полета типа Тестер У-3 и описаны в техническом описании этой системы и в литературе [1, 3].

Аналогово-цифровой преобразователь 4, регистры приема и передачи информации 6, 7, 8, сумматоры 9 и 10, запоминающие устройства 11 и 12 представляют собой серийные устройства и описаны в литературе [4].

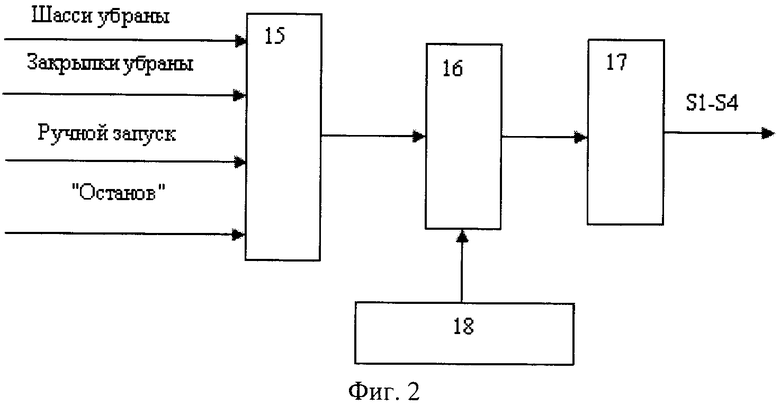

Устройство управления 13 представлено на фиг.2 и состоит из генератора прямоугольных импульсов 18, двухразрядного счетчика 16 со схемой управления 15 и дешифратора 17.

Коммутатор аналоговых сигналов 4 и генератор прямоугольных импульсов 18 - это типовые устройства, применяемые в микропроцессорной технике и, в частности, в бортовых устройствах регистрации типа Тестер У-3 [4, 5]. Прямоугольные импульсы генератора 18 непрерывно поступают на счетчик 16 с момента подачи питания в устройство. Схема управления 15 реализована на типовых логических элементах И-НЕ [4]. По мере поступления импульсов счетчик 16 циклически выдает повторяющуюся последовательность кодовых комбинаций: 00, 01, 10 и 11 с момента запуска устройства в работу комбинацией сигналов «Шасси убраны» и «Закрылки убраны» или сигналом «Ручной запуск». Остановка счетчика 16 осуществляется сигналом переполнения счетчика модификации адреса - сигналом "Останов". В зависимости от текущего значения кодовой комбинации на выходе счетчика 16 с выхода дешифратора 17 в АЦП 5 поступает один из сигналов управления S1-S4. Счетчик и дешифратор это также типовые изделия, применяющиеся в электронной технике [4, 5].

Счетчик модификации адреса 14 аналогичен счетчику 16 устройства управления и отличается только числом разрядов. Число разрядов счетчика модификации адреса 14 равно числу разрядов шины адресов запоминающих устройств 11 и 12.

Система для записи на борту показаний датчиков вибрации 1, 2, 3 работает только при наборе высоты и запускается в работу постоянными логическими сигналами "Шасси убраны", "Закрылки убраны". Система решает в цикле алгоритм и записывает результаты в запоминающие устройства 11 и 12 в дискретном виде с периодом Т. После заполнения запоминающих устройств 11, 12 проходит сигнал "Переполнение счетчика модификации адреса" и система останавливается. На земле происходит вычисление по приведенным в прототипе алгоритмам и определяется оценка Ωи1л и Ωи1п. Результаты оценки накапливаются по множеству в группе обслуживания средств объективного контроля для статистической оценки снижения жесткости крыла на изгиб в процессе эксплуатации. Перед полетом система приводится в готовность сигналом "Ручной сброс". Для проверки работоспособности на земле систему можно принудительно запустить в работу сигналом "Ручной запуск".

В прототипе предполагается, что после полета данные запоминающих устройств 11 и 12 переписываются для последующей обработки в наземной ЭВМ. Современные пассажирские и транспортные самолеты выполняют постоянные или чартерные рейсы с многочисленными посадками на промежуточных аэродромах. При посадках на промежуточных аэродромах невозможно переписать информацию о жесткости крыла базу данных аэродрома базирования. Поэтому недостатком изобретения является невозможность контроля жесткости крыла вне базового аэродрома.

Техническим результатом предлагаемого устройства является повышение достоверности контроля прочностных свойств крыла самолета вне базового аэродрома для предотвращения разрушения крыла в полете. Это достигается с помощью штатного оборудования самолета. В полете измеряется первый тон крыла для оценки жесткости на изгибные колебания и при достижении критического износа конструкции крыла обеспечивается предотвращение выпуска в полет самолета.

Технический результат достигается тем, что в устройство контроля прочности крыла воздушного судна, содержащее три датчика вибраций, коммутатор аналоговых сигналов, аналого-цифровой преобразователь, три параллельных регистра, два сумматора, два оперативных запоминающих устройства, счетчик модификации адреса и устройство управления, причем датчики вибраций через коммутатор соединены с первым входом аналого-цифрового преобразователя, выход которого непосредственно связан с первыми входами регистров, выход первого регистра связан с первым входом первого сумматора, выход третьего регистра - с первым входом второго сумматора, а выход второго регистра - со вторыми входами сумматоров, выходы которых подключены к первым входам запоминающих устройств, на вторые входы которых подключен счетчик модификации адреса, а на их третьи входы включен выход устройства управления, который одновременно подключен ко вторым входам регистров и аналого-цифрового преобразователя, а также к четвертому входу коммутатора, при этом три информационных входа устройства управления соединены с постоянными логическими элементами «Шасси убраны», «Закрылки убраны» и сигнала «Ручной запуск», а четвертый вход устройства управления соединен с выходом счетчика модификации адреса, дополнительно введены устройство управления счетчиком модификации адреса, микроЭВМ, блок буферных регистров и бортовое устройство регистрации параметров полета, причем на первый и второй входы микроЭВМ включены выходы запоминающих устройств, ее третий вход служит информационным входом команды «Запуск», а второй выход подключен ко второму входу устройства управления счетчиком модификации адреса, первый вход которого служит информационным входом команды «Ручной сброс», а третий вход соединен с третьими входами запоминающих устройств, чьи четвертые входы подключены к первому выходу устройства управления счетчиком модификации адреса, второй выход которого соединен со счетчиком модификации адреса.

Изложенная сущность изобретения поясняется чертежами, представленными на фиг.3 и на фиг.2, отображающей структуру устройства управления 13. На чертежах приняты следующие обозначения:

1, 2, 3 - датчики вибраций;

4 - коммутатор аналоговых сигналов;

5 - аналогово-цифровой преобразователь;

6, 7, 8 - три параллельных регистра;

9, 10 - два сумматора;

11, 12 - два оперативных запоминающих устройства;

13 - устройство управления;

14 - счетчик модификации адреса;

15 - схема управления;

16 - двухразрядный счетчик;

17 - дешифратор;

18 - генератор прямоугольных импульсов;

19 - устройство управления счетчиком модификации адреса;

20 - микроЭВМ;

21 - блок буферных регистров;

22 - бортовое устройство регистрации параметров полета.

Работа заявляемого устройства в полете не отличается от работы устройства-прототипа.

На земле по команде «Запуск» запускается программа в специализированной микроЭВМ 20.

После начала работы микроЭВМ 20 программно подает сигнал «Сброс» на устройство управления счетчиком модификации адреса 19. По этому сигналу происходит сброс счетчика модификации адреса 19 в начальное значение k=0.

По начальному адресу счетчика модификации адреса 19 запоминающие устройства 11 и 12 выбирают первое значение измеренных сигналов  и

и  .

.

Программно измеренные сигналы  и

и  одно за другим считываются в микроЭВМ 20 для обработки по алгоритмам, приведенным в формулах 1-13.

одно за другим считываются в микроЭВМ 20 для обработки по алгоритмам, приведенным в формулах 1-13.

Программно с микроЭВМ 20 подается сигнал S1, по заднему фронту которого происходит модификация адреса в счетчике 14 (код адреса увеличивается k=k+1).

Запоминающие устройства 11 и 12 выбирают значения измеренных сигналов  и

и  по адресу k=1.

по адресу k=1.

Программно измеренные сигналы  и

и  одно за другим считываются в микроЭВМ 20 для обработки по заданным алгоритмам (формулы 1-13).

одно за другим считываются в микроЭВМ 20 для обработки по заданным алгоритмам (формулы 1-13).

После этого цикл считывания повторяется до завершения обработки информации при k=N.

Значения частоты собственных колебаний Ωи1л и Ωи1п, вычисленные в микроЭВМ 20, записываются в блок буферных регистров 21.

Из блока буферных регистров 21 значения Ωи1л и Ωи1п записываются в бортовой регистратор 22 для накопления.

На земле накопленные значения Ωи1л и Ωи1п из бортового регистратора 22 переписываются в базу данных самолета, которая может быть реализована на наземных устройствах обработки полетной информации типа «Топаз».

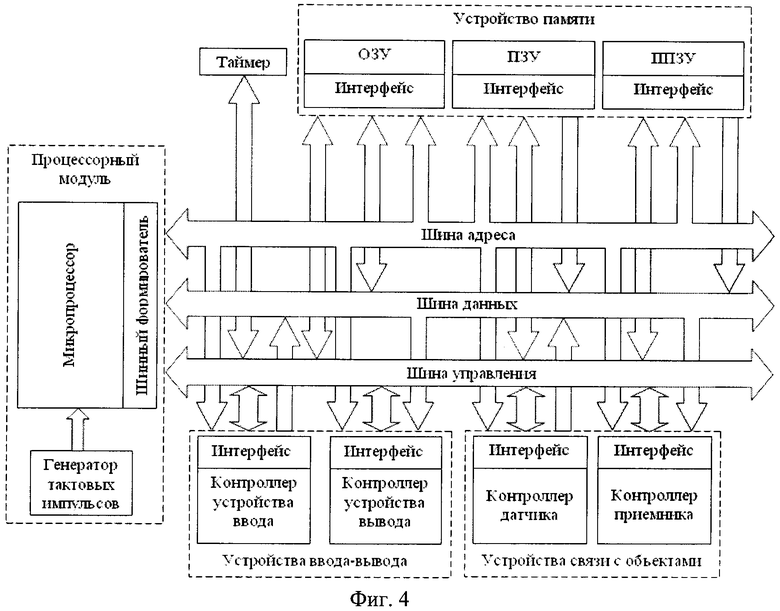

МикроЭВМ 20 может быть реализована на различной элементной базе. В качестве примера рассмотрим микроЭВМ на базе микропроцессорного комплекта интегральных схем серии КР580. Данная микроЭВМ строится по модульному принципу. Типовая принципиальная электрическая схема микропроцессорной системы на базе микросхем данной серии показана в [5]. Поскольку микроЭВМ 20 предназначена для выполнения только одной специализированной программы расчета, ее конструкцию можно упростить, исключив узлы прямого доступа в память и прерываний. Структурная схема микроЭВМ показана на фиг.4.

В состав комплекта модулей, необходимых для построения микроЭВМ, входят [6]:

- модуль центрального процессора;

- модуль памяти, предназначенный для хранения данных и программ;

- модуль ввода-вывода, осуществляющего сопряжение микроЭВМ с внешними устройствами.

Все модули соединяются с помощью единой системы шин: шины данных (ШД), шины адреса (ША) и шины управления (ШУ).

Шина данных представляет собой двунаправленную шину, с помощью которой осуществляется обмен данными.

Шина адреса является однонаправленной шиной и используется для передачи адресов.

Шина управления, объединяющая определенное количество линий передачи сигналов управления, представляет собой шину, сигналы которой определяют режимы работы памяти и внешнего устройства. Дополнительно шина управления может выполнять функции выдачи сигналов разрешения прерывания и приема запросов прерываний, приема сигнала захвата шин и выдачи сигнала подтверждения захвата шин при организации прямого доступа к памяти и др.

Модуль центрального процессора строится на основе микропроцессора. Для его работы необходимо дополнительно подключить внешние цепи формирования сигналов синхронизации и сигналов управления для сопряжения с системными шинами.

Схема синхронизации (генератор тактовых импульсов) обеспечивает формирование двух последовательностей тактовых импульсов с необходимыми временными и амплитудными параметрами, которые подаются на входы Ф1 и Ф2 микропроцессора, а также используются для стробирования внешних цепей;

формирования сигнала «СБРОС», синхронизации сигналов готовности и др. В качестве тактового генератора используется специальная микросхема, входящая в состав микропроцессорного комплекта интегральных схем.

Согласование внутренних шин микропроцессора с системными шинами микроЭВМ обеспечивается шинными формирователем, входящим в состав микропроцессорного комплекта (МПК). Это необходимо для устойчивой работы всей системы, поскольку подключение модулей памяти и внешних устройств увеличивает нагрузку на внутренние шины и может снизить необходимые для работы уровни сигнала.

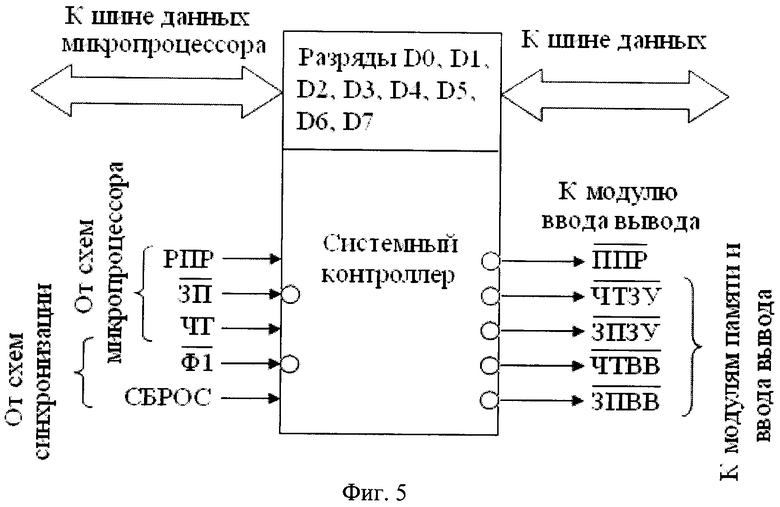

Формирование сигналов управления обеспечивается специальным системным контроллером, входящим в состав МПК (КР580ВК28 [5]). Системный контроллер формирует сигналы управления на основе байта состояния, выдаваемого микропроцессором на шину данных в первом такте машинных циклов, и сигналов ЗП и ЧТ микропроцессора. Схема формирования управляющих сигналов системным контроллером показана на фиг.5.

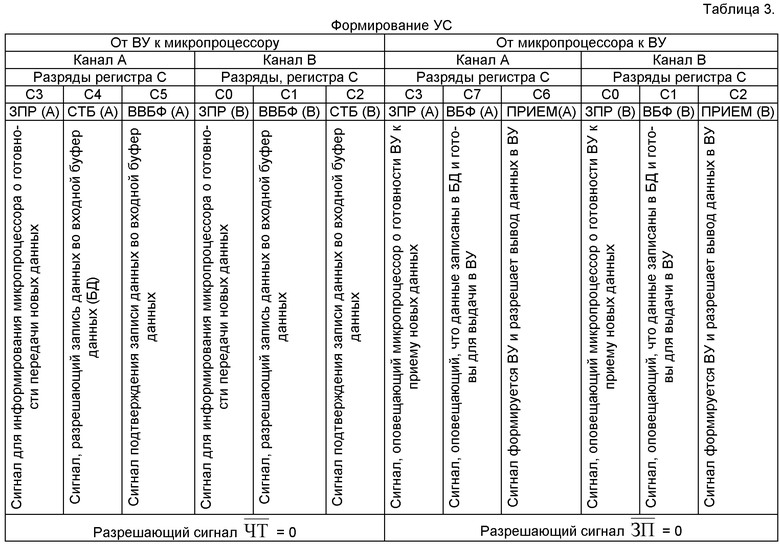

По сигналу РПР байт состояния с шины данных записывается в регистр состояния системного контроллера. Код на выходе регистра состояния дешифрируется и используется для формирования управляющих сигналов (табл.1).

Инверсные сигналы  ,

,  ,

,  и

и  , как видно из схемы, формируются на основе сигналов с микропроцессора и схемы синхронизации. В формировании этих сигналов используются также значения таких разрядов байта состояния как «ВВОД», «ВЫВОД», «ППР», «ЧТП» и «

, как видно из схемы, формируются на основе сигналов с микропроцессора и схемы синхронизации. В формировании этих сигналов используются также значения таких разрядов байта состояния как «ВВОД», «ВЫВОД», «ППР», «ЧТП» и « » (см. табл.1). Сигнал ППР предназначен для разрешения ввода команды прерывания RSTn с шины данных, поступающий с модуля ввода-вывода.

» (см. табл.1). Сигнал ППР предназначен для разрешения ввода команды прерывания RSTn с шины данных, поступающий с модуля ввода-вывода.

Модуль памяти состоит из постоянных запоминающих устройств (ПЗУ) и оперативных запоминающих устройств (ОЗУ), для которых в микроЭВМ используется единое пространство адресов, разделенное на область адресов обращения к ПЗУ и область адресов обращения к ОЗУ.

Для построения модуля памяти используются микросхемы, не входящие в состав микропроцессорного комплекта интегральных схем, но имеющие общие с ним параметры входных и выходных сигналов.

Модуль ввода-вывода включает в себя группу портов ввода-вывода, представляющих собой либо регистры с логическими схемами управления, либо специальные интерфейсные устройства ввода-вывода в виде БИС, содержащих внутренние порты ввода-вывода. Каждое внешнее устройство подключается к одному или нескольким портам, и выборка внешнего устройства осуществляется путем выборки соответствующих портов.

С точки зрения центрального процессора память и порты ввода-вывода можно рассматривать как совокупность запоминающих ячеек с произвольным доступом. Микропроцессор выдает адрес памяти и порта ввода-вывода (ВВ) на общую шину адреса. Разделение адресов памяти и портов ввода-вывода в микроЭВМ может осуществляться двумя способами.

= 0 указывает, что выполняются циклы ЗАПИСЬ В ПАМЯТЬ или ВЫВОД

= 0 указывает, что выполняются циклы ЗАПИСЬ В ПАМЯТЬ или ВЫВОД = 1 указывает на выполнение циклов ЧТЕНИЕ ПАМЯТИ или ВВОД

= 1 указывает на выполнение циклов ЧТЕНИЕ ПАМЯТИ или ВВОД

Первый способ состоит в раздельной адресации памяти и портов. Область адресов памяти в этом случае максимальная и определяется разрядностью адресного слова. При адресном слове, равном двум байтам (16 разрядов), объем адресуемой памяти составляет 64 кбайт. При раздельной адресации адресное слово в командах ввода-вывода составляет один байт (8 разрядов). В этом случае количество адресуемых портов ввода-вывода равно 256. Применение первого способа позволяет сохранить полный объем памяти, равный 64 кбайтам, но для обращения к внешним устройствам необходимо использовать только команды ввода-вывода IN port и OUT port. Полностью система команд микроЭВМ приведена в [6].

Второй способ заключается в использовании общего поля адресации памяти и портов ВВ. Это позволяет повысить гибкость и производительность системы, но при этом сокращается адресуемое пространство памяти.

Разделения адресов к памяти и к портам ВВ осуществляется установкой в 0 или 1 разряда А15 на шине адреса и осуществляется сигналами чтения и записи. Кроме того, формируются раздельные сигналы чтения и записи содержимого ячеек памяти портов ввода-вывода. В этом случае порты ВВ рассматриваются как ячейки памяти в общем поле адресов. Если в разряде адреса A15=0, то адресуется память, если А15=1, то адресуется внешнее устройство. При таком способе адресации с общим полем адресов объем адресуемой памяти и портов ВВ составляет 32 кбайта каждый. Для адресации к памяти используется область адресов 0000-7FFF, а для адресации к портам - 1000-FFFF. Особенностью такого способа является возможность использования всех команд обращения к памяти для работы, с внешними устройствами.

Например, по команде MOV r, М можно ввести содержимое порта, косвенно адресуемого регистровой парой HL, в любой регистр микропроцессора. Если же используется команда IN port, то содержимое порта можно ввести только в регистр-аккумулятор А с последующей пересылкой командой MOV r1, r2 из регистра А в любой другой регистр.

Используя команду MVI М, data8, можно непосредственно записать данные в любой косвенно адресуемый порт.

По ряду соображений второй способ предпочтительнее. Так, например, при общей адресации имеется возможность выполнения арифметических и логических операций, над содержимым портов ВВ и аккумулятора, если при этом используются команды с косвенной адресацией к памяти. Например, при раздельной адресации для сложения содержимого порта и аккумулятора необходимо первоначально сохранить содержимое аккумулятора в каком-нибудь регистре (команда МОУ г, А), затем занести содержимое порта в аккумулятор (IN port) и выполнить команду сложения ADD г. При использовании общего поля адресации эту операцию можно выполнить командой ADD М.

В состав модуля ввода-вывода также включены:

- различные схемы интерфейсов для сопряжения с внешними устройствами, обмен информацией с которыми осуществляется в параллельном или последовательном коде; в МПК для этих целей используются специальные БИС программируемых параллельных и последовательных интерфейсов;

- БИС программируемого контроллера прерываний для приема и обработки запросов прерывании от внешних устройств и выработки сигнала приоритетного запроса (ЗПР), поступающего на вход микропроцессора;

- БИС программируемого таймера для прерываний по времени;

- БИС программируемого контроллера прямого доступа к памяти для организации обмена данными между оперативной памятью и внешним устройством.

В составе микроЭВМ предлагаемого устройства должно быть два модуля программируемых параллельных интерфейсов КР580ВВ55А [6]. Один для подключения запоминающих устройств 11 и 12, второй для подключения блока буферных регистров 21.

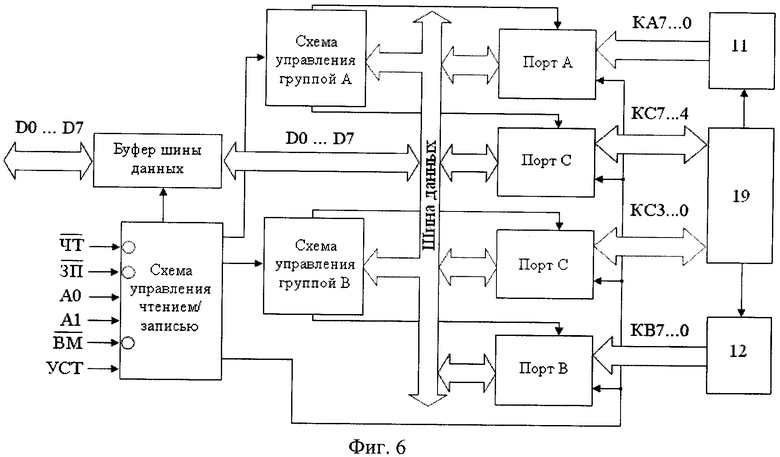

Структура соединения программируемого параллельного интерфейса с запоминающими устройствами 11 и 12 приведена на фиг.6.

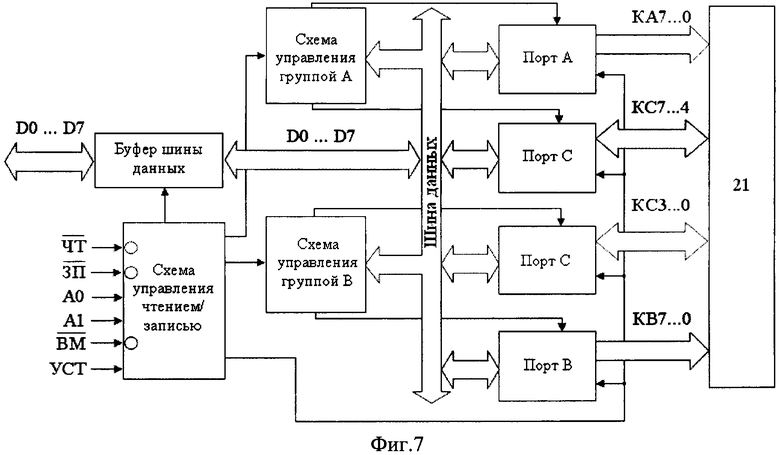

Структура соединения программируемого параллельного интерфейса с блоком буферных регистров 21 приведена на фиг.7.

Программируемый параллельный интерфейс представляет собой многофункциональное устройство и применяется для двунаправленной передачи данных и сигналов управления между центральным процессором и внешними устройствами. Информация о готовности внешних устройств к обмену данными поступает в процессор, как правило, по сигналам прерывания. При обмене данными процессор может обращаться к внешним устройствам как к ячейкам памяти или как к устройствам ввода-вывода (УВВ).

Программируемый параллельный интерфейс состоит из трех каналов обмена А, В и С, представляющих собой 8-разрядные порты ВВ с различными характеристиками. Направление обмена и режим работы каждого канала задаются программным путем. Каналы служат для передачи данных и управляющих сигналов. Упрощенно схему устройства можно рассматривать как совокупность регистров: регистра управления и трех регистров, предназначенных для ввода-вывода данных.

Схема на фиг.6 и 7 включает в себя следующие функциональные узлы:

- буфер шины данных (БФД);

- узел управления чтением-записью;

- порты В-В А, В и С.

Буфер шины, данных (БФД) предназначен для подключения внутренней шины данных к системной шине. Подключение осуществляется с помощью выводов D7, D6, D5, D4, D3, D2, D1, D0. Передача информации через БФД осуществляется по командам микропроцессора. При этом может передаваться информация трех видов: байты данных, управляющие слова и информация состояния.

Схема управления чтением-записью осуществляет управление всеми внутренними и внешними пересылками данных, управляющих слов и слов состояния. Управление происходит под воздействием сигналов, которые поступают на выводы управления и адресации схемы:

- вход, на который поступает сигнал низкого уровня выборки устройства; формируется на выходе системного дешифратора, при дешифрации разрядов А15-А2 адреса;

- вход, на который поступает сигнал низкого уровня выборки устройства; формируется на выходе системного дешифратора, при дешифрации разрядов А15-А2 адреса;

- вход сигнала низкого уровня, разрешающего передачу данных или слова состояния на системную шину данных;

- вход сигнала низкого уровня, разрешающего передачу данных или слова состояния на системную шину данных;

- вход сигнала записи низкого уровня, разрешающего прием данных или управляющего слова с системной шины данных;

- вход сигнала записи низкого уровня, разрешающего прием данных или управляющего слова с системной шины данных;

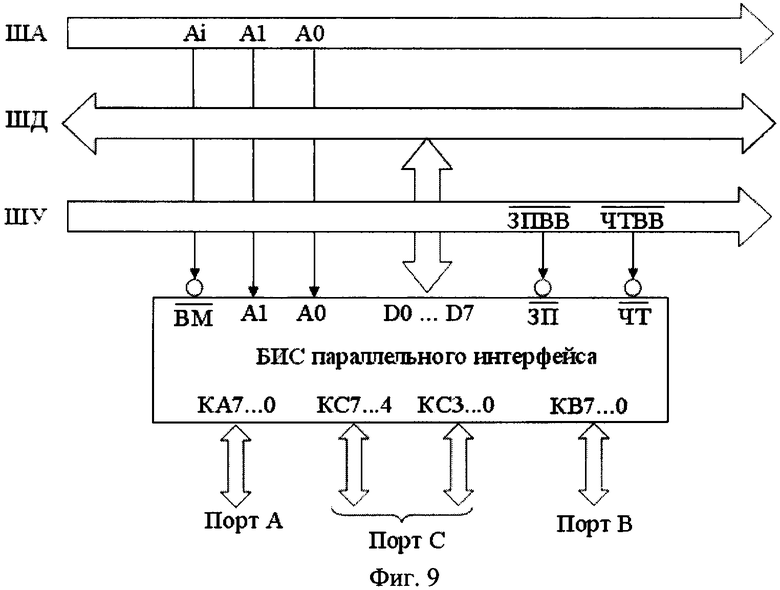

А0, А1 - входы сигналов выбора одного из портов В-В (А, В или С) или регистра управляющего слова и подключается к младшим разрядам адресной шины;

УСТ - вход сигнала сброса, устанавливающего все внутренние регистры в нуль; при этом все порты переходят в режим ввода.

Если процессор обращается к портам В-В как к внешним устройствам, входы  и

и  подключаются к линиям

подключаются к линиям  и

и  системной шины управления. При обращении к портам как ячейкам памяти входы должны соответственно быть подключены к линиям

системной шины управления. При обращении к портам как ячейкам памяти входы должны соответственно быть подключены к линиям  и

и  системной шины управления микроЭВМ.

системной шины управления микроЭВМ.

Вид обмена информацией между шиной данных и портами В-В в зависимости от значений указанных сигналов приведен в табл.2.

Схемы управления группами шин А и В предназначены для приема и хранения управляющего слова и задания режима работы портов В-В устройства.

Схема управления группой А задает режим работы порта А и старших разрядов порта С, а схема управления группой В - режим работы порта В и младших разрядов порта С. В состав схемы входит регистр управляющего слова, предназначенный для приема и хранения управляющего слова, поступающего через буфер шины данных и внутреннюю шину.

Порты В-В предназначены для подключения внешних устройств ВВ. Подключение осуществляется с помощью выводов соответствующих каналов: для канала А используются выводы КА7…КА0; для канала В - выводы КВ7…КВ0; для канала С - выводы КС7…КС0.

Порт А включает 8-разрядные входной и выходной регистры для ввода и вывода данных во всех режимах работы схемы.

Порт В состоит из одного 8-разрядного регистра, используемого для ввода и вывода данных в двух из трех возможных режимах работы схемы.

Порт С состоит из двух 4-разрядных регистров, которые могут использоваться для ввода и вывода 4-разрядных данных или для приема и выдачи управляющих сигналов обмена. В регистре С формируется слово состояния схемы.

Режимы работы портов задаются при начальной установке путем записи управляющего слова в регистр управляющего слова. При этом порты А, В и С устанавливаются в один из трех режимов работы: режим 0, режим 1 и режим 2.

Режимы работы можно устанавливать в любом месте выполнения программы, что позволяет обслуживать различные внешние устройства одним интерфейсом в произвольном порядке.

В режиме 0 осуществляется асинхронный обмен данными по двум 8-разрядным каналам А и В и по двум 4-разрядным подканалам С без управляющих сигналов о готовности к работе внешних устройств и без подтверждения возможности обмена. Это означает, что данные, выводимые из микропроцессора по командам вывода, фиксируются в соответствующих регистрах каналов, а затем по линиям связи передаются во внешние устройства.

Данные хранятся в регистрах до конца выполнения команды вывода, после чего информация в портах обновляется. При вводе данные считываются из портов и заносятся в регистр - аккумулятор микропроцессора по командам ввода. Режим 0 обычно используется для ввода медленно меняющихся данных. При выводе в этом режиме можно программно формировать сигналы управления (байты управления) внешними устройствами.

В режиме 1 осуществляется асинхронный обмен данными по каналам А и В с помощью сигналов управления, передаваемых по каналу С. В этом режиме может быть организован асинхронный обмен данными со стробированием и квитированием. Стробирование обеспечивает синхронизацию передаваемых данных и повышение надежности установки сигналов на линиях связи.

Квитирование позволяет обеспечить согласование работы внешних устройств и микропроцессора. При квитировании очередной байт данных передается только тогда, когда получено подтверждение о считывании предыдущего.

Ввод информации в буфер данных канала осуществляется при получении стробирующего сигнала  от внешнего устройства. Канал в свою очередь формирует сигнал ВВБФ, который поддерживается в течение всего интервала времени от записи данных до их чтения микропроцессором. Для информирования микропроцессора о готовности данных для ввода используется выходной сигнал

от внешнего устройства. Канал в свою очередь формирует сигнал ВВБФ, который поддерживается в течение всего интервала времени от записи данных до их чтения микропроцессором. Для информирования микропроцессора о готовности данных для ввода используется выходной сигнал  .

.

Данные в канал записываются с помощью импульса записи с системной шины, подаваемого на вход  . В момент окончания записи данных формируется выходной управляющий сигнал

. В момент окончания записи данных формируется выходной управляющий сигнал  , который указывает на готовность данных для выдачи в ВУ.

, который указывает на готовность данных для выдачи в ВУ.

Вывод информации из буфера канала и ввод ее в ВУ происходит по сигналу «ПРИЕМ», выдаваемому с внешнего устройства, а сигнал  используется для информирования микропроцессора о готовности канала к выводу новых данных (табл.3).

используется для информирования микропроцессора о готовности канала к выводу новых данных (табл.3).

Режим 2 используется только для организации двунаправленной передачи данных в канале А. При этом разряды регистра С (С3, С4, С5, С6 и С7) по-прежнему предназначены для формирования и приема управляющих сигналов, аналогичных сигналам режима 1 (см. табл.3). Канал В при этом может работать только в режимах 0 и 1 (С0, С1 и С2).

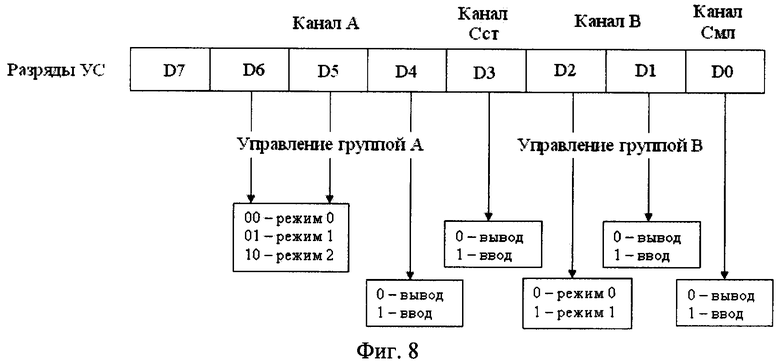

Комбинации режимов для каналов задаются программным путем при начальной установке. Программирование состоит в настройке на требуемый режим обмена и непосредственный обмен данными при помощи двух команд ввода-вывода микропроцессора IN и OUT. При программировании в регистр управления (адрес А1А0=11) командой OUT записывается управляющее слово УС, разряды которого определяют режим работы для каждого канала (0, 1 или 2) и направление обмена.

Управляющее слово формируется в микропроцессоре как 8-разрядное слово и содержится в аккумуляторе. Формат управляющего слова показан на фиг 8.

В качестве примера рассмотрим, как установить режимы работы и направления обмена в каналах А, В и С. Пусть, например, необходимо организовать ввод данных по каналу А и вывод данных по каналам В и С в режиме 0. Для этого в микропроцессоре должно быть сформировано УС следующего содержания: 10010000.

Это управляющее слово командой OUT xxxxxx 11 записывается в регистр управления, где два младших разряда адреса порта 11 указывают, что запись содержимого аккумулятора (УС) должна быть произведена именно в регистр управления. Остальные разряды адреса порта используются для адресации к БИС путем формирования сигнала ВМ

Команды ввода-вывода данных для каналов А, В и С имеют следующий вид:

IN xxxxxx 00 (чтение байта данных из канала А и ввод его в аккумулятор);

OUT xxxxxx 01 (вывод данных из аккумулятора процессора и запись в канал В);

OUT xxxxxx 10 (вывод данных из аккумулятора процессора и запись в канал С).

Схема подключения программируемого интерфейса КР580ВВ55А к системным шинам микроЭВМ приведена на фиг.9.

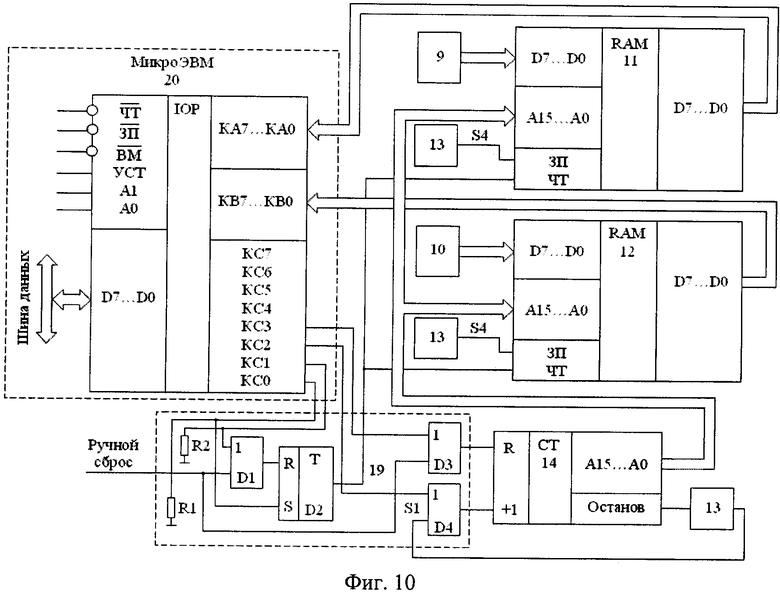

Функциональная схема устройства управления счетчиком модификации адреса 19 и его взаимосвязь с другими блоками показана на фиг.10.

В полете информация на входы DO-D7 запоминающих устройств RAM 11 и RAM 12 поступает с сумматоров 9 и 10 соответственно. Запись информации осуществляется по заднему фронту сигнала S4, поступающего из блока управления 13.

Адрес записи в запоминающие устройства RAM 11 и RAM 12 формируется счетчиком модификации адреса 14. В полет модификация адреса осуществляется по сигналу S1, поступающему из блока управления 13 через инвертор D4 2хИЛИ в блоке управления счетчиком модификации адреса 19.

При переполнении счетчика модификации адреса на его выходе формируется сигнал «Останов», поступающий на вход блока управления 13.

На земле сброс счетчика модификации адреса 14 осуществляется сигналом от кнопки «Ручной сброс», поступающим через инвертор D3 2хИЛИ в блоке управления счетчиком модификации адреса 19.

Ввод информации из запоминающих устройств RAM 11 и RAM 12 осуществляется системным контроллером IOP, входящим в состав микроЭВМ 20. Системный контроллер IOP реализован на микросхеме КР580ВК28, работа которой была описана выше.

Информационный выход D0-D7 запоминающего устройства RAM 11 заведен на порт А контроллера IOP, запоминающего устройства RAM 12 на порт В соответственно (см. фиг.10).

Считывание данных из запоминающих устройств RAM 11 и RAM 12 осуществляется в режиме 0. Выбор этого режима обусловлен тем, что микроЭВМ решает только одну специализированную задачу. Поэтому от нее не требуется ни производительности, ни мультизадачности.

Управление блоком 19 осуществляется сигналами, поступающими из порта С контроллера IOP. Перечень команд приведен в табл.4.

Цикл считывания информации состоит из следующих операций:

1. Перед началом вычислений Ωи1л и Ωи1п на порт С выводится команда «Сброс счетчика модификации адреса 14». По этой команде «1» из разряда КС3 порта С поступает на инвертор D3 2хИЛИ блока 19 и далее на вход R 16-разрядного счетчика модификации адреса 14. Разряды А15-А0 счетчика сбрасываются в 0.

2. На порт С выводится команда «Сброс сигнала ЧТ на выходе RS триггера D2». По этой команде «1» из разряда КС1 порта С поступает на инвертор D1 2хИЛИ и далее на вход R RS триггера D2 блока 19. RS триггер D2 устанавливает сигнал ЧТ = 0. По этой команде запоминающие устройства RAM 11 и RAM 12 переводятся в режим готовности к выборке по новому адресу.

3. На порт С выводится команда «Установка сигнала ЧТ на выходе RS триггера D2». По этой команде «1» из разряда КС0 порта С поступает на вход S RS триггера D2 блока 19. RS триггер D2 устанавливает сигнал ЧТ = 1. По этой команде запоминающие устройства RAM 11 и RAM 12 осуществляют выборку данных по модифицированному адресу.

4. МикроЭВМ 20 асинхронно считывает данные из запоминающего устройства RAM 11 через порт А.

5. МикроЭВМ 20 асинхронно считывает данные из запоминающего устройства RAM 12 через порт В.

6. МикроЭВМ 20 выполняет операции по вычислению Ωи1л и Ωи1п.

7. На порт С выводится команда «Модификация адреса». По этой команде «1» из разряда КС2 порта С поступает на инвертор D4 2хИЛИ и далее на вход +1 счетчика модификации адреса 14. 16-разрядный адрес А15-А0 счетчика увеличивается на единицу и поступает на адресные входы запоминающих устройств RAM 11 и RAM 12.

После этого операции 2-7 повторяются в цикле до заполнения счетчика модификации адреса 14. Количество считанных данных определяется программно, поэтому сигнал «Останов» в микроЭВМ 20 не заводится.

Резисторы R1 и R2 блока 19 предназначены для ввода «0» на входы RS триггера при установке разрядов КС0 и КС1 в состояние высокого уровня импеданса.

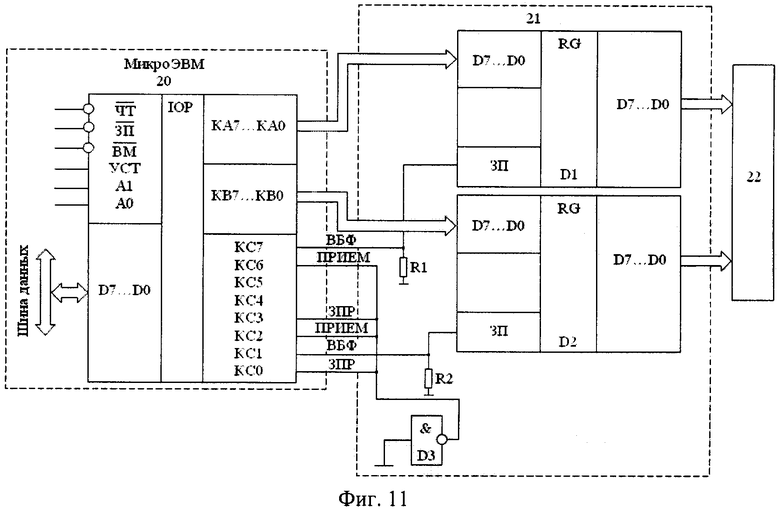

Функциональная схема блока буферных регистров 21 и его взаимосвязь с микроЭВМ 20 и бортовым устройством регистрации параметров полета 22 показана на фиг.11.

Вывод информации в блок буферных регистров 21 осуществляется системным контроллером IOP, входящим в состав микроЭВМ 20. Данный системный контроллер IOP, как и системный контроллер IOP для ввода информации из запоминающих устройств RAM 11 и RAM 12 на фиг.10, реализован на микросхеме КР580ВК28.

Контроллер IOP для вывода результатов вычисления Ωи1л и Ωи1п в блок буферных регистров 21 работает в режиме 1.

Инвертор D3 блока 21 предназначен для ввода микроЭВМ сигналов ЗПР = 1 и ПРИЕМ = 1 по каналам А и В (см. табл.3).

Результат вычисления Ωи1п из порта А контроллера IOP микроЭВМ 20 заносится в разряды D0-D7 регистра D1. Запись осуществляется сигналом ВБР, поступающим с КС7 порта С (см. табл.3).

Результат вычисления Ωи1п из порта В контроллера IOP микроЭВМ 20 заносится в разряды D0-D7 регистра D2. Запись осуществляется сигналом ВБР, поступающим с КС1 порта С (см. табл.3).

Резисторы R1 и R2 блока 21 предназначены для ввода «0» на входы ЗП регистров D1 и D2 при установке разрядов КС1 и КС7 в состояние высокого уровня импеданса.

Выходы D0-D7 регистров D1 и D2 поступают для записи в бортовое устройство регистрации.

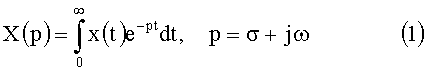

Рассмотрим алгоритм вычисления Ωи1л и Ωи1п.

К недостатку алгоритма прототипа, а именно определения частоты собственных колебаний крыла воздушного судна (первого тона) следует отнести необходимость использования операций двойного интегрирования. При наличии постоянной ошибки в сигнале акселератора такая процедура приводит к появлению неконтролируемой ошибки в расчетном сигнале после проведения операций двойного интегрирования. Кроме того, для получения численного значения частоты собственных изгибных колебаний по первому тону необходимо осуществить спектральное разложение сигналов акселерометров. Для такого разложения наибольшее применение нашли интегральные преобразования Фурье и Лапласа.

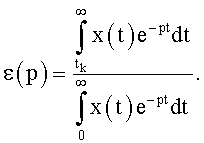

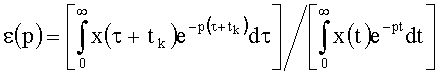

Существенная трудность, связанная с численным применением интегральных преобразований, вызвана бесконечными пределами. При практическом вычислении преобразования Фурье обычно применяют временные или спектральные окна, которые, в свою очередь, могут значительно исказить исходный спектр. Для преобразования Лапласа можно воспользоваться процедурой усечения бесконечных пределов [7]. В этом случае также встает вопрос об искажении спектра. Для преобразования

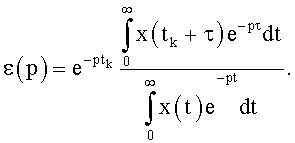

относительная погрешность, связанная с ограничением верхнего предела величиной tk, имеет вид:

После замены переменной τ=t-tk имеем

,

,

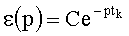

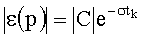

Значение ε(р) представляет собой для некоторого сигнала x(t) постоянную величину, модуль которой зависит от вида сигнала. Таким образом, относительную ошибку можно представить в виде:  , а ее модуль

, а ее модуль  .

.

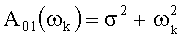

Итак, для нерасходящегося процесса при |C|≤1 и σ=α/tk величина относительной ошибки не превышает величины е-α. Поэтому за счет указанного выбора действительной части σ комплексной переменной р можно добиться малости ошибки ограничения интегрального преобразования.

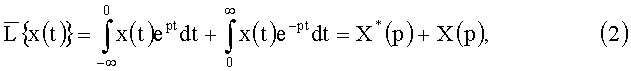

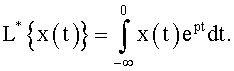

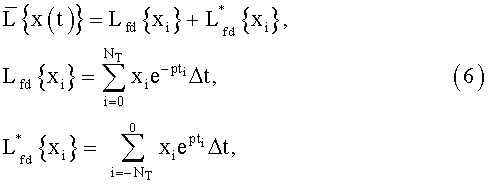

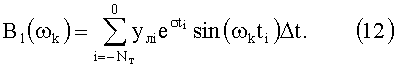

Для исключения из алгоритма операции двойного интегрирования воспользуемся «симметричным преобразованием Лапласа» [8]:

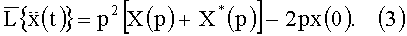

К практически значимому свойству такого преобразования относится:

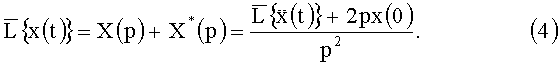

Соотношение (3) позволяет получить искомую энергетическую характеристику процесса x(t), по регистрируемым значениям второй производной  :

:

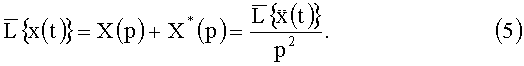

Соотношение (4) можно упростить, выбрав начало отсчета t=0, так чтобы х(0)=0.

В результате получим окончательно:

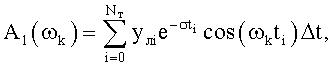

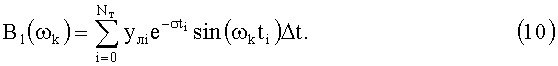

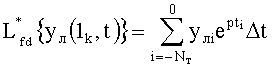

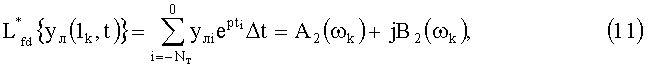

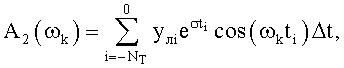

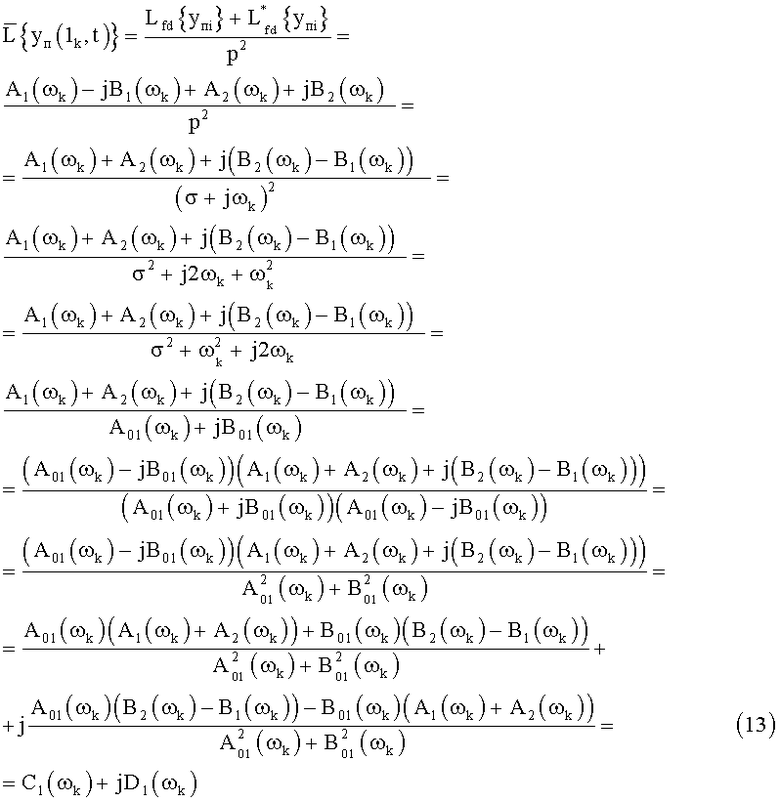

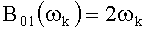

С учетом дискретизации и финитности приближенные расчетные соотношения для изображения (2) имеют вид:

где i - номер дискретного момента времени; NT+1 - число малых отрезков дискретизации отрезков [-Т, 0], [0, Т].

Заметим, что в соотношениях (6) p=σ+jωк, где ωк - расчетное значение частоты.

Выбор достаточно малого шага дискретизации при вычислении изображений аналогичен выбору шага интегрирования дифференциальных уравнений динамической модели исследуемой системы при моделировании переходных процессов и определяется верхней частотой учитываемых гармонических составляющих.

Частоты гармонических составляющих спектральных представлений переходных процессов задаются величиной коэффициента ω мнимой части комплексной переменной р. Поэтому, накладывая ограничение на ω, в зависимости от величины Δt обеспечивается требуемая степень малости ошибки дискретизации при вычислении изображений.

С достаточной для практических расчетов точностью и при применении линейной интерполяции процессов это ограничение имеет вид (ω/2p)<(5-6)fp, где fp=1/Δt - частота регистрационных процессов.

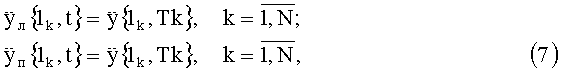

Применительно к записям сигналов акселерометров:

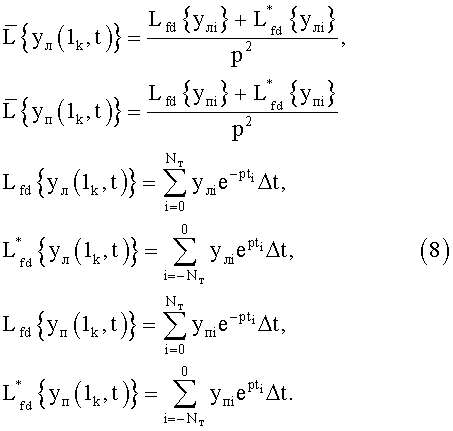

соотношение (5) с учетом (6) примет следующий вид:

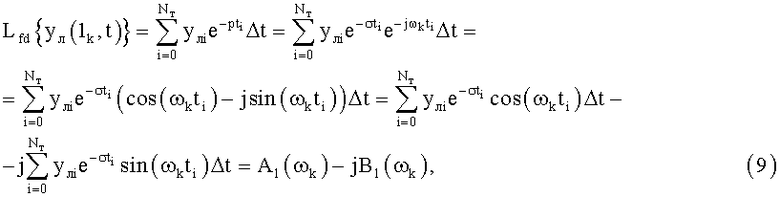

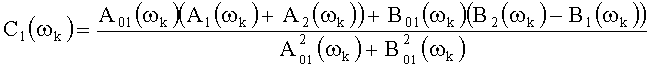

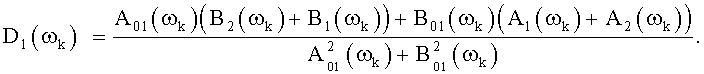

Соотношения (8) являются комплексными. Для упрощения алгоритма расчета искомых энергетических характеристик выполним ряд преобразований. Указанные преобразования рассмотрим применительно к сигналу левого акселерометра  .

.

где

Аналогично, для  имеем:

имеем:

где

Заметим, что соотношения (9)-(12) получены для конкретного значения частоты ωk.

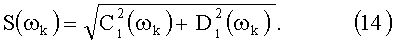

С учетом полученных соотношений (9), (11) спектральная характеристика для «правого акселерометра» примет вид:

где  ,

,  ,

,

,

,

Значение спектральной характеристики для частоты ωk примет вид:

Для получения спектральной характеристики во всем интересующем нас диапазоне от 0 до 10 Гц необходимо циклически повести счисления по соотношениям (9)-(14) с заданным шагом по частоте.

Поиск частоты собственных колебаний целесообразно проводить методом прямого перебора, с учетом малого количества точек спектральной характеристики и наличия априори одного экстремума, соответствующего частоте собственных колебаний.

Аналогично определяется спектральная характеристика для сигнала «левого» акселерометра.

Таким образом предлагаемое устройство исключает недостатки прототипа, а именно невозможность контроля жесткости крыла вне базового аэродрома, что позволит повысить достоверность контроля прочностных свойств крыла воздушного судна и предотвращения разрушения крыла в полете.

Кроме этого, исключены недостатки алгоритма прототипа, который предусматривал необходимость использования операции двойного интегрирования и появления неконтролируемой ошибки в расчетном сигнале.

Для исключения из алгоритма операции двойного интегрирования предлагается «симметричное преобразование Лапласа», представленное формулами (1-13).

Источники информации

1. Воробьев В.Г. и др. Авиационные приборы, информационно-измерительные системы и комплексы. Учебник для вузов / В.Г.Воробьев и др. - М.: Транспорт, 1992. - С.104-108.

2. Система контроля прочностных свойств крыла ЛА. Кашковский В.В., Устинов В.В. Полуэктов С.П. Желтухин С.Н. Патент РФ №2348916, МПК G01N 3/02, G01M 7/02, 2009.

3. Авиационные приборы. Под ред. С.С.Дорофеева. - М.: Военное издательство, 1992. - С.373-405.

4. Стрыгин В.В.и др. Основы вычислительной, микропроцессорной техники и программирования. Учебник для учащихся техникумов. / В.В.Стрыгин и др. - М.: Высшая школа, 1989. - С.225, 92, 108, 149, 74, 98, 103.

5. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник. Под ред. В.А.Шахнова. - М.: Радио и связь, 1988. - Т.1. - 368 с.

6. Половов P.M. и др. Бортовые вычислительные устройства и машины. Учебное пособие. Часть II. / Р.М.Половов и др. - М.: МГТУ ГА, 2004. - 96 с.

7. Качанов Б.О. Изображение по Лапласу случайных процессов и непараметрическая идентификация непрерывных систем // Автоматика и телемеханика. №1, 2004, с.74-81.

8. Качанов Б.О. Симметричное и кососимметричное преобразования Лапласа для задач идентификации. - В сб. Математическое обеспечение задач управления, оценивания и идентификации летательных аппаратов и их систем. Научно-методические материалы. - М.: ВВИА им. Н.Е.Жуковского, 1996.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕКСНАЯ СИСТЕМА ИНФОРМАЦИИ И КОНТРОЛЯ СОСТОЯНИЯ АВИАЦИОННОЙ ТЕХНИКИ | 2011 |

|

RU2474867C1 |

| СИСТЕМА КОНТРОЛЯ ПРОЧНОСТНЫХ СВОЙСТВ КРЫЛА ЛЕТАТЕЛЬНОГО АППАРАТА | 2007 |

|

RU2348916C1 |

| Устройство для вычисления логических функций | 1986 |

|

SU1367011A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

Изобретение относится к устройствам для исследования прочностных свойств конструкций, в частности крыла воздушного судна, и может быть использовано для контроля его прочности путем замера вибраций консоли крыла непосредственно в полете. В предлагаемое устройство контроля прочности крыла воздушного судна, содержащее три датчика вибраций, установленных в центре масс и на консолях левой и правой плоскостей крыла, коммутатор аналоговых сигналов, аналогово-цифровой преобразователь, три параллельных регистра, два сумматора, два оперативных запоминающих устройства, счетчик модификации адреса и устройство управления, согласно изобретению дополнительно введены устройство управления счетчиком модификации адреса, микроЭВМ, блок буферных регистров и бортовое устройство регистрации параметров полета. При этом на первый и второй входы микроЭВМ включены выходы запоминающих устройств, ее третий вход служит информационным входом команды «Запуск», а второй выход подключен ко второму входу устройства управления счетчиком модификации адреса, первый вход которого служит информационным входом команды «Ручной сброс», третий вход его соединен с третьими входами запоминающих устройств, чьи четвертые входы подключены к первому выходу устройства управления счетчиком модификации адреса, второй выход которого соединен со счетчиком модификации адреса. Технический результат - повышение достоверности контроля прочностных свойств крыла самолета вне базового аэродрома для предотвращения разрушения крыла в полете. 11 ил.

Устройство контроля прочности крыла воздушного судна, содержащее три датчика вибраций, коммутатор аналоговых сигналов, аналого-цифровой преобразователь, три параллельных регистра, два сумматора, два оперативных запоминающих устройства, счетчик модификации адреса и устройство управления, причем датчики вибраций через коммутатор соединены с первым входом аналого-цифрового преобразователя, выход которого непосредственно связан с первыми входами регистров, выход первого регистра связан с первым входом первого сумматора, выход третьего регистра - с первым входом второго сумматора, а выход второго регистра - со вторыми входами сумматоров, выходы которых подключены к первым входам запоминающих устройств, на вторые входы которых подключен счетчик модификации адреса, а на их третьи входы включен выход устройства управления, который одновременно подключен ко вторым входам регистров и аналого-цифрового преобразователя, а также к четвертому входу коммутатора, при этом три информационных входа устройства управления соединены с постоянными логическими элементами «Шасси убраны», «Закрылки убраны» и сигнала «Ручной запуск», а четвертый вход устройства управления соединен с выходом счетчика модификации адреса, отличающееся тем, что в него дополнительно введены устройство управления счетчиком модификации адреса, микроЭВМ с последовательно соединенными с ее выходом блоком буферных регистров и бортовым устройством регистрации параметров полета, при этом на первый и второй входы микроЭВМ включены выходы запоминающих устройств, ее третий вход служит информационным входом команды «Запуск», а второй выход подключен ко второму входу устройства управления счетчиком модификации адреса, первый вход которого служит информационным входом команды «Ручной сброс», третий вход его соединен с третьими входами запоминающих устройств, чьи четвертые входы подключены к первому выходу устройства управления счетчиком модификации адреса, второй выход которого соединен со счетчиком модификации адреса.

| СИСТЕМА КОНТРОЛЯ ПРОЧНОСТНЫХ СВОЙСТВ КРЫЛА ЛЕТАТЕЛЬНОГО АППАРАТА | 2007 |

|

RU2348916C1 |

| СПОСОБ И УСТРОЙСТВО КОНТРОЛЯ СОСТОЯНИЯ КОНСТРУКЦИИ САМОЛЕТА | 2006 |

|

RU2385456C2 |

| СИСТЕМА И СПОСОБ ДЛЯ ОБНАРУЖЕНИЯ И ИЗМЕРЕНИЯ РАСПРОСТРАНЕНИЯ ДЕФЕКТОВ В ДЕТАЛИ ИЛИ КОНСТРУКЦИИ | 2001 |

|

RU2263888C2 |

| US 20100307223 A1, 09.12.2010. | |||

Авторы

Даты

2012-12-10—Публикация

2011-07-13—Подача