Zspunno ffxoaoff

OOffM

fffe/x

(Л

.1

ycTpoficTBo Д.Г1Я контроля цифровых систем содержит блок 1 формирования сЩ ресов, блок 2 памяти микрокома Щ5 блок 3 логической обработки, блок 4 служебных рс гистров, блок 5 кодирования, блок

6 оперативной памяти, блок 7 управления и обработки, включаю- щи контроллер 7.1 памяти блок 9 ин- дршации, клавиатуру 10, блок 8 памяти команд. 1 з,п. ф-льц 15 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Доменное запоминающее устройство | 1986 |

|

SU1336105A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

Изобретение относится к контролю и диагностике цифровых систем и может быть использовано в качестве программного анализатора логических состояний при разработке, наладке, контроле работоспособности и техническом обслуживании сложных цифровых устройств и систем, в том числе систем, построенных на базе микроЭВМ. Цель изобретения - повышение быстродействия устройства. Программируемое

Изобретепне относится к области контроля и диагност1-п :и цифровых систем и может быть использовано в качестве програмг-шруемого атгализатора ло гических состояний при разрйботке, нападке, контроле работоспособности и техническом обслзгжи1заь;ии сложных ц гфроБЫх устройств и систем, в том числе систем, построенных на базе и r-iHKpoSBM,

Целью изобретения является повышение быстродействия о

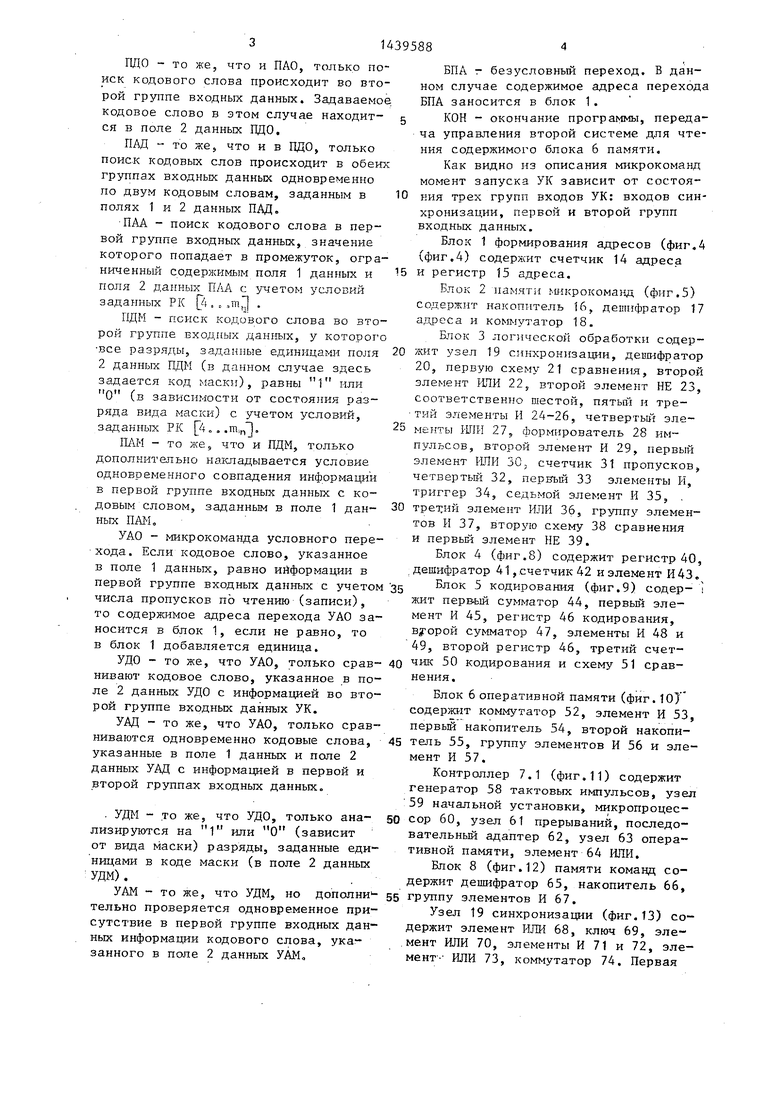

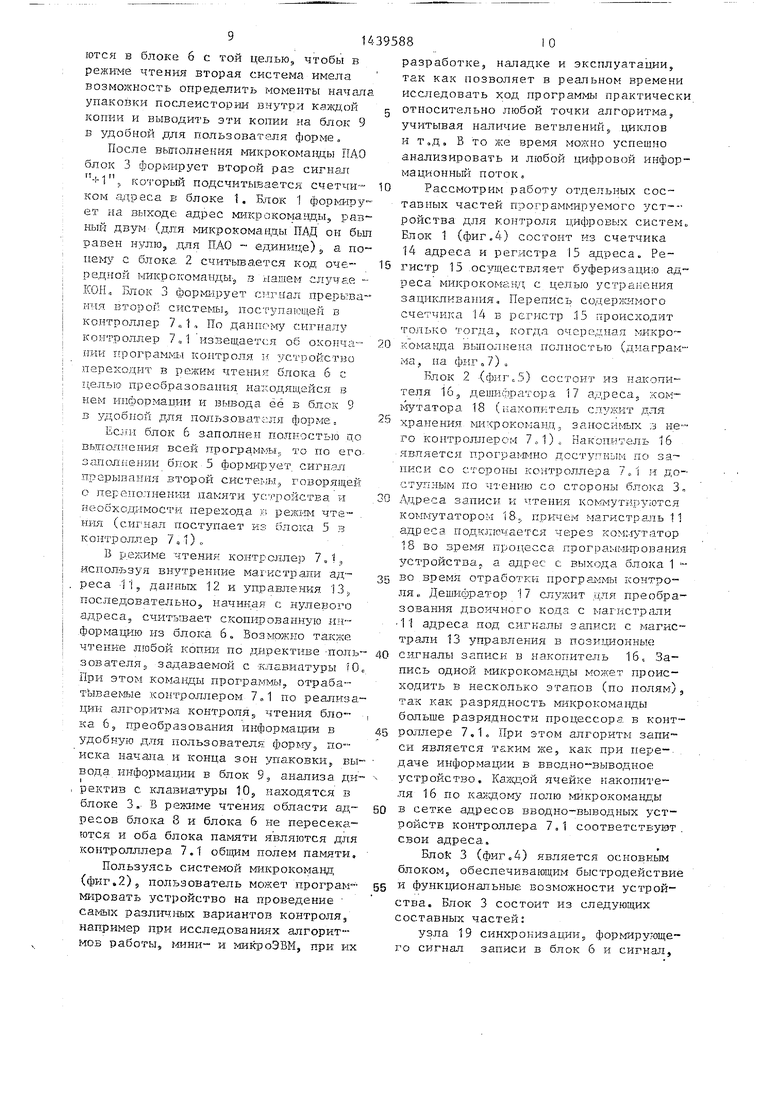

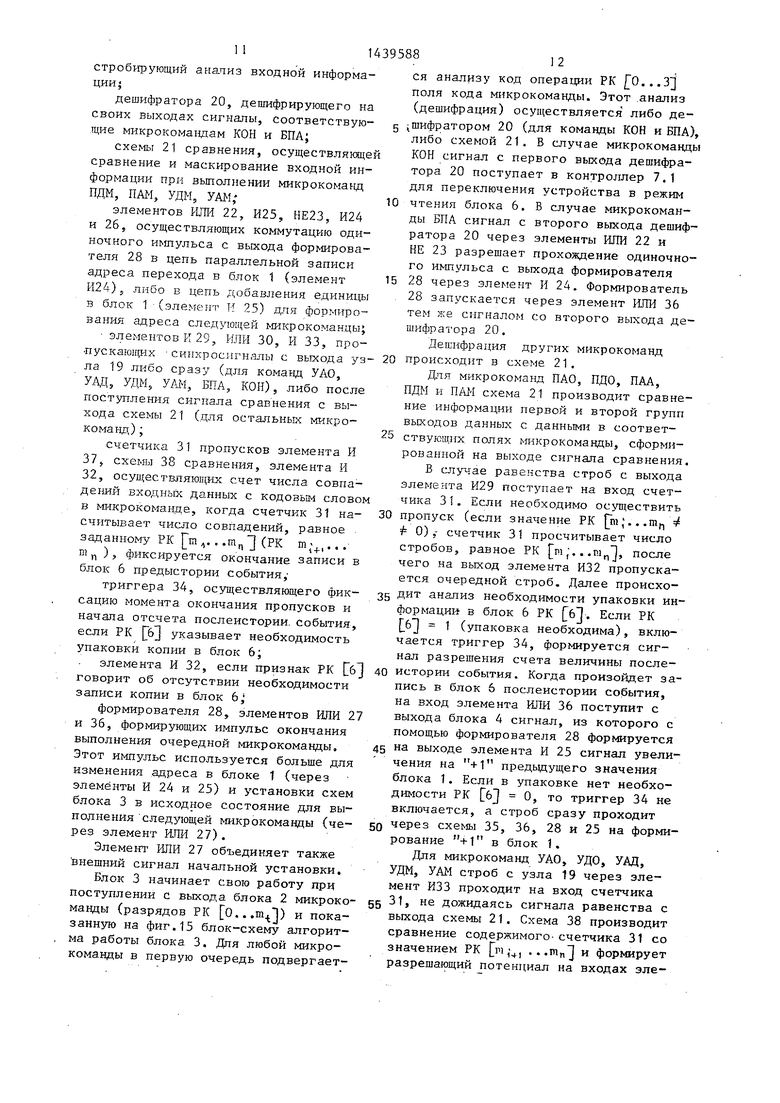

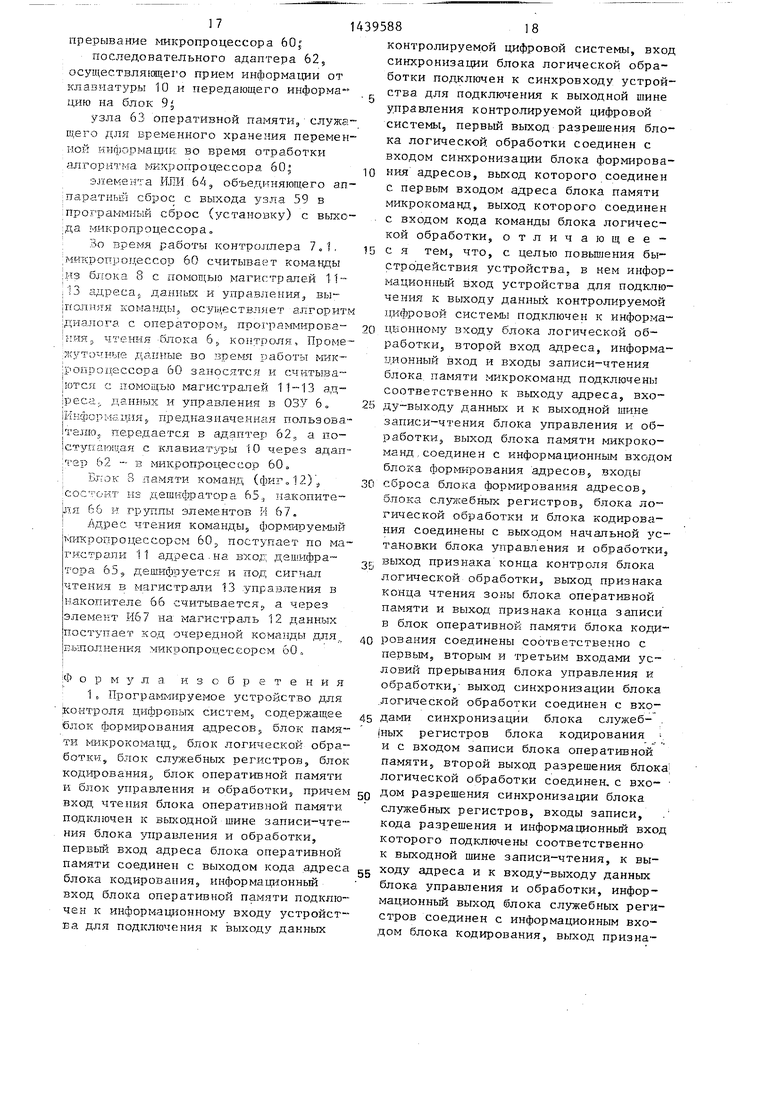

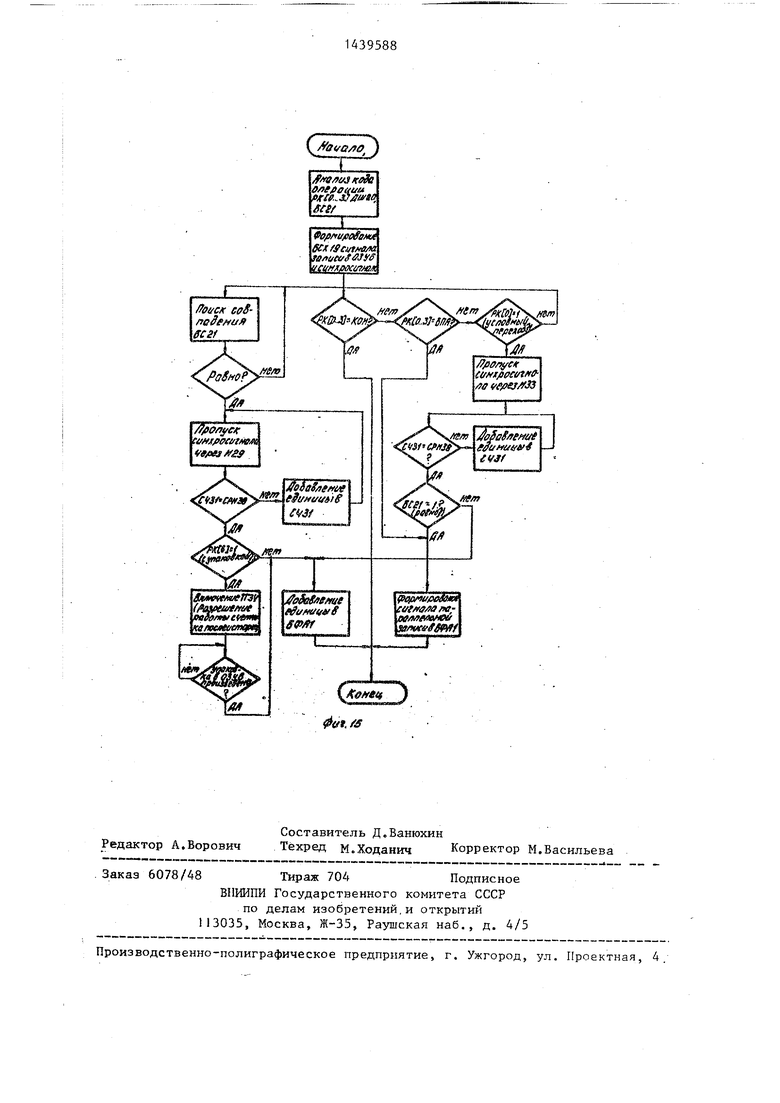

Иа фиг,1 представлена структурная схема программируемого устройства для контроля дифровых систем на фиг,2 - структура микрокоманд реализуемая блоком логической обработки; на фиг,3 - распополсение копии в блоке оперативной памяти; на фиг,4 - CTpyic- турнал схема блока формирования ад :1е сов; на фиг.З - структ урная схема блока ГЕамяти микрокоманд; на - структурная схема блока- логической обработки на фиг„7 -- диаграмма работы блока логической обработкИд на фиг58--14 - структзфные cxeiN-ш соответственно блока сл т1себных регистров, блока кодирования5 блока оперативной памяти,, контгюллера , блока памяти комадц, узла синхронизации и схемы сравнения, ВХОДЯЩРГХ в состав блока логической обработки на фиг«15 блок с7-:ема алгоритма работы блока логической обработки.

Программируемое устройство дхш контроля цифровых систем (фиг«1) содержит блок 1 фopмIipoвaния адресовj блок 2 памяти микрокоманд, блок 3 ло ГIiчecкoй обработки, блок 4 служебных регистров, блок 5 кодирования,, блок: 6 оперативной памяти блок 7 управления и обработки содержаа ий контролллер 7,1 памяти,, блок 8 памяти командj блок 9 индикгодии и клавиатуру 10, ма

2

гистраль 11 адреса, магистраль 12 данных и магистраль 13 управления, Структу15а микрокоманд (фиг,, 2) представляет собой следуюпгее. Весь формат

микрокомапды ;:{елится на четыре ноля: поле кода микрокоманды РК jO,.s7j3 поле числа пропусков РК f г;ц , . ,,т,, поле 1 данных РК L-ii-f п+р и по- ле 2 данных РК ш(,,,р,,| -., Поле

кода микрокоманды РК 10„,,7 /делится на поле кода операции РК L0,,.3j и по,гте условия анализа РК С « I Для микрокоманд УАО, З ДО, УА.Ц,, УДМ и БПА поле чис,на пропусков РК т ,,, , пг.,.

состоит из поля адреса перехода РК т, о ,. ,т I и поля числа ,пропусков РК fm,:; о, «mf,, ,Г1оле условия анализа РК Г4:, ,,7J состоит из следуюп их призна- ков: анализа по чтению упаковки входных данных в ОЗУ 6 Р,К Ъ вида маски (единичный к,ли нулевой) РК D j Все микрокоманды делятся на четыре группы: микрокомапды поиска (ПАО,, ПДО, ПАД, ПАЛ, 1ЩМ,, ПАМ) условных переходов (УАО. УДО, УАД, УШ, УАМ), безусловного перехода (БПА) и окончания программы (Кон.).

ПАО - поиск кодового слова в первой группе входных данных УК., равного кодовому слову, за,цанному полем 1 данных, при этом анализ происходит во время наличия признаков запуска, обозначенных единидами в поле РК 4 о о 7j (по чтению, по записи, с/без упаковки). Запись в блок 6 памяти входной информации первых и вторых групп входов происходит после отсчета числа совпадений кодовых слов, равного числу, указанному в поле пропусков, и не происходит вообще, если признак с/без упаковки будет равным нулю После выполнения микрокоманды в счетчик адреса микрокоманд блока 1 добавляется единица„

ГЩО - то же, что и ПАО, только поиск кодового слова происходит во второй группе входных данных. Задаваемое кодовое слово в этом случае находится в поле 2 данных ЩО,

ПАД то же, что и в ПДО, только поиск кодовых слов происходит в обеих группах входных данных одновременно по двум кодовым словам, заданным в полях 1 и 2 данных ПАД.

ПАА - поиск кодового слова в первой группе входных данных, значение которого попадает в промежуток, ограниченный содерлчимым поля 1 данных и поля 2 данных ПАА с учетом условий заданных РК 4 , ,m, Jj .

ПДМ - поиск кодового слова во втоЬпок 3 логической обработки содеррои группе входных данных, у которого все разряды, заданные единицами поля 20 жит узел 19 синхронизации, дeuл фpaтop 2 данных ПДМ (в данном случае здесь 20, первую схему 21 сравнения, второй задается код маски), равны 1 или элемент РШИ 22, второй элемент НЕ 23,

Соответственно шестой, пятый и тре- тий элементы И 24-26, четвертый эле- 25 менты 1ШН 27,, формирователь 28 (в зависимости от состояния разряда вида маски) с учетом условий, заданных РК р4., .mir,.

- то же, что и ПДМ, только дополнительно накладывается условие одновременного совпадения информации в первой группе входных данных с копульсов, второй элемент И 29, первый

жит первый сумматор 44, первый элемент И 45, регистр 46 кодирования, вуорой сумматор 47, элементы И 48 и 49, второй регистр 46, третий счетэлемент 1 ШИ 30, счетчик 31 пропусков, четвертый 32, первьш 33 элементы И, триггер 34, седьмой элемент И 35, .

довым словом, заданным в поле 1 дан- 30 трет::ий элемент ИЛИ 36, группу злемен- ных ПАМо тов И 37, вторую схему 38 сравнения

УАО - микрокоманда условного пере- и первьй элемент НЕ 39.

хода. Если кодовое слово, указанное Блок 4 (фиг.8) содержит регистр 40, в поле 1 данных, равно ийформации в дешифратор 41 ,счетчик 42 и элемент И43. первой группе входных данных с учетом 35 Блок 5 кодирования (фиг.9) содер i числа пропусков по чтению (записи), то содержимое адреса перехода УАО заносится в блок 1, если не равно, то в блок 1 добавляется единица.

УДО - то же, что УАО, только срав- 40 чик 50 кодирования и схему 51 сравнивают кодовое слово, указанное в по- нения.

Блок 6 оперативной памяти (фиг. 10У содержит коммутатор 52, элемент И 53, первьй накопитель 54, второй накопи- 45 тель 55, группу элементов И 56 и элемент И 57.

Контроллер 7.1 (фиг.11) содержит генератор 58 тактовых импульсов, узел 59 начальной установки, микропроцес. УДМ - то же, что УДО, только ана- 50 сор 60, узел 61 прерываний, последовательньш адаптер 62, узел 63 оперативной памяти, элемент 64 ИЛИ.

Блок 8 (фиг.12) памяти команд содержит дешифратор 65, накопитель 66,

ле 2 данных УДО с информацией во второй группе входных данных УК.

УАД - то же, что УАО, только сравниваются одновременно кодовые слова, указанные в поле 1 данных и поле 2 данных УАД с информацией в первой и второй группах входных данных.

лизируются на 1 или О (зависит от врща маски) разряды, заданные единицами в коде маски (в поле 2 данных УДМ) .

УАМ - то же, что УДМ, но дополни - 55 группу элементов И 67.

тельно проверяется одновременное при- Узел 19 синхронизации (фиг.13) содержит элемент ИЛИ 68, ключ 69, элемент ИЛИ 70, элементы И 71 и 72, элемент-- ИЛИ 73, коммутатор 74. Первая

сутствие в первой группе входных данных информации кодового слова, указанного в поле 2 данных УАМ

БПА т- безусловный переход. В данном случае содержимое адреса перехода БПА заносится Б блок 1. КОН - окончание программы, передача управления второй системе для чтения содержимого блока 6 памяти.

Как видно из описания микрокоманд моьгент запуска УК зависит от состоя- кия трех групп входов УК: входов синхронизации, первой и второй групп входных данных.

Блок 1 формирования адресов (фиг.4 (фиг.4) содержит счетчик 14 адреса и регистр 15 адреса.

Блок 2 na.NiHTii hu-ncpoKOMaiw (фиг.5) содержит накопитель 16, дешифратор 17 адреса и коммутатор 18.

Ьпок 3 логической обработки содержит узел 19 синхронизации, дeuл фpaтop 20, первую схему 21 сравнения, второй элемент РШИ 22, второй элемент НЕ 23,

пульсов, второй элемент И 29, первый

жит первый сумматор 44, первый элемент И 45, регистр 46 кодирования, вуорой сумматор 47, элементы И 48 и 49, второй регистр 46, третий счетБлок 4 (фиг.8) содержит регистр 40 дешифратор 41 ,счетчик 42 и элемент И43 Блок 5 кодирования (фиг.9) содер514395886

схема 21 сравнения (фиг.КО содержит , входов: входовсинхронизации и первой

узлы 75-77 сравнения, узел маскирова-, и второй группвходов ,

ни я

1, включающий схемы 78-79 равнозначности и коммутатор SOj элементы И 81--835 ко1-«х1утатор 84 и дешифратор 85 а

Програмг шруемое устройство для контроля цифровьгх систем работает следующим образом.

Перед включением устройства пользователю необходимо подключить вход синхронизации к управляювдим цепям, а группы входов данных - к информационным цепям исследуемого устройства е После включения контроллер 7.1 в соответствии с программой хранимой в блоке 8, п зоизвод,ит контроль работоспособности всех блоков устройства и выводит сообщение о их состоянии на блок 9 для информирования пользователя „ В случае отсутствия неисправРассмотрим работу устройства на f- примере контроля некоторой микропро- цессорной системы (МП-системы), Например, построенной на базе микропроцессорного набора 580 серии. В данном случае устройство целесообразно под10 ключить к следующим трем магистргшям (МП-системтаО : входы синхронизации к магистрали управления, первую группу входов данных к магистрали адреса j а вторую группу входов данных 15 к магистрали данных МП-системы, Допустим, что пользователю необходга о проанализировать вьшолнение программы МП-системы в реальном масштабе времени относительно двух условий: отьгоси20 тельно момента заггиси данных Д1 в па- М51ть МП системь по адресу А1 и от но- сительно момента чтения неизвестньЕХ данных из памяти МП-системы по адресу А2„ причем необходимо знать пре20 тельно момента заггиси данных Д1 М51ть МП системь по адресу А1 и о сительно момента чтения неизвест данных из памяти МП-системы по ад су А2„ причем необходимо знать п

|ности пользователь должен с номоЕ1;ью

клавиатуры 10 запрограт-шнровать уст- дысторию хода программ в объеме

300 циклов обращения в память и леисторию хода программы в объем 50 циклов обращения в память от тельно каждого из условийс

30

300 циклов обращения в память и пос- леисторию хода программы в объеме 50 циклов обращения в память относительно каждого из условийс

Кроме того,, анализ первого условия необходимо провести лишь тогда, когда первая ситуация появится 35-й раз, а вторая ситуация - 15-й раз. Для ре- Е1ения этой задачи пользователь должен

2g с помощью клавиатуры 10 занести через контроллер 7,1 в блок 2 следующую программу, состоящую из трех микрокоманд: ШЩ (по чтению О, по записи 1, упаковки 1;, число пропус40 ков 35j данные 1 А, данные 2 Д1), ПАО (по чтению 1, по записи О, с/без упаковки 1, число пропусков 15, данные 1 А2), КОН„ Далее пользова х ель с помощью кла45 виатуры 10 долйшн занести через контроллер 7.1.в блок 4 величину предыстории события, равную 300, и велигчи- ну послеистории события, равную 50, после чего производится пуск устройдр ства на анализ выходов. До момента появления на магистралях МГ1-систе:мы ситуации, за,цанной микрокомандой ПАД, блоки устройства будут находиться в

роиство на конкретный вид контроля, для чего с помощью директивы сначала задается -величина зоны упрлсовки копии входного процесса для записи в блок 6 S Эта информация пересклается контроллером 7,1.в блок 4, где хранится в течетге всего цикла контроля о Далее оператор, полт зуясь системой ш-ш- рокоманд (фиг„2)5 составляет программу контроля и заносит ее с клавиатуры 10, Во BpeivL4 этой процедуры контроллер 7,1 4iopf.MpyeT коды микрокоманд в задапной пользователем последовательности и по магистрали адреса 11з -данйых 12 и управления 13 заносит их в блок 2. Параллельно контроллер 7„1 отображает на блоке 9 заносимые микрокоманды для информирования пользователя о их вводе После окончания процедуры программирования пользователь с помощью директивы клавиатуры 10 переводит устройство в режим контроля входной ипформадии„

С этого момента блок 3 в зависимости от СОСТОЯН1-Ш групп входных данных и состояния цепей входа синхронизации ачшшет последовательно выполнять микрокоманды, занесенные следующих состояниях: в блок 2, и копировать участки gg блок 1 формирует на выходе нуле- входного потока групп данных в бло- вой адресу ке 6,блок 2 считывает по нулевому

Момент залуска устройства (фиг,2) адресу код микрокоманды ПД.Ц,- зависит от состояния трех групп его блок 3 начинает искать во входных

Рассмотрим работу устройства на примере контроля некоторой микропро- цессорной системы (МП-системы), Например, построенной на базе микропроцессорного набора 580 серии. В данном случае устройство целесообразно подключить к следующим трем магистргшям (МП-системтаО : входы синхронизации к магистрали управления, первую группу входов данных к магистрали адреса j а вторую группу входов данных к магистрали данных МП-системы, Допустим, что пользователю необходга о проанализировать вьшолнение программы МП-системы в реальном масштабе времени относительно двух условий: отьгосительно момента заггиси данных Д1 в па- М51ть МП системь по адресу А1 и от но- сительно момента чтения неизвестньЕХ данных из памяти МП-системы по адресу А2„ причем необходимо знать пре дысторию хода программ в объеме

30

300 циклов обращения в память и пос- леисторию хода программы в объеме 50 циклов обращения в память относительно каждого из условийс

Кроме того,, анализ первого условия необходимо провести лишь тогда, когда первая ситуация появится 35-й раз, а вторая ситуация - 15-й раз. Для ре- Е1ения этой задачи пользователь должен

2g с помощью клавиатуры 10 занести через контроллер 7,1 в блок 2 следующую программу, состоящую из трех микрокоманд: ШЩ (по чтению О, по записи 1, упаковки 1;, число пропус40 ков 35j данные 1 А, данные 2 Д1), ПАО (по чтению 1, по записи О, с/без упаковки 1, число пропусков 15, данные 1 А2), КОН„ Далее пользова х ель с помощью кла45 виатуры 10 долйшн занести через контроллер 7.1.в блок 4 величину предыстории события, равную 300, и велигчи- ну послеистории события, равную 50, после чего производится пуск устройдр ства на анализ выходов. До момента появления на магистралях МГ1-систе:мы ситуации, за,цанной микрокомандой ПАД, блоки устройства будут находиться в

следующих состояниях: gg блок 1 формирует на выходе нуле- вой адресу блок 2 считывает по нулевому

данных первой и второй групп входов одновременно ситуацию, заданную ПДЦ, с учетом состояния цепей синхронизации (сигналов Чтение и Запись в память МП-системы),

блок 4 на первых выходах будет удерживать величину упаковки, равнукГ 350, а на втором выходе - потенциал нуля, говорящий об отсутствии в блоке 6 интересующей пользователя информации, описанной ПАЦ

блок 5 под сигналом синхронизации с выхода блока 3 формирует последовательность адресов записи в блок 6, начиная с нулевого и кончая адресом, равным 350. Далее форг шрование адресов снова начинается с нулевого адреса и T.A.J

в блок 6 запис явается последовательно по адресам с выхода блока 5 вся информагрш, появляющаяся в реальном масштабе времени в первой и второй группах входов данньк устройства причем после записи очередного слова информац;ии по адресу 350 следующее слово записывается по адресу О, стирая таким образом слово, записанное- ранее по адресу О, и т.д., т.е. в блоке 6 постоянно копируется состояние магистралей адреса и данных МП- системы в объеме 350 слов.

При появлении первый раз на магистралях МП-системы ситуации, заданной НАД, блок 3 просчитывает это событие с помощью внутреннего счетчика Состояния других блоков не изменяются. После того, как блок 3 насчитывает ЧИСЛО таких ситуаций, равное 35, с его выхода в блок 4 пос гупает сиг- нап, разрешающий счет величины после истории входного процесса. Блок 4 отсчитывает количество записей в бло

6, равное величине послеистории собы- 45 располагаются друг за другом со сметия (60), и формирует сигнал, поступающий на входы блоков 5, 6 и 3 для формирования новых адресов записи в блок 5, фиксации адреса окончания записи первого блока (в блок 6), форми- JQ сигнала +1 (в блок 3),

Одновременно (в течение одного такта) блок 3 формирует сигнал на вход блока 1, по которому блок 1 добавляет единицу к счетчику адреса, gg после чего на его выходе устанавливается адрес, равный 1. По данному адресу из блока 2 считывается вторая микрокоманда (ПАО),

щением в 350 адресов. Взаимное расположение зон упаковки послеистории и предыстории событий внутри каждой зоны упаковки при заданной программе может меняться при повторных запусках устройства, но обязательно выполняются условия: U1+U2 +дЗ &4+Л5 350, U1 + йЗ Л5 50, U2 &4

300, 350,

адреса Ац,, ОЗУ О, А,,, ОЗУ

Н2

ОЗУ + 1, А,, ОЗУ 350.

Признаки конечных адресов записи в блок 6 очередной копии (для нашей задачи А;, ОЗУ для первой зоны упаков- ки, А).-г.ОЗУ для второй зоны) запомина-

Смена микрокоманды происходит в

МП-системы еще не изменилось, а сле- довательно, не нарушено ее реальное время. Таким образом, смена микроко- , манды произойдет после того, как МП- система 35 раз занесет данные Д1 по адресу А1, причем относительно этого

события в блоке 6 окажется копия реального кода программы МП-системы (копия последовательности машинных кодов команд и соответствующих им адресов), включая предысторию события

в объеме 300 циклов синхронизации и после11сторию события в объеме 50 циклов синхронизации. - При этом базовый адрес с выхода блока 6 скачком увеличивается на величину, равную 350 (при

отработке микрокоманды ПДЦ он был ра вен 0).

Микрокоманда ПАО изменяет алгоритм работы устройства следующим образом. Во-первьгх, анализу подвергаются лишь входы синхронизации и первая группа входов данных устройства (магистрали управлення и адреса MП-cиcтe ы) . Во-, вторых, адрес МП-системь аналияирует-- ся на равенство А2 в моменты чтения

информации из МП-системы. В третьих, при появленрш на магистрали адреса : указанной ПАО ситуации (чтения по адресу А2) блок 3 просчитывает число совпадений таких ситуаций, равное 15

после чего в блоке 4 включается отсчет величины послеистории.

Величины предыстории и послеистории событий остаются при обработке : обеих микрокоманд одинаковыми. Различными будут лишь внутренние адреса записи двух копий в блок 6. Возможное расположение копий в блоке 6 показано на фиг.З. Объемы упаковок копий в блоке 6 одинаковы, равны 350 слов и

щением в 350 адресов. Взаимное расположение зон упаковки послеистории и предыстории событий внутри каждой зоны упаковки при заданной программе может меняться при повторных запусках устройства, но обязательно выполняются условия: U1+U2 +дЗ &4+Л5 350, U1 + йЗ Л5 50, U2 &4

300, 350,

адреса Ац,, ОЗУ О, А,,, ОЗУ

Н2

ОЗУ + 1, А,, ОЗУ 350.

Признаки конечных адресов записи в блок 6 очередной копии (для нашей задачи А;, ОЗУ для первой зоны упаков- ки, А).-г.ОЗУ для второй зоны) запомина-

914

готся в блоке 6 с той целью, чтобы в режиме чтения вторая система имела возможность определить моменты начаг{а упаковки послеистории внутри калодой копии и выводить эти копии на блок 9 в удобной для пользователя форме.

После выполнения микрокомавды ПАО блок 3 формирует второй раз сигнал -I-1, r oTopbDi подсчитывается счетчиком ддреса в блоке 1. Блок 1 форьафу- ет на выходе адрес микрокоманды, рав Шзтй двум (для микрокоманды НАД он бьш равен нулю, для ПАО единице) а по- с блока 2 считьгоз.ется код очередной ьткрокоманды-з з Апашем - КОН, Блок 3 формирует прерывания второй системы поступающей в контроллер 7„К По данпом: сигналу контроллер 7,1 извещается об окончании програмУдЫ контроля и устройство перекодит в релсим чтения блока 6 с преобразования на ходящейся в нем инфор.мадии и 1зывода её в блок 9 в удобной для пользоватгля форме,

Есзти блок 6 заполнен полностыо цо вьтолнения всей программы, то по его- заполнении бпок 5 формирует сигнал прерывания второй систет.1Ы, говорящей о переполнении памяти ус тройства и необходимости перехода :fv рела-ш чтения (сигнал поступает из блока 5 в контроллер 7,1),,

В ре :симе чтения контролле з 7.1, испол-ьзуя Енутренпие маг истрапи адреса -11, данных 12 и управления 13:, последовательно, начиная с нулевого адреса, считывает скопированную информацию из блока 6. Возможно также. чтение любой копии по директиве -ноль- зов ателяа за цаваемой с -клавиатуры iO При этом команды программы, отраба- тЬ1ваемые контролх1ером 7,1 по реализации алгоритма контроля; чтения бло- ка 65 преобразования информации в удобную для пользователя форму поиска начала и конца зон упаковкиj вывода информации в блок 9, анализа ди , ректив с клавиатуры 10, находятся в блоке 3. В режиме чтения области адресов блока 8 и блока 6 не пересекаются и оба блока памяти являются для контролллера 7.1 обищм полем памяти.

Пользуясь системой мз-псрокоманд (фиг.2) 5 пользователь может пpoгpa s мировать устройство на проведение самых различ) вариантов контролЯд например при исследованиях алгоритмов работы, гдани™ и микроЭБМ, при их

9588I О

разработке, наладке и эксплуатании, так как позволяет в реальном времени исследовать ход програг-гмы практически

g относительно любой точки алгоритма, учитывая наличие ветвлений, циклов и ТоД, В то же время можно успешно анализировать и любой цифровой инфор- ма ци о н ньй поток,

0Рассмотрим работу отдельных составных частей программируемого уст-- ройства для контроля цифровых систем Блок 1 (фиг,4) состоит из счетчика 14 адреса и регистра 15 а,цреса„ Ре15 гистр 15 осуществляет буферизацию адреса микроком-анд с целью устранения зацикливания. Перепись содержимого счетчика 14 в регистр .15 происходит только Т огда, когда очередная микро20 команда выполкена полностью (диаграмма J на фиг,7),

Блок 2 -(фиг.5) состои-т из нахсопи- теля 16, дешифратора 17 адреса, ком- ьгутатора 18 (накопитель служит для

-25 хранения микрокоманд, заносимых з него контроллером 7„1) Накопитель 16 .является nporpai MHo доступным по записи со стороны контроллера и до- -етупным по ча-ению со стороны 3,

30 Адреса записи и чтения коммут фуются коммутатором 18,, npi-гчем магистраль 11 адреса подклгсчается через коммл татор 18 во время процесса программ1-фО зания устройства, а адрес с выхода блока 1 35 во время отработки програ - мы контроля. Дешифратор 17 слулсит для преобразования двоичного кода с т-гагистргши 11 адреса под сигналы- записи с магистрали 13 управления в позиционные

40 С1-1гналы записи в накопитель 16 Запись одной микрокоманды может происходить в несколько этапов (по полям), так как разрядность ш крокоманды больше разрядности процессора в конт45 роллере 7«1. При этом алгоритм записи является таким же, как при передаче информации в вводно-выводное устройство, Калсдой ячейке накопителя 16 по ка сдому полю микрокоманд;ы

50 в сетке адресов вводно-выводных устройств контроллера 7.1 соответствуют. СБОИ адреса,

Бло1с 3 (фиго4) является основным блоком5 обеспечивающим быстродействие

55 и функциональные возможности устройства. Блок 3 состоит из следующих составных частей:

узла 19 синхронизации, формирующего сигнал записи в блок 6 и сигнал.

11

стробирующий анатиз входной информации- дешифратора 20, дешифрирующего на своих выходах сигналы, соответствующие микрокомандам КОН и БГГА;

схемы 21 сравнения, осуществляющей сравнение и маскирование входной информации при выполнении микрокоманд ПДМ, ПАИ, УДМ, ,

элементов ИЛИ 22, И25., НЕ23, И24 и 26, осуществляющих коммутацию одиночного иьтульса с выхода формирователя 28 в цепь параллельной записи адреса перехода в блок 1 (элемент И24)5 либо в цепь добавления единицы в блок 1 (элемент И 25) для формирования адреса следующей микрокоманды; элементов К 29, ИЛИ 30, И 33, про- пускающих синхросигналь с выхода узла 19 либо сразу (для команд УАО, УАД, УДМ, УАМ, БПА, КОН), либо после поступления сигнала сравнения с выхода схемы 21 (для остальных микро- ) ,

счетчика 31 пропусков элемента И 37, схемы 38 сравнения, элемента И 32, осущестБляюп(их счет числа совпадений входных данных с кодовым словом в микрокоманде, когда счетчик 31 насчитывает число совпадений, равное . заданному РК т ,. . .т (РК ,.. . m ), фиксируется окончание записи в блок 6 предыстории события,

триггера 34, осуществляющего фиксацию момента окончания пропусков и начала отсчета послеистории. события, если РК бЗ ук:азывает необходимость упаковки копии в блок 6;

10

15

ся анализу код операции РК 0,,,3 поля кода микрокоманды. Этот .анализ (дешифрация) осуществляется либо де- 5 шифратором 20 (для команды КОН и БПА), либо схемой 21. В случае микрокоманды КОН сигнал с первого выхода дешифратора 20 поступает в контроллер 7.1 для переключения устройства в режим чтения блока 6. В случае микрокоманды БПА сигнал с второго выхода дешифратора 20 через злементы 1ШИ 22 и НЕ 23 разрешает прохождение одиночного икшульса с выхода формирователя 28 через элемент И 24. Формирователь 28 запускается через элемент J-ШИ 36 тем же сигналом со второго выхода дешифратора 20.

Дешифрация других микрокоманд происходит в схеме 21.

Для микрокоманд ПАО, ПДО, ПАА, ПДМ и П/Ш схема 21 производит сравнение информации первой и второй групп выходов данных с данными в соответствующих полях микрокоманды, сформированной на выходе сигнала сравнения.

В случае равенства строб с выхода элемента И29 поступает на вход счетчика 31, Если необходимо осуп ествить пропуск (если значение РК |jii ...mf ф 0).- счетчик 31 просчитывает число стробов, равное РК ,., ., после чего на выход элемента И32 пропускается очередной строб. Далее происхо- 35 дит анализ необходимости упаковки информации в блок 6 РК . Если РК iJi 1 (упаковка необходима), включается триггер 34, формируется сигнал разрешения счета величины после20

25

30

элемента И 32, если признак РК 40 истории события. Когда произойдет заговорит об отсутствии необходимости записи копии в блок 6

формирователя 28, элементов ИЛИ 27 и 36, формирующих импульс окончания выполнения очередной микрокоманды. Этот импульс используется больше для изменения адреса в блоке 1 (через элементы И 24 и 25) и установки схем блока 3 в исходное состояние для вы- поднения следующей микрокоманды (через элемент И.ПИ 27).

Элемет ИЛИ 27 объединяет также внешний сигнал начальной установки.

Блок 3 начинает свою работу при поступлении с выхода блока 2 микроко- мавды (разрядов РК О...) и показанную на фиг.15 блок-схему алгоритма работы блока 3. Для любой микрокоманды в первую очередь подвергаетпись в блок 6 послеистории события, на вход элемента ИЛИ 36 поступит с выхода блока 4 сигнал, из которого с помощью формирователя 28 формируется

45 на выходе элемента И 25 сигнал увеличения на +1 предьвдущего значения блока 1. Если в упаковке нет необходимости РК О, то триггер 34 не включается, а строб сразу проходит

50 через схемы 35, 36, 28 и 25 на формирование +1 в блок 1.

Для микрокоманд УАО, УДО, УАД, УДМ, УАМ строб с узла 19 через элемент ИЗЗ проходит на вход счетчика

g5 31, не дожидаясь сигнала равенства с выхода схемы 21. Схема 38 производит сравнение содержимого-счетчика 31 со значением РК ...Шп и формирует разрешающий потенциал на входах эле

10

15

39588J2

ся анализу код операции РК 0,,,3 поля кода микрокоманды. Этот .анализ (дешифрация) осуществляется либо де- 5 шифратором 20 (для команды КОН и БПА), либо схемой 21. В случае микрокоманды КОН сигнал с первого выхода дешифратора 20 поступает в контроллер 7.1 для переключения устройства в режим чтения блока 6. В случае микрокоманды БПА сигнал с второго выхода дешифратора 20 через злементы 1ШИ 22 и НЕ 23 разрешает прохождение одиночного икшульса с выхода формирователя 28 через элемент И 24. Формирователь 28 запускается через элемент J-ШИ 36 тем же сигналом со второго выхода дешифратора 20.

Дешифрация других микрокоманд происходит в схеме 21.

Для микрокоманд ПАО, ПДО, ПАА, ПДМ и П/Ш схема 21 производит сравнение информации первой и второй групп выходов данных с данными в соответствующих полях микрокоманды, сформированной на выходе сигнала сравнения.

В случае равенства строб с выхода элемента И29 поступает на вход счетчика 31, Если необходимо осуп ествить пропуск (если значение РК |jii ...mf ф 0).- счетчик 31 просчитывает число стробов, равное РК ,., ., после чего на выход элемента И32 пропускается очередной строб. Далее происхо- 35 дит анализ необходимости упаковки информации в блок 6 РК . Если РК iJi 1 (упаковка необходима), включается триггер 34, формируется сигнал разрешения счета величины после20

25

30

40 истории события. Когда произойдет запись в блок 6 послеистории события, на вход элемента ИЛИ 36 поступит с выхода блока 4 сигнал, из которого с помощью формирователя 28 формируется

45 на выходе элемента И 25 сигнал увеличения на +1 предьвдущего значения блока 1. Если в упаковке нет необходимости РК О, то триггер 34 не включается, а строб сразу проходит

50 через схемы 35, 36, 28 и 25 на формирование +1 в блок 1.

Для микрокоманд УАО, УДО, УАД, УДМ, УАМ строб с узла 19 через элемент ИЗЗ проходит на вход счетчика

g5 31, не дожидаясь сигнала равенства с выхода схемы 21. Схема 38 производит сравнение содержимого-счетчика 31 со значением РК ...Шп и формирует разрешающий потенциал на входах эле131439588f

ментов И 26 н 32. Если в этот момент ных с содержимым РК ш

времени на втором входе элемента И 26 присутствует сигнал Равно, то через элементы ИЛР1 22 и FiE 23 на первом .„ входе элемента И24 будет присутство вать разрешающий потенциал, пропус- каюЕцшЧ строб через схемы 32, 35, 36 и 28, второй вход элемента И24 на формирование сигнала параллельной ю записи в блок 1, Если же в момент равенства содержимого счетчика 31 и схемы 38 на втором входе элемента И 26 быи сигкгал Не равно, по тем . же цепям только через элемент И 25, 15 произойдет добавление +1 в блок 1о Вьщеление синхронизируклцих стробов происходит в узле 19 Рассмотр1 м работу одного из возможных вариантов его построения на примере, описанного 20 контроля МП-системы (фиг,13), Узел 19 ссгстоит из элемента ИЛР 68, ключа 69 элементов Ш1И 70 и 13, И 71 и 72 коммутатора 74, Элемент ИЛИ 68 объединяет сигналы обращения МП-системы 25 по чтению либо к собственной памяти, либо к устройствам ввода-вывода. Элемент ИЛИ 70 производит то же самое, только по сигналам запргсн МП-системы, Кпюч 69 реярешает прохождение сигна-- 30 лов с выходов ШИ 68 и ИЛИ 70 через И71 и 72 либо всегда, либо только во время работы канала прямого доступа Ш™систе гьи С ИЛИ 73 обобшенузел 77 сравнения,

сравнение первой групп с содержимым РК

узел маскирования, себя схемы 78 и 79 рав коммутатор 80, ; (вид м ваемой РК {l, поступа 78 и 79);

схема И 81, выделяю сигнал одновременного ных данных в группах 1 мым РК п1 .1. .пц ;

элемент И 82, выдел сигнап одновременного ных первой группы вход Сга,, . ИИ и маски .,,га данных пе входов;

элемент И 83, выдел , сигнап при попадании з в ггервой группе входов

заданный вeличинa и РК и РК ,..,

коммутатор 84 и деш осуществляющие коммута результатов давления н 21 в зависимости от ко

РК Го,.,;Л,

При коде операции Р

на выходе коммутатора рез щьтат сравнения РК

с первой группой входо

с первой группой входов, при РК

ные сигналы записи и чтения поступают 35 1 - выход узла 76, при РК в блоки 6 и 5 в качестве стробирую- 0,.„3 1 2 - И81, при РК 0...31

щкк сигналов, ком утатор 74 пропускает на соста.вные части блока 3 сиг- i-iiWoi чтения (с выхода И7 ) либо записи с (вьпсода И72), либо оба сигнала вместе,, Это зависит от значений РК L4J и РК .5J. Такое построение узла 19 дает возможность анализировать отдельно работу программы, работу канала прямого доступа МП-системы., а так- :е выводить ка блок 9 из блока 6 информацию в удобной форме, что eDj;e бол.ьше облегчает пользователю поиск возможных ошибок в исследуемой МП- системе ,

Структурная схема возможного варианта построения схемы 21 сравнения (фиг.14) содержит следующие составные части;

узел 75 сравнения, осуществляющий сравнение первой группы входных дан 3 - выход И83, при РК о, 0,3 4

40

45

ньпс с содержимым РК i

m

.m,

|... .

узел 76 сравнения., ос тцествляющий сравнение второй группы входных данкоммутатор 80 и при РК 0„..,3j 5 - выход коммутатора 80.

Блок 4 служебных регистров (фиг.8 состоит из следующих составных частей:

регистра 40, осуществляющего при программировании устройства фиксацию величины зоны упаковки одной копии в блок 6;

дещифратора 41, осуществляющего де1 ифрацию номера регистра 40 счетчика 42; ,

счетчика 42, осуществляющего счет синхроимпульсов с выхода блока 3 при фиксации в блоке 6 послеистории события j

элемента И43, разрешающего прохож 55 дение стробов с блока 3 на счетчик 4 только при наличии разрешения с блока 3 (выхода триггера 34) .

Работа блока 4 происходит следующим образом. Регистр 40 и счетчик 42

50

ых с содержимым РК ш

. узел 77 сравнения, осуществляющий

равнение первой группы входных дан- с содержимым РК ,. . . .

узел маскирования, включающий в ебя схемы 78 и 79 равнозначности и оммутатор 80, ; (вид маски, задааемой РК {l, поступает на схемы 78 и 79);

схема И 81, выделяющая на выходе сигнал одновременного равенства входных данных в группах 1 и 2 с содержимым РК п1 .1. .пц ;

элемент И 82, выделяющий на выходе сигнап одновременного равенства данных первой группы входов с РК Сга,, . ИИ и маскированных РК .,,га данных во второй группе входов;

элемент И 83, выделяющий на выходе сигнап при попадании значения данных в ггервой группе входов в промежуа ок,

П+1

. гя.

.4-f

1

заданный вeличинa и РК п и РК ,..,

коммутатор 84 и дешифратор 85, осуществляющие коммутацию одного из результатов давления на выход схемы 21 в зависимости от кода операции

РК Го,.,;Л,

р п При коде операции РК LO.,.3J О

на выходе коммутатора 84 присутствует рез щьтат сравнения РК , . лп,р

с первой группой входов, при РК

1 - выход узла 76, при 0,.„3 1 2 - И81, при РК 0...31

1 - выход узла 76, при РК 0,.„3 1 2 - И81, при РК 0...31

3 - выход И83, при РК о, 0,3 4

коммутатор 80 и при РК 0„..,3j 5 - выход коммутатора 80.

Блок 4 служебных регистров (фиг.8) состоит из следующих составных частей:

регистра 40, осуществляющего при программировании устройства фиксацию величины зоны упаковки одной копии в блок 6;

дещифратора 41, осуществляющего де1 ифрацию номера регистра 40 счетчика 42; ,

счетчика 42, осуществляющего счет синхроимпульсов с выхода блока 3 при . фиксации в блоке 6 послеистории события j

элемента И43, разрешающего прохож- дение стробов с блока 3 на счетчик 42 только при наличии разрешения с блока 3 (выхода триггера 34) .

Работа блока 4 происходит следующим образом. Регистр 40 и счетчик 42

являются для контроллера 7.1 программно-доступным по записи, выставляя на магистрали 12 данных данные для записи в регистр 40, счетчик 42 формирует адрес регистра 40 счетчика 42 на магистрали 11 адреса и строб записи в магистрали 13 управления. Дешифратор 41 в зависимости от номера разрешает прохождение сигналов записи на регистр 40 или счетчик 42 для записи данных, установленных на магистрали 12 данных.

Блок 5 кодирования (фиг,9) состоит

20

25

из следующих составных частей: сумма-15 ,роны контроллера 7.1. Запись информатора 44, элемеь та И 45, регистра 46, сумматора 47, элементов И48 и 49, счетчика 50, схемы 51 сравнения.

Начальная установка (сброс в ноль) .регистра 46 и счетчика 50 происходит по сигналу сброса контроллера 7.1, С выхода сумматора 47 формируется адрес записи в блок 6.

При записи в блок 6 первой зоны упаковки адреса начинают изменяться, начиная с нулевого. Элемент И 48 пропускает счетные импульсы с выхода блока 3 на вход счетчика 50, при эт ОхМ схема 51 сравнивает содержимое счетчика 50 с величиной зоны упаковки, заданной регистром 40 в -блоке 4.

При их равенстве через элемент И49 под импульс записи с блока 3 на вход счетчика 50 поступает имйульс сброса, устанавливающий счетчик 50 снова в нулевое состояние. Сумматор 47, имея на первых входах ноль с выхода регистра 46, пропускает содержимое счетчика 50 на вход блока 6. Сумматор 44 суммирует содержимое регистров 40 и 46, т.е. при первой упаковке на выходе сумматора 44 присутствует

30

щий в накопитель 54 ос тцестьпяется с первой и второй групп входов данных устройства. В накопитель 54 одновременно записываются признаки адресов конца упаковки для каждой зоны. Эта информация сообщается контроллеру 7.1 в форме прерываний в режиме чтения, коммутатор 52 в режиме записи пропускает на адресные входы накопителей 54 и 55 адреса с выхода блока 5, а в режиме чтения - адреса с магистрали адреса 11 . Подключение да накопителя к магистрали 12 данных осуществляется во время реждаш чтения через элемент PI56. В это же время возможно появление сигнала прерывания с выхода накопителя 55 через элемент И57. Хранение признаков конца упаковки накопителя 55 необходимо

35 контроллеру 7.1 для того, чтобы в режиме чтения можно было бы программно рассчитать начало и конец каждой зоны упаковки, так как общая величина упаковки, задаваемая пользователем, из40 вестна и в блоке 9 пользователю, все зоны упаковки с одинаковым распределением (для удобства анализа).

Контроллер 7.1 памяти (фиг.11) состоит из следующих составных часра 40. С приходом из блока 42 сигнала, говорящего об окончании копирования в блоке 6 первой зоны, с выхода элемента И45 под сигнал записи в блок 6 в регистр 46 поступает импульс записи содержимого сумматора 44. В результате адрес на выходах сумматора 47 и 44 меняется скачком на величину, равную величине регистра 40. Далее процедура формирования адресов повторяется, но уже относительно смещенного в регистр 46 базового адреса. При формировании с выхода сумматора 47 адреса последней ячейки памяти блока 6 на его втором выходе формируется сигнал переполнения, запрещаю

ций на элемент И 48 прохождение счетных импульсов и поступающий в контроллер 7.1 для переключения устройства в режим чтения. Формирование адресов записи в блок 6 приведенным способом обеспечивает упаковку копий в блок 6 в соответствии с фиг.З.

Блок 6 (фиг.10) состоит из коммутатора 52, элемента И 53, первого накопителя 54, второго накопителя 55, элементов И 56 и 57.

Накопители 54 и 55 являются программно -до с т ушными по чтению со сто

роны контроллера 7.1. Запись информа

щий в накопитель 54 ос тцестьпяется с первой и второй групп входов данных устройства. В накопитель 54 одновременно записываются признаки адресов конца упаковки для каждой зоны. Эта информация сообщается контроллеру 7.1 в форме прерываний в режиме чтения, коммутатор 52 в режиме записи пропускает на адресные входы накопителей 54 и 55 адреса с выхода блока 5, а в режиме чтения - адреса с магистрали адреса 11 . Подключение да накопителя к магистрали 12 данных осуществляется во время реждаш чтения через элемент PI56. В это же время возможно появление сигнала прерывания с выхода накопителя 55 через элемент И57. Хранение признаков конца упаковки накопителя 55 необходимо

контроллеру 7.1 для того, чтобы в режиме чтения можно было бы программно рассчитать начало и конец каждой зоны упаковки, так как общая величина упаковки, задаваемая пользователем, известна и в блоке 9 пользователю, все зоны упаковки с одинаковым распределением (для удобства анализа).

Контроллер 7.1 памяти (фиг.11) состоит из следующих составных частей:

генератора 58 тактовых импульсов, формирующего в непрерывном режиме тактовые импульсы для работы микропроцессора и Последовательного адаптера;

узла 59 начальной установки, формирующего сигнал начальной установки (сброса) при появлении питающих напряжений;

микропроцессора 60, реализующего выполнение команд алгоритма контрол- лера 7.1;

узла 61 прерывания, принимающего внещние прерывания и осуществляющего

17

прерывание микропроцессора 60j

последовательного адаптера 62, осуществлжощего прием информации от клавиатуры 10 и передающего информацию на блок 9i,

узла 63 оперативной памяти, служащего для временного хранения переменной кнформащ1и во время отработки алгоритма г ШКропроцессора 60

элемента И.ПИ 64, объединяющего ап- ;яаратньй сброс с выхода узла 59 в программный сброс (установку) с выхода мирсропроцессора

Во время работы контроллера 7.1, микропроцессор 60 считывает команды ;из блока 8 с помоп1;ыо магистралей 11-- i13 адреса., данньЕ : и управления., вы- |г :ол1- яя команды, осуществляет а.17горнтм ;диа.пога с оператором, программирова- кия,) чтения блока 6,, контроля, Проме- :куточные цаиные. во зремл работы шк- ;ропроцессора 60 заносятся и считыв-а иотся с помощью магистралей 11-13 ад- ipeca,, данных и управления в ОЗУ 6. Информация предназначенная пользова 1телю, передается в адаптер 62, а по- 1ступа1ош,ая с клавиатуры через адап : гер 62 - в микропроцессор 60. , Блок 8 памяти команд (фиг„12),, сос 7оит из дешифратора 65., накопите- |ля 66 и группы элементов И 67. I йдрес чтения командЫ; фop мpyeмый микропроцессором 60,, поступает по ма гистрапи 11 адреса-на вход дешифратора 65, дешифруется и под сигнал чтения в магистрали 13 управления в накопителе 66 считывается,, а через элемент И67 на магистраль 12 данных поступает очередной команды для, Е.кполнения микропроцессором 60«

Ф о р м у л а изобретения 1 Программируемое устройство для контроля цифровых систем содержащее блок формирования адресов, блок памяти ьшкрокоманд., блок логической обработки, блок служебных регистров, бло кодирования, блок оперативной памяти

и блок управления и обработки, причем gQ дом разрешения синхронизации блока вход чтения блока оперативной памяти служебных регистров, входы записи, подключен к выходной шине записи-чтения блока управления и обработки.

первьй вход адреса блока оперативной

кода разрешения и информационньй вход которого подключены соответственно к выходной шине записи-чтения, к вы- памяти соединен с выходом кода .адреса gg ходу адреса и к входу-выходу данных блока кодирования, информационньй блока управления и обработки, инфорвход блока оператршной памяти подключен к информационному входу устройстмационньй выход блока служебных регистров соединен с информационным входом блока кодирования, выход призмава для подключения к выходу данных

43958818

контролируемой цифровой системы, вход синхронизации блока логической обработки подключен к синхровходу устройства для подключения к выходной шине

5

управления контролируемой цифровой

системы, первый выход разрешения блока логической обработки соединен с входом синхронизации блока формирова10 ния адресов, выход которого соединен с первым входом адреса блока памяти микрокоманд, выход которого соединен с входом кода команды блока логической обработки, отличающее15 с я тем, что, с. целью повьшшния быстродействия устройства, в нем информационный вход устройства для подключения к выходу данных контролируемой цифровой системы подключен к информа20 циопному входу блока логической обработки, второй вход адреса, информационный вход и входы записи-чтения блока, памяти микрокоманд подключены соответственно к выходу адреса, вхо

25 ду-выходу данных и к выходной шине записи-чтения блока управления и обработки, выход блока памяти микрокоманд . соединен с информационным входом блока форм грования адресов, входы

30 сброса блока формирования адресов, б.лока слуткебных регистров, блока логической обработки и блока кодирования соединены с выходом начальной установки блока управления и обработки,

2р, выход признака конца контроля блока логической обработки, выход признака конца чтения зоны блока оперативной памяти и выход признака конца записи в блок оперативной памяти блока коди40 рования соединены соответственно с первым, вторым и третьим входами условий прерывания блока управления и обработки, выход синхронизации блока ..логической обработки соединен с вхо45 Дами синхронизации блока служеб- . (ных регистров блока кодирования . и с входом записи блока оперативной памяти, второй выход разрешения блока логической обработки соединен, с вхо-

мационньй выход блока служебных регистров соединен с информационным входом блока кодирования, выход призма19143958820

ка конца записи блока служебных ре- мационным входом второго с:умматора н гистров соединен с разрешающими вхо- с вторым информа1у онным входом схемы дами блока кодирования и блока логи- ; сравнения, выход которой со единен с ческой обработки и с входом признака g вторым входом третьего элемента И, конца записи текущей зоны блока one- выход которого соединен с первым вхо- ративной памяти, второй вход адреса дом сброса счетчика кодирования, вход и информационный выход которого под- сброса блока кодирования подключен к клмчены соответственно к выходу адре- входу сброса регистра кодирования и са и к входу-выходу данных блока уп- 10 к второму входу сброса счетчика коди- равления и обработки, входы признаков рования, выход регистра кодирования параллельной записи и приращения ад- соединен с вторыми информационными реса блока формирования адресов сое- входами первого и второго сумматоров, динены соответственно с первым и вто- выход переполнения которого соединен рым выходами записи блока логической 15 с вторым входом второго элемента И обработки, причем блок служебных ре- и является выходом признака конца за- гистров содержит регистр, счетчик, писи в блок оперативной памяти, блока дешифратор и элеметгг И, первый и вто- кодирования, ииформационньш выход рой входы которого являются соответ- второго сумматора является выходом .ственно входом сиыхронизации и входом 20 кода адреса блока кодирования, разрешения синхронГ захщи блока слу- 2. Устройство по п.1, от л i-i ч а жебных регистров, выход элемента И ю 0 е е с я тем, что блок логической соединен со счетным входом счетчг-гка, обработки содержит узел синхрониза- выход переполнения которого является ции, дешифратор, две схемы сравнения, выходом прггзнака кокиа записи блока 25 формг-фователь импульсов, счетчик про- служебных регистров, входы записи пусков, триггер, семь элементов М, счетчика и регистра подключены к вхо- четыре элемента ИЛИ, два элемента НЕ ду записи блока служебных регистров, и группу элементов И, причем вход де- информационные входы счетчика и ре- шифратора, первый информационный вход гистра подключены к информационном 30 первой схемы сравнения, разрешающ1Ш входу блока служебных регистров, вход вход узла синхронизацшг, первый вход дешифратора является входом кода раз- первого элемента И, входы элементов решения блока служебных регистров, И группы, первая группа разрядов пер- первый- и второй выходы деишфратора вого информационного входа второй соединены с входами разрешения соот- 35 схемы сравнения, D-вход триггера и ветственно регистра и счетчика, входы вход первого элемента НЕ образуют сброса регистра и счетчика подключены вход кода команды блока логической к входу сброса блока служебных реги- обработки, второй информационн-ый вход стров, выход регистра является инфор- первой схемы сравнения является ин мационным выходом блока служебных ре- 40 формационным входом блока лопгческой гистров, причем блок кодирования со- обработки, выход первой схемы срав- держи Г два сумматора, регистр коди- нения соединен с первыми входами вто рования, счетчик кодирования, схему рого и третьего элементов И, первьй сравнения и три элемента И, вход сии- выход дешифратора является выxoдo J хронизации блока, кодирования подклю- 45 признака конца контроля блока логичен к первым входам с первого по тре- ческой обработки, информационный вход тий элементов И, информахдионный вход узла синхронизации является входом блока кодирования подключен к первым синхронизации блока логической обра- информационным входам первого сумма- ботки, первьм выход узла синхронизатора и схемы сравнения, разрешающий gg ции является выходом синхронизации вход блока кодирования подключен к блока логической обработки, второй второму входу первого элемента И, вы- выход узла синхронизации соединен с ХОД которого соединен с входом син- вторыми входами первого и второго хронизации регистра кодирования, ин- элементов И, выходы которых соединены формационный вход которого соединён gg соответственно с первым и вторым вхо- с выходом первого сумматора, выход дами первого элемента 1ШИ, выход ко- второго элемента И соединен со счет- торого соединен со счетчиком входом ньм входом счетчика кодирования, вы- :счетчика пропусков и с первым входом ход которого соединен с первым инфор - четвертого элемента И, выходы элемен21

тов И группы соединены с второй группой разрядов первого информационного входа второй схемы сравнения, выход которой соединен с вторыми входами третьего и четвертого элементов И, выход счетчика пропусков соединен с вторым информационным входом второй схемБ сравнения, второй выход дешифратора соединен с первыми входами

второго и третьего элементов ИЛР1, выход третьего элемента И соединен с вторым входом второго элемента РШИ, выход которого соединен с первым вхо

143958822

элемента ИЛИ и явл яется первым выходом разрешения блока логической обработки, вход сброса блока логической 5 обработки, вход сброса блока normiec- кой обработки подключен к второму входу четвертого элемента ИЛИ, выход которого соединен с входом сброса счетчика пропусков и с R-входом 10 триггера, триггера и .первьй

вход седьмого элемента И соединены с выходом четвертого элемента И, выход первого элемента НЕ соединен с вторым входом седьмого элемента И, выход

„„, „ ,, .j,jji-jwi и jjici cnia л, иылид

дом пятого элемента И „ ,ер„ второй 15 которого соединен с вторь, входом

, в:,хоГГото:о°Гяв™:«г : :::::;: p™i eiLrr,

вторым выходом записи блока логичес- .«ггот п .,,,, - «г входом

олока логической обработки, выхоп

кои Обработки, вьпсод пятого элемен-третьего элемента ШИ соедшшн с хота И является первым выходом записи зодом запуска формирователя ИМПУЛЬСОВ,

блока логической обработки, выходRI.VOT, т,,,-,„г,

,t- , f.выход триггера является вторым выкоформирователя импульсов соединен с„пм ,„с, я;„

дом разрешения блока логической обвторыми входами пятого и шестого эле-работки

ментов И, с первым входом четвертого

958822

элемента ИЛИ и явл яется первым выходом разрешения блока логической обработки, вход сброса блока логической 5 обработки, вход сброса блока normiec- кой обработки подключен к второму входу четвертого элемента ИЛИ, выход которого соединен с входом сброса счетчика пропусков и с R-входом 10 триггера, триггера и .первьй

вход седьмого элемента И соединены с выходом четвертого элемента И, выход первого элемента НЕ соединен с вторым входом седьмого элемента И, выход

.j,jji-jwi и jjici cnia л, иылид

15 которого соединен с вторь, входом

e/K ffg/axfS

:&птяз/щ

f

e

. .З

ff / ffi/fff }

Pfjfff

ff ffffff/ ny/

X SViiff, S/m i/t S

fxOJ

ill

c

КХЛ

fffffff/Н/Л

E,

г I faT-U

ii

.fm д/р./

3b/xoffsf

Ci//V/ O f/2 /

ff6/xoff2S

/A///fy/

ГшжгахГ1(1

I 4 fff f I

...

fffCf

Д-/ Л5 « -/ Ц

/( ... /w7

r

f

JJ/

IT

l,.

J«

/%w

pr

ч

-F

:йгг/ У

U

jX W

Pui.5

t

O jSeCG /fe ff / ff/ AMffJ f f&//

Q/77/C/77

.J

Фаг

/r Jj 4fД-хГ/

,y

1439588

Of jt:/ ff/n / fscxfffj

ч

ff/ ff/ a3irrj J

. ffflfff /f J

0с/. Щ

S9

т

JSL

/ffS/fa3l /splsflfS/((cff(ffJ

ff .

§t/

смж

JL

ЗИП/

iiL

§s

1439588

//

о

pVy, /

I S

ff SM-ffg.

ffifiatiuu

ss

0л« /Э

flfffVffff...

.ii-a /

Xf

7

Х Ж/77

7/

/effCfiti, fflfsetiff

XffSf

yyjtf ,

/ЯЛ/

MCo.,3

ova/fO )

(ff9e

O/tffaauu

ffff..

Ш/

foflfufefoMt SCXfScuiffa/ia fe/metff jys

IffdffXiKK MK

/fffSefffffffue fffi/ftaituS

j| u-l, /y

(UysfWft MU

caiwMMt- Mf ief«a jg/Wif/f f

J

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бабкин П.А | |||

| и др.-Программируемьй активный анализатор логических состояний для эксплуатационного обслуживания цифровых систем,- Управляющие системы и машины, 1982, № 3 (59), с, 15-19. | |||

Авторы

Даты

1988-11-23—Публикация

1986-02-05—Подача