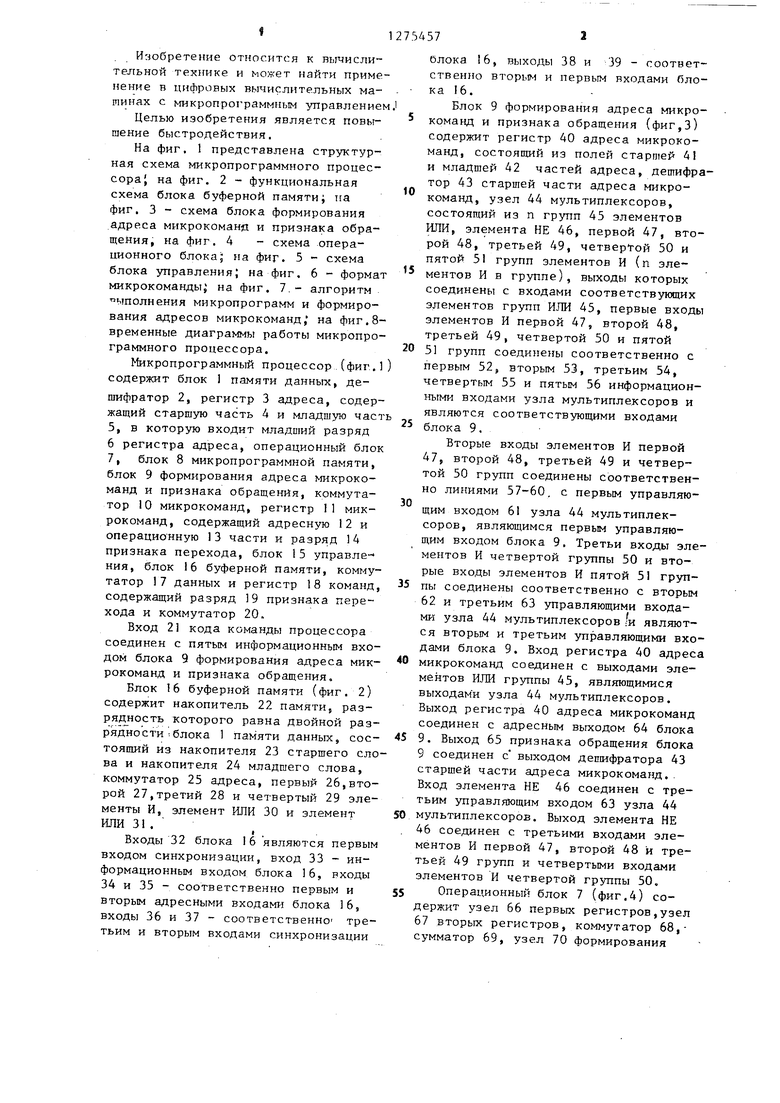

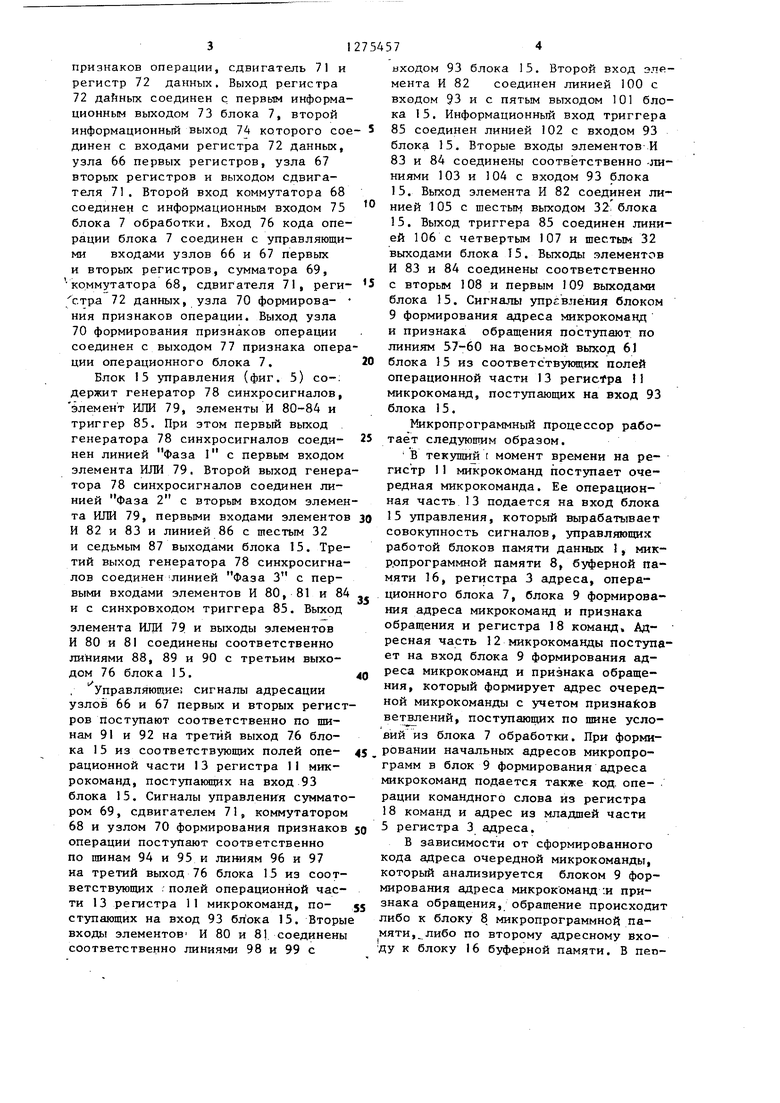

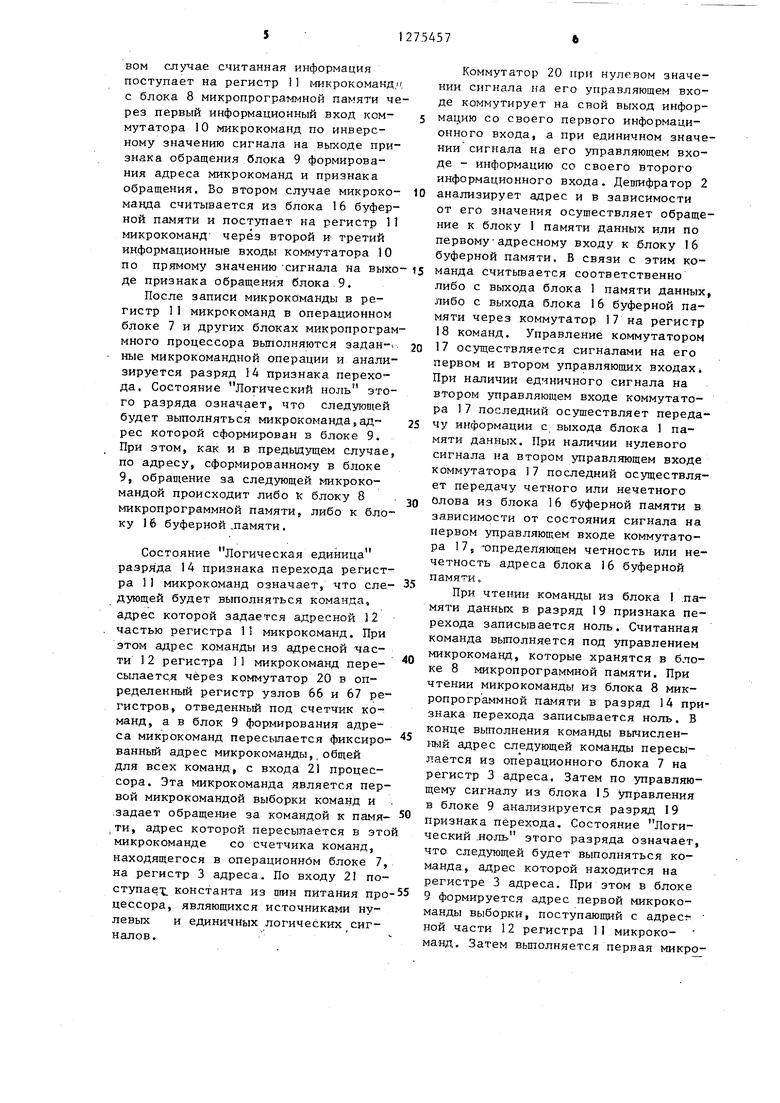

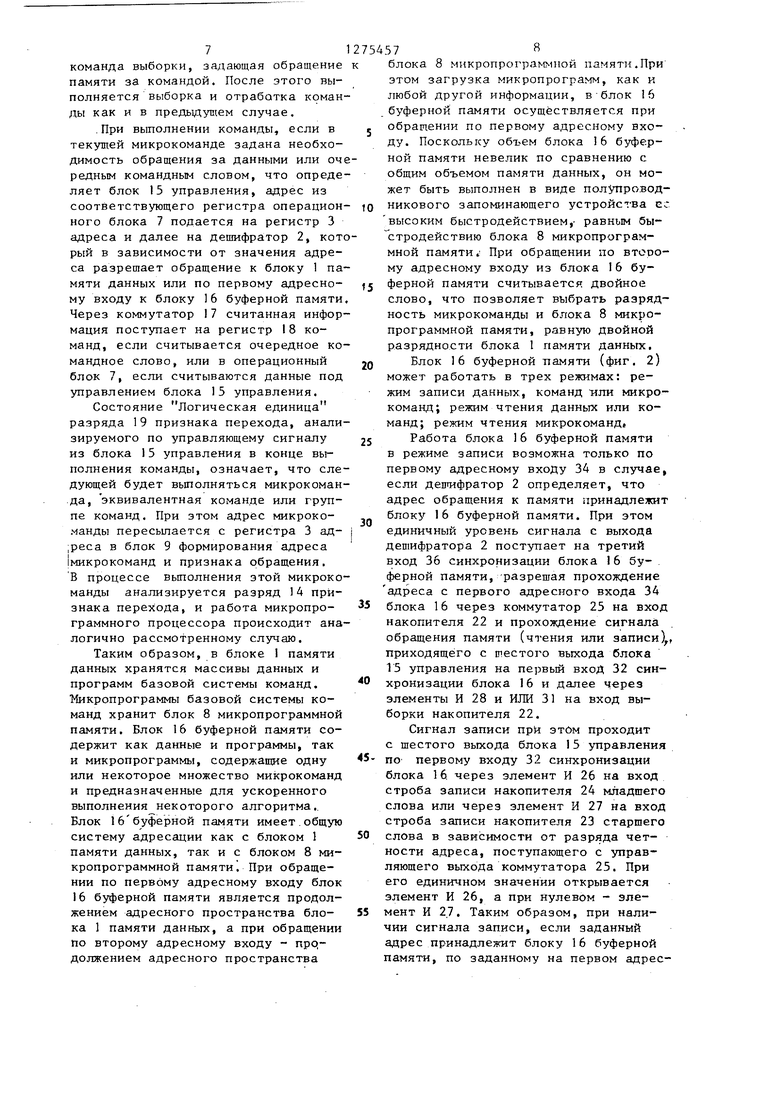

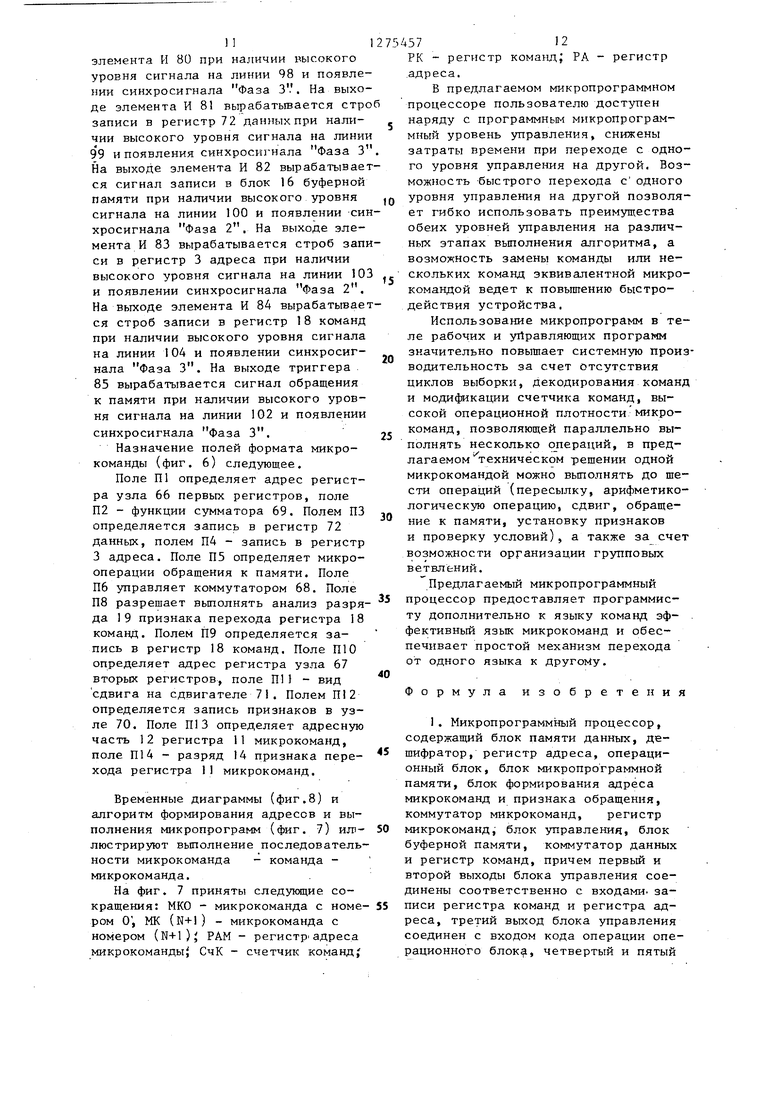

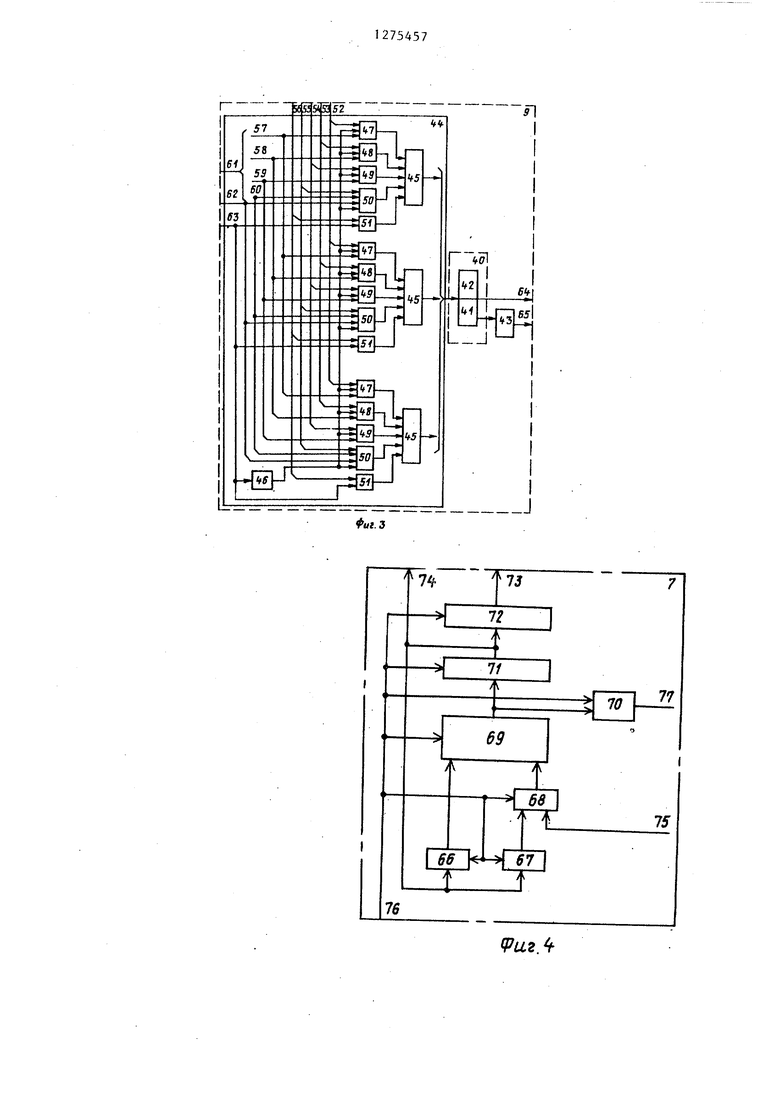

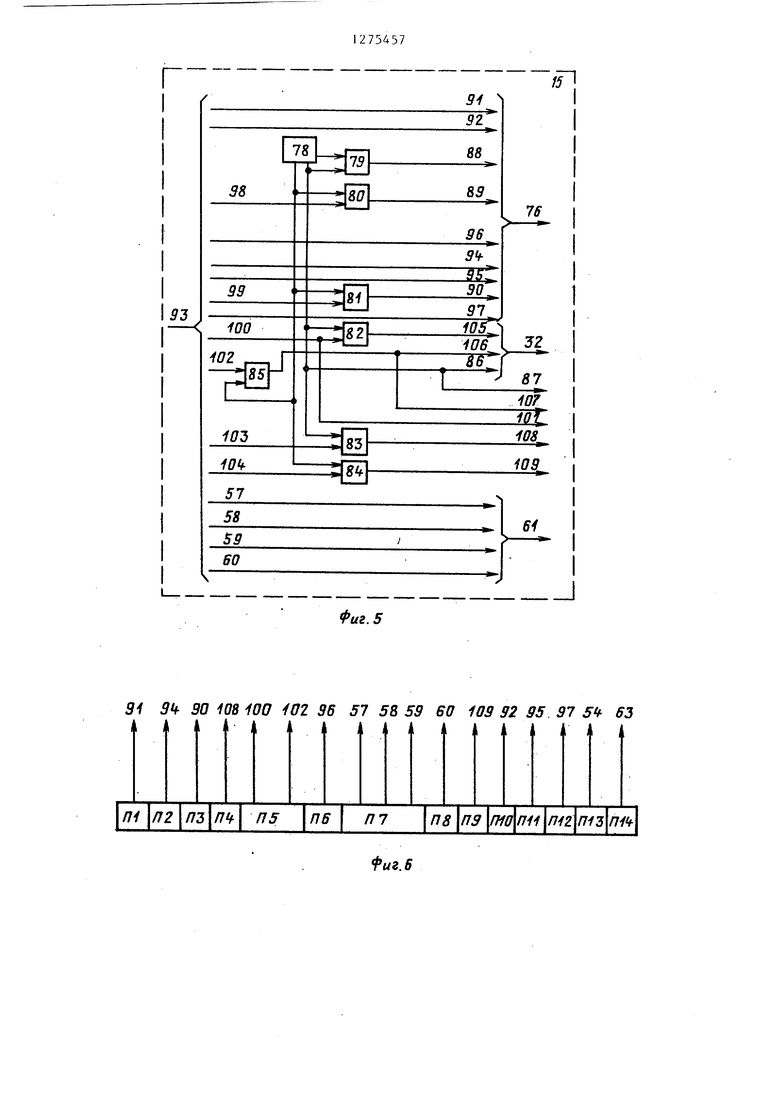

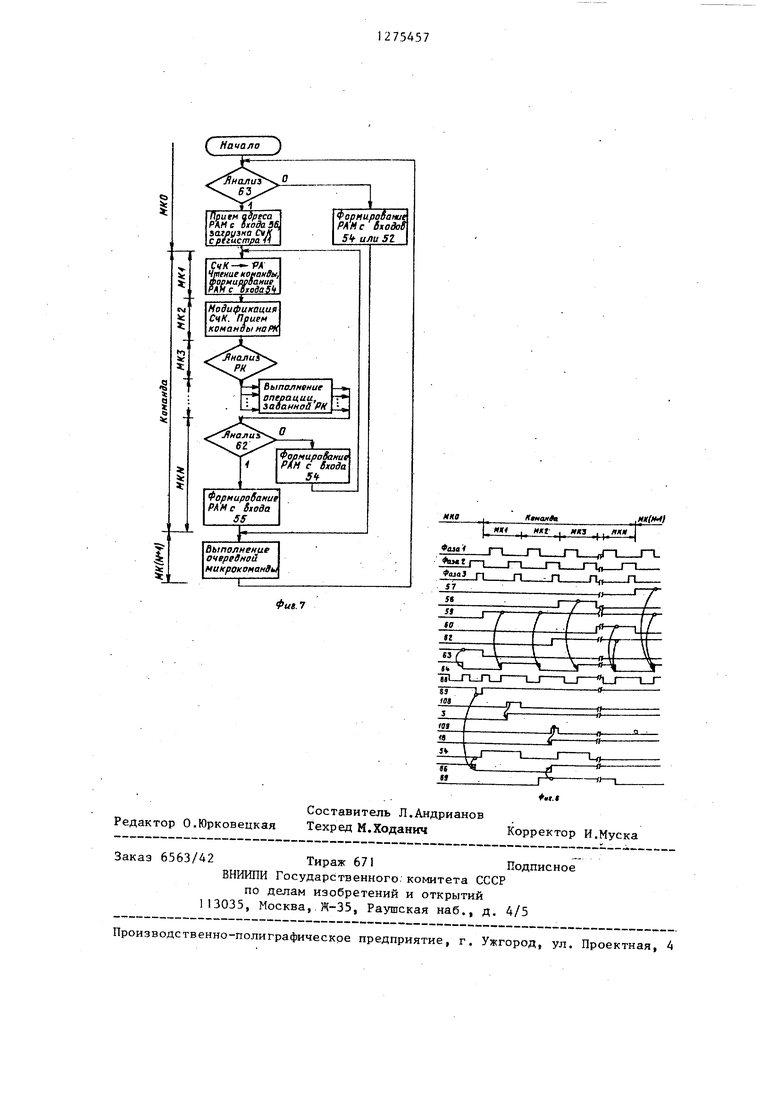

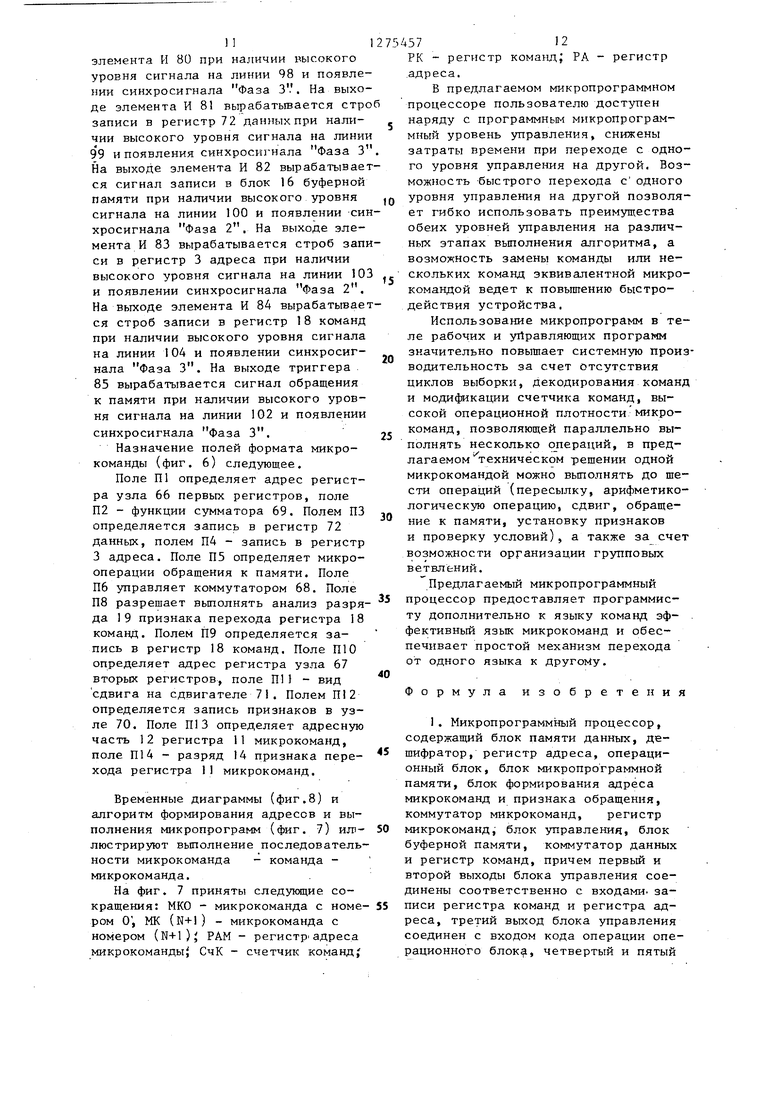

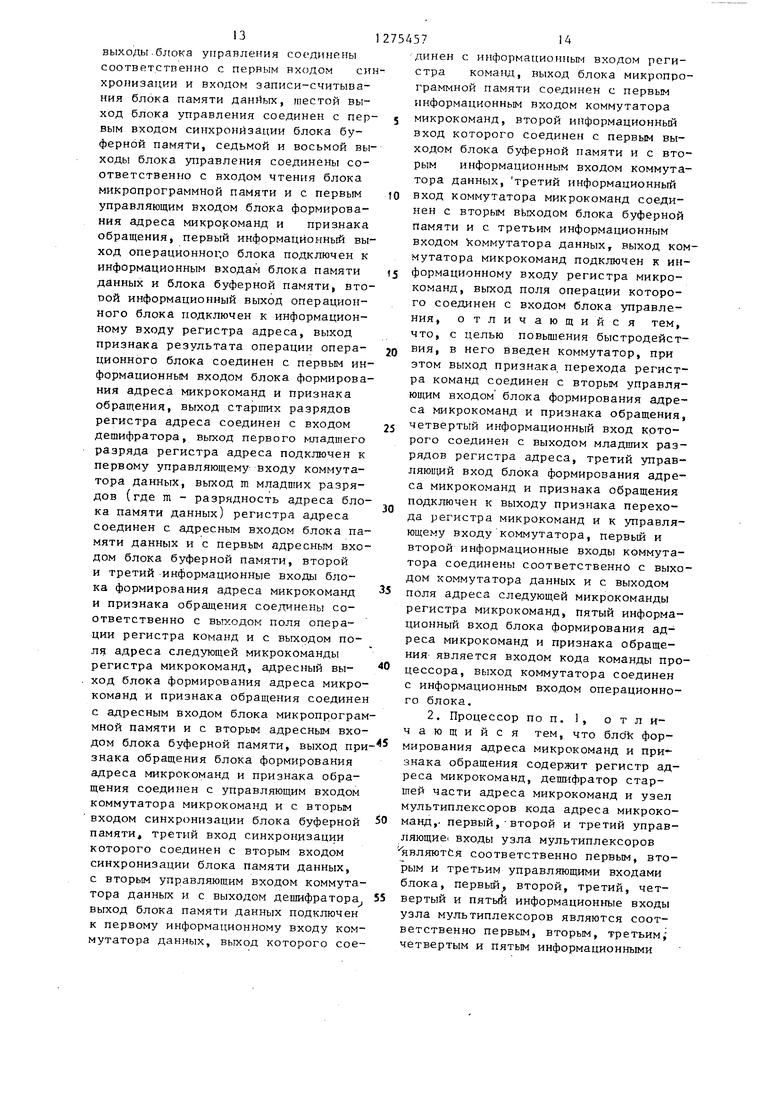

Изобретение относится к вычислительной технике и может найти применение в цифровых вычислительных машинах с микропрограммным управлением Целью изобретения является повышение быстродействия. На фиг. 1 представлена структурная схема микропрограммного процессора} на фиг. 2 - функциональная схема блока буферной памяти; па фиг. 3 - схема блока формирования адреса микрокоманд и признака обращения, на фиг. 4 - схема операционного блока; на фиг. 5 - схема блока управления; на фиг. 6 - формат микрокоманды на фиг, 7.- алгоритм выполнения микропрограмм и формирования адресов микрокоманд; на фиг.8временные диаграммы работы микропрограммного процессора. Микропрограммный процессор (фиг. содержит блок 1 памяти данных, дешифратор 2, регистр 3 адреса, содержащий старшую часть 4 и младшую час 5, в которую входит младший разряд 6 регистра адреса, операционный блок 7, блок 8 микропрограммной памяти, блок 9 формирования адреса микрокоманд и признака обращения, коммутатор 10 микрокоманд, регистр II микрокоманд, содержащий адресную 12 и операционную 13 части и разряд 14 признака перехода, блок 15 управле- ния, блок 16 буферной памяти, коммутатор 17 данных и регистр 18 команд содержащий разряд 19 признака перехода и коммутатор 20. Вход 21 кода команды процессора соединен с пятым информационным вхо дом блока 9 формирования адреса мик рокоманд и признака обращения. Блок 16 буферной памяти (фиг. 2) содержит накопитель 22 памяти, разрядность которого равна двойной раз рядности-блока 1 Памяти данных, сое тояпшй из накопителя 23 старшего сл ва и накопителя 24 младшего слова, коммутатор 25 адреса, первый 26,вто рой 27,третий 28 и четвертый 29 эле менты И, элемент ИЛИ 30 и элемент ИЛИ 31, Входы 32 блока 16 являются первы входом синхронизации, вход 33 - информационным входом блока 16, входы 34 и 35 - соответственно первым и вторым адресными входами блока 16, входы 36 и 37 - соответственно тре тьим и вторым входами синхронизации блока 6, выходы 38 и 39 - соответственно вторым и первым входами блока 16, Блок 9 формирования адреса микрокоманд и признака обращения (фиг,3) содержит регистр 40 адреса микрокоманд, состоящий из полей старшей 41 и младшей 42 частей адреса, дешифратор 43 старшей части адреса микрокоманд, узел 44 мультиплексоров, состоящий из п групп 45 элементов ИЛИ, элемента НЕ 46, первой 47, второй 48, третьей 49, четвертой 50 и пятой 51 групп злементов И (п элементов И в группе), выходы которых соединены с входами соответствующих элементов групп ИЛИ 45, первые входы злементов И первой 47, второй 48, третьей 49, четвертой 50 и пятой 51 групп соединены соответственно с первым 52, вторым 53, третьим 54, четвертым 55 и 56 информационными входами узла мультиплексоров и являются соответствующими входами блока 9. Вторые входы элементов И первой 47, второй 48, третьей 49 и четвертой 50 групп соединены соответственно линиями 57-60, с первым управляющим входом 61 узла 44 мультиплексоров, являющимся первым управляющим входом блока 9. Третьи входы элементов И четвертой группы 50 и вторые входы элементов И пятой 51 группы соединены соответственно с вторым 62 и третьим 63 управляющими входами узла 44 мультиплексоров и являются вторым и третьим управляющими входами блока 9, Вход регистра 40 адреса микрокоманд соединен с выходами элементов ИЛИ группы 45, являющимися выходами узла 44 мультиплексоров. Выход регистра 40 адреса микрокоманд соединен с адресным выходом 64 блока 9, Выход 65 признака обращения блока 9 соединен с выходом дешифратора 43 старшей части адреса микрокомагзд,. Вход элемента НЕ 46 соединен с третьим управляющим входом 63 узла 44 мультиплексоров. Выход элемента НЕ 46 соединен с третьими входами элементов И первой 47, второй 48 и третьей 49 групп и четвертыми входами элементов И четвертой группы 50, Операционный блок 7 (фиг.4) содержит узел 66 первых регистров,узел 67 вторых регистров, коммутатор 68,сумматор 69, узел 70 формирования признаков операции, сдвигатель 71 и регистр 72 данных. Выход регистра 72 дайных соединен с первым информационным выходом 73 блока 7, второй информационный выход 74 которого сое динен с входами регистра 72 данных, узла 66 первых регистров, узла 67 вторых регистров и выходом сдвигателя 71. Второй вход коммутатора 68 соединен с информационным входом 75 блока 7 обработки. Вход 76 кода операции блока 7 соединен с управляющими входами узлов 66 и 67 первых и вторых регистров, сумматора 69, коммутатора 68, сдвигателя 71, регистра 72 данных, узла 70 формирова- ния признаков операции. Выход узла 70 формирования признаков операции соединен с выходом 77 признака опера ции операционного блока 7. Блок 15 управления (фиг. 5) со-: держит генератор 78 синхросигналов, элемент ИЛИ 79, элементы И 80-84 и триггер 85. При этом первый выход генератора 78 синхросигналов соединен линией фаза I с первым входом элемента ИЛИ 79. Второй выход генера тора 78 синхросигналов соединен линией фаза 2 с вторым входом элемен та ИЛИ 79, первыми входами элементов И 82 и 83 и линией 86 с шестым 32 и седьмым 87 выходами блока 15. Третий выход генератора 78 синхросигналов соединен линией Фаза 3 с первыми входами элементов И 80, 81 и 84 и с синхровходом триггера 85. Выход элемента ИЛИ 79 и выходы элементов И 80 и 81 соединены соответственно линиями 88, 89 и 90 с третьим выходом 76 блока 15. Управляющие; сигналы адресации узлов 66 и 67 первых и вторых регист ров Поступают соответственно по шинам 91 и 92 на третий выход 76 блока 15 из соответствующих полей операционной части 13 регистра 11 микрокоманд, поступающих на вход 93 блока 15. Сигналы управления суммато ром 69, сдвигателем 71, коммутатором 68 и узлом 70 формирования признаков операций поступают соответственно по шинам 94 и 95 и линиям 96 и 97 на третий выход 76 блока 15 из соответствующих . полей операционной части 13 регистра 11 микрокоманд, поступающих на вход 93 блока 15. Вторы входы элементов- И 80 и 81. соединены соответственно линиями 98 и 99 с входом 93 блока 15. Второй вход элемента И 82 соединен линией 100 с входом 93 и с пятым выходом 101 блока 15. Информационный вход триггера 85 соединен линией 102 с входом 93 блока 15. Вторые входы элементов И 83 и 84 соединены соответственно -;шниями 103 и 104 с входом 93 блока 15. Выход элемента И 82 соединен линией 105 с шестым выходом 32. блока 15. Выход триггера 85 соединен линией 106 с четвертым 107 и шестым 32 выходами блока 15. Выходы элементов И 83 и 84 соединены соответственно с вторым 108 и первым 109 выходами блока 15. Сигналы упргвления блоком 9 формирования адреса микрокоманд и признака обращения поступают по линиям 57-60 на восьмой выход 61 блока 15 из соответствующих полей операционной части 13 регистра 11 микрокоманд, поступающих на вход 93 блока 15. Микропрограммный процессор работает следующим образом. В текупий г момент времени на регистр 11 микрокоманд поступает очередная микрокоманда. Ее операционная часть 13 подается на вход блока 15 управления, который вырабатывает совокупность сигналов, управляющих работой блоков памяти данных 1, микр.опрограммной памяти 8, буферной памяти 16, регистра 3 адреса, операционного блока 7, блока 9 формирования адреса микрокоманд и признака обращения и регистра 18 команд. Адресная часть 12 микрокоманды поступает на вход блока 9 формирования адреса микрокоманд и признака обращения, который формирует адрес очередной микрокоманды с учетом призна1сов ветвлений, поступающих по шине условий из блока 7 обработки. При формировании начальных адресов микропрограмм в блок 9 формирования адреса микрокоманд подается также код. oneрации командного слова из регистра 18 команд и адрес из младшей части 5 регистра 3 адреса. В зависимости от сформированного кода адреса очередной микрокоманды, который анализируется блоком 9 форирования адреса микрокоманд :и признака обращения, обращение происходит ибо к блоку 8. микропрограммной паяти, либо по второму адресному вхоу к блоку 16 буферной памяти. В пеоBOM случае считанная информация поступает на регистр 11 микрокоманд/, с блока 8 микропрограммной памяти через первый информационный вход коммутатора 10 микрокоманд по инверсному значению сигнала на вьгходе признака обращения блока 9 формирования адреса микрокоманд и признака обращения. Во втором случае микрокоманда считывается из блока 16 буферной памяти и поступает на регистр 11 микрокоманд через второй и третий информационные входы коммутатора 10 по прямому значению -сигнала на выхо де признака обращения блока 9.

После записи микрокоманды в регистр I1 микрокоманд в операционном блоке 7 и других блоках микропрограммного процессора вьшолняются зaдaнные микрокомандной операции и анализируется разряд 14 признака перехода. Состояние Логический ноль этого разряда означает, что следующей будет выполняться микрокоманда,адрее которой сформирован в блоке 9. При этом, как и в предыдущем случав, по адресу, сформированному в блоке 9, обращение за следующей микрокомандой происходит либо к блоку 8 микропрограммной памяти, либо к блоку 16 буферной-Памяти.

Состояние Логическая единица разряда 14 признака перехода регистра 11 микрокоманд означает, что еледующей будет выполняться команда, адрес которой задается адресной 12 частью регистра П микрокоманд. При зтом адрес команды из адресной часта 12 регистра 11 микрокоманд пересылается через коммутатор 20 в определенный регистр узлов 66 и 67 регистров, отведенный под счетчик команд, а в блок 9 формирования адреса микрокоманд пересылается фиксированный адрес микрокоманды,,общей для всех команд, с входа 21 процессора. Эта микрокоманда является первой микрокомандой выборки команд и .задает обращение за командой к памя;Ти, адрес которой пересылается в это микрокоманде со счетчика команд, находящегося в опарационнбм блоке 7, на регистр 3 адреса. По входу 21 поCTynaqt константа из пгин питания про цессора, являющихся источниками нулевых и единичных логических сигналов.

Коммутатор 20 при нулевом значении сигнала на его управляющем входе коммутирует на свой выход информацию со своего первого информационного входа, а при единичном значении сигнала на его управляющем входе - информацию со своего второго информационного входа. Дешифратор 2 анализирует адрес и в зависимости от его значения осуществляет обращение к блоку 1 памяти данных или по первому адресному входу к блоку 16 буферной памяти. В связи с этим команда считьгоается соответственно либо с выхода блока 1 памяти данных либо с выхода блока 16 буферной памяти через коммутатор 17 на регистр 18 команд. Управление коммутатором 17 осуществляется сигналами на его первом и втором управляюпшх входах При наличии единичного сигнала на втором управляющем входе коммутатора 17 последний осуществляет передачу информации с выхода блока 1 памяти данных. При наличии нулевого сигнала на втором управляющем входе коммутатора 17 последний осуществляет передачу четного или нечетного Олова из блока 16 буферной памяти в зависимости от состояния сигнала на первом управляющем входе коммутатора 17, -определяющем четность или нечетность адреса блока 16 буферной памяти,

При чтении команды из блока I .памяти данных в разряд 19 признака перехода записывается ноль. Считанная команда выполняется под управлением микрокоманд, которые хранятся в блоке 8 микропрограммной памяти. При чтении микрокоманды из блока 8 микропрограммной памяти в разряд 14 признака перехода записьшается ноль. В конце выполнения команды вычисленный адрес следующей команды пересылается из операционного блока 7 на регистр 3 адреса. Затем по управляющему сигналу из блока I5 управления в блоке 9 анализируется разр.яд 19 признака перехода. Состояние Логический .ноль этого разряда означает, что следующей будет выполняться команда, адрес которой находится на регистре 3 адреса. При этом в блоке 9 формируется адрес первой микрокоманды выборки, поступающий с адреса ной части 12 регистра 11 микрокоманд. Затем выполняется первая микро7команда выборки, задающая обращение памяти за командой. После этого выполняется выборка и отработка коман ды как и в предыдуием случае, .При выполнении команды, если в текушей микрокоманде задана необходимость обращения за данными или оч редным командным словом, что опреде ляет блок 15 управления, адрес из соответствующего регистра операцион ного блока 7 подается на регистр 3 адреса и далее на дещифратор 2, кот рый в зависимости от значения адреса разрешает обращение к блоку 1 па мяти данных или по первому адресному входу к блоку 16 буферной памяти Через коммутатор 17 считанная инфор мация поступает на регистр 18 команд, если считывается очередное ко мандное слово, или в операционный блок 7, если считываются данные под управлением блока 15 управления. Состояние Логическая единица разряда 19 признака перехода, анали зируемого по управляющему сигналу из блока 15 управления в конце выполнения команды, означает, что сле дующей будет выполняться микрокоман да, эквивалентная команде или группе команд. При этом адрес микрокоманды пересылается с регистра 3 адjpeca в блок 9 формирования адреса |микрокоманд и признака обращения. В процессе выполнения этой микроко манды анализируется разряд 14 признака перехода, и работа микропрограммного процессора происходит ана логично рассмотренному случаю. Таким образом, в блоке I памяти данных хранятся массивы данных и программ базовой системы команд. Микропрограммы базовой системы команд хранит блок 8 микропрограммной памяти. Блок 16 буферной памяти содержит как данные и программы, так и микропрограммы, содержащие одну или некоторое множество микрокоманд и предназначенные для ускоренного выполнения некоторого алгоритма.. Блок 16буферной памяти имеет.общую систему адресации как с блоком 1 памяти данных, так и с блоком 8 микропрограммной памяти. При обращении по первому адресному входу блок 16 буферной памяти является продолжением адресного пространства блока 1 памяти данных, а при обращении по второму адресному входу - пррдолжением адресного пространства 57 блока 8 микропрограммной памяти.При этом загрузка микропрограмм, как и любой другой информации, в-блок 16 буферной памяти осуществляется при обращении по первому адресному входу. Поскольку объем блока 16 буферной памяти невелик по сравнению с общим объемом памяти данных, он может быть выполнен в виде полупро.водникового запоминающего устройства ее высоким быстродействием,- равным быстродействию блока 8 микропрограммной памяти. При обращении по второму адресному входу из блока I6 буферной памяти считывается двойное слово, что позволяет выбрать разрядность микрокоманды и блока 8 микропрограммной памяти, равную двойной разрядности блока 1 памяти данных. Блок 16 буферной памяти (фиг. 2) может работать в трех режимах: режим записи данных, команд или микрокоманд; режим чтения данных или команд; режим чтения микрокоманд, Работа блока 16 буферной памяти в режиме записи возможна только по первому адресному вхоДу 34 в случае, если дешифратор 2 определяет, что адрес обращения к памяти принадлежит блоку 16 буферной памяти. При этом единичный уровень сигнала с выхода дещифратора 2 поступает на третий вход 36 синхронизации блока 16 буферной памяти, -разрешая прохождение адреса с первого адресного входа 34 блока 16 через коммутатор 25 на вход накопителя 22 и прохождение сигнала обращения памяти (чтения или записи), приходящего с шестого выхода блока 15 управления на первый вхоД 32 синхронизации блока 16 и далее через элементы И 28 и ИЛИ 31 на вход выборки накопителя 22. Сигнал записи при этим проходит с шестого выхода блока 15 управления по первому входу 32 синхронизации блока 16. через элемент И 26 на вход строба записи накопителя 24 младшего слова или через элемент И 27 на вход строба записи накопителя 23 старшего слова в зависимости от разряда четности адреса, поступающего с управляющего выхода коммутатора 25. При его единичном значении открывается элемент И 26, а при нулевом - элемент И 27. Таким образом, при наличии сигнала записи, если заданный адрес принадлежит блоку 16 буферной памяти, по заданному на первом адресном входе J адресу записывается информация с информационного входа 33, причем запись осуществляется либо в накопитель 23 старшего слова, ,пибо в накопитель 24 младшего слова в зависимости от разряда четности адреса.

Работа блока 16 в режиме чтения данных или команд происходит следующим образом. В случае, если дешифратор 2 определяет, что адрес обращения к памяти принадлежит блоку 16, единичный уровень сигнала на третьем входе 36 синхронизации блока 16 разрешает црохоадениё адреса с первого адресного входа 34 блока 16 через коммутатор 25 на вход накопителя 22, а также разрешает прохождение сигнала обращения с первого входа 32 синхронизации блока 16 через элементы И 28 и ИЛИ 31 на вход выборки накопителя 22. На выходах 38 и 39 накопителя -22 появляется считанная информация.

Режим чтения микрокоманд из блока 16 буферной памяти выполняется в случае, когда дешифратор 43 блока 9 определяет, что сформированный на регистре 40 адрес микрокоманды принадлежит .блоку 16 буферной памяти. При этом единичный уровень сигнала с вы хода 65 дешифратора 43 поступает на второй вход 37 синхронизации блока 16, разрешая прохождение адреса микрокоманды с второго адресного входа 35 блока 16 через коммутатор 25 на вход накопителя 22 и прохождение сигнала выборки микрокоманд, проходящего с шестого выхода блока 15.управления на первый вход 32 синхронизаци блока 16и далее через элемент И 29 и ИЛИ 31 на вход выборки накопителя 22i На выходах 38 и 39 накопителя 22 появляется считанная микрокоманда,

Блок формирования адреса микрокоманд и признака обращения (фиг, З) работает следующим образом.

Под управлением сигналов на управляющих входах 61-63 осуп(ествляется прием адреса микрокоманды в регистр 40 микрокоманд через группу 45 элементов ИЛИ с второго 53, третьего 54, четвертого 55 и пятого 56 информационных входов или путем дизъюнктивного вписывания с первого 52 и третьего 54 информационных входов, Единичный уровень сигнала на третьем управляющем входе 63 разрешает формирование адреса микрокоманд с пятого информационного входа 56, запрещая одновреме(-пю через элемент НЕ 46 фop шpoвaниe адреса с других направлений; .Дешифратор 43 осуществляет анализ содержимого старшей части 41 регистра 40 адреса микрокоманд и в случае его соответствия адресу, принадлежащему блоку 16 буферной памяти, формирует единичный сигнал на выходе 65 признака обращения, С адресного выхода 64 вьщается содержимое регистра 40 адреса микрокоманд.

Операционный блок 7 (фиг. 4) работает следующим образом.

В зависимости от вьтолняемой микрокоманды под воздействием управляющих сигналов на входе 76 кода операции блок осуществляет арифметикологические операции на сумматоре 69 над одним или двумя операндами, поступающими из узлов 66 и 67 первых и вторых регистров либо с информационного входа 75, вырабатывает признаки результата в узле 70 формирования признаков, осуществляет сдвиг результата арифметико-логической операции на сдвигателе 71, заносит результат операции в узлы 66 и 67 первых и вторых регистров или в регистр 72 данных, Результат операции выдается также через второй информационный выход 74 блока 7 на регистр 3 адреса. В микрокомандах перехода на программный уровень управления (раз.ряд 14 признака перехода которых равен единице), адресуемым регистром узлов 66 и 67 является счетчик команд, а остальные узлы (коммутатор 68, сумматор 69, сдвигатель 71) настраиваются с входа 76 кода операции таким образом, чтобы пропустить информацию с информационного входа 75 блока 7 через коммутатор 68, сумматор 69 и сдвигатель 71 на вход узлов 66 и 67 для ее записи. С первогоинформационного выхода 73 блока 7 выдается содержимое регистра 72 данных, а с выхода 77 признака результата операции - признаки результата операции ,

Блок 15 управления (фиг, 5) управляет работой других блоков процессора. Генератор 78 синхросигналов осуществляет синхронизацию предлагаемого устройства. На выходе элемента ИЛИ 79 вырабатывается строб выборки узлов 66 и 67 первых и вторых регистров. Строб записи в эти регистры на линии 89 вырабатывается на выходе элемента И 80 при наличии РЫСОКОГО уровня сигнала на линии 98 и появле нии синхросигнала Фаза 3.. На выхо де элемента И 81 вырабатьгоается стр записи в регистр 72 данных при наличии высокого уровня сигнала на лини 99 и появления синхросигнала Фаза 3 На выходе элемента И 82 вырабатывае ся сигнал записи в блок 6 буферной памяти при наличии высокого уровня сигнала на линии 100 и появлении си хросигнала Фаза 2. На выходе элемента И 83 вырабатывается строб зап си в регистр 3 адреса при наличии высокого уровня сигнала на линии 10 и появлении синхросигнала Фаза 2 . На выходе элемента И 84 вырабатывае ся строб записи в регистр 18 команд при наличии высокого уровня сигнала на линии 104 и появлении синхросигнала Фаза 3. На выходе триггера 85 вырабатывается сигнал обращения к памяти при наличии высокого уровня сигнала на линии 102 и появлении синхросигнала Фаза 3. Назначение полей формата микрокоманды (фиг. 6) следующее. Поле П1 определяет адрес регистра узла 66 первых регистров, поле П2 - функции сумматора 69. Полем ПЗ определяется запись в регистр 72 данных, полем П4 - запись в регистр 3 адреса. Поле П5 определяет микрооперации обращения к памяти. Поле П6 управляет коммутатором 68. Поле П8 разрешает выполнять анализ разря да 19 признака перехода регистра 18 команд. Полем П9 определяется запись в регистр 18 команд. Поле П10 определяет адрес регистра узла 67 вторых регистров, поле П11 - вид сдвига на сдвигателе 71. Полем П12 определяется запись признаков в узле 70. Поле П13 определяет адресную часть 12 регистра 11 микрокоманд, поле П14 - разряд 14 признака перехода регистра 1 микрокоманд. Временные диаграммы (фиг.8) и алгоритм формирования адресов и выполнения микропрограмм (фиг. 7) ИЛ1люстрируют выполнение последовательности микрокоманда - команда микрокоманда. На фиг. 7 приняты следующие сокращения: МКО - микрокоманда с номером О, МК (N+I) - микрокоманда с номером (N+I) РАМ - регистрадреса микрокоманды СчК - счетчик командJ РК - регистр команд; РА - регистр .адреса. В предлагаемом микропрограммном процессоре пользователю доступен наряду с программным микропрограммный уровень управления, снижены затраты времени при переходе с одного уровня управления на другой. Возможность -быстрого перехода с одного уровня управления на другой позволяет гибко использовать преимущества обеих уровней управления на различных этапах выполнения алгоритма, а возможность замены команды или нескольких команд эквивалентной микрокомандой ведет к повышению быстродействия устройства. Использование микропрограмм в теле рабочих и уйравляющих программ значительно повыщает системную производительность за счет отсутствия циклов выборки, декодирования команд и модификации счетчика команд, высокой операционной плотности микрокоманд, позволяющей параллельно выполнять несколько о пераций, в предлагаемом техническом рещении одной микрокомандой можно выполнять до щести операций (пересылку, арифметикологическую операцию, сдвиг, обращение к памяти, установку признаков и проверку условий), а также за счет возможности организации групповых ветвлений. Предлагаемый микропрограммный процессор предоставляет программисту дополнительно к языку команд эф- . фективный язык микрокоманд и обеспечивает простой механизм перехода от одного языка к другому. Формула изобретения 1. Микропрограммный процессор, содержащий блок памяти данных, дешифратор, регистр адреса, операционный блок, блок микропрограммной памяти, блок формирования адреса микрокоманд и признака обращения, коммутатор микрокоманд, регистр микрокомандj блок управления, блок буферной памяти, коммутатор данных и регистр команд, причем первый и второй выходы блока управления соединены соответственно с входами, записи регистра команд и регистра адреса, третий выход блока управления соединен с входом кода операции операционного блок, четвертый и пятый 13 выходы.блока управления соединены соответственно с первым входом син хронизации и входом записи-считывания блока памяти данйых, гпестой выход блока управления соединен с первым входом синхронизации блока буферной памяти, седьмой и восьмой выходы блока управления соединены соответственно с входом чтения блока микропрограммной памяти и с первым управляющим входом блока формирования адреса микрО} оманд и признака обращения, первый информацйонньй выход операционного блока подключен к информационным входам блока памяти данных и блока буферной памяти, ВТОРОЙ информационный выход операционного блока подключен к информационному входу регистра адреса, выход признака результата операции операционного блока соединен с первым информационнь М входом блока формирования адреса микрокоманд и признака обращения, выход старших разрядов регистра адреса соединен с входом дешифратора, выход первого младшего разряда регистра адреса подключен к первому управляющему входу коммутатора данных, выход m младших разрядов (где m - разрядность адреса блока памяти данных) регистра адреса соединен с адресным входом блока памяти данных и с первым адресным вхо дом блока буферной памяти, второй и третий -информационные входы блока формирования адреса микрокоманд и признака обращения соединень соответственно с выходом поля операции регистра команд и с выходом поля адреса следующей микрокоманды регистра микрокоманд, адресный выход блока формирования адреса микро команд и признака обращения соедине с адресным входом блока микропрограм мной памяти и с вторым адресным вхо дом блока буферной памяти, выход при знака обращения блока формирования адреса микрокоманд и признака обращения соединен с управляющим входом коммутатора микрокоманд и с вторым входом синхронизации блока буферной памяти, третий вход синхронизации которого соединен с вторым входом синхронизации блока памяти данных, с вторым управляющим входом коммута тора данных и с выходом дешифратора выход блока памяти данных подключен к первому информационному входу ком мутатора данных, выход которого сое 571динен с информациомныг-1 входом регистра команд, выход блока микропрограммной памяти соединен с первым информационным входом коммутатора микрокоманд, второй информационный вход которого Соединен с первым выходом блока буферной памяти и с вторым информационнь м входом коммутатора данных, третий информационный вход коммутатора микрокоманд соединен с вторым выходом блока буферной памяти и с третьим информационным входом Коммутатора данных, выход коммутатора микрокоманд подключен к информациониому входу регистра микрокоманд, выход поля операции которого соединен с входом блока управления, отличающийся тем, что, с целью повышения быстродейстВИЯ, в него введен коммутатор, при этом выход признака, перехода регистра команд соединен с вторым управляющим входом блока формирования адреса микрокоманд и признака обращения, четвертый информационный вход которого соединен с выходом младших разрядов регистра адреса, третий управляюuy й вход блока формирования адреса микрокоманд и признака обращения подключен к выходу признака перехода регистра микрокоманд и к управляющему входу коммутатора, первый и второй информационные входы коммутатора соединены соответственно с выходом коммутатора данных и с выходом поля адреса следующей микрокоманды регистра микрокоманд, пятый информационный вход блока формирования адреса микрокоманд и признака обращения является входом кода команды процессора, выход коммутатора соединен с информационным входом операционного блока. 2. Процессор по п, 1, отличающийся тем, что блоК формирования адреса микрокоманд и при- знака обращения содержит регистр адреса микрокоманд, дешифратор старшей части адреса микрокоманд и узел мультиплексоров кода адреса микрокоманд,, первый, второй и третий управляющие, входы узла мультиплексоров являются соответственно первым, вторым и третьим управляющими входами блока, первый второй, третий, четвертый и пятый информационные входы узла мультиплексоров являются соответственно первым, вторым, третьим, четвертым и пятым информационными 5 - 127 входами блока, выход узла мультиплексоров соединен с информационным входом регистра адреса микрокоманд,выход старших разрядов регистра адреса микрокоманд соединен с входом дешифратора старшей части адреса микро5457команд, выход регистра адреса микрокоманд является адресным выходом блока, выход дешифратора старшей части адреса микрокоманд является выходом . признака обращения блока.

7fy

/

73

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах с микропрограммньм управлением. Цель изобретения -: повышение быстродействия. Микропрограммный процессор содержит блок памяти данньтх, депшфратор, регистр адреса, операционный блок, блок микропрограммной памяти, блок формирования адреса и признака обращения, коммутатор микрокоманд, регистр микрокоманд, блок управления, блок буферной памяти, коммутатор данных, регистр команд и коммутатор. Цель достигается указанной совокупностью признаков. (Л I 3. п. ф-лы, 8 ил. с 1C ел 4i сд vj

f

77

70

VU2

Г

/Л

jy 52

78

88

38

tjSJ

8S

76

39

38

53

100

WZ

97

ml

i06

Ml

fJ3

3

58 9i 9Ц- 90 i08 iOO 102 96 57 SB 59 60

iOS

109

61

1I

Фиг. 5

iuB.S 103 92 95 97 Stf 63

| Патент CDIA № 3859636, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хассон С | |||

| Микропрограммное управление | |||

| - М.: Мир, 1973 | |||

| Микропрограммный процессор | 1978 |

|

SU752341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Фельдман Б.Я., Панферов Б.И., Громов B.C | |||

| Логическая организация процессора СМ-ЗП | |||

| - Управляющие вычислительные комплексЬ на базе малых ЭВМ: Труды ИЭУМ, вып | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-12-07—Публикация

1985-05-11—Подача