(54) УСТРОЙСТВО ДЛЯ ТРАНСЛЯЦИИ ЛОГИЧЕСКИХ АДРЕСОВ В АДРЕСА ПАМЯТИ НА МАГНИТНЫХ ДИСКАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для преобразования виртуального адреса в реальный адрес | 1979 |

|

SU1162377A3 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

1

Изобретение относигея к вычислительной технике, в частности к системам виртуальной памяти, и может быть использовано в вычислительных машинах и системах с виртуальной памятью.

В известных вычислительных системах с виртуальнои.памятью задача управления распределением памяти решается с помощью программных средств их операционных систем при наличии в небольшой степени аппаратной поддержки трансляции логических адресов в адреса оперативной памяти.

Для управления распределением внешней памяти известны следуюшие виртуаль- 5 ные методы доступа, используемые операционными системами, которые управляют виртуальной памятью: виртуальный последовательный, виртуальный индекснопоследовательный, виртуальный библиотеч- 20 ный.

Виртуальный последовательный метод доступа выбирается для тех наборов данных которые записываются и считываются последовательно. Метод доступа использует схему внешних страниц, которая хранится вместе с набором данных. Когда виртуальный последовательный набор данных открыт, схема внешних страниц переносится в основную память из таблицы соответствия относительной внешней памяти, которая используется программами методов доступа для передачи виртуальных страниц между .основной и внешней памятью.

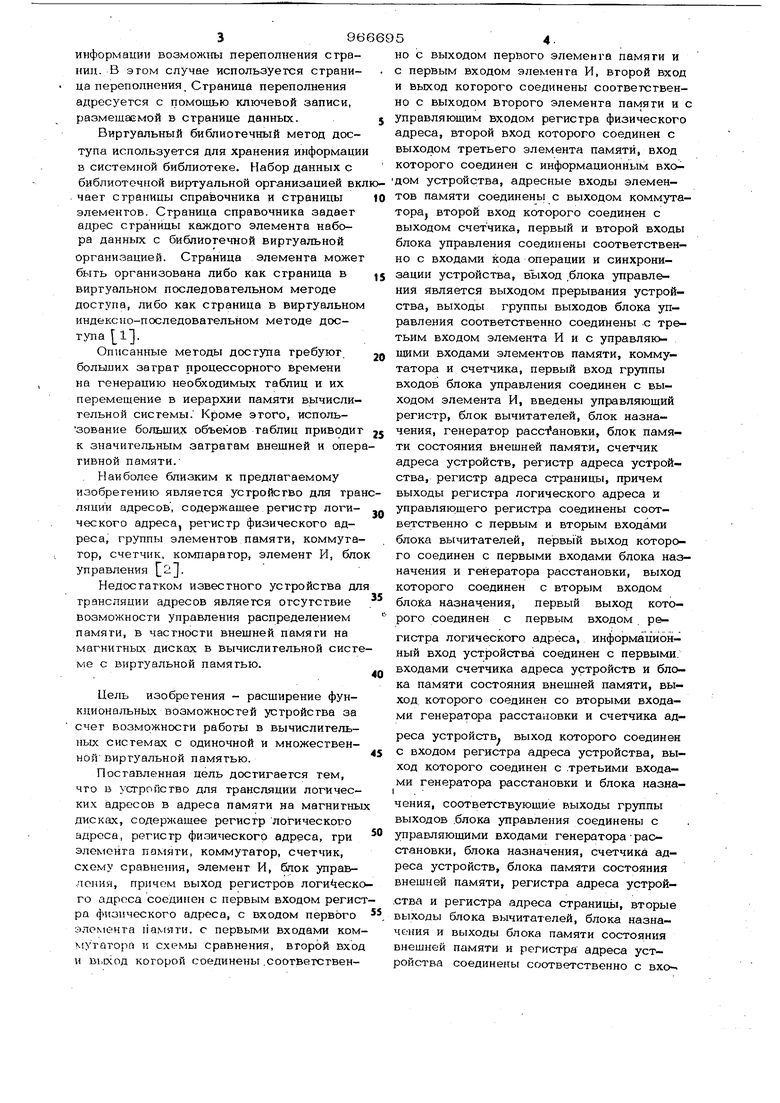

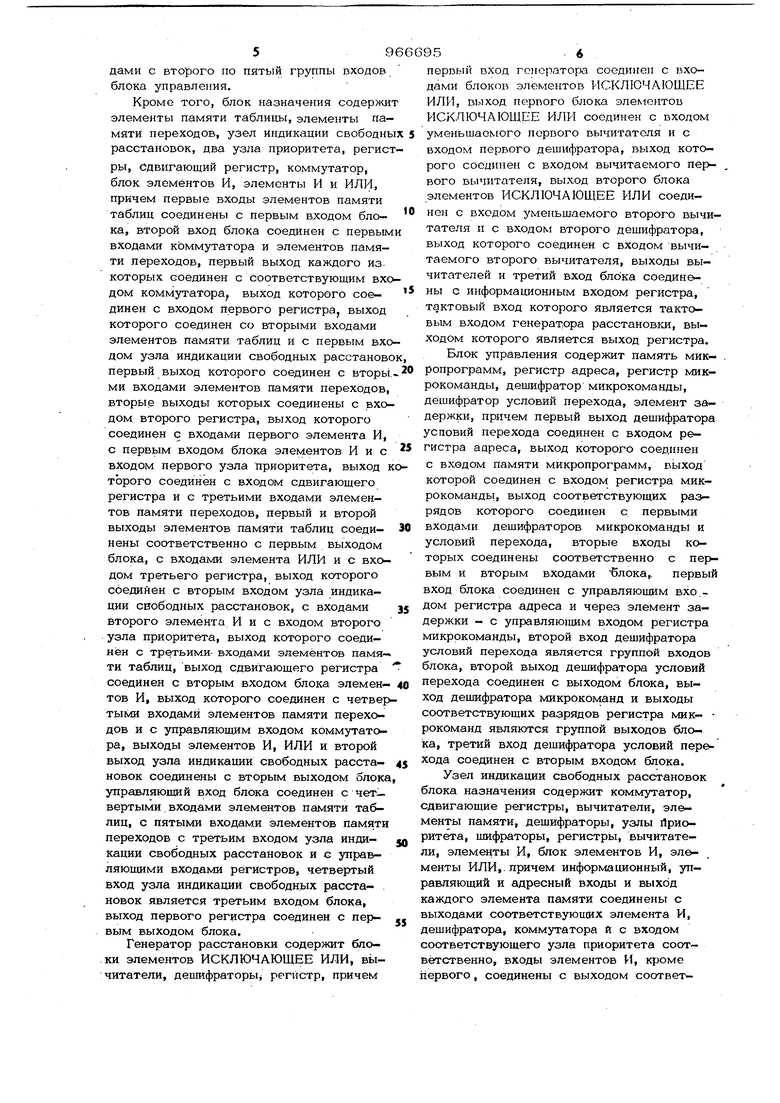

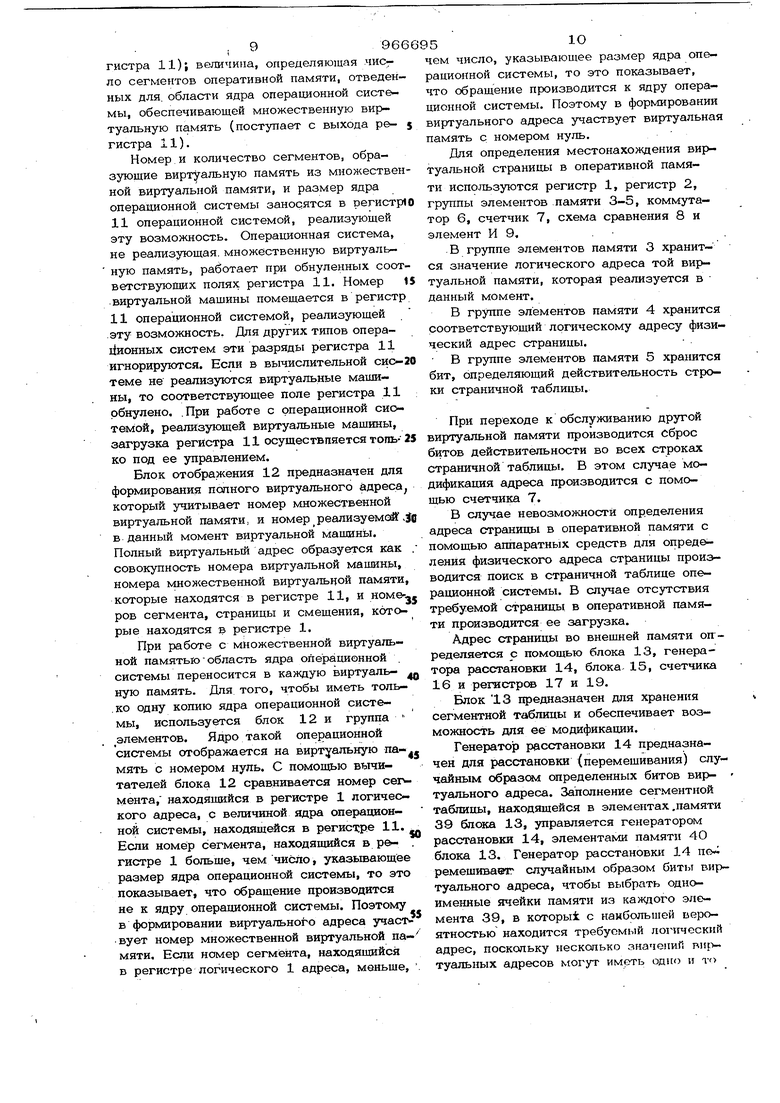

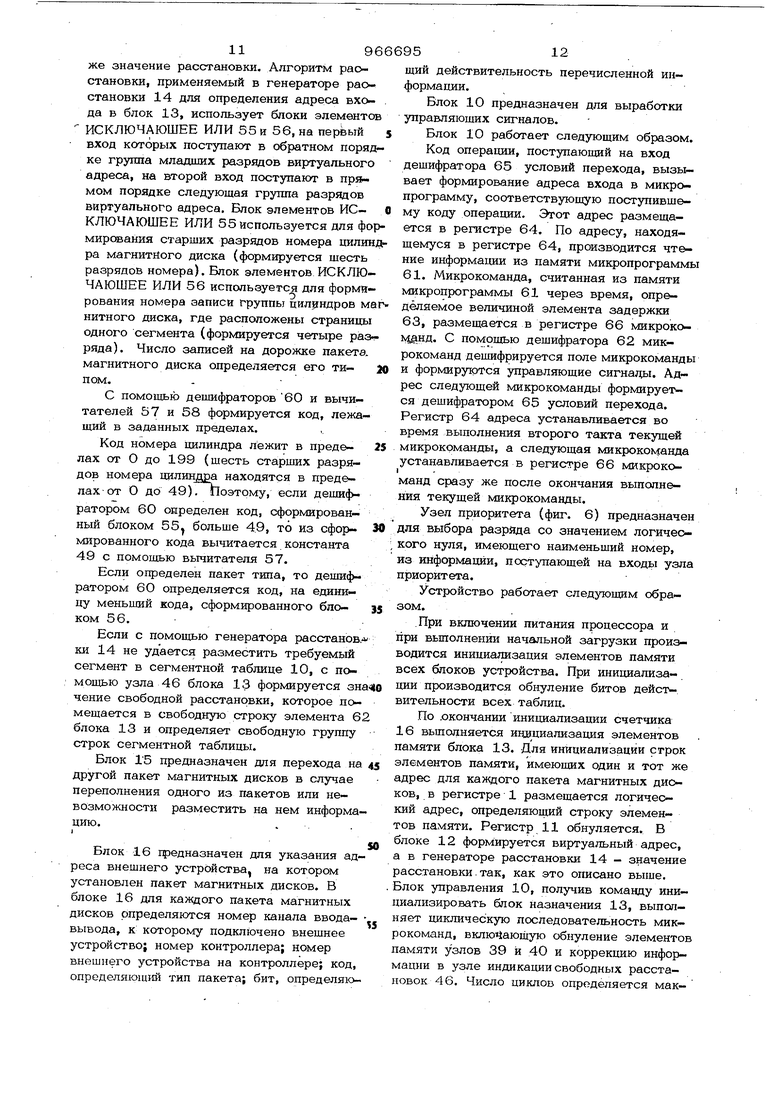

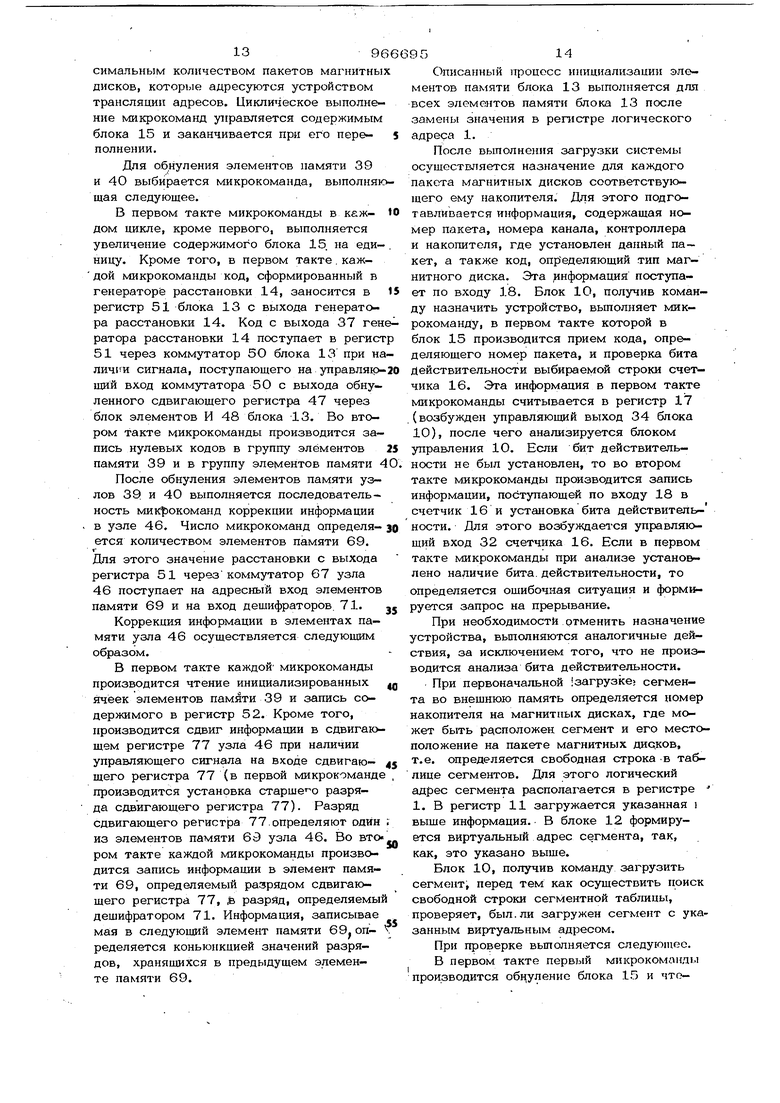

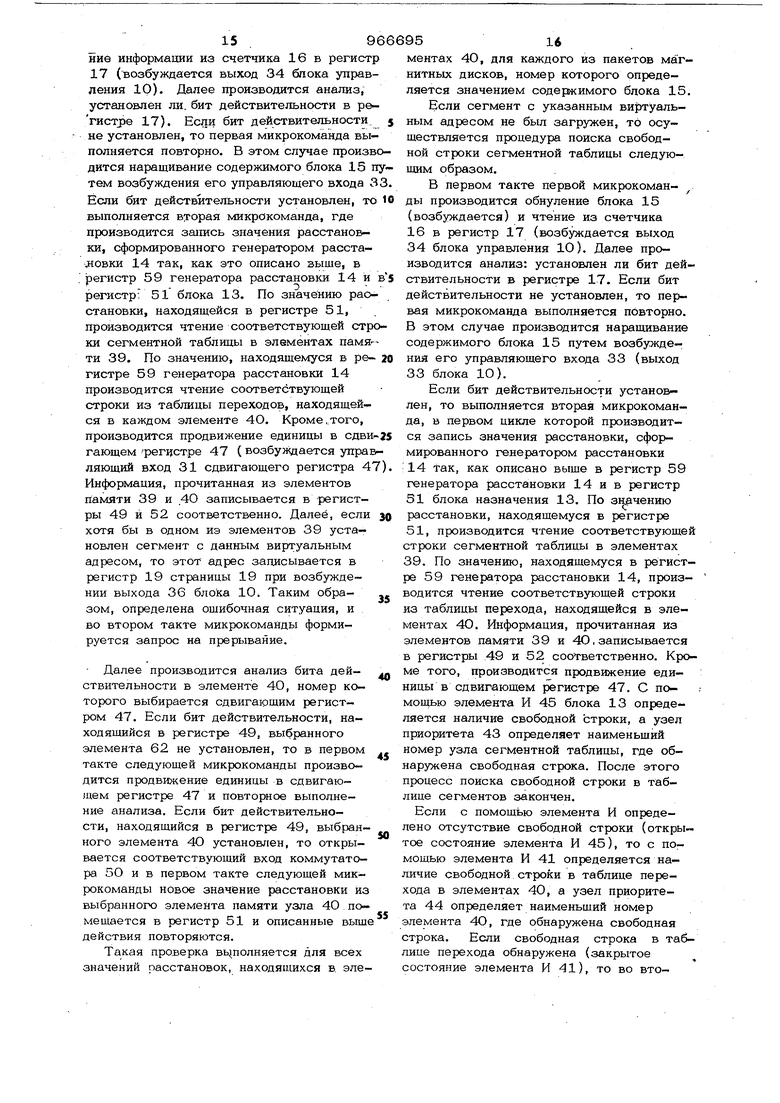

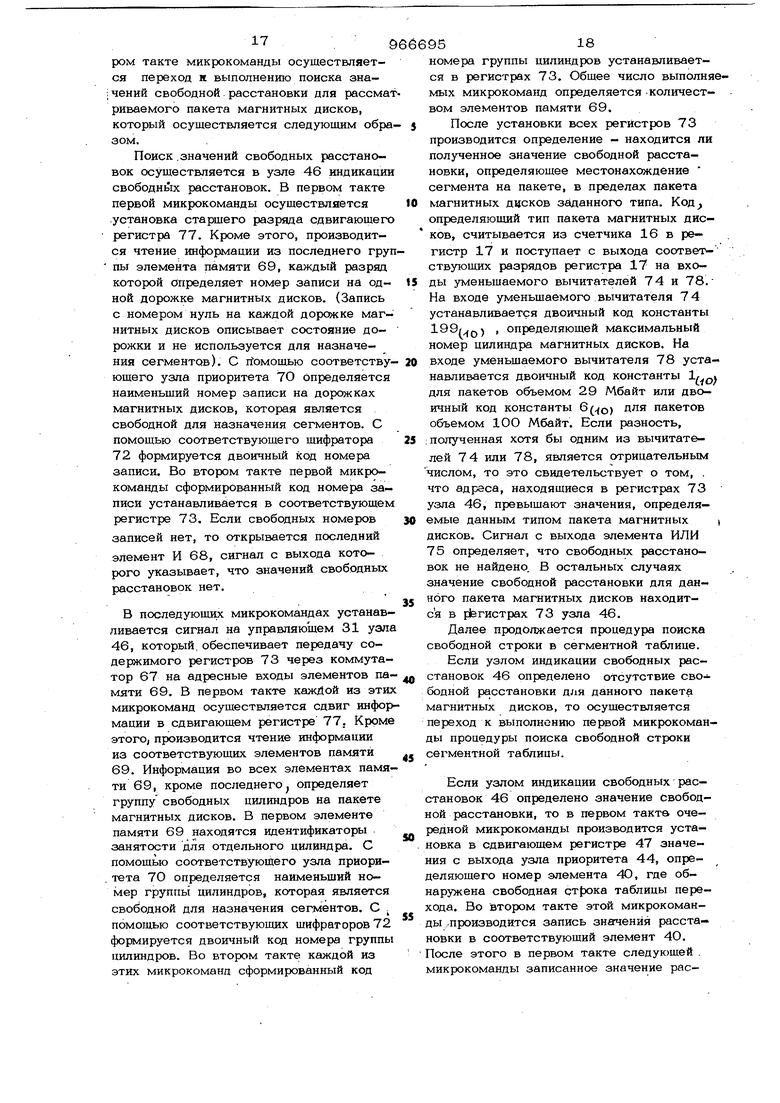

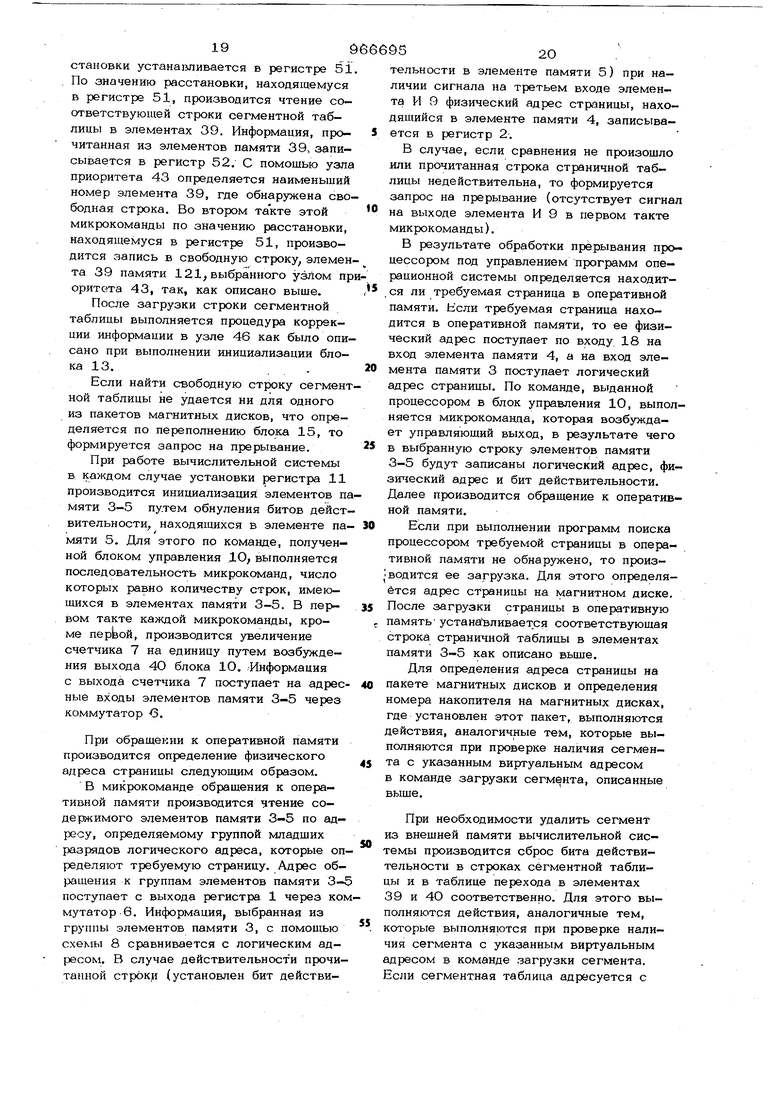

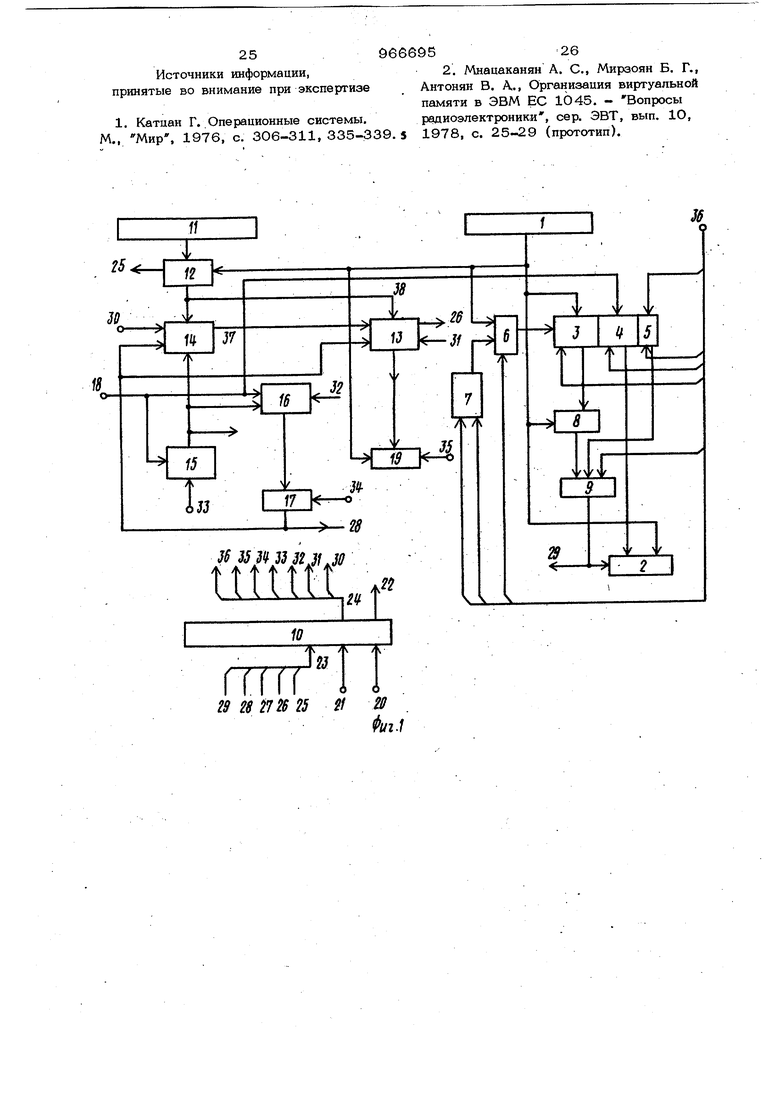

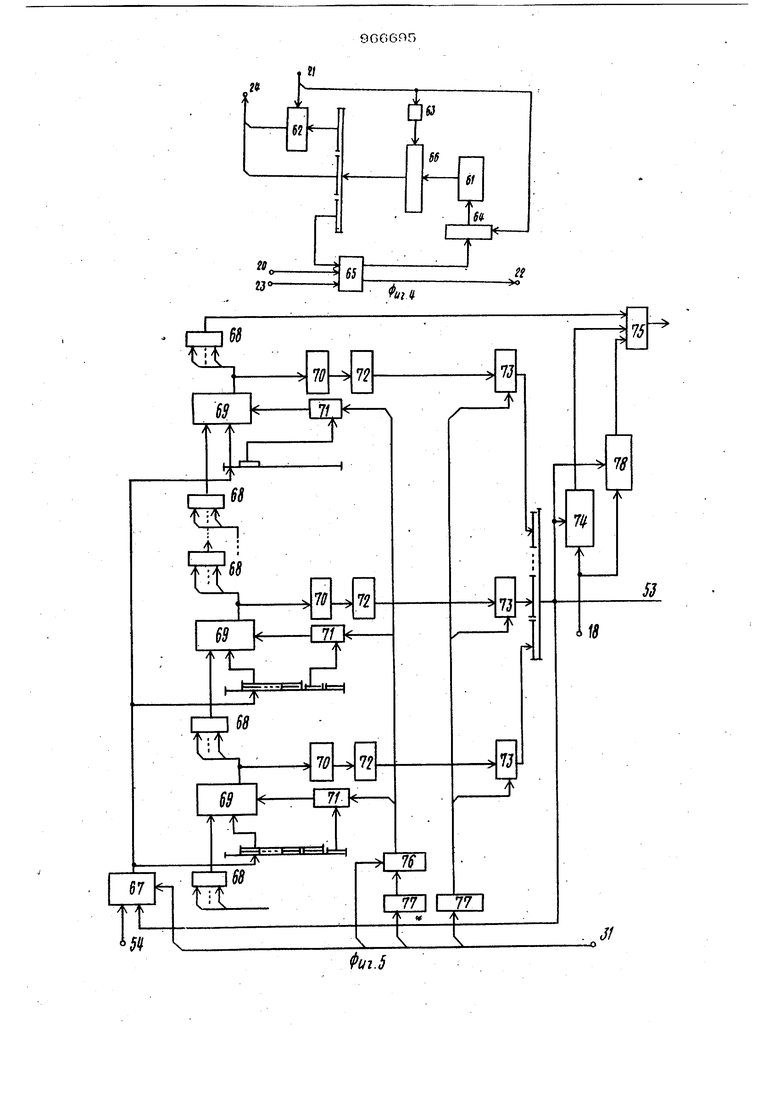

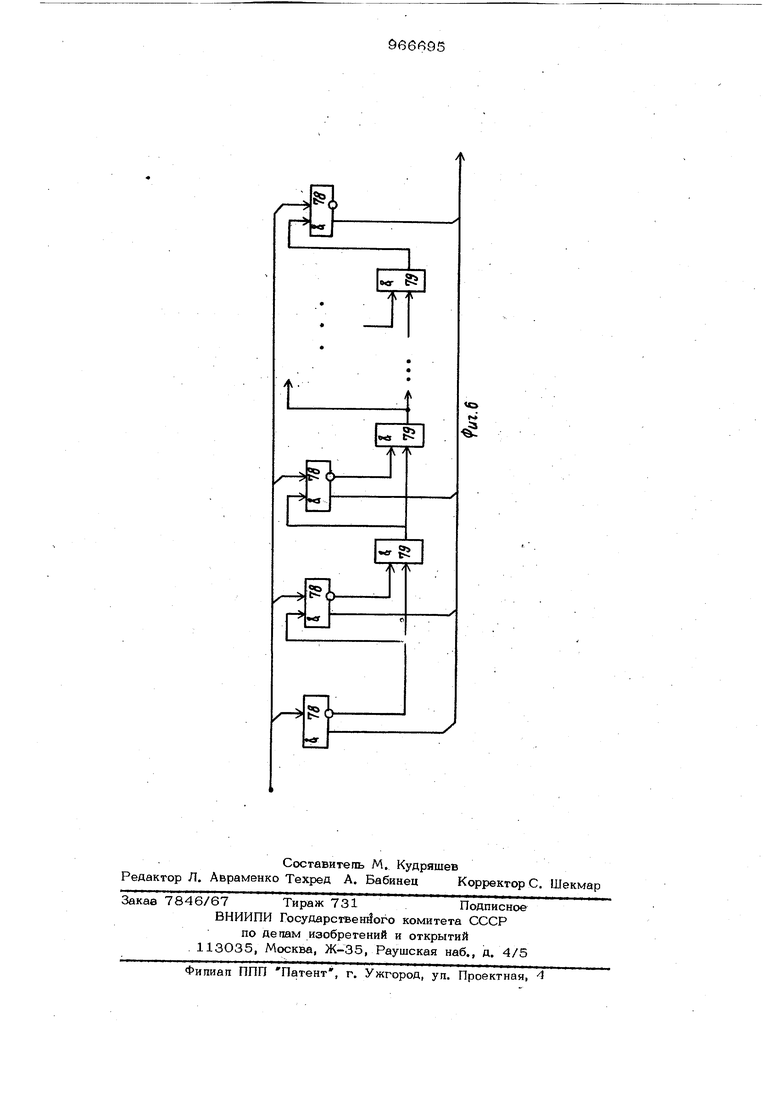

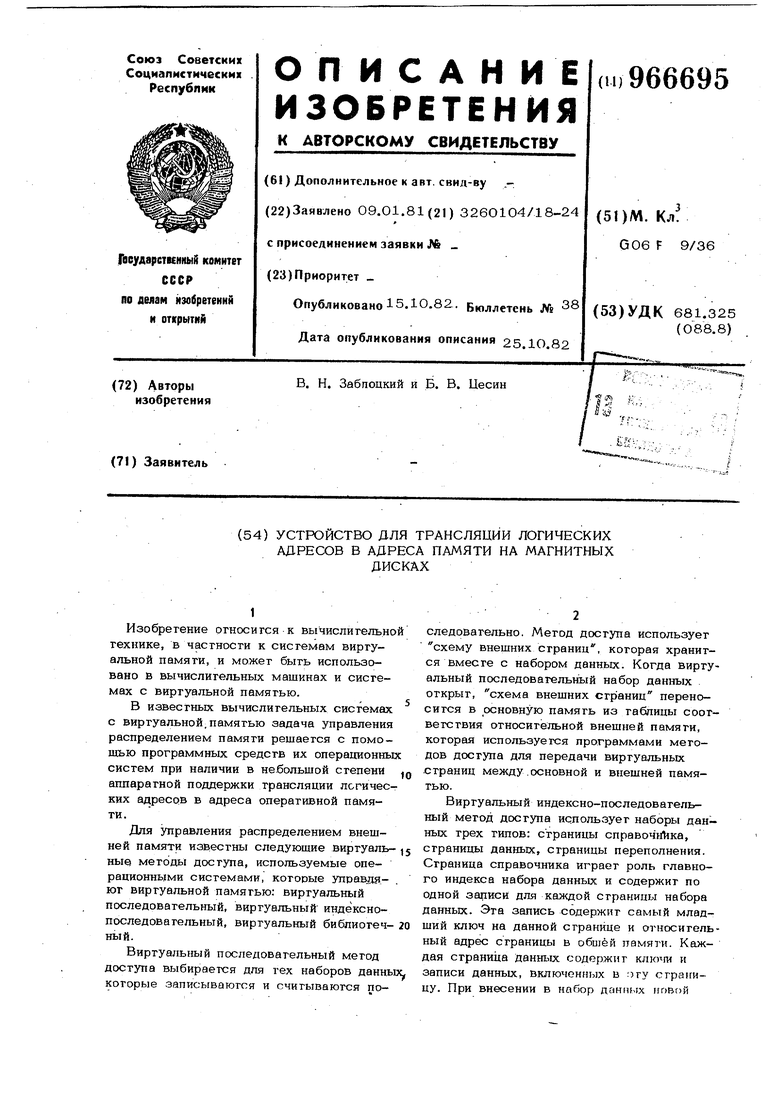

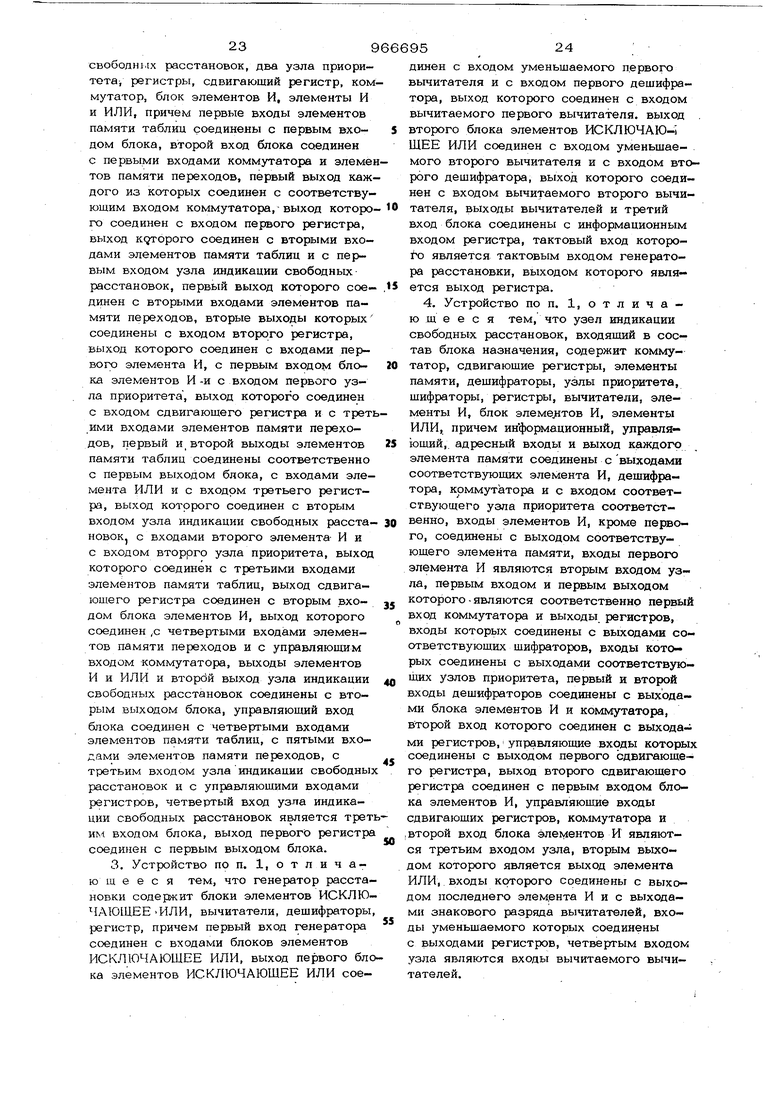

Виртуальный индексно-последовательный метод доступа использует наборы данных трех типов: страницы справочьЛка, страницы данных, страницы переполнения. Страница справочника играет роль главного индекса набора данных и содержит по одной записи для каждой страницы набора данных. Эта запись содержит самый младший ключ на данной странице и относительный адрес страницы в обшей памяти. Каждая страница содержит и записи данных, включенных в :)гу сграиицу. При внесении в набор данных 1гг|Вг)й информации возможны переполнения с границ. В этом случае используется страница переполнения Страница переполнения адресуется с помощью ключевой записи, размещаемой в странице данных. Виртуальный библиотечный метод доступа используется для хранения информаци в системной библиотеке. Набор данных с библиотечной виртуальной организацией вк чает страницы спра1вочника и страницы элементов. Страница справочника задает адрес страницы каждого элемента набора данных с библиотечной виртуальной организацией. Страница элемента мо.же быть организована либо как страница в виртуальном последовательном методе доступа, либо как страница в виртуальном индексно-последовательном методе доступа 1. Описанные методы доступа требуют больших затрат процессорного времени на генерацию необходимых таблиц и их перемещение в иерархии памяти вычислительной системы; Кроме этого, использование больщих объемов таблиц приводит к значительным затратам внешней и опер тивной памяти. Наиболее близким к предлагаемому изобретению является устройство для тран ляции адресов , содержащее регистр лог ического адреса, регистр физического адреса, группы элементов памяти, коммутатор, счетчик, компаратор, элемент И, бло управления . Недостатком известного устройства дл трансляции адресов является отсутствие возможности управления распределением памяти, в частности внещней памяти на магнитных дисках в вычислительной систе ме с виртуальной памятью. Цель изобретения - расщирение функциональных возможностей устройства за счет возможности работы в вычислительных системах с одиночной и множественной виртуальной памятью. Поставленная цель достигается тем, что в устройство для трансляции логических адресов в адреса памяти на магнитны дисках, содержащее регистр логического адреса, регистр физического адреса, три элемента памяти, коммутатор, счетчик, схему сравнс1шя, элемент И, блок управления, причем выход регистров логи 1еско го адреса соединен с первым входом регис ра физического адреса, с входом первого элемента 11амяти, с первыми входами ком мутатора и схемы сравнения, второй вход и вькод которой соединены .соответственно с выходом первого элемента памяти и с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом второго элемента памяти и с управляющим входом регистра физического адреса, второй вход которого соединен с выходом третьего элемента памяти, вход которого соединен с информационным вхоДОМ устройства, адресные входы элементов памяти соединены с выходом коммутатора, второй вход которого соединен с выходом счетчика, первый и второй входы блока управления соединены соответственно с входами кода операции и синхронизации устройства, выход ,блока управления является выходом прерывания устройства, выходы группы выходов блока управления соответственно соединены -с третьим входом элемента И и с управлякьщими входами элементов памяти, коммутатора и счетчика, первый вход группы входов блока управления соединен с выходом элемента И, введены управляющий регистр, блок вычитателей, блок назна- чения, генератор paccfaHOBKH, блок памяти состояния внещней памяти, счетчик адреса устройств, регистр адреса устройства, регистр адреса страницы, причем выходы регистра логического адреса и управляющего регистра соединены соответственно с первым и вторым входами блока вычитателей, первьгй выход которого соединен с первыми входами блока назначения и генератора расстановки, выход которого соединен с вторым входом блок:а назначения, первый выход которого соединен с первым входом регистра логического адреса, информационный вход устройства соединен с первыми, входами счетчика адреса устройств и блока памяти состояния внещней памяти, выход которого соединен со вторыми входами генератора расстановки и счетчика адреса устройств, выход которого соединен с входом регистра адреса устройства, выход которого соединен с .третьими входами генератора расстановки и блока назначения, соответствующие выходы группы выходов .блока управления соединены с управляющими входами генератора расстановки, блока назначения, счетчика адреса устройств, блока памяти состояния внещней памяти, регистра адреса устрой.ства и регистра адреса страниць, вторые выходы блока вычитателей, блока назначения и выходы блока памяти состояния внещией памяти и регистра адреса устройства соединены соответственно с вхо- 59 дами с второго но пятый группы входов блока управления. Кроме того, блок назначения содержи элементы памяти таблицы, элементы памяти переходов, узел индикации свободны расстановок, два узла приоритета, регис ры. Сдвигающий регистр, коммутатор, блок элементов И, элементы И и ИЛИ, причем первые входы элементов памяти таблиц соединены с первым входом бло- ка, второй вход блока соединен с первым входами коммутатора и элементов памяти переходов, первый выход каждого из которых соединен с соответствующим вх дом коммутатора, выход которого соединен с входом первого регистра, выход которого соединен со вторыми входами элементов памяти таблиц и с первым вх дом узла индикации свободных расстанов первый выход которого соединен с вторы ми входами элементов памяти переходов вторые выходы которых соединены с вхо дом второго регистра, выход которого соединен с входами первого элемента И, с первым входом блока элементов И и с входом первого узла приоритета, выход торого соединен с входом сдвигающего регистра и с третьими входами элементов памяти переходов, первый и второй выходы элементов памяти таблиц соединены соответственно с первым выходом блока, с входами элемента ИЛИ и с входом третьего регистра, выход которого соединен с вторым входом узла индикации свободных расстановок, с входами второго элемента И и с входом второго узла приоритета, выход которого соединён с третьими- входами элементов памяти таблиц, выход сдвигающего регистра соединен с вторым входом блока элемен- тов И, выход которого соединен с четвер тыми входами элементов памяти переходов и с управляющим входом коммутатора, выходы элементов И, ИЛИ и второй выход узла индикации свободных расстановок соединены с вторым выходом блок управляющий вход блока соединен с четвертыми . входами элементов памяти таблиц, с пятыми входами элементов памяти переходов с третьим входом узла индикации свободных расстановок и с управляющими входами регистров, четвертый вход узла индикации свободных расстановок является третьим входом блока, выход первого регистра соединен с пер- вым выходом блока. Генератор расстановки содержит бло- .ки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вычитатели, дешифраторы регистр, причем 95- 6 пероьш вход гонераторй соединен с входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом уменьшаемого первого вычитателя и с входом первого дешифратора, выход которого соединен с входом вычитаемого пер- , Бого Бычитателя, выход второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом уменьшаемого второго вычи- тателя п с входом второго дешифратора, выход которого соединен с входом вычитаемого второго вычитателя, выходы вы- читателей и третий вход блбка соединены с информационным входом регистра, тактовый вход которого является тактовым входом генераТ|Ора расстановки, выходом которого является выход регистра. Блок управления содержит память мик- . ропрограмм, регистр адреса, регистр микрокоманды, дешифратор микрокоманды, дешифратор условий перехода, элемент задержки, причем первый выход дешифратора условий перехода соединен с входом регистра адреса, выход которого соединен с входом памяти микропрограмм, вь1ход которой соединен с входом регистра микрокомандь, выход соответствующих разрядов которого соединен с первыми входами дешифраторов микрокоманды и условий перехода, вторые входы которых соединены соответственно с первым и вторым входами блока,. первый вход блока соединен с управляющим вхо.дом регистра адреса и через элемент задержки - с управляющим входом регистра микрркоманды, второй вход дешифратора условий перехода является группой входов блока, второй выход дешифратора условий перехода соединен с выходом блока, выход дешифратора микрокоманд и выходы соответствующих разрядов регистра мик- рокоманд являются группой выходов блока, третий вход дешифратора условий перехода соединен с вторым входом блока. Узел индикации свободных расстановок блока назначения содержит коммутатор, сдвигающие регистры, вычитатели, элементы памяти, дешифраторы, узлы Лриоритёта, шифраторы, регистры, вычитатели, элементы И, блок элементов И, элементы ИЛИ,.причем информационный, управляющий и адресный входы и выход каждого элемента памяти соединены с выходами соответствующих элемента И, дешифратора, коммутатора и с входом соответствующего узла приоритета соответственно, входы элементов И, кроме первого, соединены с выходом соответствующего элемс} та памяти, входы первого-элемента И являются вторым входом узла, первым входом и первым выходом которого являются первый вход коммутатора и выходы регистров, входы которых соедш1ены с выходами соответствующих шифра торов, входы которых соединены с выходами соответствующих узлов приоритета, первый и второй входы дешифраторов соединены с выходами блока элементов И и коммутатора, второй вход которого соединен с выходами регистров, управляющие входы которых сое динены с выходом первого сдвигающего регистра, выход второго сдвигающего регистра соединен с первым входом блок элементов И., управляющие входы сдвигаю щих регистров, коммутатора и второй вхо блока элементов И являются третьим вхо дом узла, вторым выходом которого явля ются выход элемента ИЛИ, входы которого соединеныс выходом последнего элемента И и с выходами знакового разряда вычитателей, входы уменьщаемого которых соединены с выходами регистров, че вертым входом узла являются входы вычитаемого вычитателей. На фиг 1 приведена структурная схема устройства для трансляции логических адресов в адреса памяти на магнитных дисках; на фиг. 2 - структурная схема блока назначения; на фиг. 3 - функциональная схема генератора расстановки; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - функциональная схема узла индикации свободных расстановок; на фиг. 6 - функциональная схема узла приоритета. Устройство для трансляции логических адресов, в вдреса памяти на магнитных дисках (фиг. 1) содержит регистр 1 логического адреса, регистр 2 физического адреса, группы элементов памяти 3-5, коммутатор 6, счетчик 7, схему сравнения 8, элемент И 9, блок 10 управления управляющий регистр 11, блок 12 вычитателей, блок 13 назначения, генератор расстановки 14, блок 15 памяти состояния внешней ;памяти, счетчик 16 адреса устройств, регистр 17 адреса устройства, информационный вход 18 устройства, регистр 19 адреса страницы, вход 20 ко да операции устройства, вход 21 синхронизации устройства, выход 22 прерывания устройства, группу 23 входов, группу 24 выходов блока управления 10, входы; 25 29 группы входов 23 и выходы 30-36 группы выходов 24 блока управления 1О выход 37 генератора расстановки 14, выход 38 блока вычитателей 12. Блок назначения 13 (фиг. 2) содержит вычитатели, группу элементов памяти таблиц 39, группу элементов памяти переходов 40, элемент И 41, элемент ИЛИ 42, узлы приоритета 43 и 44, элемент И 45, узел 46 индикации свободных расстановок, регистр 47 сдвига, блок 48 элементов И, регистр 49, коммутатор 50, регистр 51 и 52, выход 53 и вход 54 узла 46. Генератор расстановки 14 (фиг. 3) содержит блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 55 и 56, вычитатели 57 и 58, регистр 5Q, дешифраторы 60. Блок управления Ю (фиг. 4) содержит память 61 микропрограмм, дешифратор 62 микропрограмм, элемент задержки 63, регистр 64 адреса, дешифратор 65 условий, регистр 66 микрокоманды. Узел индикации свободных расстановок 46 (фиг. 5) содержит коммутатор 67, элементы И 68, элементы памяти 69, узлы приоритета 70, дешифраторы 71, шифраторы 72, регистры 73, вычитатели 74, элемент ИЛИ 75, блок 76 элементов И регистры сдвига 77. Узел приоритета (фиг. 6) содержит, группу элементов И-И-НЕ 78, группу злементов И 79. Устройство-для трансляции логических адресов в адреса памяти на магнитных дисках предназначено для преобразования логических адресов сегментов в адреса устройств внешней памяти (накопителей на магнитных дисках), а также определяет местонахождение страницы заданного сегмента на пакете магнитных дисков и в оперативной памяти. Устройство предназначено для работы в вычислительной системе, управляемой операционными cиcтe iai,iи,-которые обеспечивают одинояную или множественную виртуальную память, а также под управлением операционной системы, реализующей работу виртуальных машин. Для обеспечения этих врзможностей в управляющем регистре 11 хранятся следующие системные параметры: номер виртуальной машины, работающей в данный момент времени (поступает с выхода регистра 11); номер виртуальной памяти из множественной виртуальной памяти, которая реализуется в данный момент времени (поступает с выхода регистра 11); количество сегментов, образующих виртуальную память из множественной виртуальной памяти, которая реализуется в данный момент времени (поступает с выхода ре-

гистра 11); величина, определяющая число сегментов оперативной памяти, отведенных для. области ядра операционной системы, обеспечивающей множественную виртуальную память (поступает с выхода ре- 5 гистра 11).

Номер и количество сегментов, образующие виртуальную память из множественной виртуальной памяти, и размер ядра операционной системы заносятся в регистрю 11 операционной системой, реализующей эту возможность. Операционная система, не реализующая, множественную виртуальную память, работает при обнуленных соответствуюЕшх полях регистра 11. Номер 1$ виртуальной мащины помещается в регистр И операционной системой, реализующей эту возможность. Для других типов опера11ионных систем эти разряды регистра 11 игнорируются. Если в вычислительной сио-20 теме не реализуются виртуальные мащины, то соответствующее поле регистра 11 обнулено, .При работе с операционной сиотемой, реализующей виртуальные мащины, загрузка регистра 11 осуществляется топь-2$ ко под ее управлением.

Блок отображения 12 предназначен для формирования полного виртуального адреса который учитывает номер множественной виртуальной памяти, и номер реализуемсэЖ,й в данный момент виртуальной мащины. Полный виртуальный адрес образуется как ; совокупность номера виртуальной мащины, номера множественной виртуальной памяти, которые находятся в регистре 11, и номвг.. ров сегмента, страницы и смещения, которые находятся в регистре 1.

При работе с множественной виртуальной памятью область ядра операционной системы переносится в каждую виртуаль- ную память. Для того, чтобы иметь толь.ко одну копию ядра операционной системы, используется блок 12 и группа элементов. Ядро такой операционной системы отображается на виртуальную па-.. мять с номером нуль. С помощью вычитателей блока 12 сравнивается номер сег. мента, находящийся в регистре 1 логического адреса, с величиной ядра операционной системы, находящейся в регистсре 11. Если номер сегмента, находящийся в ре- . гистре 1 больще, чем число, указьшающее размер ядра операционной системы, то это показывает, что обращение производится не к ядру операционной системы. Поэтому в формировании виртуального адреса участ

вует номер множественной виртуальной па- мяти. Если номер сегмента, находящийся в регистре логического 1 адреса, меньще, .

чем число, указывающее размер ядра операционной системы, то это показывает, что обращение производится к ядру операционной системы. Поэтому в формировании виртуального адреса участвует виртуальна память с номером нуль.

Для определения местонахождения вир туальной страницы в оперативной памяти используются регистр 1, регистр 2, группы элементов памяти 3-5, коммутатор 6, счетчик 7, схема сравнения 8 и элемент И 9,.

В группе элементов памяти 3 хранится значение логического адреса той виртуальной памяти, которая реализуется в данный момент.

В группе элементов памяти 4 хранится соответствующий логическому адресу физический адрес страницы.

В группе элементов памяти 5 хранится бит, определяющий действительность строки страничной таблицы.

При переходе к обслуживанию другой виртуальной памяти производится сброс битов действительности во всех строк 1Х страничной таблицы. В этом случае модификация адреса производится с помощью счетчика 7.

В случае невозможности определения адреса страницы в оперативной памяти с помощью аппаратных средств для определения физического адреса страницы производится поиск в страничной таблице операционной системы. В случае отсутствия требуемой страницы в оперативной памяти производится ее загрузка.

Адрес страницы во внещней памяти определяется с помощью блока 13, генератора расстановки 14, блока 15, счетчика 16 и регистре® 17 и 19.

Блок 13 предназначен для хранения сегментной таблицы и обеспечивает возможность для ее модификации.

Генератор расстановки 14 предназначен для расстановки (перемещивания) случайным образсал определенных битов виртуального адреса. Заполнение сегментной таблицы, наход5пцейся в элементах .памяти 39 блока 13, управляется генератором расстановки 14, элементами памяти 40 блока 13. Генератор расстановки 14 ремещиваег случайным образом биты виртуального адреса, чтобы выбрать одноименные ячейки памяти из каждого элемента 39, в которы с наибольшей вероятностью находится требуемый логический адрес, поскольку несколько значениГ BIIII- туальных адресов могут иметь одно и то же значение расстановки. Алгоритм раостановки, применяемый в генераторе раостановки 14 для определения адреса входа в блок 13, использует блоки элементо ИСКЛЮЧАЮЩЕЕ ИЛИ 55 и 56, на перЬый вход которых поступают в обратном поряд ке группа младших разрвдов виртуального адреса, на второй вход поступают в прямом порядке следующая группа разрадов виртуального адреса. Блок элементов ИСКЛЮЧАЮШЕЕ ИЛИ 55 используется для фо мирования старших разрядов номера цилин ра магнитного диска (формируется шесть разрядов номера). Блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 56 используется для формирования номера записи группы цилиндров м нитного диска, где расположены страницы одного сегмента (формируется четыре раз ряда). Число записей на дорожке пакета, магнитного диска определяется его типом. С помощью дешифраторов 60 и вычи- тателей 57 и 58 формируется код, лежащий в заданных пределах. Код номера цилиндра лежит в преде- лах от О до 199 (шесть старших разрядов номера цилиндра находятся в пределах от О до 49). Поэтому, если деиш ратором 6О определен код, сформированный блоком 55. больше 49, то из сформированного кода вычитается константа 49 с помошью вычитателя 57. Если определен пакет типа, то деши4ь ратором 60 определяется код, на единицу меньший кода, сформированного блоком 56. Если с помощью генератора расстанов. ки 14 не удается разместить требуемый сегмент в сегментной таблице 10, с помощью узла 46 блока 13 формируется зна чение свободной расстановки, которое помещается в свободную строку элемента 62 блока 13 и определяет свободную группу строк сегментной таблицы. Блок Г5 предназначен для перехода на другой пакет магнитных дисков в случае переполнения одного из пакетов или невозможности разместить на нем информацию.. Блок 16 предназначен для указания адреса внешнего устройства, на которсм установлен пакет магнитных дисков. В блоке 16 для каждого пакета магнитных дисков определяются номер канала ввода- вывода, к которому подключено внешнее устройство; номер контроллера; номер внешнего устройства на контроллере; код, определяющий тип пакета; бит, определяющий действительность перечисленной информации. Блок 10 предназначен для выработки управляющих сигналов. Блок 10 работает следующим образом. Код операции, поступающий на вход дешифратора 65 условий перехода, вызывает формирование адреса входа в микропрограмму, соответствующую поступившему коду операции. Этот адрес размещается в регистре 64, По адресу, находящемуся в регистре 64, производится чтение информации из памяти микропрограммы 61. Микрокоманда, считанная из памяти микропрограммы 61 через время, определяемое величиной элемента задержки 63, размещается в регистре 66 микрокогущнд. С помошью дешифратора 62 микрокоманд дешифрируется поле микрокоманды и формируются управляющие сигналы. Адрес следующей микрокоманды формируется дешифратором 65 условий перехода. Регистр 64 адреса устанавливается во время выполнения второго такта текущей микрокоманды, а следующая микрокоманда устанавливается в регистре 66 микрокоманд сразу же после окончания выполнения текущей микрокоманды. Узел приоритета (фиг. 6) предназначен для выбора разряда со значением логического нуля, имеющего наименьший номер, из информации, поступающей на входы узла приоритета. Устройство работает следующим образом. .При включении питания процессора и при выполнении начальной загрузки производится инициазшзация элементов памяти всех блоков устройства. При инициализации производится обнуление битов действительности всех таблиц. По .окончании инициализации счетчика 16 вьшолняется ивд циализа1шя элементов памяти блока 13. Для инициализации строк элементов памяти, имеющих один и тот же адрес для каждого пакета магнитных дисков, в регистре 1 размещается логический адрес, определяющий строку элементов памяти. Регистр 11 обнуляется. В блоке 12 формируется виртуальный адрес, а в генераторе расстановки 14 - значение расстановки.так, как это описано вьние. Блок управления 10, получив команду инициализировать блок назначения 13, выполняет циклическую последовательность микрокоманд, вклю |ающую обнуление элементов памяти узлов 39 и 40 и коррекцию информации в узле индикации свободных расстановок 46. Число циклов определяется мак- регистра 51 черезкоммутатор 67 узла 46 поступает на адресный вход элементо памяти 69 и на вход дещифраторов. 71. Коррекция информации в элементах памяти узла 46 осуществляется следующим образом. В первом такте каждой микрокоманды производится чтение инициализированных ячеек элементов памяти 39 и запись содержимого в регистр 52. Кроме того, производится сдвиг информации в сдвигаю щем регистре 77 узла 46 при наличии управляющего сигнала на входе сдвигающего регистра 77 (в первой микрокоманде производится установка старшего разряда сдвигающего регистра 77). Разряд сдвигающего регистра 77.определяют один из элементов памяти 69 узла 46. Во вто« ром такте каждой микрокоманды производится запись информации в элемент памяти 69, определяемый разрядом сдвигающего регистра 77, э разряд, определяемы дешифратором 71. Информация, записывае мая в следующий элемент памяти 69 определяется коньюнкцией значений разрядов, хранящихся в предыдущем элементе памяти 69. дисков, которые адресуются устройством трансляции адресов. Циклическое выполнение микрокоманд управляется содержимым блока 15 и заканчивается при его пере- s полнении. Для обнуления элементов памяти 39 и 40 выбирается микрокоманда, выполняю-пакета магнитных дисков соответствующая следующее.щего ему накопителя. Для этого подгоВ первом такте микрокоманды в каж- Ютавливается информация, содержащая иодом цикле, кроме первого, выполняетсямер пакета, номера канала, контроллера увеличение содержимого блока 15 на еди- .и накопителя, где установлен данный па- ницу. Кроме того, в первом такте. каж-кет, а также код, определяющий тип магдои микрокоманды код, сформированный внитного диска. Эта информация поступагенераторе расстановки 14, заносится в 15ет по входу 18. Блок 10, получив команрегистр 51 блока 13 с выхода генерато-ду назначить устройство, выполняет микра расстановки 14. Код с выхода 37 гене-рокоманду, в первом такте которой в ратора расстановки 14 поступает в регистрблок 15 производится прием кода, опре51 через коммутатор 5О блока 13 при на-деляющего номер пакета, и проверка бита личии сигнала, поступающего на управля1 -20действительности выбираемой строки счетщий вход коммутатора 50 с выхода обну-чика 16. Эта информация в первом такте ленного сдвигающего регистра 47 черезмикрокоманды считывается в регистр 17 блок элементов И 48 блока 13. Во вто-(возбужден управляющий выход 34 блока ром такте микрокоманды производится за-10), после чего анализируется блоком пись нулевых кодов в группу элементов 25управления 10. Если бит действительпамяти 39 и в группу элементов памяти 40.ности не был установлен, то во втором После обнуления элементов памяти уз-такте микрокоманды производится запись лов 39 и 40 выполняется последователь-информации, поступающей по входу 18 в ность мик|)окоманд коррекции информациисчетчик 16 и установка бита действительв узле 46. Число микрокоманд определя- зоности. Для этого возбуждается управляюется количеством элементов памяти 69.щий вход 32 счетчика 16. Если в первом Для этого значение расстановки с выхода такте микрокоманды при анализе устано&ментов памяти блока 13 выполняется для всех элементов памяти блока 13 после замены значения в регистре логического адреса 1. После выполнения загрузки системы осуществляется назначение для каждого лено наличие бита, действительности, то определяется ощибочная ситуация и формируется запрос на прерывание. При необходимости отменить назначение устройства, выполняются аналогичные действия, за исключением того, что не производится анализа бита действительности. При первоначальной загрузке сегмента во внещнюю память определяется номер накопителя на магнитных дисках, где может быть расположен сегмент и его местоположение на пакете магнитных дисков. определяется свободная строка -в таблице сегментов. Для этого логический адрес сегмента располагается в регистре 1. В регистр 11 загружается указанная i выще информация. В блоке 12 формируется виртуальный адрес сегмента, так, как, это указано выще. Блок 10, получив команду загрузить сегмент, перед тем как осуществить поиск свободной строки сегментной таблицы, проверяет, был. ли загружен сегмент с указанным виртуальным адресом. При проверке вьшолняется следующее. В первом такте перв1 1й микрокоманды производится обнуление блока 15 и что- нив информации из счетчика 16 в регист 17 (возбуждается выход 34 блока управ ления 10). Далее производится анализ, установлен ли. бит действительности в ре гистре 17). Если бит действительности не установлен, то первая микрокоманда вы полняется повторно. В этом случае произ дится наращивание содержимого блока 15 тем возбуждения его управляющего входа Если бит действительности установлен, т выполняется вторая микрокоманда, где производится запись значения расстано&ки, сформированного генератором расстадовки 14 так, как это описано выше, в . регистр 59 генератора расстановки 14 и регистрГ 51 блока 13. По значению рас становки, находящейся в регистре 51, производится чтение соответствующей стр ки сегментной таблицы в элементах памя ти 39. По значению, находящемуся в регистре 59 генератора расстановки 14 производится чтение соответствующей строки из таблицы переходов, находящейся в каждом элементе 4О. Кроме „того, производится продвижение единицы в сдви гающем регистре 47 (возбуждается упра ляющий вход 31 сдвигающего регистра 4 Информация, прочитанная из элементов памяти 39 и 40 записывается в регистры 49 и 52 соответственно. Далее, если хотя бы в одном из элементов 39 установлен сегмент с данным виртуальным адресом, то этот адрес записывается в регистр 19 страницы 19 при возбуждении выхода 36 блока 10. Таким образом, определена ощибочная ситуация, и во втором такте микрокоманды формируется запрос на прерывание. Далее производится анализ бита дей- ствительности в элементе 4О, номер которого выбирается сдвигающим регистром 47. Если бит действительности, находящийся в регистре 49, выбранного элемента 62 не установлен, то в первом такте следующей микрюкоманды производится продвижение единицы в сдвигающем регистре 47 и повторное выполнение анализа. Если бит действительности, находящийся в регистре 49, выбранного элемента 4О установлен, то открывается соответствующий вход коммутатора 5О и в первом такте следующей микрокоманды новое значение расстановки из выбранного элемента памяти узла 40 помещается в регистр 51 и описанные выще действия повторяются. Такая проверка выполняется для всех значений расстановок, находящихся в элементах 4О, для каждого из пакетов магнитных дисков, номер которого определяется значением содержимого блока 15. ЕСЛИ сегмент с указанным виртуальным адресом не был загружен, то осуществляется процедура поиска свободной строки сегментной таблицы следующим образом. В первом такте первой микрокоманды производится обнуление блока 15 (возбуждается) и чтение из счетчика 16 в регистр 17 (возбуждается выход 34 блока управления 10). Далее производится анализ: установлен ли бит действительности в регистре 17. Если бит действительности не установлен, то первая микрокоманда выполняется псэвторно. В этом случае производится наращивание содержимого блока 15 путем возбуждения его управляющего входа 33 (выход 33 блока 10). Если бит действительности установлен, то выполняется вторая микрокоманда, в первом цикле которой производится запись значения расстановки, сформированного генератором расстановки 14 Так, как описано выще в регистр 59 генератора расстановки 14 и в регистр 51 блока назначения 13. По значению расстановки, находящемуся в регистре 51, производится чтение соответствующей строки сегментной таблицы в элементах 39. По значению, находящемуся в регистре 59 генератора расстановки 14, производится чтение соответствующей строки из таблицы перехода, находящейся в элементах 40. Информация, прочитанная из элементов памяти 39 и 4О, записывается в регистры 49 и 52 соответственно. Кроме того, производится продвижение единицы в сдвигающем регистре 47. С помощью элемента И 45 блока 13 определяется наличие свободной строки, а узел приоритета 43 определяет наименьщий номер узла сегментной таблицы, где обнаружена свободная строка. После этого процесс поиска свободной строки в таблице сегментов закончен. Если с помощью элемента И определено отсутствие свободной строки (открытое состояние элемента И 45), то с помощью элемента И 41 определяется наличие свободной строки в таблице перехода в элементах 4О, а узел приоритета 44 определяет наименьщий номер элемента 4О, где обнаружена свободная строка. Если свободная строка в таблице перехода обнаружена (закрытое состояние элемента И 41), то во втором такте микрокоманды осуществляется переход н выполненюо поиска зна- ;чений свободной расстановки для рассма риваемого пакета магнитных дисков, который осуществляется следующим обра зом. Поиск .значений свободных расстановок осуществляется в узле 46 индикации свободных расстановок. В первом такте первой микрокоманды осушествляется установка старшего разряда сдвигающего регистра 77. Кроме этого, производится чтение информации из последнего гру пы элемента памяти 69, каждый разряд которой определяет номер записи на одной дорожке магнитных дисков. (Запись с номером нуль на каждой дорожке магнитных дисков описывает состояние до- рожки и не используется для назначения сегментов). С помощью соответству ющего узла приоритета 70 определяется наименьший номер записи на дорожках магнитных дисков, которая является свободной для назначения сегментов. С помощью соответствующего щифратора 72 формируется двоичный код номера записи. Во втором такте первой микрокоманды сформированный код номера записи устанавливается в соответствующем регистре 73. Если свободных номеров записей нет, то открывается последний элемент И 68, сигнал с выхода которого указывает, что значений свободных расстановок нет. В последующих микрокомандах устанавливается сигнал на управляющем 31 узла 46, который, обеспечивает передачу содержимого регистров 73 через коммутатор 67 на адресные входы элементов па- мяти 69. В первом такте кажйой из этих микрокоманд осуществляется сдвиг инфо1 мации в сдвигающем регистре 77. Кроме этого, производится чтение информации из соответствующих элементов памяти 69. Информация во всех элементах памяти 69, кроме последнего, определяет группу свободных цилиндров на пакете магнитных дисков. В первом элементе памяти 69 находятся идентификаторы занятости для отдельного цилиндра. С помощью соответствующего узла приори. тета 70 определяется наименьший номер группь цилиндров, которая является свободной для назначения сегментов. С . помощью соответствующих шифраторов 72 формируется двоичный код номера группы цилиндров. Во втором такте каждой из этих микрокоманп сформированный код номера группы цилиндров устанавливается в регистрах 73. Общее число выполняемых микрокоманд определяется количеством элементов памяти 69. После установки всех регистров 73 производится определение - находится ли полученное значение свободной расстановки, определяющее местонахождение сегмента на пакете, в пределах пакета магнитных дисков заданного типа. Код определяющий тип пакета магнитных дисков, считывается из счетчика 16 в регистр 17 и поступает с выхода соответ ствутощих разрядов регистра 17 на входы уменьшаемого вычитателей 74 к 78.На входе уменьшаемого вычитателя 74 устанавливается двоичный код константы ) , определяющей максимальный номер цилиндра магнитных дисков. На входе уменьшаемого вычитателя 78 устанавливается двоичный код константы 1, для пакетов объемом 29 Мбайт или двоичный код константы для пакетов объемом 10О Мбайт. Если разность, : полученная хотя бы одним из вычитате- лей 74 или 78, является отрицательным числом, то это свидетельствует о том, . что адреса, находящиеся в регистрах 73 узла 46, превышают значения, определяемые данным типом пакета магнитных ( дисков. Сигнал с выхода элемента ИЛИ 75 определяет, что свободных расстановок не найдено. В остальных случаях значение свободной расстановки для данного пакета магнитных дисков находится в регистрах 73 узла 46. Далее продолжается процедура поиска свободной строки в сегментной таблице. Если узлом индикации свободных расстановок 46 определено отсутствие свободной расстановки для данного пакета магнитных дисков, то осуществляется переход к выполнению первой микрокоманды процедуры поиска свободной строки сегментной таблицы. Если узлом индикации свободных расстановок 46 определено значение свободной расстановки, то в первом такте очередной микрокоманды производится установка в сдвигающем регистре 47 значения с выхода узла приоритета 44, определяющего номер элемента 40, где обнаружена свободная ст{юка таблицы перехода. Во втором такте этой микрокоманды /производится запись значения расстановки в соответствующий элемент 40. После этого в первом такте следующей . микрокоманды записанное значение рас199становки устанавливается в регистре 51 По значению расстановки, находящемуся в регистре 51, производится чтение соответствующей строки сегментной таблицы в элементах 39. Информация, прючитанная из элементов памяти 39, записывается в регистр 52, С помощью узла приоритета 43 определяется наименьший номер элемента 39, где обнаружена сво бодная строка. Во втором такте этой микрокоманды по значению расстановки, находящемуся в регистре 51, производится запись в свободную cтpoкy элемен та 39 памяти 121, выбранного узЛом пр оритета 43, так, как описано выще. После загрузки строки сегментной таблицы выполняется процедура коррекции информации в узле 46 как было опи сано при выполнении инициализации блока 13.. Если найти свободную строку сегмент ной таблицы не удается ни для одного из пакетов магнитных дисков, что определяется по переполнению блока 15, то формируется запрос на прерывание. При работе вычислительной системы в каждом случае установки регистра 11 производится инициализация элементов п мяти 3-5 путем обнуления битов дейст мяти 5. Для этого по команде, полученной блоком управления 10; выполняется последовательность микрокоманд, число которых равно количеству строк, имеющихся в элементах памяти 3-5. В перовом такте каждой микрокоманды, кроме первой, производится увеличение счетчика 7 на единицу путем возбуждения выхода 4О блока 10. Информация с выхода счетчика 7 поступает на адрес ные входы элементов памяти 3-5 через коммутатор 3. При обращении к оперативной памяти производится определение физического адреса страницы следующим образом. В микрокоманде обращения к оперативной памяти производится чтение содержимого элементов памяти 3-5 по адресу, определяемому группой младших разрядов логического адреса, которые оп ределяют требуемую страницу. Адрес обращения к группам элементов памяти 3- поступает с выхода регистра 1 через ко мутатор 6. Информация, выбранная из группы элементов памяти 3, с помощью схемы 8 сравнивается с логическим адресом, В случае действительности прочитанной строки (установлен бит действи95тельности в элементе памяти 5) при наличии сигнала на третьем входе элемента И 9 физический адрес страницы, находящийся в элементе памяти 4, записывается в регистр 2. В случае, если сравнения не произошло или прочитанная строка страничной таблицы недействительна, то формируется запрос на прерывание (отсутствует сигнал на выходе элемента И 9 в первом такте микрокоманды). В результате обработки прерывания процессором под управлением программ операционной системы определяется находится ли требуемая страница в оперативной памяти. Ьсли требуемая страница находится в оперативной памяти, то ее физический адрес поступает по входу 18 на вход элемента памяти 4, а на вход элемента памяти 3 поступает логический адрес страницы. По команде, выданной процессором в блок управления 10, выполняется микрокоманда, которая возбуждает управляющий выход, в результате чего в выбранную строку элементов памяти 3-5 будут записаны логический адрес, фи- зкческШ адрес и бит действительности. Далее производится обращение к оперативной памяти. Если при выполнении программ поиска прюцессором требуемой страницы в оперитивной памяти не обнаружено, то производится ее загрузка. Для этого определяется адрес страницы на магнитном диске. После загрузки страницы в оперативную память- устанавливается соответствующая строка страничной таблицы в элементах памяти 3-5 как описано вьщ;е. Для Определения адреса страницы на пакете магнитных дисков и определения номера накопителя на магнитных дисках, где установлен этот пакет, выполняются действия, аналогичные тем, которые выполняются при проверке наличия сегмента с указанным виртуальным адресом в команде загрузки сегмента, описанные выше. При необходимости удалить сегмент из внешней памяти вычислительной системы производится сброс бита действительности в строках сегментной таблицы и в таблице перехода в элементах 39 и 40 соответственно. Для этого выполняются действия, аналогичные тем, которые выполняются при проверке наличия сегмента с указанным виртуальным адресом в команде загрузки сегмента. Если сегментная таблица адресуется с помощью таблицы перехода, то содержимое сдвигающего регистра 47 указывает элемент 4О, где осуществляется сброс бита действительнсютй. Информация с выхода блока 15, по ступающая через генератор расстановки 14 на вход блока 13, поступает на вход регистра 51 и на вход регистров 73 уз ла 46 через коммутаторы 5О.и 67 соот ветственно независимо от состояния их управляющих входов. Если процессором во время работы обнаружен сбой. по заиште сегментов или страниц, для которых устройством для трансЗляции логических адресов опрбделен адрес на магнитном диске, то про- цессор производит повторное определение адреса требуемой страницы на пакете магнитных дисков. В случае возникновекия ошибок при выполнении заданного чйс ла повторений задания, находящееся в ви туальной памяти, которая обслуживалась в момент определения ошибки, заканчивается аварийно, и область памяти, занимаемая этим заданием на пакетах магнит ных дисков, освобождается. Применение изобретения позволяет рас ширить функциональные возможности устройства за счет возможности его работы в вычислительных системах с одиночной множественной виртуальной памятью; Формула изобретения 1. Устройство для трансляции логических адресов в адреса памяти на магнитных дисках, содержащее регистр логического адреса, регистр физического адреса, три элемента памяти, коммутатор, счетчик, схему сравнения, элемент И, блок управления, причем выход регистра логического адреса соединен с первым входом регистра физического адреса, с входом первого элемента памяти, с первыми входами коммутатора и схемы сравнения, второй вход и выход которой соединены соответственно с выходом первого элемента памяти и с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом второго элемента памяти-и с управляющим входом регистра физического адреса, второй вход которого соединен с выходом третьего элемента памяти, вход которого соединен с информационным входом устройства, адресные входы элементов памяти соединены с выходом коммутатора, второй вход которого соединен с выходом счетчика, первый и второй входы блока управления соединены соответственно с входами кода операции и синхронизации устройства, выход блока управления является выходом прерывания устройства, выходы группы выходов блока управления соединены соответственно с третьим входом элемента И и с управляющими вх:одами элементов памяти, коммутатора и счетчика, первый вход группы входов блока управления соединен с. выходом элемента И, о т л и ч а ю щ е-,, е с я тем, что, с целью расщирения функциональных возможностей за счет возможности работы в вычислительных системах с одиночной и множественной виртуальной памятью, в него введены управляющий регистр, блок вычитателей, блок назначения, генератор расстановки, блок памяти состояния внешней памяти, счетчик адреса устройств,регистр адреса устройства, регистр адреса страницы, причем выходы регистра логического адреса и управляющего регистр соедине- ны соответственно с первым и вторым входами блока отображения, первый выход которого соединен с первыми входами блока назначения и генератора расстановки, выход которого соединен с вторым входом блока назначения, первый выход которого соединен с первым входом регистра логического адреса, информационный вход устройства соединен с первыми входами счетчика адреса устройств и блока памяти состояния внешней памяти, выход которого соединен с вторыми входами генератора расстановки и счетчика адреса устройств, выход которого соединен с входом регистра адреса устройства, вы- ход которого соединен с третьими входами генератора расстановки и блока назначения, соответствующие группы выходов блока управления соединены с тактовыми входами генератора расстановки, блока назначения, счетчика адреса устройств, блока памяти состояния внешней памяти, регистра адреса устройства и регистра адреса страницы, вторые выходы блока вычитателей, блока назначения и выходы блока памяти состояния внешней памяти- и регистра адреса устройства соединены соответственно с входами с второго по пятый группы входов блока управления. 2, Устройство по п. 1,-о т л и ч аю щ е е с я тем, что блок назначения содержит элементы памяти таблиц, элементы памяти переходов, узел ипликаиии свободнь х расстановок, два узла приоритета, регистры, сдвигающий регистр, ком мутатор, блок элементов И, элементы И и ИЛИ, причем первые входы элементов памяти таблиц соединены с первым входом блока, второй вход блока соединен с первыми входами коммутатора и элеме тов памяти переходов, первый выход каж дого из которых соединен с соответствующим входом коммутатора, выход которо го соединен с входом первого регистра, выход которого соединен с вторыми входами элементов памяти таблиц и с первым входом узла индикации свободныхрасстановок, первый выход которого соединен с вторыми входами элементов памяти переходов, вторые выходы которых соединены с входом второго регистра, выход которого соединен с входами первог;о элемента И, с первым входом блока элементов И -и с входом первого узла приоритета , выход которого соединен с входом сдвигающего регистра и с трет ими входами элементов памяти переходов, первый и, второй выходы элементов памяти таблиц соединены соответственно с первым выходом блока, с входами элемента ИЛИ и с входом третьего регистра, выход которого соединен с вторым входом узла индикации свободных расста HOBOKj с входами второго элемента- И и с входом вторрго узла приоритета, выход которого соединен с третьими входами элементов памяти таблиц, выход сдвигающего регистра соединен с вторым входом блока элементов И, выход которого соединен ,с четвертыми входами элементов памяти переходов и с управляющим входом коммутатора, выходы элементов И и ИЛИ и вторёй выход узла индикации свободных расстановок соединены с вторым выходом блока, управляющий вход блока соединен с четвертыми входами элементов памяти таблиц, с пятыми входами элементов памяти переходов, с третьим входом узлаиндикации свободны расстановок и с управляющими входами регистров, четвертый вход узла индикации свободных расстановок является трет им входом блока, выход первого регистр соединен с первым выходом блока. 3, Устройство по п. 1, о т л и ч аю щ е е с я тем, что генератор расста новки содержит блоки элементов ИСКЛЮ ЧАЮЩЕЕ-ИЛИ, вычитатели, дешифраторы регистр, причем первый вход генератора соединен с входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого бл ка элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом уменьщаемого дервого вычитателя и с входом первого дешифратора, выход которого соединен с входом вычитаемого первого вычитателя. выход . второго блока элементов ИСКЛЮЧАЮ-i ШЕЕ ИЛИ соединен с входом уменьшаемого второго вычитателя и с входом второго дешифратора, выход которого соединен с входом вычитаемого второго вычитателя, выходы вычитателей и третий вход блока соединены с информационным входом регистра, тактовый вход которой) является тактовым входом генератора расстановки, выходом которого является выход регистра. 4. Устройство по п. 1,отличают е е с я тем, что узел индикации свободных расстановок, входящий в состав блока назначения, содержит коммутатор, сдвигающие регистры, элементы памяти, дешифраторы, узлы приоритета, шифраторы, регистры, вычитатели, элементы И, блок элеме.нтов И, элементы ИЛИ, причем информационный, управляющий,, адресный входы и выход каждого элемента памяти соединены свыходами соответствующих элемента И, дешифратора, коммутатора и с входом соответствующего узла приоритета соответственно, входы элементов И, кроме первого, соединены с выходом соответствующего элемента памяти, входы первого элемента И являются вторым входом узла, первым входом и первым выходом которого - являются соответственно первый вход коммутатора и выходы регистров, входы которых соединены с выходами соответствующих шифраторов, входы которых соединены с выходами соответствующих узлов приоритета, первый и второй входы дешифраторов соединены с выходами блока элементов И и коммутатора, второй вход которого соединен с выходами регистров, управляющие входы которых соединены с выходом первого сдвигающего регистра, выход второго сдвигающего регистра соединен с первым входом блока элементов И, управляющие входы сдвигающих регистрюв, коммутатора и (Второй вход блока элементов И являются третьим входом узла, вторым выходом которого является выход элемента ИЛИ, входы которого соединены с выходом последнего элемента И и с выходами знакового разряда вычитателей, входы уменьшаемого которых соединены с выходами регистров, четвертым входом узла являются входы вычитаемого вычи- тателей.

2596669526

Источники информации,2. Мнацаканян А. С., Мирзоян Б. Г.,

принятые во внимание при экспертизеАнтонян В. А., Организация виртуальной

М., Мир, 1976, с. 306-311, 335-339.5 1978, с. 25-29 (прототип).

J

ГПТГ i

2S 28 t72n5 if

памяти в ЭВМ ЕС 1045. - Вопросы

38

i 33

J7 о

18

26

и

5i

52

43

if

у

W

I 50

Фиг.2

1

v

r

|«

Авторы

Даты

1982-10-15—Публикация

1981-01-09—Подача