ел

Iraii ч1 00

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении высоконадежных запоминающих устройств.

Цель изобретения - повышение быстродействия устройства.

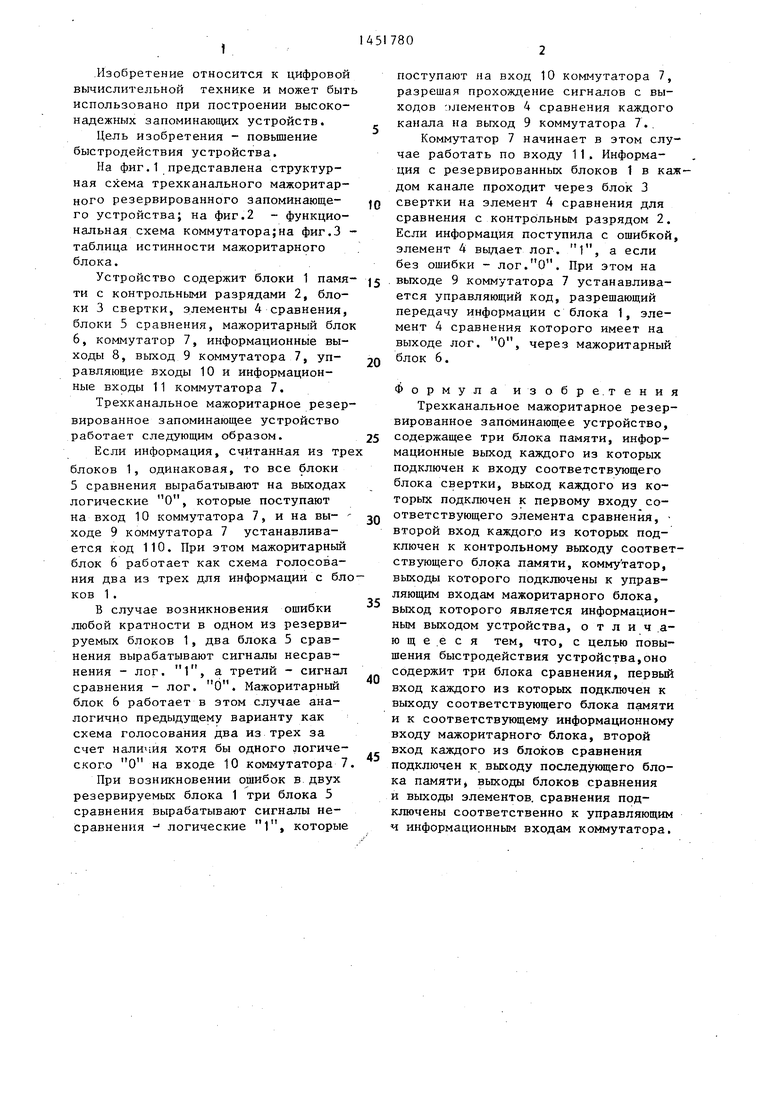

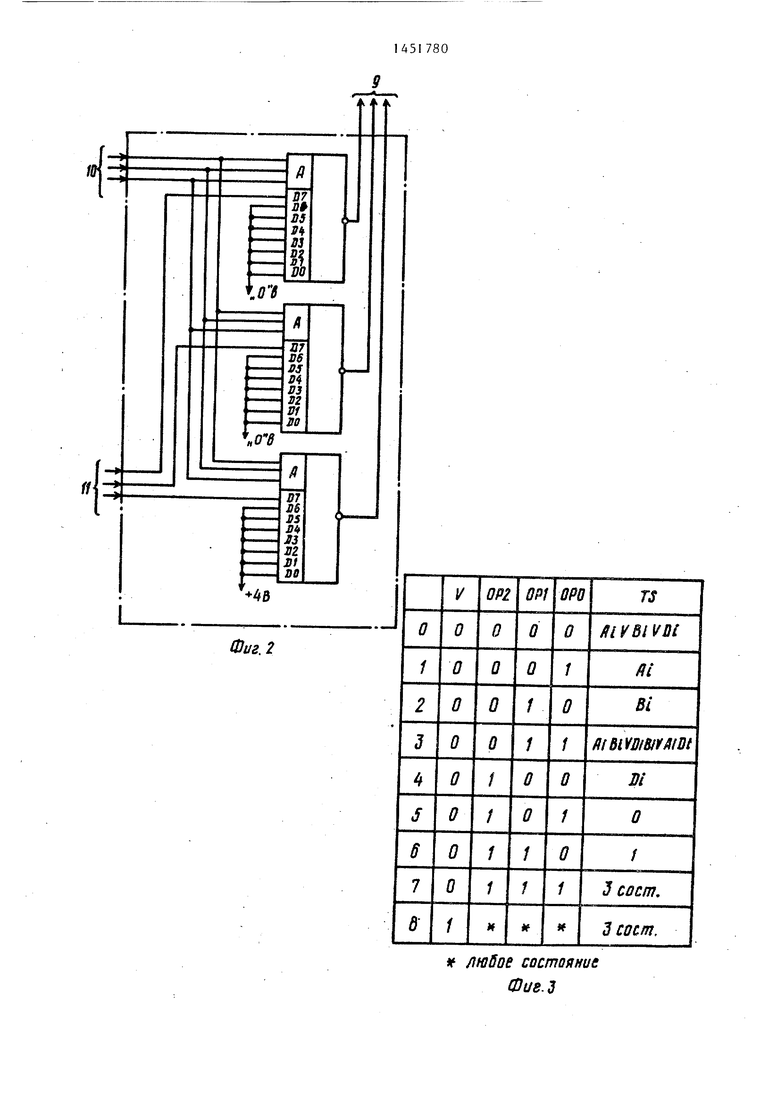

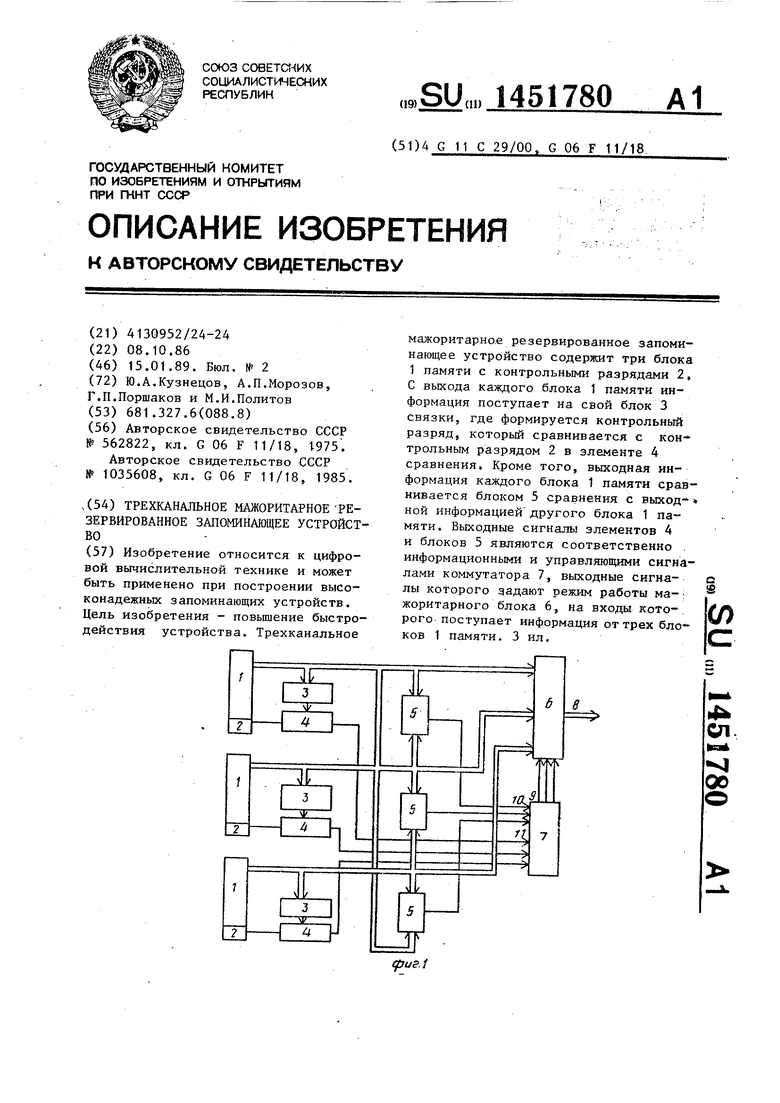

На фиг.1 представлена структурная схема трехканального мажоритарного резервированного запоминающего устройства; на фиг.2 - функциональная схема коммутатора;на фиг.З - таблица истинности мажоритарного блока.

Устройство содержит блоки 1 памяти с контрольными разрядами 2, блоки 3 свертки, элементы 4 сравнения, блоки 5 сравнения, мажоритарный блок 6, коммутатор 7, информационные выходы 8, выход 9 коммутатора 7, управляющие входы 10 и информационные входы 11 коммутатора 7.

Трехканальное мажоритарное резервированное запоминающее устройство работает следующим образом.

Если информация, считанная из тре блоков 1, одинаковая, то все блоки 5 сравнения вырабатывают на выходах логические О, которые поступают на вход 10 коммутатора 7, и на вы- ходе 9 коммутатора 7 устанавливается код 110. При этом мажоритарный блок 6 работает как схема голосования два из трех для информации с блоков 1 .

В случае возникновения ошибки любой кратности в одном из резервируемых блоков 1, два блока 5 сравнения вырабатывают сигналы несравнения - лог.

1 , а третий - сигнал б. Мажоритарный

сравнения - лог. блок 6 работает в этом случае аналогично предыдущему варианту как схема голосования два из трех за счет наличия хотя бы одного логического О на входе 10 коммутатора 7.

При возникновении ошибок в двух резервируемых блока 1 три блока 5 сравнения вырабатывают сигналы несравнения - логические 1, которые

o

5

0

5

0

5

0

5

поступают на вход 10 коммутатора 7, разрешая прохождение сигналов с выходов элементов 4 сравнения каждого канала на выход 9 коммутатора 7.,

Коммутатор 7 начинает в этом случае работать по входу 11. Информация с резервированных блоков 1 в каждом канале проходит через блок 3 свертки на элемент 4 сравнения для сравнения с контрольным разрядом 2. Если информация поступила с ошибкой, элемент 4 выдает лог. 1, а если без ошибки - лог.О. При этом на выходе 9 коммутатора 7 устанавливается управляющий код, разрешающий передачу информации с блока 1, элемент 4 сравнения которого имеет на выходе лог. О, через мажоритарный блок 6.

Формулаиз обре.тения Трехканальное мажоритарное резервированное запоминающее устройство, содержащее три блока памяти, информационные выход каждого из которых подключен к входу соответствующего блока свертки, выход каждого из которых подключен к первому входу соответствующего элемента сравнений, второй вход каждого из которых подключен к контрольному выходу соответствующего блока памяти, коммутатор, выходы которого подключены к управляющим входам мажоритарного блока, выход которого является информационным выходом устройства, о т л и ч .а- ю щ е е с я тем, что, с целью повышения быстродействия устройства,оно содержит три блока сравнения, первый вход каждого из которых подключен к выходу соответствующего блока памяти и к соответствующему информационному входу мажоритарного блока, второй вход каждого из блоков сравнения подключен к выходу последующего блока памяти, выходы блоков сравнения и выходы элементов, сравнения подключены соответственно к управляющим ч информационным входам коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное мажоритарно-резервированное устройство | 1990 |

|

SU1795461A1 |

| Трехканальное мажоритарно-резервированное устройство | 1981 |

|

SU1035608A1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Резервированная система | 1982 |

|

SU1084802A1 |

| Трехканальная резервированная вычислительная система | 1980 |

|

SU949864A1 |

| Резервированное трехканальное устройство | 1981 |

|

SU1069204A1 |

| Устройство для управления реконфигурацией резервированной системы | 1982 |

|

SU1040632A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1984 |

|

SU1234885A2 |

| Трехканальная резервированная вычислительная система | 1983 |

|

SU1156274A1 |

Изобретение относится к цифровой вычислительной технике и может быть применено при построении высоконадежных запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Трехканальное мажоритарно.е резервированное запоминающее устройство содержит три блока 1 памяти с контрольными разрядами 2, С выхода каждого блока 1 памяти информация поступает на свой блок 3 связки, где формируется контрольный разряд, который сравнивается с контрольным разрядом 2 в элементе 4 сравнения. Кроме того, выходная информация каждого блока 1 памяти сравнивается блоком 5 сравнения с выход- ной информацией другого блока 1 памяти. Выходные сигналы элементов 4 и блоков 5 являются соответственно информационными и управляющими сигналами коммутатора 7, выходные сигналы которого задают режим работы ма- жоритарного блока 6, на входы которого поступает информация от трех бло ков 1 памяти. 3 ил. с (Л

| Авторское свидетельство СССР № 562822, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Трехканальное мажоритарно-резервированное устройство | 1981 |

|

SU1035608A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-01-15—Публикация

1986-10-08—Подача