выходы третьего регистра управления соединены с первыми входами седьмого восьмого и девятого элементов ИЛИ, выходы которых соединены с первым, вторым и третьим управляющими входами третьего коммутатора информации из резервных блоков и третьего блока коммутации восстановленной информации, а через седьмой, восьмой и девя тый элементы НЕ подключены к их соот ветственно четвертому, пятому и шестому управляющим входам, выход контроля первого резервного блока соединен с вторыми входами первого, четвертого и седьмого элементов ИЛИ, выход контроля второго резервного блока соединен с вторыми входами второго, пятого и восьмого элементов ИЛИ, выход контроля третьего резервного блока соединен с вторыми входами третьего, шестого и девятого элементов ИЛИ. 2. Система по п. 1, отличающаяся тем, что коммутатор информации из резервных блоков содержит три группы элементов И и груп пу элементов ИЛИ, причем входы первой, второй и третьей групп информационных входов коммутатора соединены с первыми входами элементов И соответственно первой, втброй и третьей групп, выходы которых соединены с первыми, вторыми и третьими входами соответственно элементов ИЛИ группы, четвертые - восьмые входы которых подключены к входам четверто группы информационных входов коммута тора, а выходы соединены с выход ни коммутатора, первый управляющий вход коммутатора соединен с вторыми входами элементов И второй и третьей групп, второй управляющий вход коммутатора подключен к вторым входам 2 элементов И первой группы и третьим входам элементов И третьей группы, третий -управляющий вход коммутатора подключен к третьим входам элементов И первой и второй групп, четвертый, пятый и шестой управляющие входы коммутатора соединены с четвертыми входами элементов И соответственно первой, второй и третьей групп, 3. Система по п. 1, отличающаяся тем, что блок коммутации воссЛновленной информации содержит пять групп элементов И, выходы которых соединены с выходами блока, а первые входы - с информационными входами блока, вторые входы элементов И первой группы соединены с первым управляющим входом блока, третьи входы элементов И первой группы соединены с вторым управляю цим входом блока, четвертые входы элементов И первой группы соединены с третьим управляющим входом блока, четвертый управляющий вход блока подключен к вторым входам элементов И второй группы, пятый управляющий вход блока соединен с третьими входами элементов И второй группы, шестой управляющий вход блока подключен к четвертым входам элементов .второй группы, вторые, третьи и четвертые входы элементов И третьей группы соединены соответственно с третьим, четвертым и пятым управляющими входами блока, вторые третьи и четвертые входы элементов И четвертой группы подключены соответственно к второму, четвертому и шестому управляющим входам блока, вторые, третьи и четвертые входы элементов И пятой группы соединены соответственно с первым, пятым и шестым управляющими входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Отказоустойчивая вычислительная система | 1981 |

|

SU1077070A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| Резервированная система | 1985 |

|

SU1384063A2 |

| Резервированный оконечный модуль для цифровых автоматических систем коммутации | 1988 |

|

SU1578838A1 |

| Адаптивное четырехканальное резервированное устройство | 1990 |

|

SU1742821A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

1. РЕЗЕРВИРОВАННАЯ СИСТЕМА, содержащая три резервных блока, первый коммутатор информации из резервных блоков и первьш регистр управления, причем информационные выходы первого, второго и третьего резервных блоков соединены с входами первой, второй и третьей групп информационных входов первого коммутатора информации из резервных блоков, выходы контроля первого, второго и третьего резервных блоков соединены с входами первого, второго и третьего разрядов первого регистра управления, о тличающаяся тем, что, с целью повьшения надежности системы за счет более полного использования резерва, в нее введены второй и третий коммутаторы информации из резервных блоков, второй и третий ре- гистры управления, три группы мажоритарных элементов, девять элементов ИЛИ, девять элементов НЕ и три блока коммутации восстановленной информации, причем информационные выходы первого, второго и третьего резервных блоков соединены с входами первой, второй и третьей групп мажоритарных элементов, выходы которых соединены с информационными входами соответственно первого, второго и третьего блоков коммутации восстановленной информации, выходы которых соединены с входами четвертой группы информационных входов соответственно первого, второго и третьего коммутаторов информации из резервных блоков, выходы контроля первого, второго и третьего резервных блоков соединены с входами соответственно первого, второго и третьего i разрядов первого второго и третьего регистра управления, выходы первого регистра управления соединены с первыми входами первого, второго и третьего элементов ИЛИ, выходы которых соединены с первым, вторым и третьим соответственно управляющими входами первого коммутатора информации из резервных блоков и первого 00 блока коммутации восстановленной информации, а через первый, второй if и третий элементы НЕ подключены соот30 ветственно к их четвертому, пятому и шестому управляющим входам, выходы второго регистра управления соединены с первьми входами четвертого, пятого и шестого элементов ИЛИ, выходы которых соединены с первым, вторым и третьим соответственно управляющими входами второго коммутатора информации из резервных блоков и второго блока коммутации восстановленной информации, а через четвертый, пятый и шестой элементы НЕ подключены к их четвертому, пятому и шестому соответственно управляющим входам.

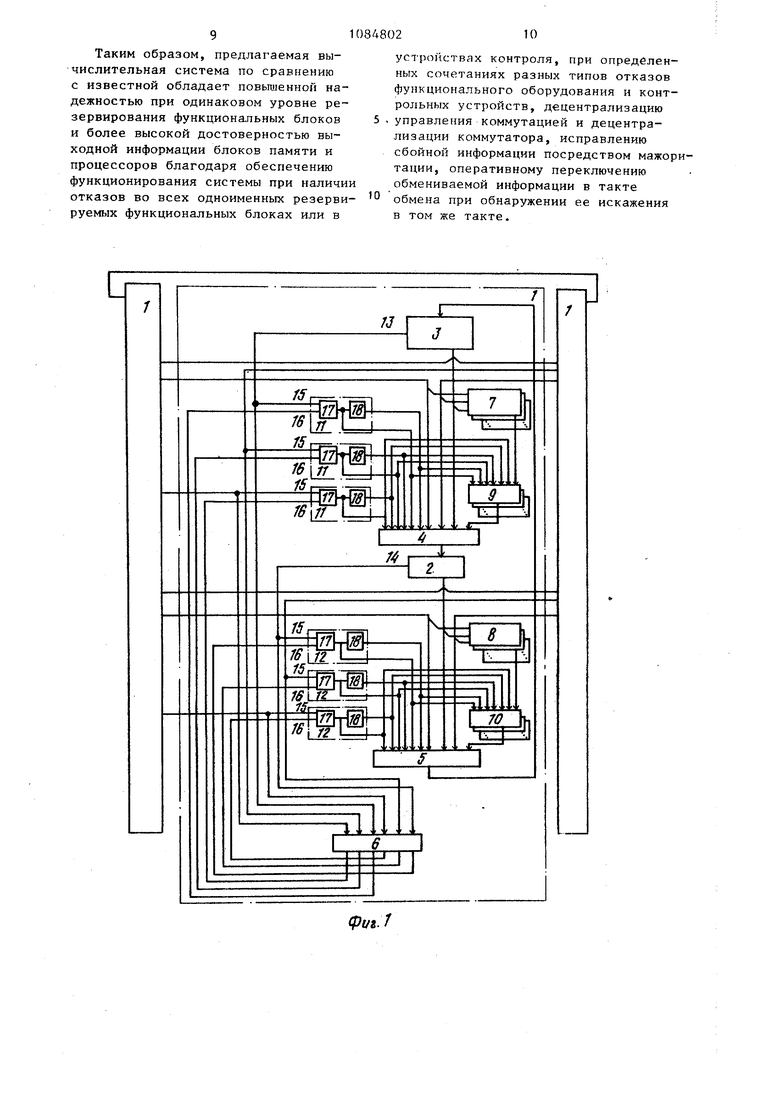

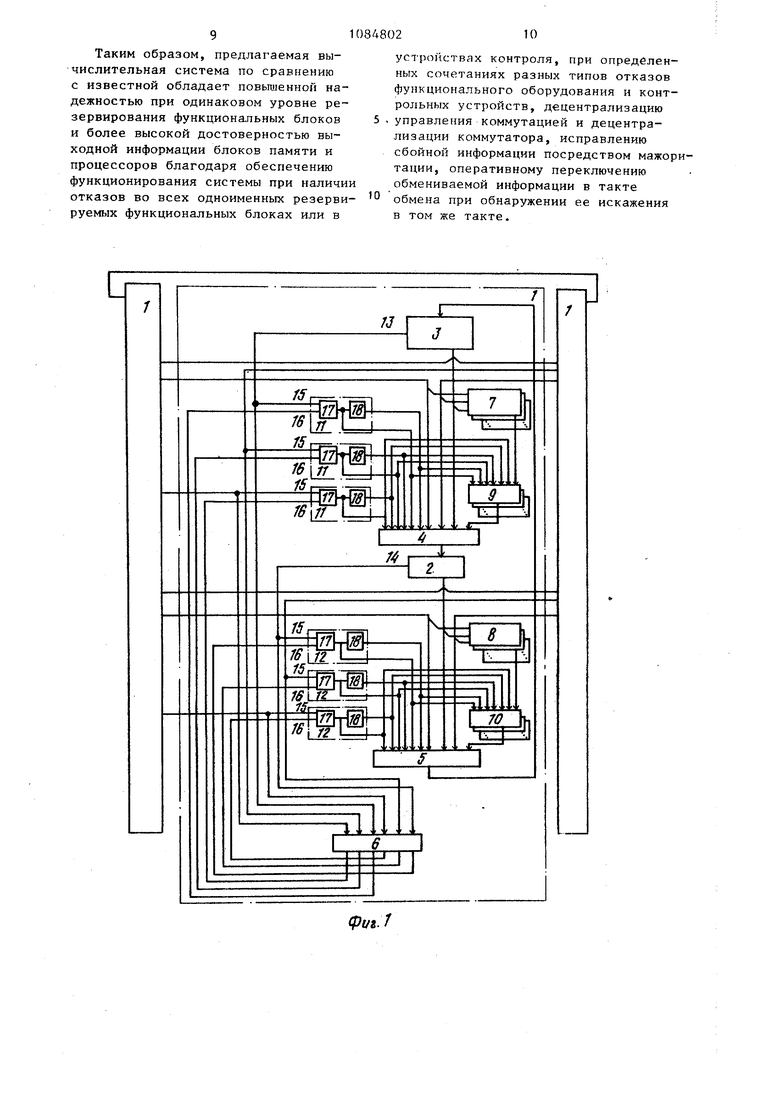

Изобретение относится к вычислительной технике и может быть использовано при проектировании высоконадежных вычислительных систем.

Известны трехканальные мажоритарно-резервированные устройства, которые, кроме мажоритации, реализуют

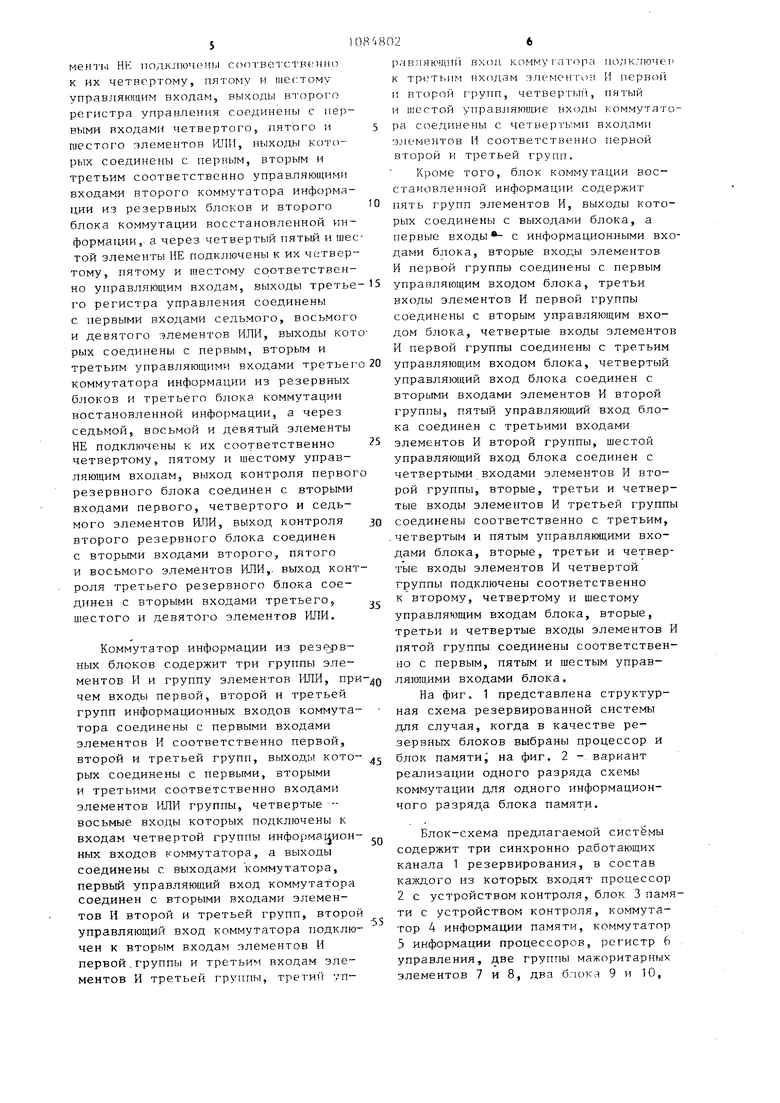

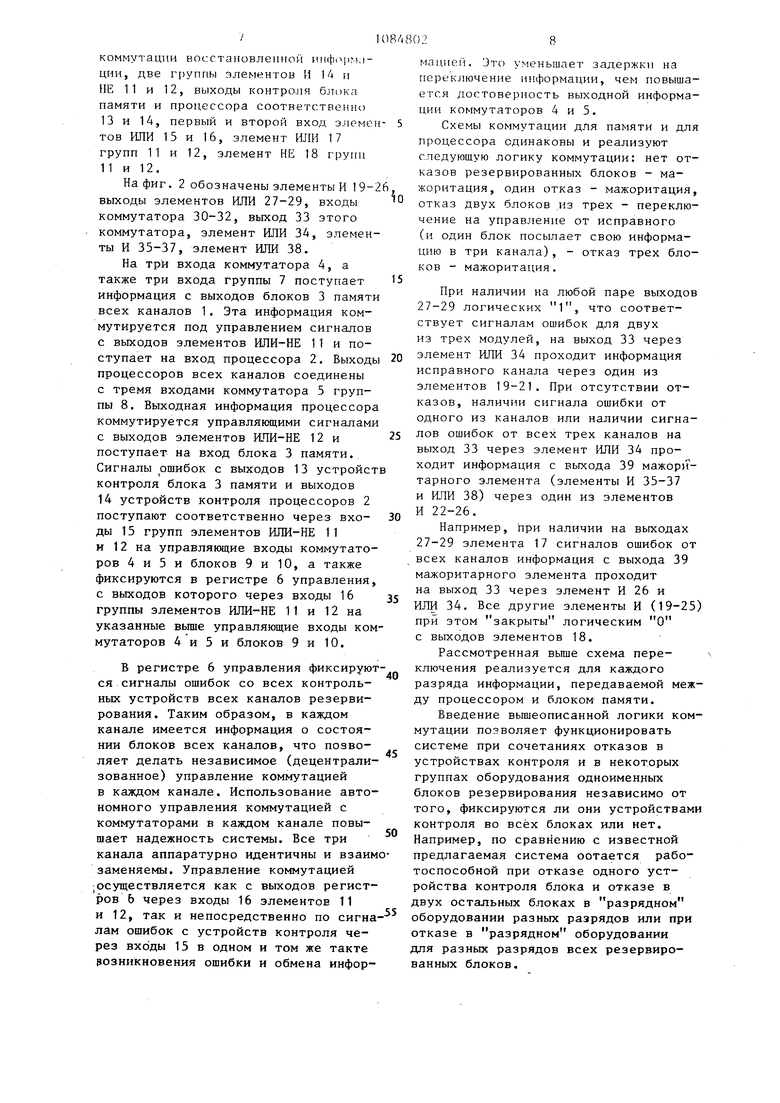

переключение выходной информации резервируемых блоков при их отказах по сигналам с контрольных устройств, т.е. обеспечивают работоспособность резервированной системы при наличии хотя бы одного исправного резервированного блока lj . 3 Системы с данным устройстном отказывают при отказе всех систем кон роля или при обнаружении искажения информации во всех каналах резервируемых блоков, произошедшего в разных разрядах. Известно устройство, обеспечиваю щее работоспособность резервированной системы при отказах всех схем, контроля izj , Однако при отказе одного канала резервирования из трех на одну его выходную шину, проходит искаженная информация. Известна вычислительная система, содержащая К запоминающих устройств (ЗУ), М процессоров, коммутатор памяти, коммутатор процессоров, уст ройства контроля процессоров и ЗУ, регистр состояния и управления коммутаторами, причем выходы ЗУ соединены с соответствующими входами ком мутатора памяти, выходы которого соединены с входами процессоров, выходы которых соединены с соответствующими входами коммутатора проце соров, выходы которого соединены с входами ЗУ и с входами устройств ввода-вывода, выходы контрольных устройств процессоров и ЗУ соединен с входами регистра состояния и упра ления, выходы которого соединены с управляющими входами коммутаторов процессора и памяти 31 Недостатком известной системы явл ется невозможность функционирования при возникновении отказов во всех одноименных блоках (не обязательно одновременно) таких, что приводят к появлению сигналов ошибки, но исправляются мажоритацией. Например, искажение различных разрядов информ ции одноименных блоков или разновре менное появление искажений в разрядах, а также некоторые сочетания отказов устройств контроля и разряд ных отказов блоков приводят к отказ системы. Система не работает также при отказах всех устройств контроля одноименных блоков. Кроме того, в известной системе отсутствует оперативное переключени обмениваемой информации, а также обмена при обнаружении ее искажения в том же такте. Управление коммутат рами идет через логические цепи и регистры, что при использовании .быстродействующих процессоров и бло 2 ков памяти может привести к задержке в срабатывании коммутаторов и пропуску на их выход искаженной информации. Целью изобретения является повышение надежности путем более полного использования резерва и повышения доставерности выходной информации коммутаторов. Указанная цель достигается тем, что в резервированную систему, содержащую три резервных блока, первый коммутатор информации из резервных блоков и первый регистр управления, причем информационные выходы первого, второго и третьего резервных блоков соединены с входами первой, второй и третьей групп информационных входов первого коммутатора информации из резервных блоков, выходы контроля первого, второго и третьего резервных блоков соединены с входами первого, второго и третьего разрядов первого регистра управления, введены второй и третий коммутаторы информации из резервных блоков, второй и .третий регистры управления, три группы мажоритарных элементов, девять элементов ИЛИ, девять элементов НЕ и три блока коммутации восстановленной информации, причем информационные выходы первого, второго и третьего резервных блоков соединены с входами первой, второй и третьей групп мажоритарных элементов, выходы которых соединены с информационными входами соответственно первого, второго и третьего блоков коммутации восстановленной информации, выходы которых соединены с входами четвертой группы информационных входов соответственно первого, второго и третьего коммутаторов информации из резервных блоков, выходы контроля первого, второго и третьего резервных блоков соединены с входами соответственно первого, второго и третьего разрядов первого, второго и третьего регистра управления, выходы первого регистра управления соединены с первыми входами первого, второго и третьего элементов ИЛИ, выходы которых соединены с первым, вторым и третьим соответственно управляющими входами первого коммутатора информации из резервных блоков и первого блока комму-: . тации восстановленной информации, а через первый, второй и третий элемент.1 НЕ полключ( ссхттветств -нио к их четвертому, пятому и шестому управляющим входам, выходы второго ре.гистра управления соединены с первыми входами четвертогоS пятого и шестого элементов Ш1И, выходы которых соединены с первым, вторым и третьим соответственно управляющими входами второго коммутатора информации из резервных блоков и второго блока коммутации восстановленной ;нформации, а через четвертый пятьй и шее той элементы НЕ подключены к их четвертому, пятому и шестому соответственно управляющим входам, выходы третье го регистра управления соединены с первыми входами седьмого, восьмого и девятого элементов ИЛИ, выходы кот рых соединены с первым, вторым и третьим управляющими входами третье коммутатора информации из резервных блоков и третьего блока коммутации востановленной информации, а через седьмой, восьмой и девятый элементы НЕ подключены к их соответственно четвертому, пятому и шестому управляющим входам, выход контроля перво резервного блока соединен с вторыми входами первого, четвертого и седьмого элементов ИПИ, выход контроля второго резервного блока соединен с вторыми входами второго, пятого и восьмого элементов ИЛИ,, выход кон роля третьего резервного блока соединен с вторыми входами третьегоj шестого и девятого элементов ИЛИ, Коммутатор информации из резервных блоков содержит три группы элементов И и группу элементов ИЛИ, пр чем входы первой, второй и третьей групп информационных входов коммута тора соединены с первыми входами элементов И соответственно первой, второй и третьей групп, выходы кото рьрс соединены с первыми, вторыми и третьими соответственно входами элементов ИЛИ группы, четвертые восьмые входы которых подключены к входам четвертой группы информаь ион нык входов коммутатора, а выходы соединены с выходами коммутатора, первый управляющий вход коммутатора Соединен с вторыми входами элементов И второй и третьей групп, второ управляющий вход коммутатора подклю чен к вторым входам элементов И первой,. группы и третьим входам элементов И третьей группы, трети1 г управняющий вход комму i aTopa подключен И пер в oil к тр гтьим вх(1дам злементоа п второй групп, четверть, пятый и шестой управляющие коммутатора соединены с четверть-ми входами элементов И соответственно первой второй и третьей групп. Кроме того, блок коммутации восстановленной информации содержит пять групп элементов И, выходы которых соединены с выходами блока, а первые входы - с информационными входами блока, вторые входы элементов И первой группы соединены с первым управляющим входом блока, третьи входы элементов И первой группы соединены с вторым управляющим входом блока, четвертые ВХОДЬЕ элементов И первой группы соединены с третьим управляющим входом блока, четвертый управляющий вход блока соединен с вторыми входами элементов И второй группы, пятый управляющий вход блока соединен с третьими входами элементов И второй группы, шестой управляющий вход блока соединен с четвертыми входами элементов И второй группы, вторые, третьи и четвертые входы элементов И третьей группы соединены соответственно с третьим, четвертым и пятым управлянщими входами блока, вторые, третьи и четвертые входы элементов И четвертой группы подключены соответственно к второму, четвертому и шестому управляющим входам блорса, вторые, третьи и четвертые входы элементов И пятой группы соединены соответственно с первым, пятым и шестым управЛЯЮ1ЦИМИ входами блока. На фиг. 1 представлена структурная схема резервированной системы для случая, когда в качестве резервных блоков выбраны процессор и блок памяти на фиг, 2 -, вариант реализации одного разряда схемы коммутации для одного информационного разряда блока памяти. Блок-схема предлагаемой системы содержит три синхронно работающих канала 1 резервирования, в состав кажд,ого из которых входят процессор 2 с устройством контроля, блок 3 памяти с устройством контроля, коммутатор 4 информации памяти, коммутатор 5 информации процессоров, регистр 6 , управления, две группы мажоритарных элементов 7 и 8, два блока 9 и 10, коммутации восстановленной информ.цни, две группы элементов И 1А и Е 11 и 12, выходы контроля блока памяти и процессора соответственно 13и 14, первый и второй вход элеме тов ИЛИ 15 и 16, элемент ИЛИ 17 групп 11 и 12, элемент НЕ 18 групп 11 и 12, На фиг. 2 обозначены элементы И 1 9выходы элементов ИЛИ 27-29, входы коммутатора 30-32, выход 33 этого коммутатора, элемент ИЛИ ЗА, элемен ты И 35-37, элемент ИЛИ 38, На три входа коммутатора 4, а также три входа группы 7 поступает информация с выходов блоков 3 памят всех каналов 1. Эта информация коммутируется под управлением сигналов с выходов элементов ИЛИ-НЕ 11 и поступает на вход процессора 2. Выход процессоров всех каналов соединены с тремя входами коммутатора 5 группы 8. Выходная информация процессор коммутируется управляющими сигналам с выходов элементов ИЛИ-НЕ 12 и поступает на вход блока 3 памяти. Сигналы ошибок с выходов 13 устройс контроля блока 3 памяти и выходов 14устройств контроля процессоров 2 поступают соответственно через входы 15 групп элементов ИЛИ-НЕ 11 и 12 на управляющие входы коммутато ров 4 и 5 и блоков 9 и 10, а также фиксируются в регистре 6 управления с выходов которого через входы 16 группы элементов ИЛИ-НЕ 11 и 12 на указанные вьше управляющие входы ко мутаторов 4 и 5 и блоков 9 и 10. В регистре 6 управления фиксирую ся сигналы ошибок со всех контрольных устройств всех каналов резервирования. Таким образом, в каждом канале имеется информация о состоянии блоков всех каналов, что позволяет делать независимое (децентрали зованное) управление коммутацией в каждом канале. Использование авто номного управления коммутацией с коммутаторами в каждом канале повышает надежность системы. Все три канала аппаратурно идентичны и взаи заменяемы. Управление коммутацией ;осуществляется как с выходов регист ров 6 через входы 16 элементов 11 и 12, так и непосредственно по сигн лам ошибок с устройств контроля через входы 15 в одном и том же такте эозникновения ощибки и обмена инфор манией. Это уменыиает задержки на переключение информации, чем повышается достоверность выходной информации коммутаторов 4 и 5. Схемы коммутации для памяти и для процессора одинаковы и реализуют следующую логику коммутации: нет отказов резервированных блоков - мажоритация, один отказ - мажоритация, отказ двух блоков из трех - переключение на управление от исправного (и один блок посылает свою информацию в три канала), - отказ трех блоков - мажоритация. При наличии на любой паре выходов 27-29 логических 1, что соответствует сигналам ошибок для двух из трех модулей, на выход 33 через элемент ИЛИ 34 проходит информация исправного канала через один из элементов 19-21. При отсутствии отказов, наличии сигнала ошибки от одного из каналов или наличии сигналов ошибок от всех трех каналов на выход 33 через элемент ИЛИ 34 проходит информация с выхода 39 мажоритарного элемента (элементы И 35-37 и ИЛИ 38) через один из элементов И 22-26. Например, при наличии на выходах 27-29 элемента 17 сигналов ошибок от всех каналов информация с выхода 39 мажоритарного элемента проходит на выход 33 через элемент И 26 и ИЛИ 34, Все другие элементы И (19-25) при этом закрыты логическим О с выходов элементов 18. Рассмотренная выше схема переключения реализуется для каждого разряда информации, передаваемой между процессором и блоком памяти. Введение вышеописанной логики коммутации позволяет функционировать системе при сочетаниях отказов в устройствах контроля и в некоторых группах оборудования одноименных блоков резервирования независимо от того, фиксируются ли они устройствами контроля во всех блоках или нет. Например, по сравнению с известной предлагаемая система остается работоспособной при отказе одного устройства контроля блока и отказе в двух остальных блоках в разрядном оборудовании разных разрядов или при отказе в разрядном оборудовании для разных разрядов всех резервированных блоков.

Таким образом, предлагаемая вычислительная система по сравнению с известной обладает повьаиенной надежностью при одинаковом уровне резервирования функциональных блоков и более высокой достоверностью выходной информации блоков памяти и процессоров благодаря обеспечению функционирования системы при наличии отказов во всех одноименных резервируемых функциональных блоках или в

устройствах контроля, при определенных сочетаниях разных типов отказов функционального оборудования и контрольных устройств, децентрализацию управления коммутацией и децентрализации коммутатора, исправлению сбойной информации посредством мажоритации, оперативному переключению обмениваемой информации в такте обмена при обнаружении ее искажения в том же такте.

(иг.7

(f}l/l.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 562822, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-05-12—Подача