Изобретение относится к автоматике и вычислительной технике и может быть нспользованс в цифровых системах при повышенных требованиях к их надежности.

Известно трехкайальное мажоритарнорезервированное устройство, содержащее в каждом канале резервируемый блок, соединенный с блоком контроля, мажоритарный элемент и элемент И 1.

Известно также резервированное устройство, содержащее в каждом канале резервируемый блок, мажоритарный элемент контроля, восстанавливающий орган и элемент И 2,

Наиболее близким по технической сущности к изобретению является резервированное трехкайальное устройство, содержащее в каждом канале резервируемый вычислительный блок, контрольный выход которого подключен к блоку контроля данного каKa.ia, выход которого соединен с соответствующими управляющими входами восстанавливающих блоков каждого канала, выхо;1,ы которых являются информационными выходами устройства 3.

Недостатком всех упомянутых устройств является то, что их функционирование возможно только при синхронной работе резерlii-ipveMbix вычислительных блоков каждого Kaiiajia. Осуществление же синхронизации между ними требует больщих аппаратурных затрат. Кроме того, при синхронной работе резервируемых вычислительных блоков воздействие помехи приводит к формированию ложной информации во всех трех каналах, так как в момент воздействия помехи все они осуществляют обработку одной и той же информации

Цель изобретения - упрощение и повыlueuHe надежности.

Поставленная цель достигается тем, что пезе1 Бированное трехканальное устройство, содержащее в каждом канале резервируемый вычислительный блок, контрольный выход которого подключен к блоку контроля данного канала, выход которого соединен с соответствующими управляющими входами восстанавливающих блоков каждого канала, выходы которых являются информационными выходами устройства, содержит генератор импульсов, и в каждом канале буферный запоминающий блок, формирователь адреса мажоритарный блок и элемент И, каждый выход генератора импульсов соединен с синхронизирующим входом формирователя адресов одного из каналов, адресные выходы формирователя адреса каждого -канала соединены с соответствующими входами мажоритарных блоков каждого канала, а выходы переполнения - с соответствующими входами элементов И двух други.х каналов, выход элемента И каждого канала соединен с нулевым установочным входом формирователя адреса данного кана,ia, выход мажоритарного блока в каждом

канале является адресным выходом устройства и соединен с вторым адресным входом буферного запоминающего блока, второй информационный вход которого является информационным входом устройства, второй

информационный выход буферного загюминающего блока каждого канала соединен с соответствующими информационными входами восстанавливающих блоков всех каналов, а первый адресный вход и информационные

вход и выход буферного запоминающего блока каждого кайала соединены соответственно с адресным выходом, информационными выходом и входом резервируемого вычислительного блока данного канала.

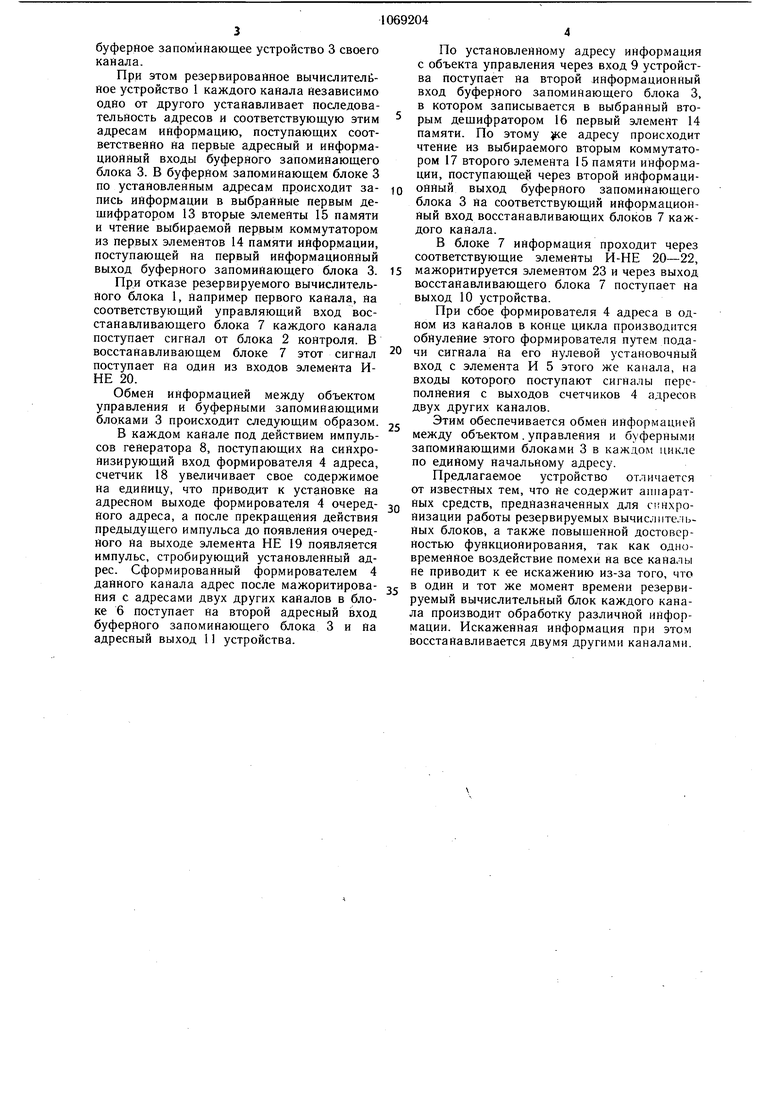

Кроме того, буферный запоминающий блок содержит первый и второй дещифраторы, первый и второй коммутаторы, первые и вторые элементы памяти, информационные входы которых соединены с первым информационным входом блока, управляющие

° входы - с соответствующими выходами первого дешифратора, а выходы через второй коммутатор - с вторым информационным выходом блока, информационные входы первых элементов памяти соединены с вторым информационным входом блока, управляющие входы - с соответствующими выходами второго дешифратора, а выходы через первый коммутатор - с первым информационным выходом блока, первый адресный вход которого соединен с адресными входами первых дещифратора и ком.мутатора, а второй адресный вход - с адресными входами вторых дешифратора и ком.мутатора.

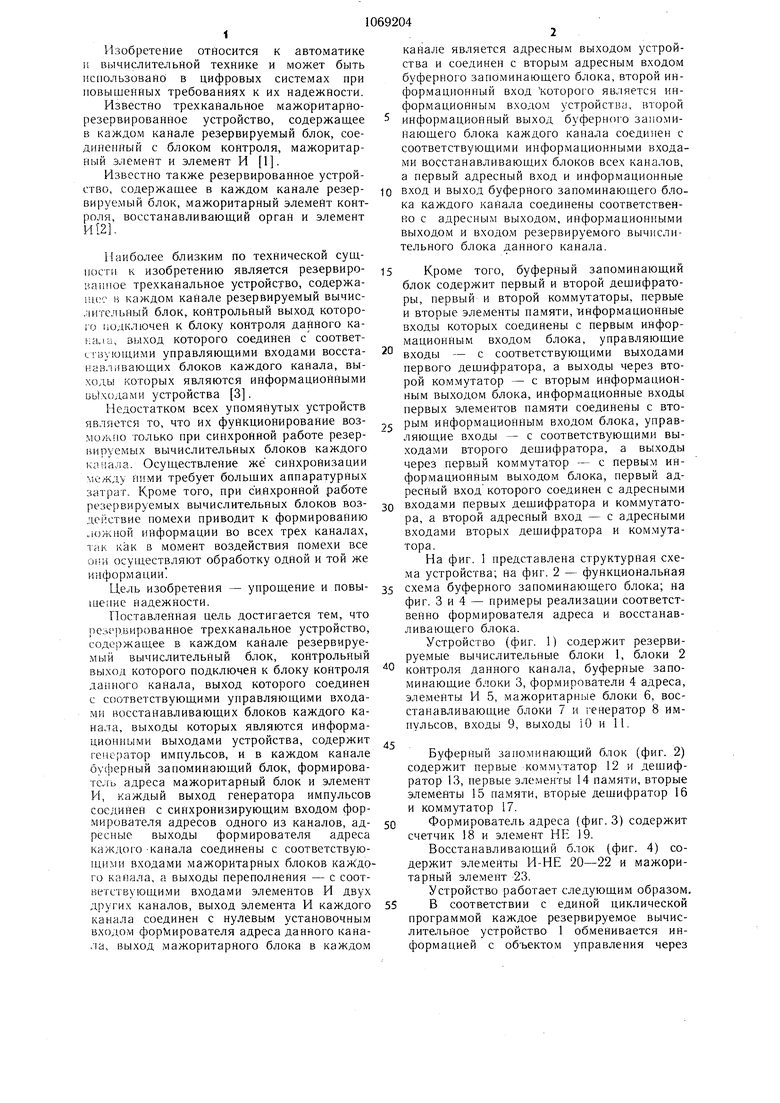

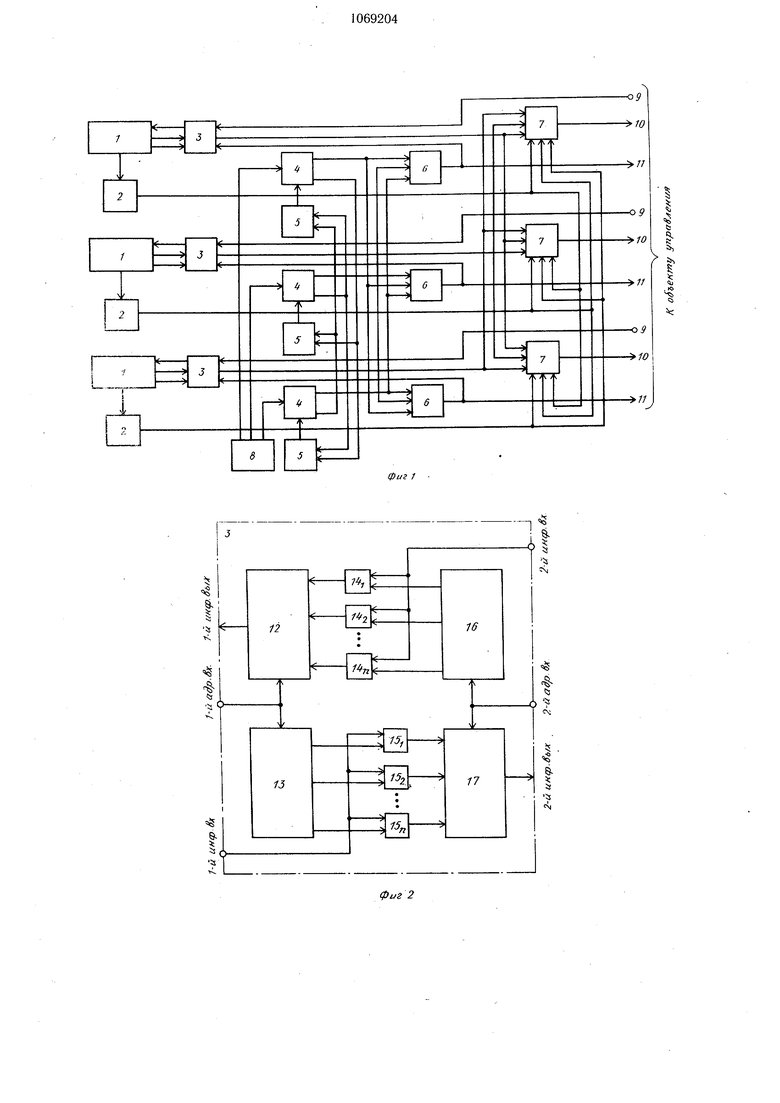

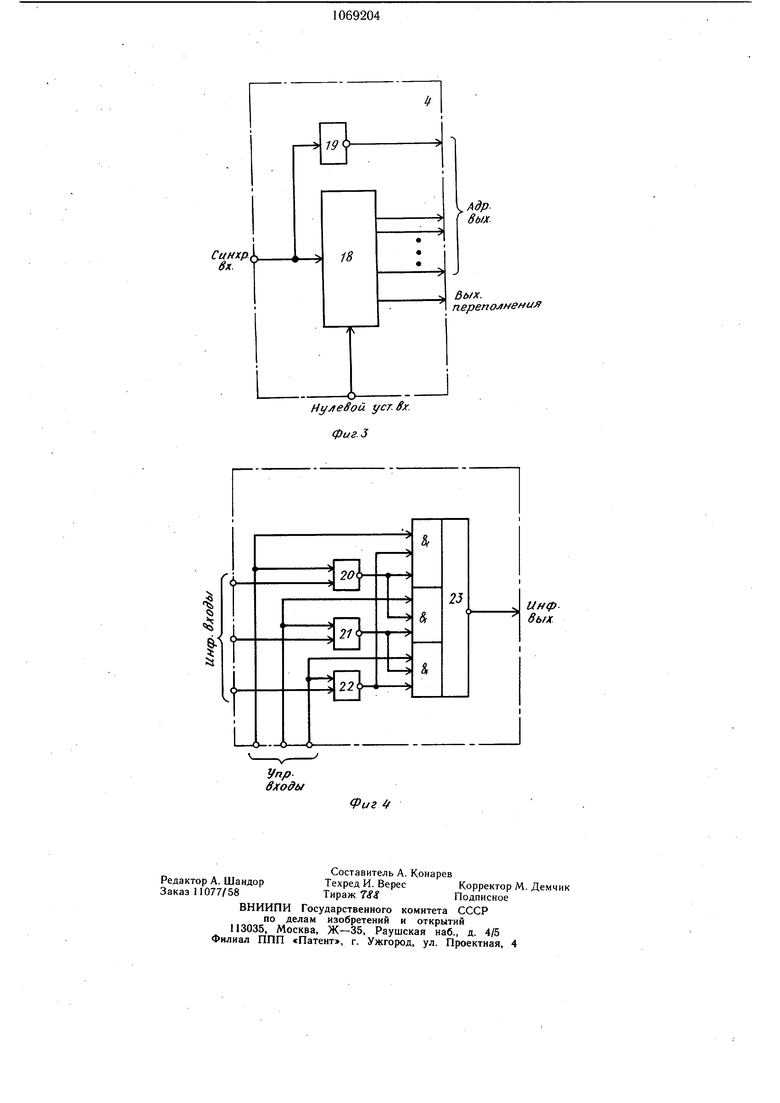

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема буферного запоминающего блока; на фиг. 3 и 4 - примеры реализации соответственно формирователя адреса и восстанавливающего блока.

Устройство (фиг. 1) содержит резервируемые вычислительные блоки 1, блоки 2 контроля данного канала, буферные запоминающие блоки 3, формирователи 4 адреса, элементы И 5, мажоритарные блоки 6, восстанавливающие блоки 7 и генератор 8 импульсов, входы 9, выходы 10 и 11.

Буферный запоминающий блок (фиг. 2) содержит первые коммутатор 12 и дешифратор 13, первые элементы 14 памяти, вторые элементы 15 памяти, вторые дешифратор 16 и коммутатор 17.

Формирователь адреса (фиг. 3) содержит счетчик 18 и элемент НЕ 19.

Восстанавливающий блок (фиг. 4) содержит элементы И-НЕ 20-22 и мажоритарный элемент 23.

Устройство работает следующим образом.

В соответствии с единой циклической программой каждое резервируемое вычислительное устройство 1 обменивается информацией с объектом управления через буферное запоминающее устройство 3 своего канала. При этом резервированное вычислителбное устройство 1 каждого канала независимо одно от другого устанавливает последовательность адресов и соответствующую этим адресам информацию, поступающих соответственно на первые адресный и информационный входы буферного запоминающего блока 3. В буферном запоминающем блоке 3 по установленным адресам происходит запись информации в выбранные первым дешифратором 13 вторые элементы 15 памяти и чтение выбираемой первым коммутатором из первых элементов 14 памяти информации, поступающей на первый информационный выход буферного запоминающего блока 3. При отказе резервируемого вычислительного блока 1, например первого канала, на соответствующий управляющий вход восстанавливающего блока 7 каждого канала поступает сигнал от блока 2 контроля. В восстанавливающем блоке 7 этот сигнал поступает на один из входов элемента ИНЕ 20. Обмен информацией между объектом управления и буферными запоминающими блоками 3 происходит следующим образом. В каждом канале под действием импульсов генератора 8, поступающих на синхронизирующий вход формирователя 4 адреса, счетчик 18 увеличивает свое содержимое на единицу, что приводит к установке на адресном выходе формирователя 4 очередЯого адреса, а после прекращения действия предыдущего импульса до появления очередного на выходе элемента НЕ 19 появляется импульс, стробирующий установленный адрес. Сформированный формирователем 4 данного канала адрес после мажоритирования с адресами двух других каналов в блоке 6 поступает на второй адресный вход буферного запоминающего блока 3 и на адресный выход 11 устройства. По установленному адресу информация с объекта управления через вход 9 устройства поступает на второй информационный вход буферного запоминающего блока 3, в котором записывается в выбранный вторым дещифратором 16 первый элемент 14 памяти. По этому е адресу происходит чтение из выбираемого вторым коммутатором 17 второго элемента 15 памяти информации, поступающей через второй информационный выход буферного запоминающего блока 3 на соответствующий информационный вход восстанавливающих блоков 7 каждого канала. В блоке 7 информация проходит через соответствующие элементы И-НЕ 20-22, мажоритируется элементом 23 и через выход восстанавливающего блока 7 поступает на выход 10 устройства. При сбое формирователя 4 адреса в одном из каналов в конце цикла производится обнуление этого формирователя путем подачи сигнала на его нулевой установочный вход с элемента И 5 этого же канала, на входы которого поступают сигналы переполнения с выходов счетчиков 4 адресов двух других каналов. Этим обеспечивается обмен информацией между объектом . управления и буферными запоминающими блоками 3 в каждом цикле по единому начальному адресу. Предлагаемое устройство отличается от извест-ных тем, что не содержит аппаратных средств, предназначенных для синхронизации работы резервируемых вычислите.1ьНых блоков, а также повышенной достоверностью функционирования, так как одновременное воздействие помехи на все каналы не приводит к ее искажению из-за того, что Б один и тот же момент времени резервируемый вычислительный блок каждого канала производит обработку различной информации. Искаженная информация при этом восстанавливается двумя другими каналами.

ь

г

41

ycT.Sx. фиг. J

Adp вых.

Вых. переполнения

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная система | 1988 |

|

SU1584137A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Адаптивное резервированное устройство | 1980 |

|

SU1003403A1 |

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

1. РЕЗЕРВИРОВАННОЕ ТРЕХКАНАЛЬНОЕ УСТРОЙСТВО, содержащее в каждом канале резерируемый вычислительный блок, контрольный выход которого подключен к блоку контроля данного канала, выход которого соединен с соответствующими управляющими входами восстанавливающих блоков каждого канала, выходы которых являются информационными выходами устройства, отличающееся тем, что, с целью упрощения и повыщения надежнос ти, оно содержит генератор импульсов, и в каждом канале буферный запоминающий блок, формирователь адреса, мажоритарный блок и элемент И, каждый выход генератора импульсов соединен с синхронизирующим входом формирователя адресов одного из каналов, адресные выходы формирователя адреса каждого канала соединены с соответствующими входами мажоритарных блоков канала, а выходы переполнения - с соответствующими входами элементов И двух других каналов, выход элемента И каждого канала соединен с нулевым установочным .входом формирователя адреса данного канала, выход мажоритарного блока в каждом канале является адресным выходом устройства и соединен с вторым адресным входом буферного запоминающего блока, второй информационный вход которого является информационным входом устройства, второй информационный выход буферного запо.минающего блока каждого канала соединен с соответствующими информационными входами восстанавливающих блоков всех каналов, а первый адресный вход и информационные вход и выход буферного запоминающего блока каждого канала соединены соответственно с адресным выходом, информационными выходом и входом резервируемого вычислительного блока данЧ) ного канала. 2. Устройство по п. 1, отличающееся тем, (Л что буферный запоминающий блок содержит первый и второй дещифраторы, первый и второй коммутаторы, первые и вторые элементы памяти, информационные входы которых соединены с первым информационным входом блока, управляющие входы - с соответствующими выходами первого дещифратора, а выходы через второй коммуО5 татор - с вторым информационным выходом QO ISD блока, информационные входы первых элементов памяти соединены с вторым инфорО 4:: мационным входом блока, управляющие входы- с соответствующими выходами второго дещифратора, а выходы через первый коммутатор - с первым информационным выходом блока, первый адресный выход которого соединен с адресными входами первых дещифратора и коммутатора, а второй адресный вход - с адресными входами вторых дешифратора и коммутатора.

25

инф вых

8,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 562822, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-23—Публикация

1981-06-30—Подача