Изобретение относится к электроизмерительной технике и может быть использовано при измерении угла сдвига фаз между электрическими сигналу- ми в многоканальных системах сбора и обработки информации.

Цель изобретения - расшир ение частотного диапазона и уменьшение времени преобразования.

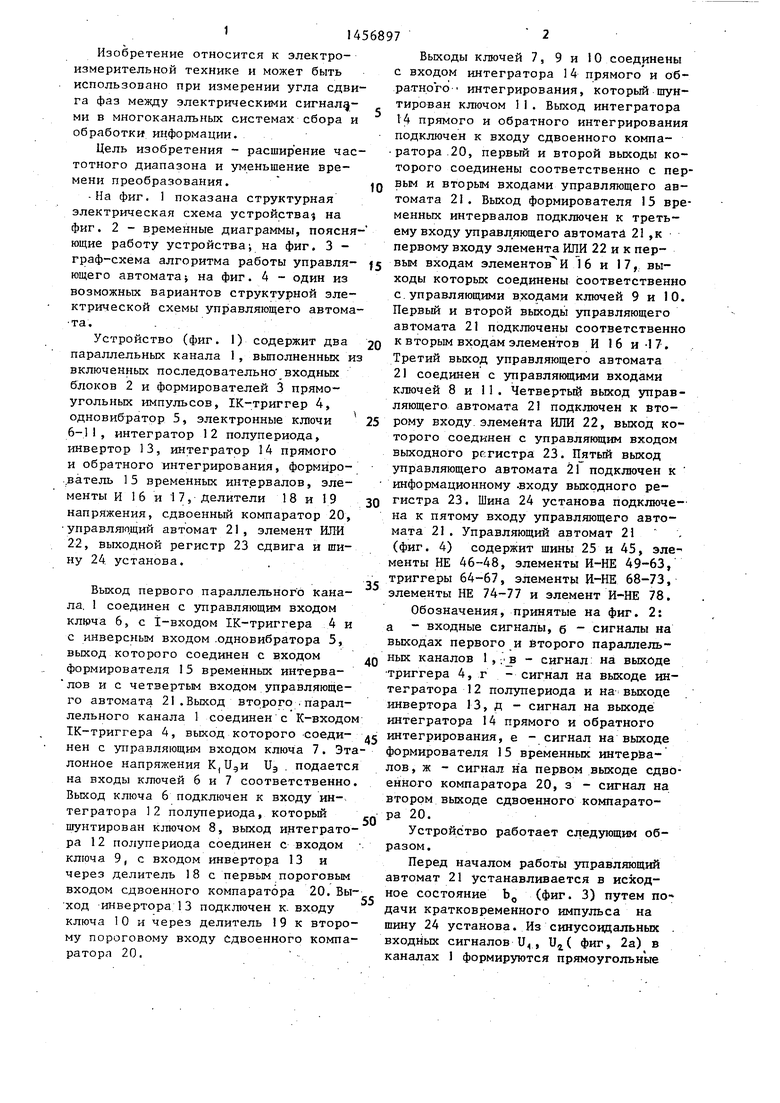

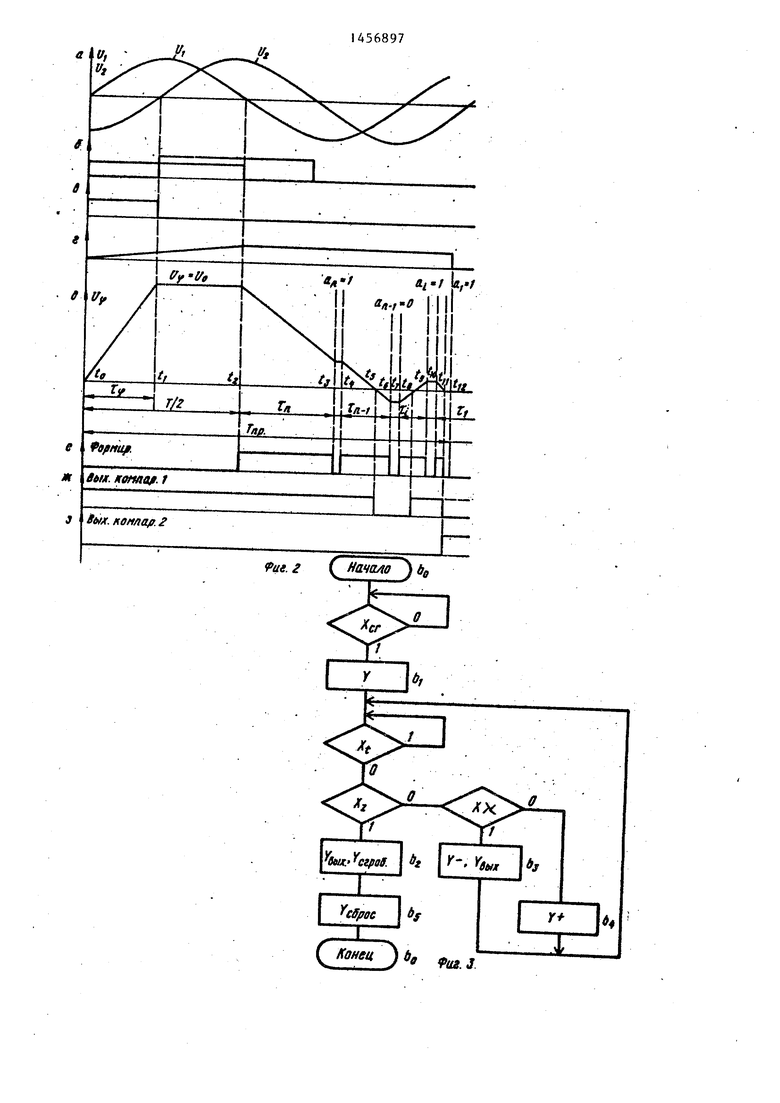

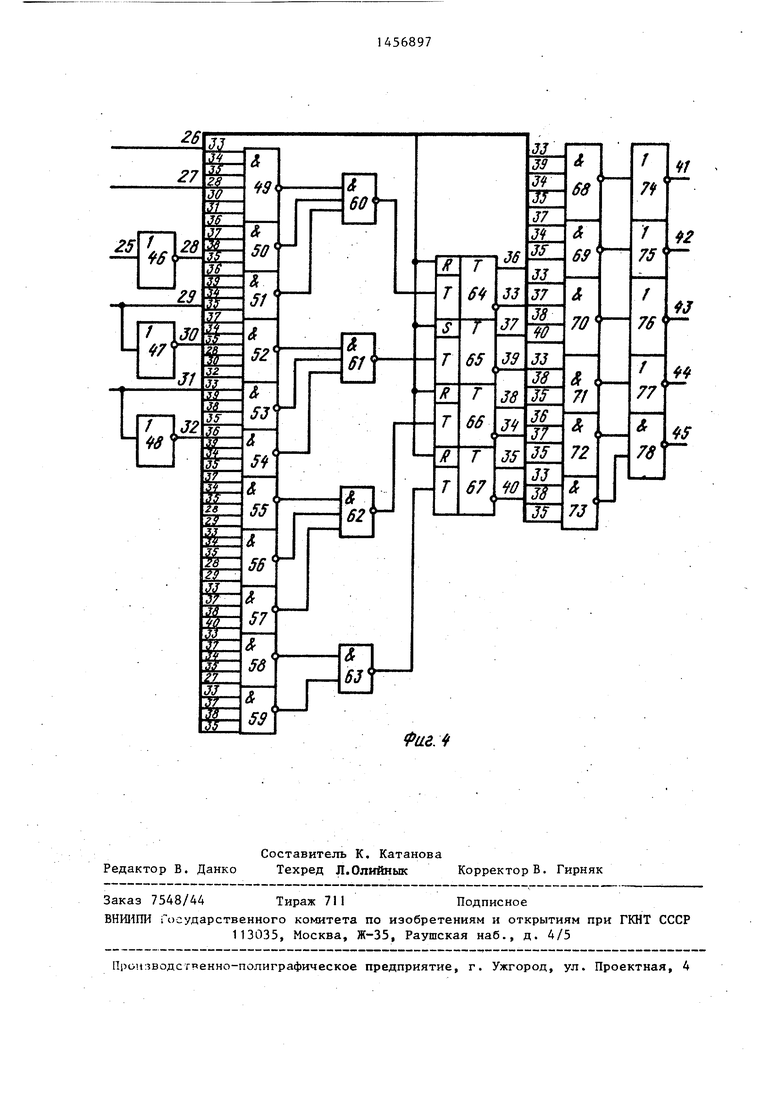

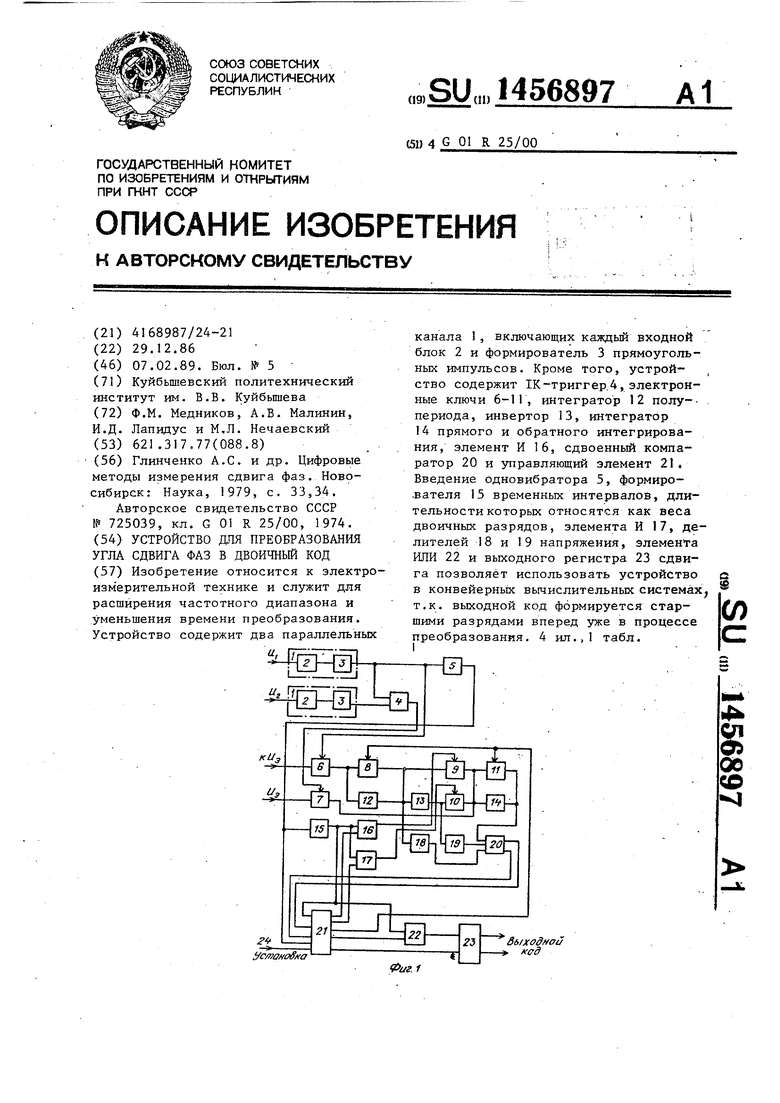

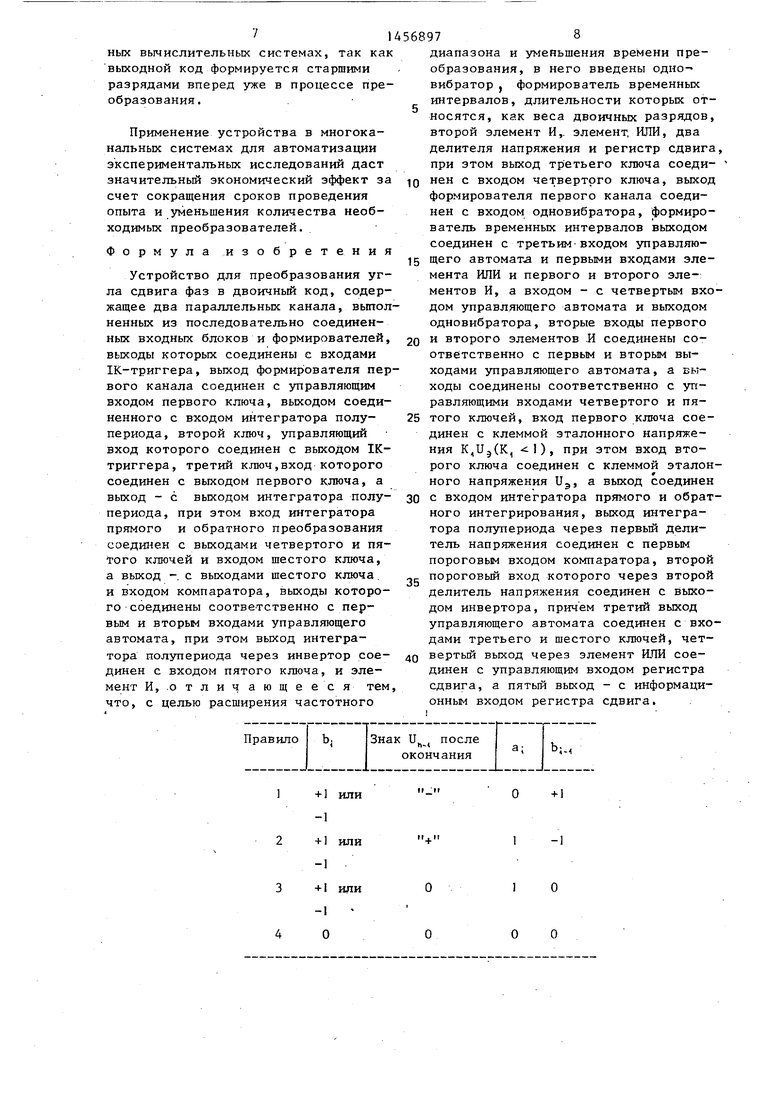

-На фиг. 1 показана структурная электрическая схема устройства на фиг. 2 - временные диаграммы, поясня ющие работу устройства; на фиг. 3 - граф-схема алгоритма работы управля- ющего автоматаi на фиг. 4 - один из возможных вариантов структурной электрической схемы управляющего автома та. .

Устройство (фиг. 1) содержит два параллельных канала 1, выполненных и включенных последовательно входных блоков 2 и формирователей 3 прямоугольных импульсов, 1К-триггер 4, одновибратор 5, электронные ктаочи

6-11, интегратор 12 полупериода, инвертор 13, интегратор 14 прямого и обратного интегрирования, формиро- .ватель 15 временных интервалов, элементы И 16 и 17, делители 18 и 19 напряжения, сдвоенный компаратор 20, управляющий автомат 21, элемент ИЛИ 22, выходной регистр 23 сдвига и шину 24 установа.

35

40

Выход первого параллельного канала. 1 соединен с управляющим входом ключа 6, с i-входом 1К-триггера 4 и с инверсным входом .одновибратора 5, выход которого соединен с входом формирователя 15 временных интервалов и с четвертым входом управляющего автомата 21.Выход второго .параллельного канала 1 соединен с К-входом

1К-триггера 4, выход которого соеди- 5 интегрирования, е - сигнал на выходе нен с управляющим входом ключа 7. Эта- формирователя 15 временных нитерйа- лонное напряжения К,идИ U

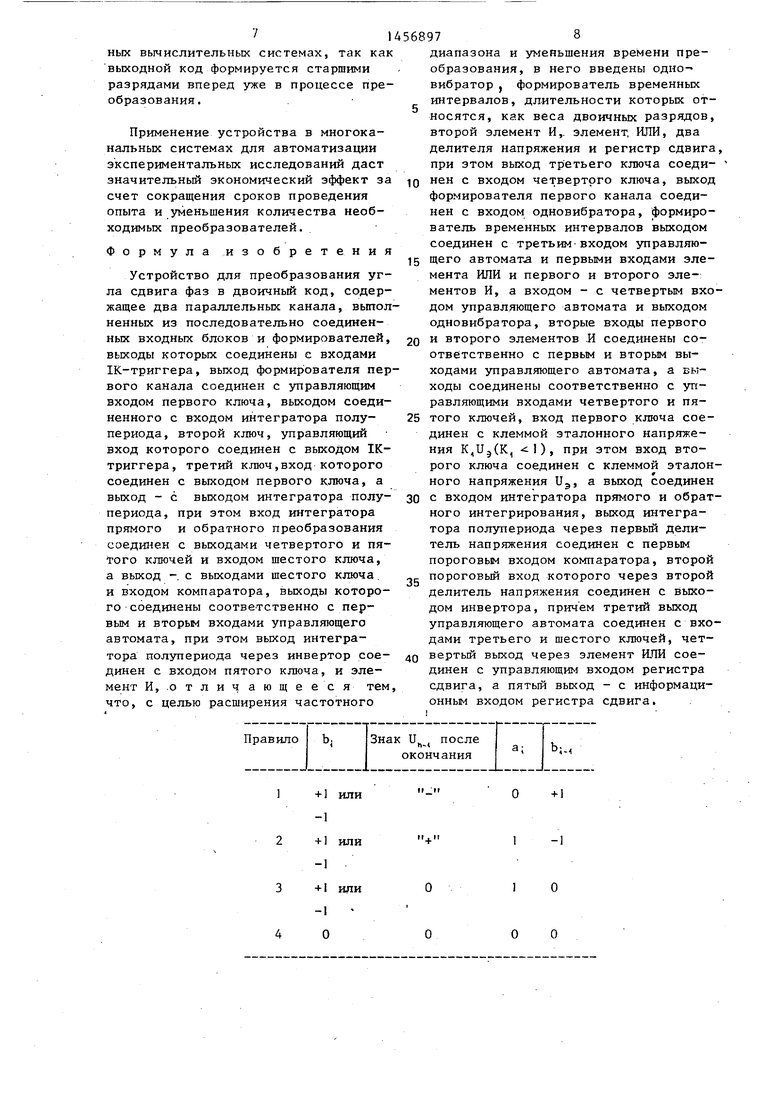

Выходы ключей 7, 9 и 10 соединен с входом интегратора 14 прямого и о ратного- интегрирования, который шу тирован ключом 11. Выход интегратор 14 прямого и обратного интегрирован подключен к входу сдвоенного компа- ратора.20, первый и второй выходы к торого соединены соответственно с п вым и вторым входами управляющего а томата 21. Выход формирователя 15 в менных интервалов подключен к треть ему входу управляющего автоматй 21 ,к первому входу элемента ИЛИ 22 и к первым входам элементов И 1 6 и 17, выходы которых соединены соответствен с.управляющими входами ключей 9 и 1 Первьй и второй выходы управляющего автомата 21 подключены соответствен к вторым входам элементов И 16 и -17. Третий вькод управляющего автомата 21 соединен с управляющими входами ключей 8 и 1I. Четвертый выход упра ляющего автомата 21 подключен к вто рому входу элемента ИЛИ 22, выход к торого соединен с управляющим входом выходного регистра 23. Пятый выход управляющего автомата 21 подключен к информационному .входу выходного регистра 23. Шина 24 установа подключе на к пятому входу управляющего автомата 21. Управляющий автомат 21 (фиг. 4) содержит шины 25 и 45, эле менты НЕ 46-48, элементы И-НЕ 49-63, триггеры 64-67, элементы И-НЕ 68-73, элементы НЕ 74-77 и элемент И-НЕ 78.

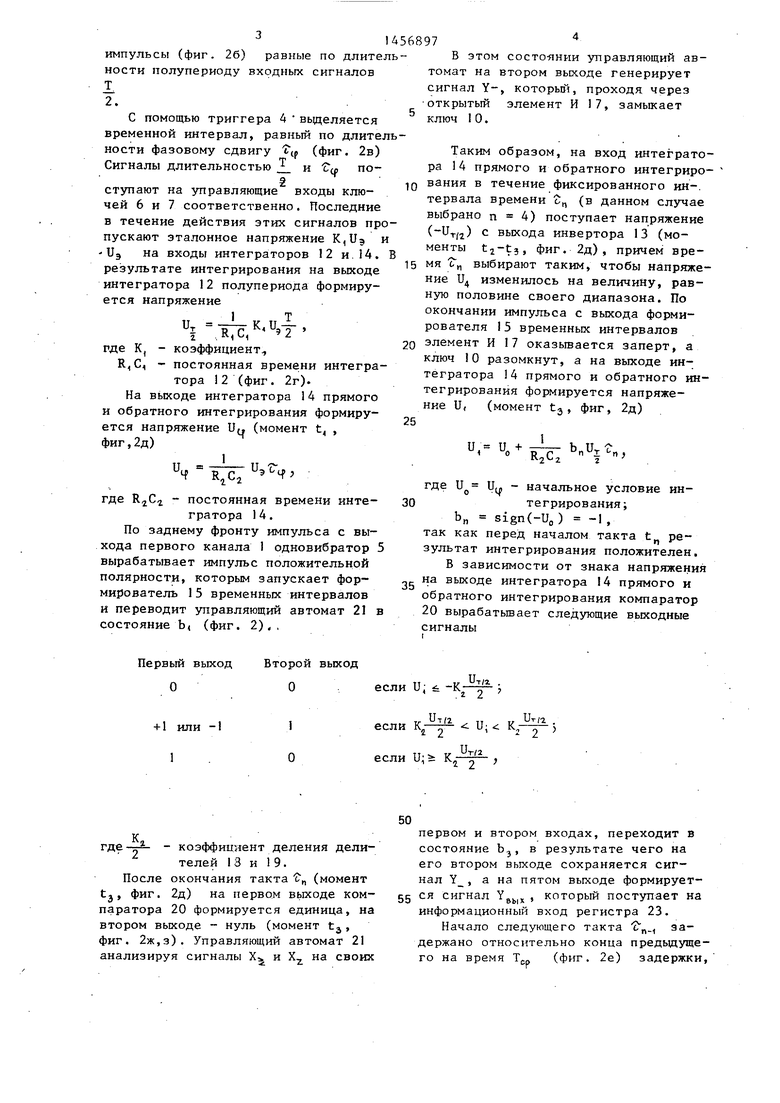

Обозначения, принятые на фиг. 2: а - входные сигналы, б - сигналы на выходах первого и второго параллельных каналов 1 , - сигнал: на выходе триггера 4, г - сигнал на выходе ин тегратора 12 полупериода и на выходе инвертора 13, д - сигнал на выходе интегратора 14 прямого и обратного

ug . подается на входы ключей 6 и 7 соответственно. Выход ключа 6 подключен к входу ин-, тегратора 12 полупериода, который шунтирован ключом 8, выход интегратора 12 полупериода соединен с входом ключа 9, с входом инвертора 13 и через делитель 18 с первым пороговым входом сдвоенного компаратора 20. Вы- ход инвертора 13 подключен к. входу ключа 10 и через делитель 19 к второму пороговому входу сдвоенного компаратора 20. ..

55

лов, ж - сигнал на первом выходе сдв енного компаратора 20, з - сигнал на втором выходе сдвоенного компаратора 20.

Устройство работает следующим образом.

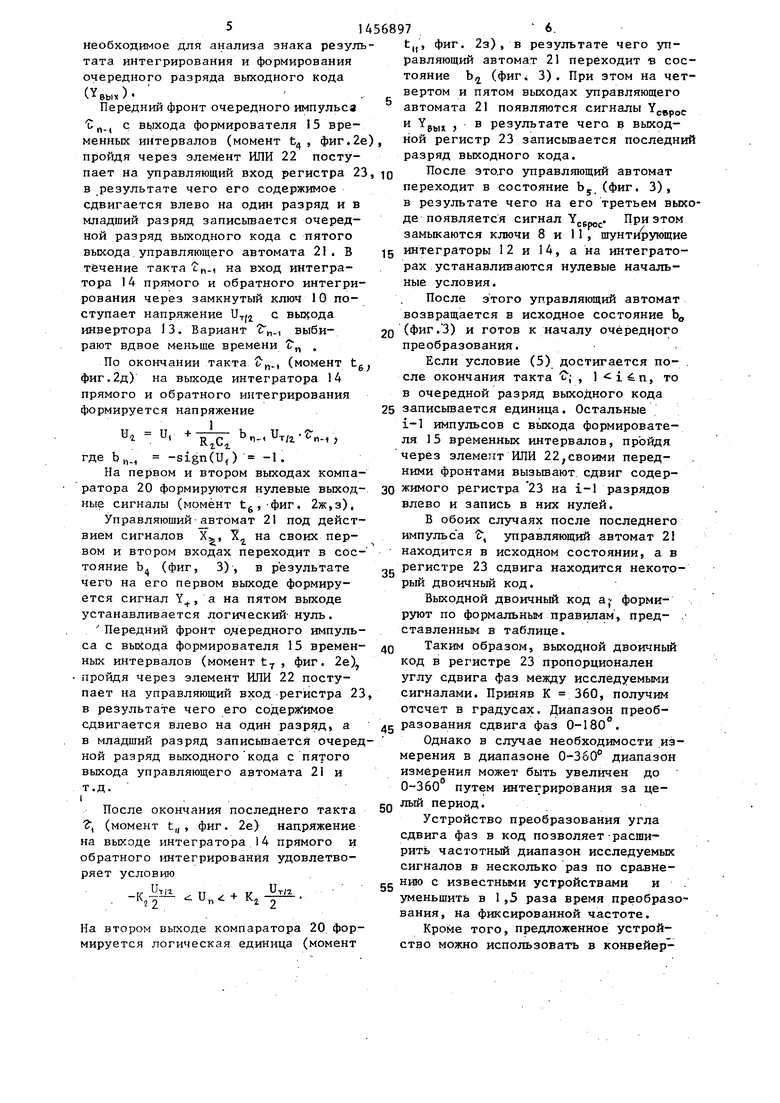

Перед началом работы управляющий автомат 21 устанавливается в исходное состояние Ь (фиг. 3) путем подачи кратковременного импульса на шину 24 установа. Из синусоидальных входных сигналов и,, и( фиг, 2а) в каналах 1 формируются прямоугольные

10

f

20

25

30

5

0

5 интегрирования, е - сигнал на выходе формирователя 15 временных нитерйа-

Выходы ключей 7, 9 и 10 соединены с входом интегратора 14 прямого и обратного- интегрирования, который шунтирован ключом 11. Выход интегратора 14 прямого и обратного интегрирования подключен к входу сдвоенного компа- ратора.20, первый и второй выходы которого соединены соответственно с первым и вторым входами управляющего автомата 21. Выход формирователя 15 временных интервалов подключен к третьему входу управляющего автоматй 21 ,к первому входу элемента ИЛИ 22 и к первым входам элементов И 1 6 и 17, выходы которых соединены соответственно с.управляющими входами ключей 9 и 10. Первьй и второй выходы управляющего автомата 21 подключены соответственно к вторым входам элементов И 16 и -17. Третий вькод управляющего автомата 21 соединен с управляющими входами ключей 8 и 1I. Четвертый выход управляющего автомата 21 подключен к второму входу элемента ИЛИ 22, выход которого соединен с управляющим входом выходного регистра 23. Пятый выход управляющего автомата 21 подключен к информационному .входу выходного регистра 23. Шина 24 установа подключе- на к пятому входу управляющего автомата 21. Управляющий автомат 21 (фиг. 4) содержит шины 25 и 45, эле-- менты НЕ 46-48, элементы И-НЕ 49-63, триггеры 64-67, элементы И-НЕ 68-73, элементы НЕ 74-77 и элемент И-НЕ 78.

Обозначения, принятые на фиг. 2: а - входные сигналы, б - сигналы на выходах первого и второго параллельных каналов 1 , - сигнал: на выходе триггера 4, г - сигнал на выходе интегратора 12 полупериода и на выходе инвертора 13, д - сигнал на выходе интегратора 14 прямого и обратного

5 интегрирования, е - сигнал на выходе формирователя 15 временных нитерйа-

5

лов, ж - сигнал на первом выходе сдвоенного компаратора 20, з - сигнал на втором выходе сдвоенного компаратора 20.

Устройство работает следующим образом.

Перед началом работы управляющий автомат 21 устанавливается в исходное состояние Ь (фиг. 3) путем подачи кратковременного импульса на шину 24 установа. Из синусоидальных . входных сигналов и,, и( фиг, 2а) в каналах 1 формируются прямоугольные

1456897

импульсы (фиг. 26) равные по длительности полупериоду входных сигналов

И 2.

то си от

С помощью триггера 4 вьщеляется временной интервал, равный по длителности фазовому сдвигу (фиг. 2в) Сигналы длительностью и с о, по2

ступают на управляющие входы ключей 6 и 7 соответственно. Последние в течение действия этих сигналов пропускают эталонное напряжение К,иэ и

Ug на входы интеграторов 12 и.14. результате интегрирования на выходе интегратора 12 полупериода формируется напряжение

1 Т

11 - If ТТ

т R г 9 9 2 , К, L,

где К, - коэффициент

R,C - постоянная времени интегратора 12 (фиг. 2г). На выходе интегратора 14 прямого и обратного интегрирования формируется напряжение Uj. (момент t , фиг,2д)

и,. г и.

R.C

Ч

где - постоянная времени интегратора 14.

По заднему фронту импульса с выхода первого канала 1 одновибратор 5 вырабатывает импульс положительной полярности, которым запускает формирователь 15 временных интервалов и переводит управляющий автомат 21 в состояние b4 (фиг. 2),,

В этом состоянии управляющий автомат на втором выходе генерирует сигнал Y-, которьп, проходя через открытый элемент И 17, замыкает

ключ I о.

Таким образом, на вход интегратора 14 прямого и обратного интегриро- 1Q вания в течение фиксированного ин-. тервала времени о (в данном случае выбрано п 4) поступает напряжение (Urfi) с выхода инвертора 13 (моменты ,, фиг. 2д), причем вре5 мя б „ выбирают таким, чтобы напряжение и изменилось на величину, равную половине своего диапазона. По окончании импульса с выхода формирователя 15 временных интервалов

0 элемент И 17 оказьгоается заперт, а ключ 10 разомкнут, а на выходе интегратора 14 прямого и обратного интегрирования формируется напряжение и, (момент tj, фиг, 2д)

5

и„ +

1

RjC,

bnUr о

2

где и U( - начальное условие ин30тегрирования;

Ь„ sign(-Uo) -1. так как перед началом такта t результат интегрирования положителен. В зависимости от знака напряжени

35 выходе интегратора 14 прямого и обратного интегрирования компаратор 20 вырабатьшает следующие выходные сигналы

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Интегрирующий аналого-цифровой преобразователь | 1982 |

|

SU1202056A1 |

| Электромагнитный расходомер | 1986 |

|

SU1509600A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией | 1989 |

|

SU1656691A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1458862A1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

Изобретение относится к электроизмерительной технике и служит для расширения частотного диапазона и уменьшения времени преобразования. Устройство содержит два параллельных / и Установка канала 1, включающих каждый входной блок 2 и формирователь 3 прямоугольных импульсов. Кроме того, устройство содержит IK-триггер.4, электронные ключи 6-11, интегратор 12 полу-- . периода, инвертор 13, интегратор 14 прямого и обратного интегрирования, элемент И 16, сдвоенный компаратор 20 и управляющий элемент 21, Введение одновибратора 5, формирователя 15 временных интервалов, длительности которых относятся как веса двоичных разрядов, элемента И 17, делителей 18 и 19 напряжения, элемента ИЛИ 22 и выходного регистра 23 сдвига позволяет использовать устройство в конвейерных вьгчислительных системах, т.к. выходной код формируется старшими разрядами вперед уже в процессе преобразования. 4 ил.,1 табл. (/) ОС ч сд . 1

Второй выход

о

1

о

К,

где - коэффициент деления делителей 13 и 19.

После окончания такта о (момент tJ, фиг. 2д) на первом вькоде компаратора 20 формируется единица, на втором выходе - нуль (момент t, фиг. 2ж,з). Управляющий автомат 21 анализируя сигналы Х и Х на своих

UT

если U; ;

если К,- - U; . К,- 5

если К

Ur/a 1 2

50

первом и втором входах, переходит в состояние bj, в результате чего на его втором выходе сохраняется сигнал Y, а на пятом выходе формирует- 55 ся сигнал У , который поступает на информационный вход регистра 23.

Начало следующего такта J n., задержано относительно конца предьщуще- го на время Т (фиг. 2е) задержки,

необходимое для анализа знака результата интегрирования и формирования очередного разряда выходного кода

(бьш)

Передний фронт очередного импульса

ПМ

с вьгхода формирователя 15 временных интервалов (момент Ц , фиг,2е), пройдя через элемент ИЛИ 22 поступает на управляющий вход регистра 23, ю в результате чего его содержимое сдвигается влево на один разряд и в младший разряд записьгоается очередной разряд выходного кода с пятого выхода.управляющего автомата 21. В течение такта t., на вход интегратора 1Д прямого и обратного интегрирования через замкнутый ключ 10 поступает напряжение UTfj с вьпсода инвертора 13. Вариант „., выбирают вдвое меньще времени t ,

По окончании такта D ., (момент tg фиг.2д) на выходе интегратора 14 прямого и обратного интегрирования формируется напряжение 1

и

г

Ьп- т1г п1 J

20

RzCi

где bj,., -sign(Uf) -1.

На первом и втором выходах компаратора 20 формируются нулевые выходные сигналы (момент tg, фиг. 2ж,з),

Управляющий-автомат 21 под действием сигналов х, 1( на своих первом и втором входах переходит в сое- тояние Ь (фиг, 3), в результате чего на его первом выходе формируется сигнал Y, а на пятом выходе устанавливается логический- нуль.

Передний фронт очередного импульса с вывода формирователя 15 временных интервалов (момент t фиг. 2е) пройдя через элемент ИЛИ 22 поступает на управляющий вход регистра 23, в результате чего его содержгимое сдвигается влево на один разряд, а в младший разряд записывается очередной разряд выходного кода с пятого выхода управляющего автомата 21 и т.д.

5

25

30

4g

gQ

35

40

После окончания последнего такта , (момент t,, , фиг. 2е) напряжение на выходе интегратора 14 прямого и обратного интегрирования удовлетворяет условию

Um

к -К, 2

К,

На втором выходе компаратора 20. формируется логическая единица (момент

1456897

ьфиг. 2з), в результате чего уп

0

равляющий автомат 21 переходит в состояние Ь (фиг 3). При этом на четвертом и пятом выходах управляющего автомата 21 появляются сигналы и , в результате чего в выходной регистр 23 записьшается последний разряд выходного кода.

После это.го управляющий автомат переходит в состояние Ь (фиг. 3), в результате чего на его третьем выходе появляется сигнал Yjp. При этом замыкаются ключи 8 и 11, шунтирующие 5 интеграторы 12 и 14, а на интеграторах устанавливаются нулевые начальные условия.

После этого управляющий автомат возвращается в исходное состояние Ь„ (фиг. З) и готов к началу очередного преобразования.

Если условие (5) достигается по- . еле окончания такта , 1 i 6 п, то в очередной разряд выходного кода 5 записьшается единица. Остальные

i-1 импульсов с выхода формирователя 15 временных интервалов, пройдя через элемент ИЛИ 22,своими передними фронтами вызьшают. сдвиг содер- 0 жимого регистра 23 на i-1 разрядов влево и запись в них нулей.

В обоих слзгчаях после последнего импульс а , управляющий автомат 21 находится в исходном состоянии, а в регистре 23 сдвига находится некоторый двоичный код.

Выходной двоичный код а;- формируют по формальным правилам, пред- . ставленным в таблице.

Таким образом, выходной двоичный код в регистре 23 пропорционален углу сдвига фаз между исследуемыми сигналами. Приняв К 360, получим отсчет в градусах. Диапазон преоб- g разования сдвига фаз 0-180°.

Однако в случае необходимости измерения в диапазоне 0-360 диапазон измерения может быть увеличен до 0-360 путем интегрирования за це- Q лый период.

Устройство преобразования угла сдвига фаз в код позволяет-расширить частотный диапазон исследуемых сигналов в несколько раз по сраане- нию с известными устройствами и

5

0

5

уменьшить в 1,5 раза время преобразо вания, на фиксированной частоте.

Кроме того, предложенное устройство можно использовать в конвейерных вычислительных системах, так как выходной код формируется старшими разрядами вперед уже в процессе преобразования.

Применение устройства в многоканальных системах для автоматизации экспериментальных исследований даст значительный экономический эффект за счет сокращения сроков проведения опыта и уменьшения количества необходимых преобразователей.

Формула изобретения

Устройство для преобразования угла сдвига фаз в двоичный код, содержащее два параллельных канала, выполненных из последовательно соединенных входных блоков и формирователей, выходы которых соединены с входами 1К-триггера, выход формирователя первого канала соединен с управляющим входом первого ключа, выходом соединенного с входом интегратора полу- периода, второй ключ, управляющий вход которого соединен с выходом IK- триггера, третий ключ,вход которого соединен с выходом первого ключа, а выход - с выходом интегратора полу- периода, при этом вход интегратора прямого и обратного преобразования соединен с выходами четвертого и пятого ключей и входом щестого ключа, а выход -. с выходами шестого ключа. и входом компаратора, выходы которого соединены соответственно с первым и вторым входами управляющего автомата, при этом выход интегратора полупериода через инвертор соединен с входом пятого ключа, и элемент И, .отличающееся тем что, с целью расширения частотного

+ 1 или

+1 или -1

+1 или -I

О

диапазона и уменьшения времени преобразования, в него введены одно-- вибратор , формирователь временных интервалов, длительности которых относятся, как веса двоичных разрядов, второй элемент И,, элемент, ИЛИ, два делителя напряжения и регистр сдвига, при этом выход третьего ключа соеди-

Q нен с входом четвертого ключа, выход формирователя первого канала соединен с входом одновибратора, формирователь временных интервалов выходом соединен с третьим-входом управляю5 щего автомат,а и первыми входами элемента ИЛИ и первого и второго эле-: ментов И, а входом - с четвертью входом управляющего автомата и выходом одновибратора, вторые входы первого

0 и второго элементов Л соединены соответственно с первым и вторым выходами управляющего автомата, а выходы соединены соответственно с управляющими входами четвертого и пя5 того ключей, вход первого ключа соединен с клеммой эталонного напряжения К,из(К, - 1 ) , при этом вход второго ключа соединен с клеммой эталонного напряжения U, а выход соединен с входом интегратора прямого и обратного интегрирования, выход интегратора полупериода через первый делитель напряжения соединен с первым пороговым входом компаратора, второй пороговый вход которого через второй делитель напряжения соединен с выходом инвертора, причем третий выход управляющего автомата соединен с входами третьего и шестого ключей, чет0 вертый выход через элемент ИЛИ соединен с управляющим входом регистра сдвига, а пятый выход - с информационным входом регистра сдвига.

0

5

+ 1

1 О

О О

.i f Начало )A

.

| Глинченко А.С | |||

| и др | |||

| Цифровые методы измерения сдвига фаз | |||

| Новосибирск: Наука, 1979, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Устройство для измерения угла сдвига фаз в диапазоне инфранизких частот | 1974 |

|

SU725039A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-02-07—Публикация

1986-12-29—Подача