Изобретение относится к технике связи и может использоваться в системах передачи данных.

Цель изобретения - повышение помехоустойчивости.

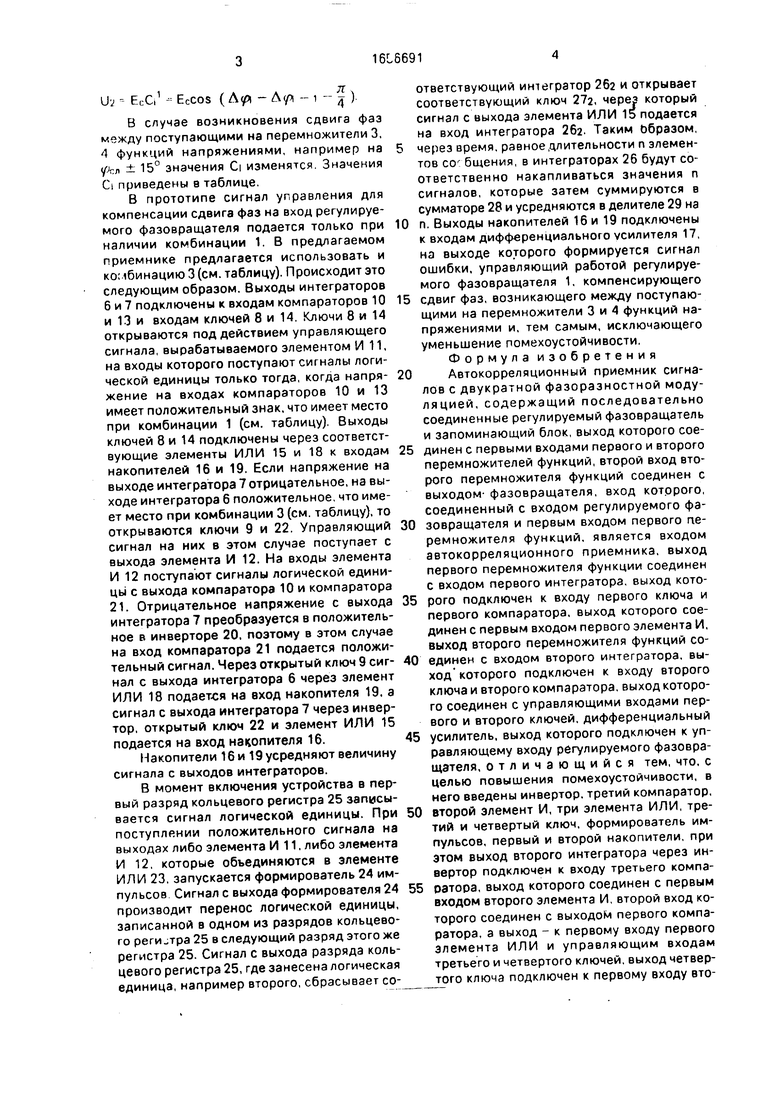

На фиг. 1 изображена структурная схема предложенного автокорреляционного приемника: на фиг 2 - схема накопителя.

Автокорреляционный приемник содержит регулируемый фазовращатель 1, запоминающий блок 2, первый перемножитель 3 функций, второй перемножитель 4 функций, фазовращатель 5, первый, второй интеграторы 6, 7, первый ключ 8, третий ключ 9, первый компаратор 10 первый элемент И 11, второй элемент И 12, второй компаратор 13, второй ключ 14, второй элемент ИЛИ 15, первый накопитель 16. дифференциальный усилитель 17, третий элемент ИЛИ 18, второй накопитель 19, инвертор 20, третий компаратор 21, четвертый ключ 22, первый элемент

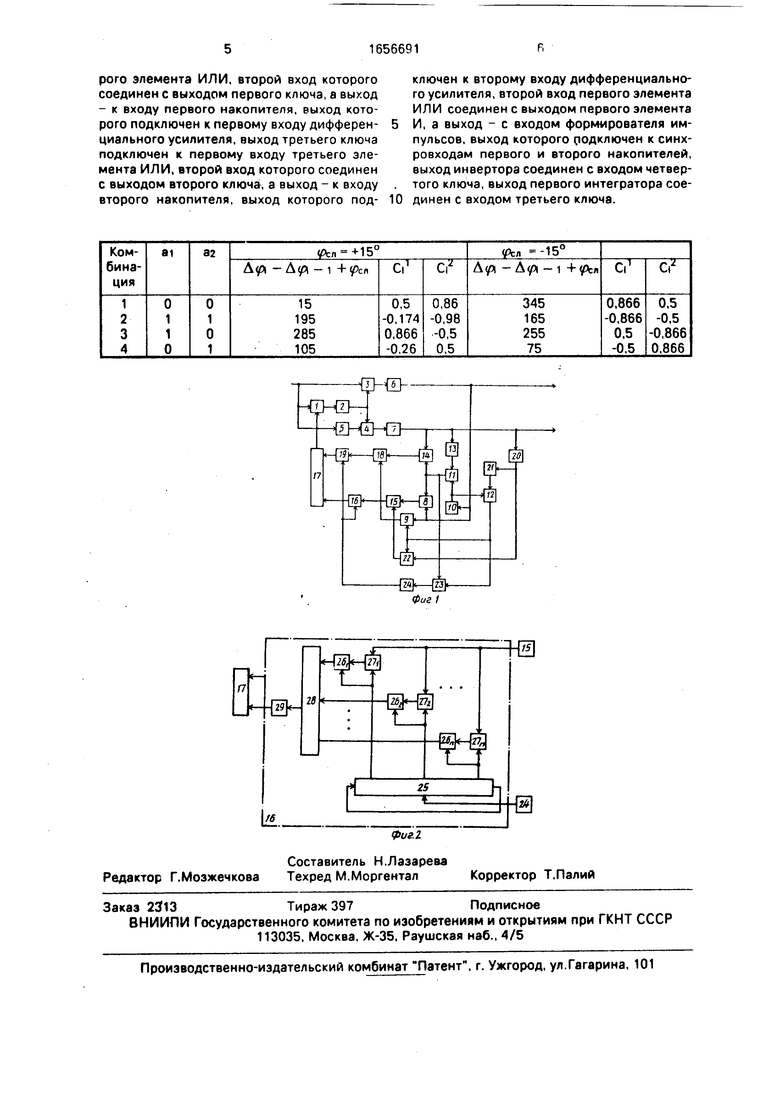

ИЛИ 23, формирователь 24 импульсов. Накопитель 16 содержит кольцевой регистр 25, интеграторы 26, ключи 27, сумматор 28, делитель 29 на п.

Автокорреляционный приемник работает следующим образом.

Сигнал поступает на перемножитель 3 и через фазовращатель 5, обеспечивающий сдвиг фаз на ж /2, на перемножитель 4. На другие входы перемножителей 3 и 4 входной сигнал поступает через регулируемый фазовращатель 1 и запоминающий блок 2, хранящий информацию о предыдущей посылке. Регулируемый фазовращатель 1 обеспечивает постоянную величину сдвига фазы сигнала на выходе запоминающего блока 2 по отношению к входному сигналу на я /4.

После перемножения и интегрирования на выходах интеграторов 6 и 7 формируются переданные в канал двоичные сигналы:

Ui-EcCi1-Eccos ( -Др|-1 +J);

(Л

С

о ел о о ю

U - ECC,1 - Eccos ( Api - Луч - 1 -- ).

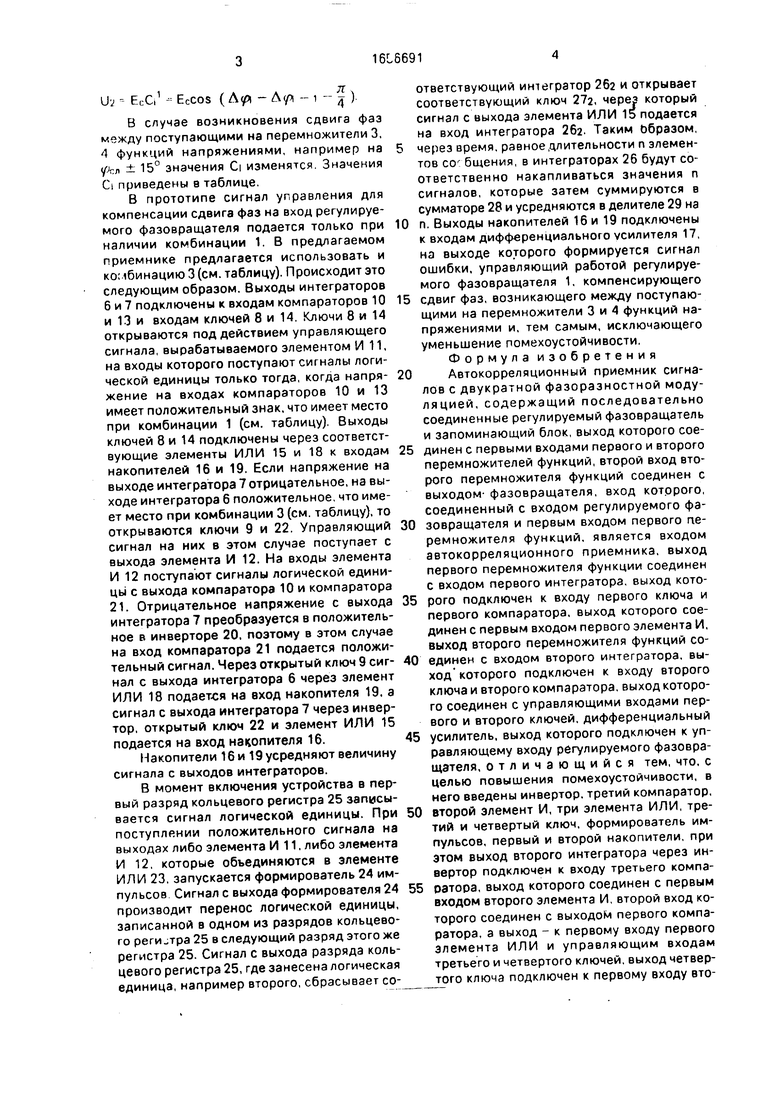

В случае возникновения сдвига фаз между поступающими на перемножители 3, 4 функций напряжениями, например на уел ± 15° значения Ci изменятся. Значения Ciприведены в таблице,

В прототипе сигнал управления для компенсации сдвига фаз на вход регулируемого фазовращателя подается только при наличии комбинации 1. В предлагаемом приемнике предлагается использовать и комбинацию 3 (см. таблицу). Происходит это следующим образом. Выходы интеграторов 6 и 7 подключены к входам компараторов 10 и 13 и входам ключей 8 и 14, Ключи 8 и 14 открываются под действием управляющего сигнала, вырабатываемого элементом И 11, на входы которого поступают сигналы логической единицы только тогда, когда напряжение на входах компараторов 10 и 13 имеет положительный знак, что имеет место при комбинации 1 (см. таблицу). Выходы ключей 8 и 14 подключены через соответствующие элементы ИЛИ 15 и 18 к входам накопителей 16 и 19. Если напряжение на выходе интегратора 7 отрицательное, на выходе интегратора 6 положительное, что имеет место при комбинации 3 (см. таблицу), то открываются ключи 9 и 22. Управляющий сигнал на них в этом случае поступает с выхода элемента И 12. На входы элемента И 12 поступают сигналы логической единицы с выхода компаратора 10 и компаратора 21. Отрицательное напряжение с выхода интегратора 7 преобразуется в положительное в инверторе 20. поэтому в этом случае на вход компаратора 21 подается положительный сигнал. Через открытый ключ 9 сигнал с выхода интегратора 6 через элемент ИЛИ 18 подается на вход накопителя 19, а сигнал с выхода интегратора 7 через инвертор, открытый ключ 22 и элемент ИЛИ 15 подается на вход накопителя 16.

Накопители 16 и 19 усредняют величину сигнала с выходов интеграторов.

В момент включения устройства в первый разряд кольцевого регистра 25 записывается сигнал логической единицы. При поступлении положительного сигнала на выходах либо элемента И 11, либо элемента И 12, которые объединяются в элементе ИЛИ 23. запускается формирователь 24 импульсов Сигнал с выхода формирователя 24 производит перенос логической единицы, записанной в одном из разрядов кольцевого реги-тра 25 в следующий разряд этого же регистра 25. Сигнал с выхода разряда кольцевого регистра 25, где занесена логическая единица, например второго, сбрасывает соответствующий интегратор 262 и открывает соответствующий ключ 272, через который сигнал с выхода элемента ИЛИ 1о подается на вход интегратора 262. Таким образом,

через время, равное длительности п элементов сог бщения, в интеграторах 26 будут соответственно накапливаться значения п сигналов, которые затем суммируются в сумматоре 28 и усредняются в делителе 29 на

0 п. Выходы накопителей 16 и 19 подключены к входам дифференциального усилителя 17, на выходе которого формируется сигнал ошибки, управляющий работой регулируемого фазовращателя 1, компенсирующего

5 сдвиг фаз, возникающего между поступающими на перемножители 3 и 4 функций напряжениями и, тем самым, исключающего уменьшение помехоустойчивости. Формула изобретения

0Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией, содержащий последовательно соединенные регулируемый фазовращатель и запоминающий блок, выход которого сое5 динен с первыми входами первого и второго перемножителей функций, второй вход второго перемножителя функций соединен с выходом- фазовращателя, вход котррого, соединенный с входом регулируемого фа0 зовращателя и первым входом первого перемножителя функций, является входом автокорреляционного приемника, выход первого перемножителя функции соединен с входом первого интегратора, выход кото5 рого подключен к входу первого ключа и первого компаратора, выход которого соединен с первым входом первого элемента И, выход второго перемножителя функций со0 единен с входом второго интегратора, выход которого подключен к входу второго ключа и второго компаратора, выход которого соединен с управляющими входами первого и второго ключей, дифференциальный

5 усилитель, выход которого подключен к управляющему входу регулируемого фазовращателя, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены инвертор, третий компаратор,

0 второй элемент И, три элемента ИЛИ, третий и четвертый ключ, формирователь импульсов, первый и второй накопители, при этом выход второго интегратора через инвертор подключен к входу третьего компа5 ратора, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого компаратора, а выход - к первому входу первого элемента ИЛИ и управляющим входам третьего и четвертого ключей, выход четвертого ключа подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом первого ключа, а выход - к входу первого накопителя, выход которого подключен к первому входу дифференциального усилителя, выход третьего ключа подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом второго ключа, а выход - к входу второго накопителя, выход которого под0

ключен к второму входу дифференциального усилителя, второй вход первого элемента ИЛИ соединен с выходом первого элемента И, а выход - с входом формирователя импульсов, выход которого подключен к синх- ровходам первого и второго накопителей, выход инвертора соединен с входом четвертого ключа, выход первого интегратора соединен с входом третьего ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автокорреляционный приемник сигналов с двухкратной фазоразностной модуляцией | 1991 |

|

SU1817252A1 |

| Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией | 1984 |

|

SU1197135A1 |

| Адаптивный приемник сигналов минимальной частотной манипуляции | 1989 |

|

SU1835611A1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| УСТРОЙСТВО ДЛЯ ГЕОЭЛЕКТРОРАЗВЕДКИ | 2008 |

|

RU2366983C1 |

| АППАРАТУРА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, УСТОЙЧИВАЯ К ВОЗДЕЙСТВИЮ МОЩНОЙ ЧМ ПОМЕХИ | 2001 |

|

RU2205506C1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией | 2017 |

|

RU2660595C1 |

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Автокорреляционный приемник содержит регулируемый фазовращатель 1, запоминающий блок 2, перемножители 3 и 4 функций, фазовращатель 5, интеграторы 6 и 7, ключи 8, 9, 14 и 22, компараторы 10, 13 и 21, элементы И 11 и 12, элементы ИЛИ 15, 18 и 23, накопители 16 и 19. дифференциальный усилитель 17, инвертор 20 и формирователь 24 импульсов. В данном приемнике осуществляется формирование сигнала ошибки, управляющего работой регулируемого фазовращателя 1, который компенсирует сдвиг фаз, возникающий между напряжениями, поступающими на перемножители 3 и 4 Тем самым исключается уменьшение помехоустойчивости вследствие воздействия нестабильности несущей. 2 ил.

28

| Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией | 1984 |

|

SU1197135A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-09—Подача