Изобретение относится к измерительной технике и может быть использовано в цифровых вольтметрах.

Цель изобретения - повышение бы- стродействия при выборе диапазона измерений.

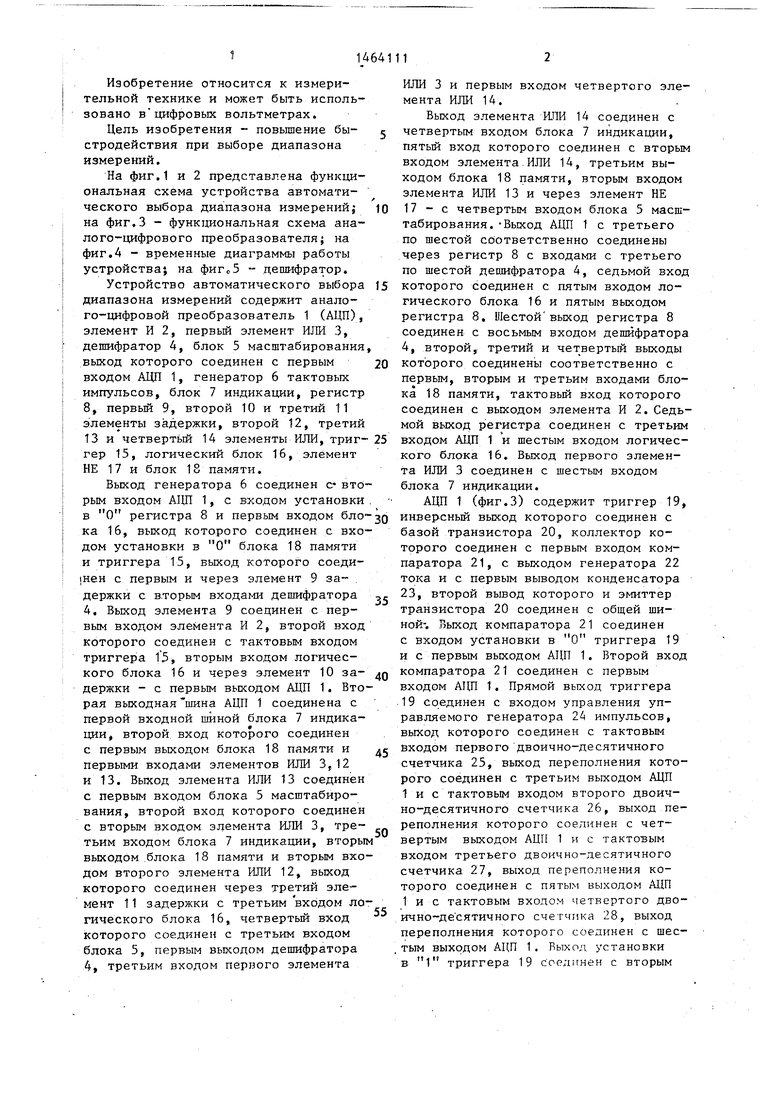

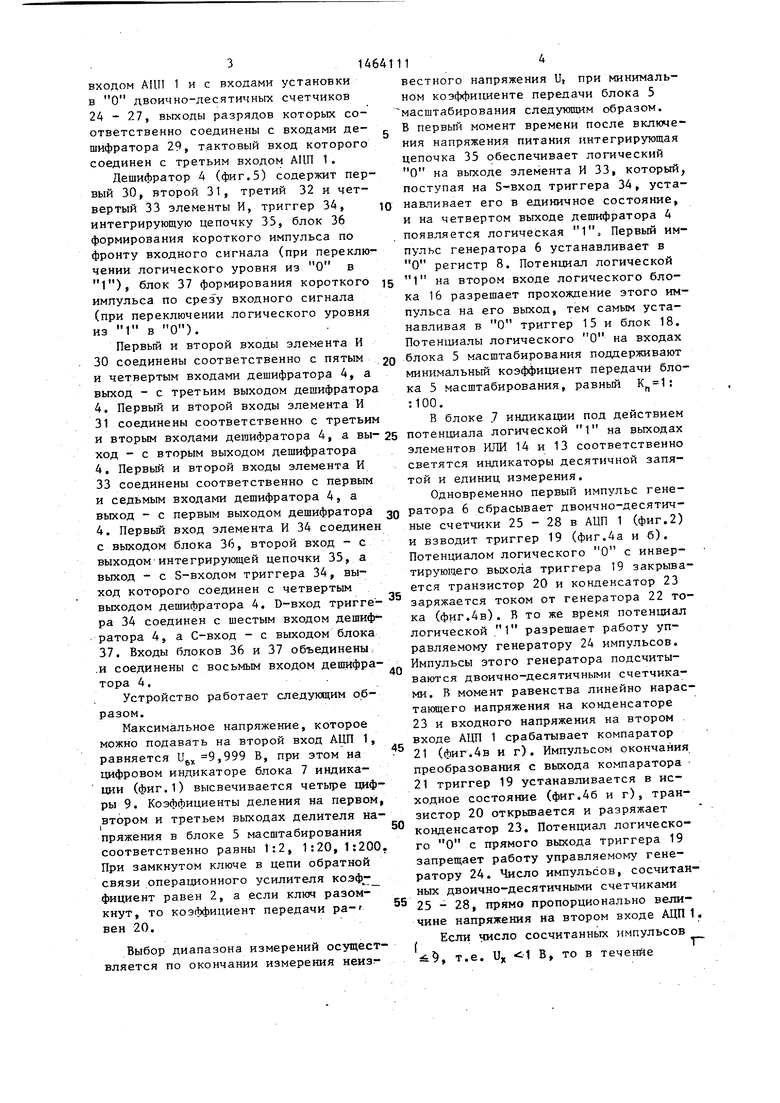

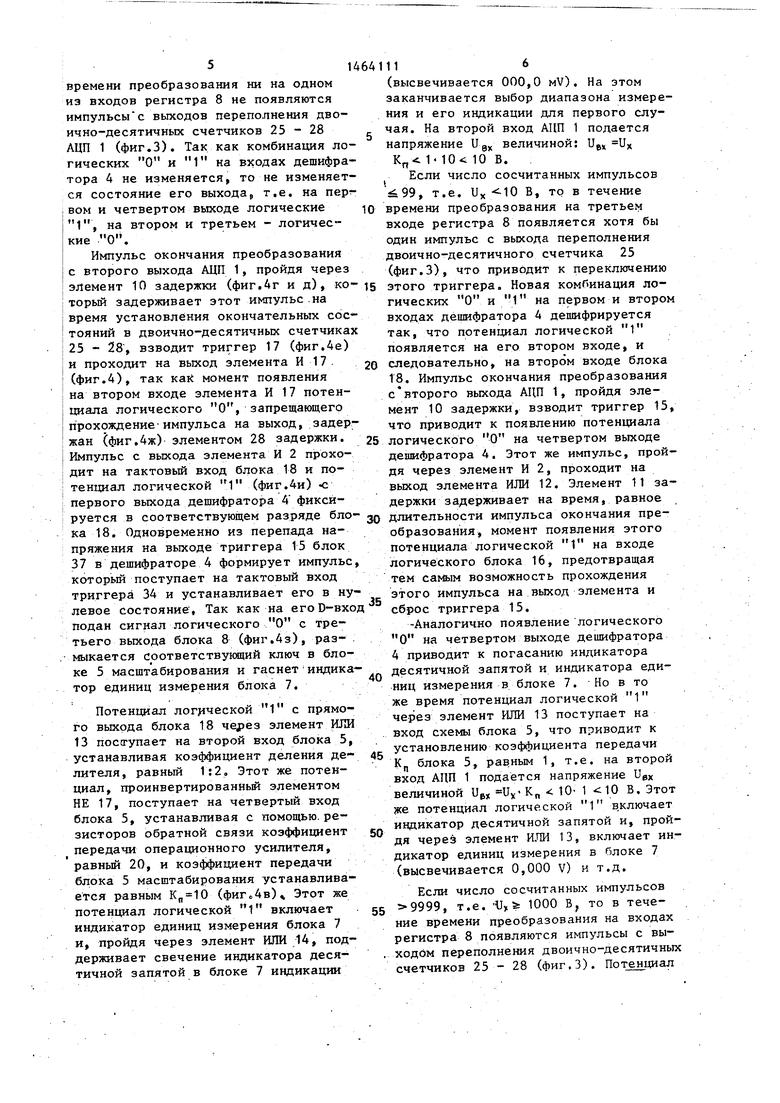

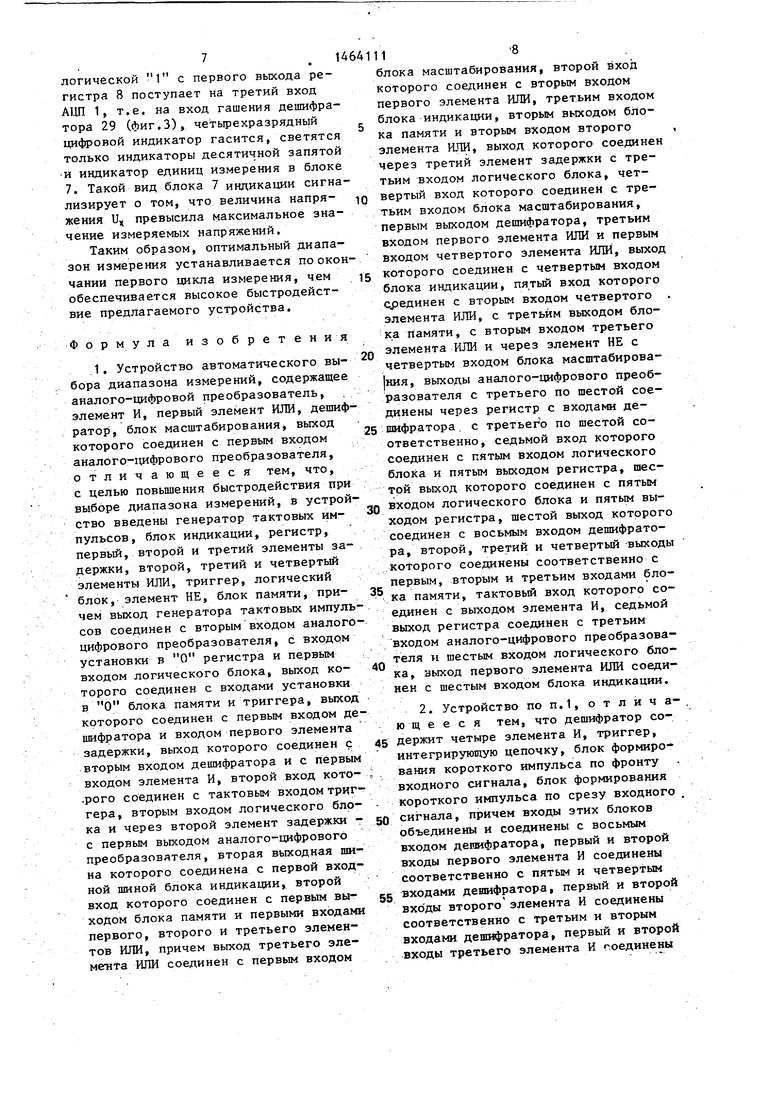

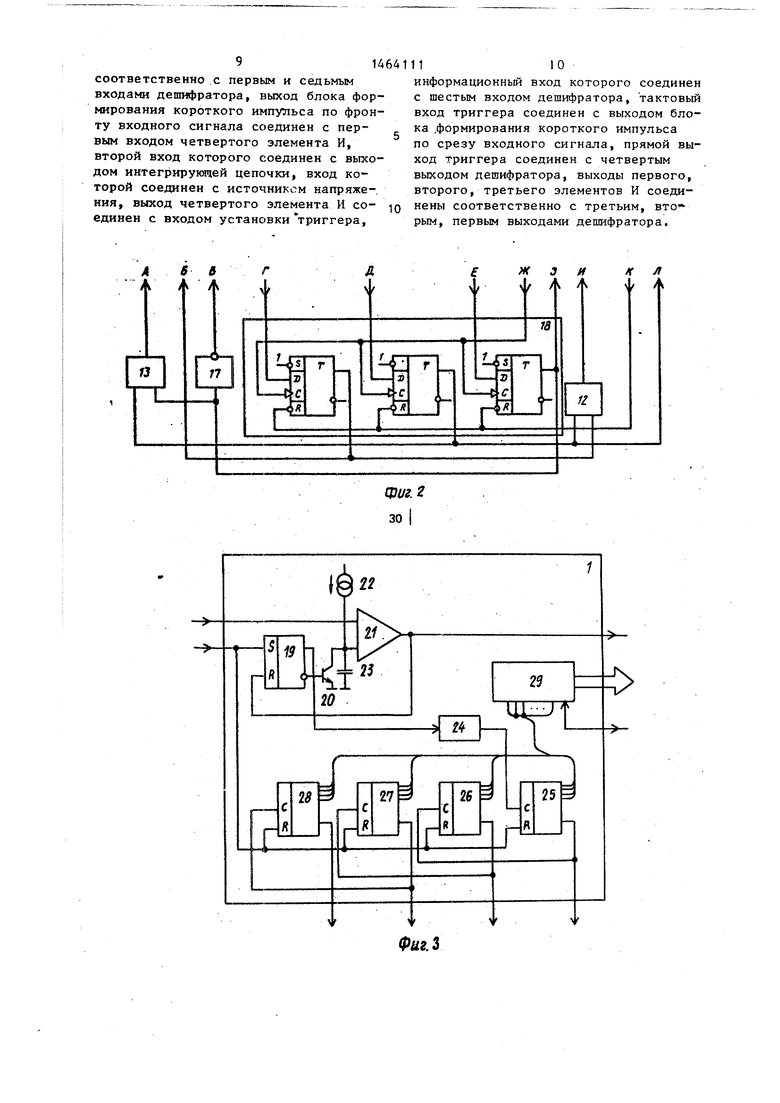

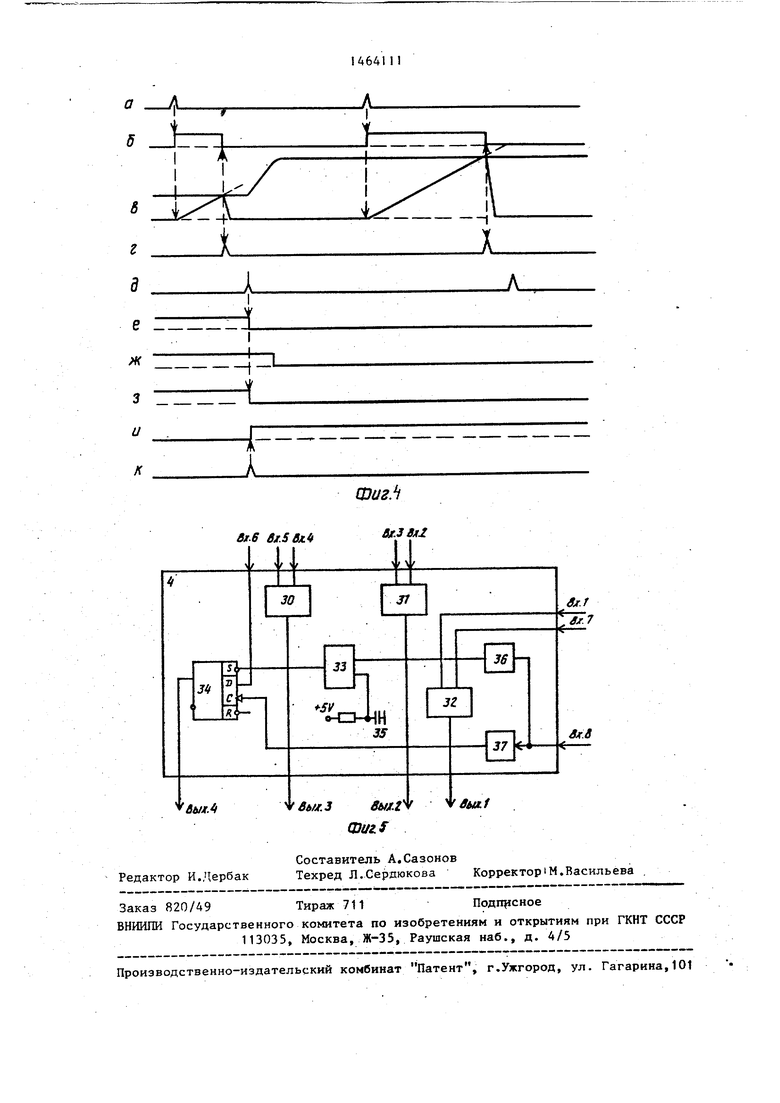

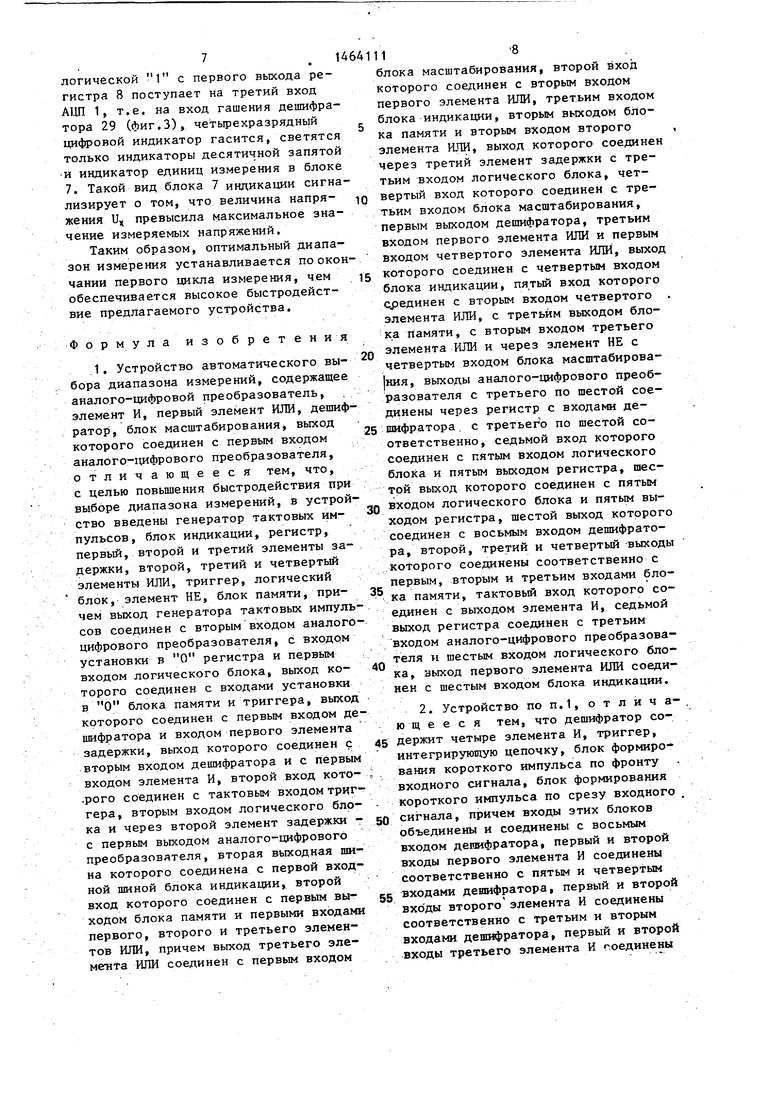

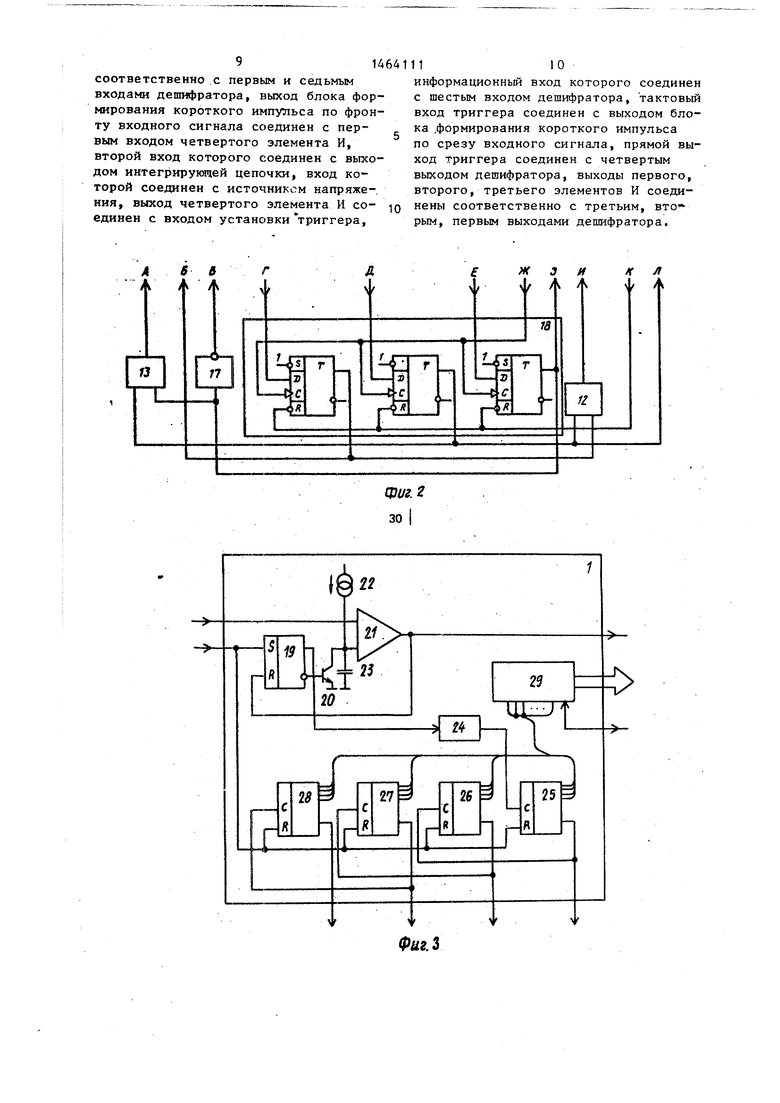

На фиг.1 и 2 представлена функциональная схема устройства автоматического выбора диапазона измерений; на фиг.З - функциональная схема аналого-цифрового преобразователя; на фиг.4 - временные диаграммы работы устройства; на фиг с 5 - дешифратор.

Устройство автоматического выбора диапазона измерений содержит аналого-цифровой преобразователь 1 (АЦП), элемент И 2, первый элемент ШШ 3, дешифратор 4, блок 5 масштабирования выход которого соединен с первым входом АЦП 1, генератор 6 тактовых импульсов, блок 7 индикации, регистр 8, первьй 9, второй 10 и третий 11 элементы задержки, второй 12, третий 13 и четвертьгй 14 элементы ИЛИ, триг- гер 15, логический блок 16, элемент НЕ 17 и блок 18 памяти.

Выход генератора 6 соединен с вторым входом АЦП 1, с входом установки в О регистра 8 и первым входом бло ка 16, выход которого соединен с входом установки в О блока 18 памяти и триггера 15, вькод которого соеди- 1нен с первым и через элемент 9 за- . держки с вторым входами дешифратора 4. Выход элемента 9 соединен с первым входом элемента И 2, второй вход которого соединен с тактовым входом триггера 15, вторым входом логического блока 16 и через элемент 10 за- держки - с первым выходом АЦП 1. Вторая выходная шина АЦП 1 соединена с первой входной шиной блока 7 индикации, второй вход которого соединен с первым выходом блока 18 памяти и первыми входами элементов ИЛИ 3,12 и 13. Выход элемента ИЛИ 13 соединен с первым входом блока 5 масштабирования, второй вход которого соединен с вторым входом элемента ИЛИ 3, тре тьим входом блока 7 индикации, вторы выходом блока 18 памяти и вторым входом второго элемента ИЛИ 12, выход которого соединен через третий элемент 11 задержки с третьим входом ло гического блока 16, четвертьш вход которого соеди нен с третьим входом блока 5, первым выходом дешифратора 4, третьим входом первого элемента

с

tO

15 0 5

о с о д .

5

ИЛИ 3 и первым входом четвертого элемента ИЛИ 14.

Выход элемента ИЛИ 14 соединен с четвертым входом блока 7 индикации, пятый вход которого соединен с вторым входом элемента,ИЛИ 14, третьим выходом блока 18 памяти, вторым входом элемента ИЛИ 13 и через элемент НЕ 17 - с четвертым входом блока 5 масштабирования. -Выход АЦП 1 с третьего по шестой соответственно соединены через регистр 8 с входами с третьего по шестой дешифратора 4, седьмой вход которого соединен с пятым входом логического блока 16 и пятым выходом регистра 8. Шестой выход регистра 8 соединен с восьмым входом дешифратора 4, второй, третий и чет вертый выходы которого соединены соответственно с первым, вторым и третьим входами блока 18 памяти, тактовый вход которого соединен с выходом элемента И 2. Седьмой выход регистра соединен с третьим входом АЦП 1 и шестым входом логического блрка 16. Выход первого элемента ИЛИ 3 соединен с шестым входом блока 7 индикации.

АЦП 1 (фиг.З) содержит триггер 19, инверсный выход которого соединен с базой транзистора 20, коллектор которого соединен с первым входом компаратора 21, с выходом генератора 22 тока и с первым выводом конденсатора 23, второй вывод которого и эмиттер Транзистора 20 соединен с общей шиной-. Выход компаратора 21 соединен с входом установки в О триггера 19 и с первым выходом АЦП 1. Второй вход компаратора 21 соединен с первым входом АЦП 1. Прямой выход триггера .19 соединен с входом управления управляемого генератора 24 импульсов, выход которого соединен с тактовым входом первого двоично-десятичного счетчика 25, выход переполнения которого соединен с третьим выходом АЦП 1 и с тактовым входом второго двоично-десятичного счетчика 26, выход переполнения которого соединен с четвертым выходом АЦП 1 и с тактовым входом третьего двоично-десятичного счетчика 27, выход переполнения которого соединен с пятым выходом АЦП 1 и с тактовым входом четвертого двоично-десятичного счетчика 28, выход переполнения которого соединен с шестым выходом АЦП 1. Выход установки в 1 триггера 19 соединен с вторым

3146

входом АЦП 1 и с входами установки в О двоично-десятичных счетчиков 24 - 27, выходы разрядов которых соответственно соединены с входами де- шифратора 29, тактовый вход которого соединен с третьим входом АЦП 1.

Дешифратор А (фиг.5) содержит первый 30, второй 31, третий 32 и четвертый 33 элементы И, триггер 34, интегрирующую цепочку 35, блок 36 формирования короткого импульса по фронту входного сигнала (при переключении логического уровня из О в 1), блок 37 формирования короткого импульса по срезу входного сигнала (при переключении логического уровня из 1 в О).

Первый и второй входы элемента И

30соединены соответственно с пятым и четвертым входами дешифратора 4, а выход - с третьим выходом дешифратора 4. Первый и второй входы элемента И

31соединены соответственно с третьим

и вторым входами дешифратора 4, а вы- ход - с вторым выходом дешифратора 4. Первый и второй входы элемента И 33 соединены соответственно с первым и седьмым входами дешифратора 4, а выход - с первым выходом дешифратора 4. Первый вход элемента И 34 соединен с выходом блока 36, второй вход - с выходом интегрирующей цепочки 35, а выход - с S-входом триггера 34, выход которого соединен с четвертым вькодом дешифратора 4. D-вход триггера 34 соединен с шестым входом дешиф . ратора 4, а С-вход - с выходом блока 37. Входы блоков 36 и 37 объединены, .и соединены с восьмым входом дешифра

тора 4.

Устройство работает следующим образом.

Максимальное напряжение, которое можно подавать на второй вход АЦП равняется ,999 В, при этом на цифровом индикаторе блока 7 индикации (фиг.1) высвечивается четыре цифры 9. Коэффициенты деления на первом втором и третьем выходах делителя напряжения в блоке 5 масштабирования соответственно равны 1:2, 1:20, 1:200 При замкнутом ключе в цепи обратной связи операционного усилителя коэф- фициент равен 2, а если ключ разомкнут, то коэффициент передачи ра- вен 20.

Выбор диапазона измерений осуществляется по окончании измерения неизг

g

0

вестного напряжения U, при минимальном коэффициенте передачи блока 5 масштабирования следующим образом. В первый момент времени после включения напряжения питания интегрирующая цепочка 35 обеспечивает логический О на выходе элемента И 33, который, поступая на S-вход триггера 34, устанавливает его в единичное состояние, и на четвертом выходе дешифратора 4 появляется логическая 1, Первый импульс генератора 6 устанавливает в О регистр 8. Потенциал логической 1 на втором входе логического блока 16 разрешает прохождение этого импульса на его выход, тем самым устанавливая в О триггер 15 и блок 18. Потенциалы логического О на входах блока 5 масштабирования поддерживают минимальный коэффициент передачи блока 5 масштабирования, равный

:100.

В блоке .7 индикации под действием потенциала логической 1 на выходах элементов ИЛИ 14 и 13 соответственно светятся индикаторы десятичной запятой и единиц измерения.

Одновременно первый импульс генератора 6 сбрасывает двоично-десятичные счетчики 25 - 28 в АЦП 1 (фиг.2) и взводит триггер 19 (фнг.а и б). Потенциалом логического О с инвертирующего выхода триггера 19 закрьша- ется транзистор 20 и конденсатор 23 заряжается током от генератора 22 тока (фиг.4в). В то же время потенциал логической 1 разрешает работу управляемому генератору 24 импульсов. Импульсы этого генератора подсчитываются двоично-десятичными счетчиками. В момент равенства линейно нарастающего напряжения на конденсаторе 23 и входного напряжения на втором входе АЦП 1 срабатывает компаратор 21 (фиг.4в и г). Импульсом окончания, преобразования с выхода компаратора 21 триггер 19 устанавливается в исходное состояние (фиг.46 и г), транзистор 20 открывается и разряжает конденсатор 23. Потенциал логического О с прямого выхода триггера 19 запрещает работу управляемоьту генератору 24. Число импульсов, сосчитанных двоично-десятичньши счетчиками 25-28, прямо пропорционально величине напряжения на втором входе АЦП 1.

Если число сосчитанных импульсов , т.е. Ux 1 В, то в течение

5

Г

514

времени преобразования ни на одном

из входов регистра 8 не появляются импульсы с вькодов переполнения двоично-десятичных счетчиков 25-28 АЦП 1 (фиг.З). Так как комбинация логических О и 1 на входах дешифратора А не изменяется, то не изменяется состояние его выхода, т.е. на пер вом и четвертом выходе логические 1, на втором и третьем - логические О.

Импульс окончания преобразования с второго выхода АЦП 1, пройдя через элемент 10 задержки (фиг.Аг ид), ко- торый задерживает этот импульс.на время установления окончательных состояний в двоично-десятичных счетчиках 25 - 28, взводит триггер 17 (фиг.Ае) и проходит на выход элемента И 17 . (фиг.4), так KBTt момент появления на втором входе элемента И 17 потенциала логического О, запрещающего прохождение-импульса на выход, задержан (фиг.4ж) элементом 28 задержки. Импульс с выхода элемента И 2 проходит на тактовый вход блока 18 и потенциал логической 1 (фиг.4и) первого выхода дешифратора 4 фиксируется в соответствующем разряде бло- ка 18. Одновременно из перепада напряжения на вьпсоде триггера 15 блок 37 в дешифраторе 4 формирует импульс который поступает на тактовый вход триггера 34 и устанавливает его в ну- левое состояние. Так как на eroD-вхо подан сигнал логического О с третьего выхода блока 8 (фиг.4з), раз- . мыкается соответствукнций ключ в блоке 5 масштабирования и гаснет индикатор единиц измерения блока 7.

Потенциал логической 1 с прямого выхода блока 18 элемент ИЛИ 13 поступает на второй вход блока 5, устанавливая коэффициент деления де- лителя, равный 1:2, Этот же потенциал, проинвертированный элементом НЕ 17, поступает на четвертый вход блока 5, устанавливая с помощью, резисторов обратной связи коэффициент передачи операционного усилителя, равный 20, и коэффициент передачи блока 5 масштабирования устанавливается равным (фиг,4в) Этот же потенциал логической 1 включает индикатор единиц измерения блока 7 и, пройдя через элемент ИЛИ 14, поддерживает свечение индикатора десятичной запятой в блоке 7 индикации

5 0 5

1116

(высвечивается 000,0 мУ). На этом заканчивается выбор диапазона измерения и его индикации для первого случая. На второй вход АЦП 1 подается напряжение Ug величиной: Up, Ux Кп МО 10 В. .

Если число сосчитанных импульсов , т.е. В, то в течение времени преобразования на третьем входе регистра 8 появляется хотя бы один импульс с выхода переполнения двоично-десятичного счетчика 25 (фиг.З), что приводит к переключению этого триггера. Новая комбинация ло0

гических О и 1 на первом и втором входах дешифратора 4 дешифрируется так, что потенциал логической 1 появляется на его втором входе, и следовательно, на втором входе блока 18. Импульс окончания преобразования с второго выхода АЦП 1, пройдя элемент 10 задержки, взводит триггер 15, что приводит к появлению потенциала логического О на четвертом выходе дешифратора 4. Этот же импульс, пройдя через элемент И 2, проходит на выход элемента ИЛИ 12. Элемент 11 задержки задерживает на время, равное длительности импульса окончания преобразования, момент появления этого потенциала логической 1 на входе логического блока 16, предотвращая тем самым возможность прохождения этого импульса на выход элемента и сброс триггера 15.

-Аналогично появление логического О на четвертом выходе дешифратора 4 приводит к погасанию индикатора десятичной запятой и индикатора единиц измерения в блоке 7. Но в то же время потенциал логической 1 через элемент ИЛИ 13 поступает на вход схемы блока 5, что приводит к установлению коэффициента передачи К„ блока 5, равным 1, т.е. на второй вход АЦП 1 подаётся напряжение Ugx величиной и„ Ux К„ 10- 1 10 В. Этот

11.1

же потенциал логической 1 в.ключает индикатор десятичной запятой и, пройдя через элемент ИЛИ 13, включает индикатор единиц измерения в блоке 7 (высвечивается 0,000 V) и т.д.

Если число сосчитанных импульсов 9999, т.е. -11,5 1000 В, то в течение времени преобразования на входах регистра 8 появляются импульсы с выходом переполнения двоично-десятичных счетчиков 25 - 28 (фиг.З). Пот.енциал

7, 14641

логической 1 с первого выхода регистра 8 поступает на третий вход АЦП 1, т.е. на вход гашения дешифратора 29 (фиг.З), четырехразрядный цифровой индикатор гасится, светятся только индикаторы десятичной запятой и индикатор единиц измерения в блоке 7. Такой вид блока 7 индикации сигнализирует о том, что величина напря- ю жения Ux превысила максимальное значение измеряемых напряжений.

Таким образом, оптимальный диапазон измерения устанавливается по окончании первого цикла измерения, чем 15 обеспечивается высокое быстродействие предлагаемого устройства.

ормула

и 3

обретения

20

1 Устройство автоматического выора диапазона измерений, содержащее налого-цифровой преобразователь, . . элемент И, первый элемент ИЛИ, дешифратор, блок масштабирования, выход которого соединен с первым входом аналого-цифрового преобразователя, отличающееся тем, что, с целью повьшаения быстродействия при выборе диапазона измерений, в устрои- ство введены генератор тактовых импульсов, блок индикации, регистр, первый, второй и третий элементы за- . держки, второй, третий и четвертый элементы ИЛИ, триггер, логический блок, элемент НЕ, блок памяти, при- 35 чем выход генератора тактовых импуль-- сов соединен с вторым входом аналоге-- цифрового преобразователя, с входом установки в О регистра и первым входом логического блока, выход ко- 40 торого соединен с входами установки в О блока памяти и триггера, выход которого соединен с первьм входом дешифратора и входом первого элемента задержки, выход которого соединен с « вторым входом дешифратора и с первым входом элемента И, второй вход кото- , , .рого соединен с тактовым входом триггера, вторым входом логического бло- - ка и через второй элемент задержки - 50 с первым выходом аналого-цифрового преобразователя, вторая выходная шина которого соединена с первой вход- ной шиной блока индикации, второй вход которого соединен с первым вы- 55 ходом блока памяти и первыми входами первого, второго и третьего элементов ИЛИ, причем выход третьего элемента ИЛИ соединен с первым входом

бло кот пер бло ка эл че ть ве ть пе вх вх ко бл со эл iK,a эл ч ни ра ш о

, 0 55

1 8

лока масштабирования, второй вход оторого соединен с вторым входом ервого элемента ИЛИ, третьим входом лока индикации, вторым выходом блоа памяти и вторым входом второго элемента ИЛИ, выход которого соединен через третий элемент задержки с третьим входом логического блока, четвертый вход которого соединен с третьим входом блока масштабирования, первым выходом дешифратора, третьим входом первого элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход которого соединен с четвертым входом блока индикации, пятый вход которого соединен с вторым входом четвертого . элемента ИЛИ, с третьим выходом бло- iK,a памяти, с вторым входом третьего элемента ИЛИ и через элемент НЕ с четвертым входом блока масштабирова- |ния, выходы аналого-цифрового преобразователя с третьего по шестой соединены через регистр с входами дешифратора . с третьего по шестой соответственно, седьмой вход которого соединен с пятым входом логического блока и пятым выходом регистра, шестой выход которого соединен с пятым входом логического блока и пятым выходом регистра, шестой выход которого соединен с восьмым входом дешифратора, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым и третьим входами блока памяти, тактовый вход которого соединен с выходом элемента И, седьмой выход регистра соединен с третьим входом аналого-цифрового преобразователя и шестым входом логического блока, выход первого элемента ИЛИ соединен с шестым входом блока индикации.

2 Устройство по П.1, о т л и ч а- . И) Щ е е с я тем, что дешифратор содержит четыре элемента И, триггер, интегрирующую цепочку, блок формирования короткого импульса по фронту - входного сигнала, блок формирования короткого импульса по срезу входного . сигнала, причем входы этих блоков объединены и соединены с в° входом де1шфратора, первый и второй входы первого элемента И соединены соответственно с пятьм и четвертым входами дешифратора, первый и второй входы второго элемента И соединены соответственно с третьим и вторым входами дешифратора, первый и второй входы третьего элемента И соединены

914641

соответственно с первым и седьмым входами дешифратора, выход блока формирования короткого импульса по фронту входного сигнала соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом интегрируклдей цепочки, вход которой соединен с источником напряжения, выход четвертого элемента И со- IQ единен с входом установки триггера.

1110

информационный вход которого соединен с шестым входом дешифратора, тактовый вход триггера соединен с выходом блока .формирования короткого импульса по срезу входного сигнала, прямой выход триггера соединен с четвертым выходом дешифратора, выходы первого, второго, третьего элементов И соединены соответственно с третьим, вто рым, первым выходами дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор спектрометрических импульсов | 1986 |

|

SU1325671A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для тренировки памяти обучаемого | 1988 |

|

SU1520574A1 |

Изобретение может быть использовано в цифровых вольтметрах. УстX е ройство автоматического выбора диапазона измерений имеет аналого-цифровой преобразователь 1, элемент И 2, элементы ИЛИ 3,14, дешифратор 4, блок 5 масштабирования, генератор 6 тактовых импульсов, блок 7 индикации, регистр 8, элементы 10,11 задержки, триггер 15, логический блок 16, эле- мент НЕ, блок памяти. Б описании изобретения приведена электрическая схема дешифратора. Оптимальный диапазон измерения устанавливается по окончании первого цикла измерения, чем обеспечивается высокое быстродействие устройства. 1 з.п. ф-лы,, 5 ил. 7 (Л С Фп.

Шиг.2

30 I

Фаг.

Jr

I I

L

i

A

6f.6 et.Sex.tf

Лых.

еш.з лмл/у (Outf

J

Фиг.

&Г.ЗЯЛ2

gjr.7

vetut

| Устройство для автоматического выбора диапазона измерения переменного напряжения | 1982 |

|

SU1132235A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для автоматического выбора предела измерения | 1983 |

|

SU1112292A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-03-07—Публикация

1986-11-10—Подача