1

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть: использовано в блоках памяти информационно-вычислительных и информационно-измерительных систем. .

Целью изобретения является упро- .Щение устройства.

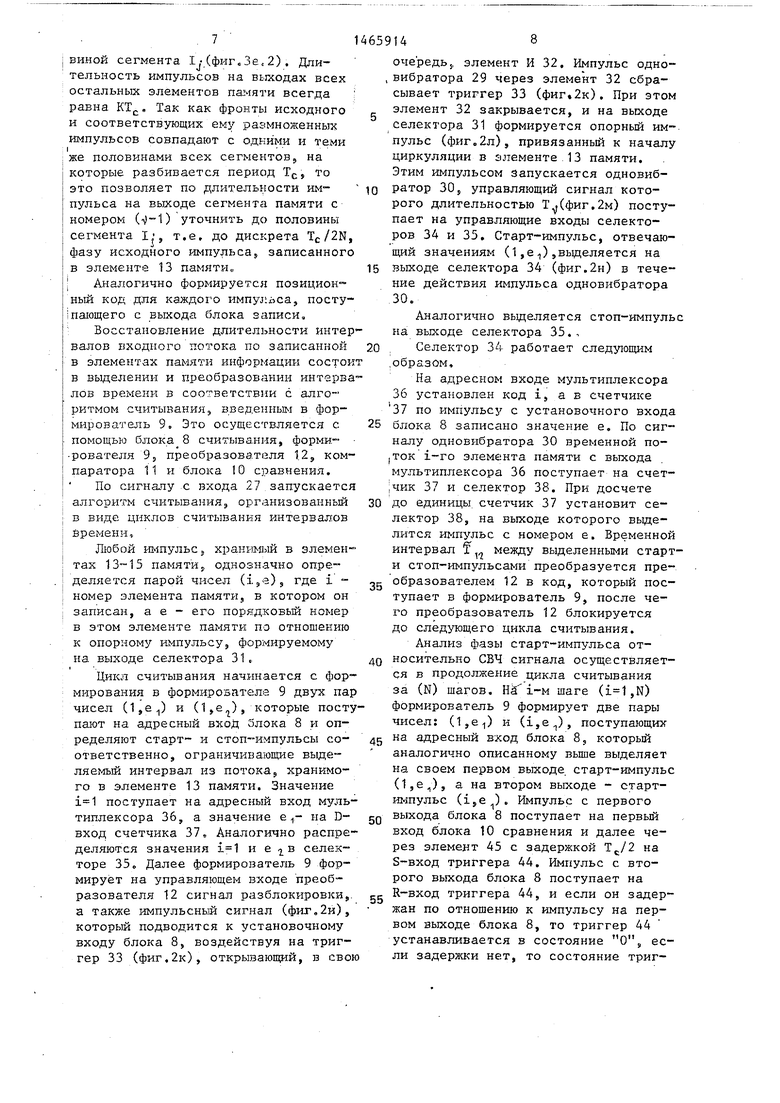

На фиг,1 приведена Функциональная схема предложенного устройства; на фиг.2,3 - временные диаграммы.

Устройство содержит блок 1 запи- си, входы которого соединены с информационным входом 2, входом 3 записи и входом 4 стирания устройства, линию 5 задержки, источник 6 СВЧ колебаний, распределитель 7 мощности, блок 8 считывания, формирователь 9

управляющих сигналов, блок 10 сравнения, компаратор И, преобразователь 12 время-код, элементы 13-15 памяти, каадьй из которых содержит элемент ИЛИ 16, формирователи 17 и 18 импульсов, пороговые элементы 19 и 20, каждый из которых состоит из резистора 21 и диода 22, триггер 23 (Элементы 24 задержки, усилитель 25 ;И источник 26 ОПОРНОГО напряжения; ;один из управляющих входов формиро- .вателя 9 является входом 27 считывания устройства. Блок 8 считывания содержит элемент И 28, одновиб- раторы 29 и 30, селектор 31, выполненный на элементе И 32 и триггере 33, селекторы 34 и 35, каждый из которых выполнен на мультиплексоре 36,

О) ел

QD

3

счетчике 37 и селекторе .38 выполненном аналогично селектору 31, Ело 1 записи содержит формирователь 39 импульсов и одновибратсры 40 и 41, Компаратор 11 выполнен на триггере 42 и элементе 43 задер кки. Аналогично ему выполнен и блок 10 сравнения на триггере 44 и элементе 45 задержки.

Устройство работает следующим образом,

В исходное состояние оно приводися по сигналу с входа 4, которым запускается одновибратор 41. Сфор- мированньй одновибратором 41 импуль с длительностью, превышающей период TO циркуляции элементов 13-15, запирает формирователи 17 и 18, что блокирует контур циркуляции., состоящий из элемента ШШ 16,, формирователей 17 и 18, элементов 19 и 20 триггера 23s, элемента 24 задержки-и усилителя 25. На выходах элементов 13-15 устанавливается логический В отсутствие импульсов на выходе элемента 13 одноЬибратор 29 находится в устойчивом состоянии с логическим .уровнем 1 на выходе. На выходе одновибратора 30 установлен логический О , что блокирует информационные входы селекторов 34 и 35. В исходном состоянии входной поток, поступающий с входа 2 в блок 1 заблокирован формирователем 39, На вторые входы элементов 19 и 20 поступает напряжение с источника 26, которое устанавливает порог сраба.тывания. С выходов распределителя 7 на входы элементов 13-15 синфазно поступает СВЧ сигнал с периодом , который модулирует уровни выставленных .порогов элементов 19 и 20.

. Запись в элементы.13-15 потока импульсов с входа 2 (фиг,2а) осуществляется по сигналу,, который подается на вход 3 (фиг,26) и запускает одновибратор 40, выходной сигнал которого (фиг.2в) отрывает на время t,, T(j- Т,- формирователь 39„ В результате на выходе блока 1 появляется сформированный формирователем 39 информационный поток стандартных импульсов (фигЛг) длительности

t, (K-i-1/2N)-T,(1)

где N - количество элементов памяти (для устройства на фиг.1 );.

659144

К - наименьшее из чисел 1,2..., обеспечиваемое быстродействием формирователя 39. Эти импульсы поступают на вход секционированной линии 5 задержки, которая состоит из (N-1) одинаковых элементов с задержкой на каждом Элементе TJ./N, и на первый вход элемен- 10 1 а 13,откуда через элемент ИЛИ 16

записываются в контур циркуляции элемента 13. Аналогично происходит запись задержанных импульсных последовательностей в контуры циркуляции 15 элементов 14 и 15. Первый записанный импульс с выхода элемента 13 (фиг.2ж) через открытый элемент И 28 запускает одновибратор 29 (фиг.2з), -который закрывает элемент И 28 до воз- Q вращения на выход элемента 13 первого записанного импульса, который вновь запускает одновибратор 29, и процесс повторяется (фиг.2з).

Хранение потока импульсов в эле- 5 менте 13 осуществляется в результате непрерывного обращения в контуре циркуляции с периодом , где п - кратность синхронизации элемента 13. В стационарном режиме хране- 0 ния длительность (tn)эп импульсов в потоке равна целому числу периодов Tf Это достигается тем, что поток импульсов, регенерируемых в результате циркуляции на втором входе эле- мента ИЛИ 16, разделяется на два потока, первый из которых формируется ,на выходе формирователя 17 (фиг.2д) и импульсы в котором сфазированы с фронтами импульсов, поступающих на элемент ИЛИ 16, а второй формируется на выходе формирователя 18 (фиг.2е), импульсы в нем сфазированы с их спа- дами. Эти .потоки поступают на элементы 19 и 20 соответственно, где осуществляетсч синхронизация перепадов каждого импульса потока с фиксированной в пределах периода Т фазой СВЧ сигнала (фазой синхронизации). Объединение двух потоков осуществляется триггером 23, фронты и спады импульсов на выходе которого иници- . ируются импульсами с выходов пороговых элементов 19 и 20 соответственно. Вследствие того, что фазы этих импульсов связаны с соответствующими синхронизации, длительность импульсов на выходе триггера 123 совпадает с целым числом перио- СВЧ сигнала. Целому числу

5

0

5

0

периодов TC равны и интервалы между импульсами. Поток импульсов с выхода триггера 23 (фиг.2ж) поступает на второй вход элемента ИЛИ 16, и процесс циркуляции повторяется. Происходит хранение потока, записанного в элемент 13 с выхода блока 1 ;записи. Так как каждый из импульсов в элементе 13 сфазирован с синхро-. низирующим сигналом, то это ведет- к искажению на выходе элемента 13 длительностей временных интервалов, соответствующих сформированным блоком 1. Для повьшения точности устройства на этапе записи формируется, а затем хранится в элементах памяти 13-15 позиционный код, который содержит информацию о фазе СВЧ сигнала, отвечающий моменту поступления на выход блока 1 каждого импульса в потоке. Это позволяет при считывании уточнить фазу прихода каждого импульса в пределах периода Т. СВЧ сигнала и провести коррекцию длительности интервалов, считываемых с выхода элемента 13.

Режим формирования устройства позиционного кода.

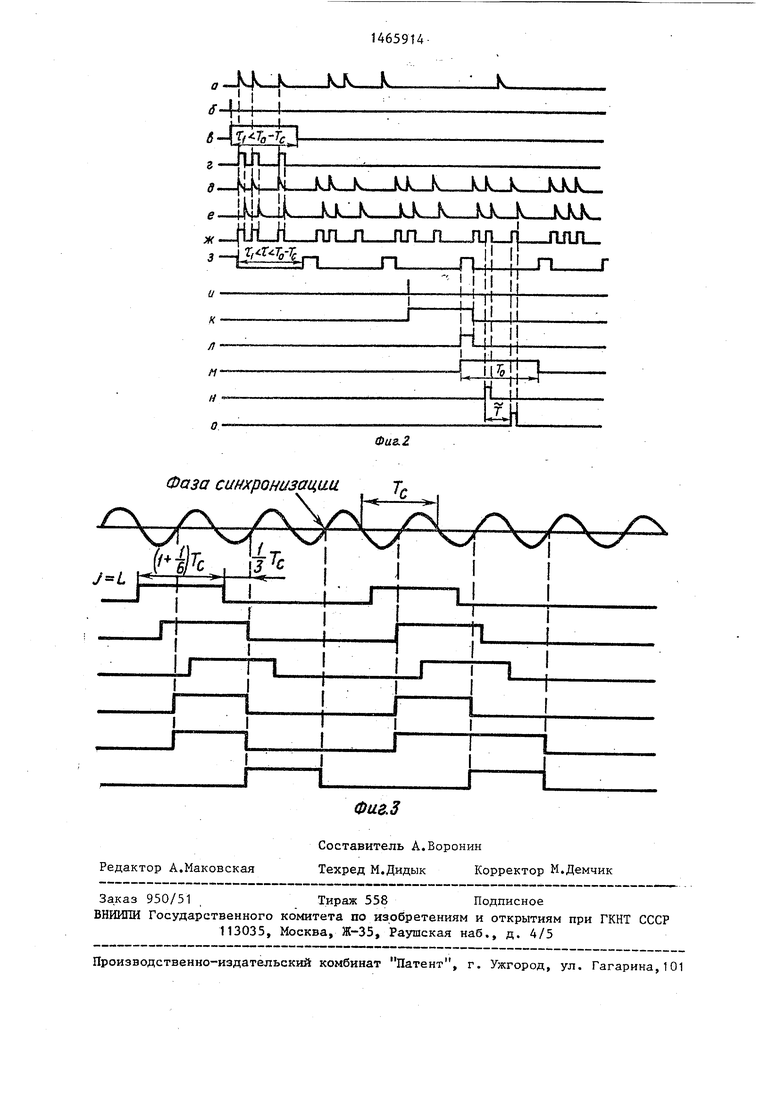

Без ограничения общности под периодом Т с можно понимать временной интервал между ближайшими точками перехода СВЧ синусоиды через нуль (фиг.2а), в которых ее первые производные положительны. Записываемый импульс потока поступает на вход элемента 13 (фиг.2б) и далее последовательно через время T /N/Ha входы элементов 14 (фиг.2в) и 15 (фиг.2г) (для. устройства на фиг.1 .). Если фронт импульса на входе элемента 1-3 совпадает во времени с сегментом I некоторого периода Т, СВЧ сигнала, где

J

Г

Г-J-----Т -1-.Т 1 1 1 м L N N -

(2)

то с этим периодом совпадают фронты импульсов, поступающих на элементы памяти с номерами ,N+1-j и получаемых в результате размножения записываемого импульса линией 9 задержки (отсчет номеров элементов памяти следует начинать с элемента, подключенного к первому выходу секционированной линии 9 задержки). Импульсы на входах элементов памяти с номерами i N+2-j,N совмещаются уже со следующим периодом СВЧ сигнала (фиг.2г). Происходит запись каждого из импульсов в соответствующий элемент памяти.

Вследствие синхронизации на первых пороговых элементах 19 фронты импульсов в элементах памяти с номе

рами 1, N+1-j оказываются жестко сфазированными с фазой синхронизации одного и того же периода СВЧ сигнала (фиг.2д,е) и в режиме хранения син- фазно повторяются на выходах этих элементов памяти. Синфазно, но со сдвигом на период Т. повторяются фронты импульсов на выходах элементов

памяти с номерами N+2-j, N (фиг.2ж). Если импульсы на выходах этих элементов с номерами от 1 до N синфаз- ны, то считаем, что сдвиг пpoиcxoJ ит на выходе фиктивного (N+1)-ro элемента памяти. Номер V N+2-j элемен- та, на котором происходит описанный сдвиг, может chyжить кодом для номе- ра j сегмента 1.. Связь ) и j дается формулой

30

j N+2- J, )2, N+1,

(3)

35

40

45

50

55

что позволяет по номеру ) уточнить в пределах периода Тс до дискрета T5./N фазу исходного импульса, поступившего на вход элемента 13.

Дополнительное уточнение фазы записанного импульса с точностью до дискрета Tc./2N достигается за счет анализа длительности t , импульса на выходе (л1-1)-го элемента памяти. Так как фронт импульса, поступившего на элемент памяти с номером (-0-1), всегда совмещен с первой или второй половиной сегмента I., то его спад согласно (1) и (2) совпадает соответственно с последующим К-м или (К+1)-м периодом СВЧ сигнала. Следовательно, в режиме хранения спад импульса, циркулирующего в (J-O-M элементе памяти, будет связан с фазой синхронизации К-го или (К+1)-го периода СВЧ сигнала (синхронизация спада импульса с фазой СВЧ сигнала осуществляется на втором пороговом элементе. (V-1)-го элемента памяти. В результате ., когда фронт совмещен с первой половиной сегмента I. (фиг.Зе.1), и 1)., (К+1)Тс, когда фронт совмещен со второй половиной сегмента I

J7 (фиг

Зе.2). Длительность импульсов на вькодах всех остальных элементов памяти всегда равна KTj,, Так как фронты исходного и соответствующих ему размноженных

импульсов совпадают с едкими и теми I....

же половинами всех сегментов, на которые разбивается период , то это позволяет по длительности им- пульса на выходе сегмента памяти с номером () уточнить до половины сегмента 1;, т.е. до дискрета Tc/2N, фазу исходного импульса, записанного в элементе 13 памяти,,

: Аналогично формируется позиционный код для каждого импульса, посту- 1пшощего с выхода блока записи, ; Восстановление длительности интервалов входного потока по записанной в элементах памяти информации состои в выделении и преобразовании интервалов времени в соответствии с алгоритмом считывания, введенным в формирователь 9. Это осуществляется с помощью блока 8 считывания, форми- рователя 9, преобразователя 12, компаратора 11 и блока 10 сравнения.

По сигналу с входа 27 запускается алгоритм считывания, организованный в виде циклов считывания интервалов Времени,

Любой импульс, храни ый в элементах 13-15 памяти,, однозначно опрв деляется парой чисел (), где i - номер элемента памяти, в котором он записан, а е - его порядковый номер в этом элементе памяти по отношению к опорному импульсу, формируемому на выходе селектора 31.

Цикл считывания начинается с формирования в формирователе 9 двух пар чисел (1,е) и (1 ,е), которые поступают на адресный вход блока 8 и определяют старт- и стоп-импульсы соответственно, ограничива:ющие выделяемый интервал, из потока, хранимого в элементе 13 памяти. Значение поступает на адресный вход мультиплексора 36, а значение е:,- на D- вход счетчика 37„ Аналогично распределяются значения и е в селекторе 35. Далее формирователь 9 формирует на управляющем входе преобразователя 12 сигнал разблокировки,, а также импульсный сигнал (фиг.2и), который подводится к установочному входу блока 8, воздействуя на триггер 33 (фиг.2к), открывающий, в сво

1465914

0 5

0

очередьS, элемент И 32. Импульс одно- ,вибратора 29 через элемент 32 сбрасывает триггер 33 (фиг.2к). При этом элемент 32 закрывается, и на выходе селектора 31 формируется опорный импульс (фиго2л), привязанный к началу циркуляции в элементе.13 памяти. Этим импульсом запускается одновиб- ратор 30, управляющий сигнал которого длительностью Т(фиг.2м) поступает на управляющие входы селекторов 34 и 35, Старт-импульс, отвечающий значениям (1,еi),выделяется на выходе селектора 34 (фиг.2н) в течение действия импульса одновибратора .30.

Аналогично выделяется стоп-импульс на выходе селектора 35.,

Селектор 34 работает следующим ,образом.

На адресном входе мультиплексора 36 установлен код 1, а в счетчике 37 по импульсу с установочного входа блока 8 записано значение е. По сигналу одновибратора 30 временной по- |Ток 1-го элемента памяти с выхода мультиплексора 36 поступает на счет- |чик 37 и селектор 38. При досчете до единицы, счетчик 37 установит селектор 38, на выходе которого выделится импульс с номером е. Временной между выделенными старт5

0

5

0

интервал

п

и стоп-импульсами преобразуется преобразователем 12 в код, который поступает в формирователь 9, после чего преобразователь 12 блокируется до следующего цикла считывания.

Анализ фазы старт-импульса относительно СВЧ сигнала осуществляется в продолжение цикла считывания за (N) шагов. шаге (,N) формирователь 9 формирует две пары чисел; (1je-|) и (1,е), поступающих на адресный вход блока 8, который аналогично описанному выше вьщеляет на своем первом выходе старт-импульс (1,е), а на втором выходе - старт- ш-шульс (ije). Импульс с первого выхода блока 8 поступает на первьй вход блока 10 сравнения и далее через элемент 45 с задержкой на S-вход триггера 44. Импульс с второго выхода блока 8 поступает на е R-вход триггера 44, и если он задержан по отношению к импульсу на первом выходе блока 8, то триггер 44 устанавливается в состояние О, если задеряжи нет, то состояние триггера - 1. Импульс с второго выхо- . да блока 8 поступает также на R-вход и через элемент 43 с задержкой

(К+-Г-) TC на S-вход триггера 42.

При поступлении на вход компаратора 11 импульса с длительностью, меньшей

на его выходе установится

логический О, в противном случае 11 1

I , .

Состояния, триггеров 42 и 44 фиксируются на каждом шагев формирователе 9, По последовательности состояний триггера 44 формирователь 9 вьщеляет номер -О элемента памяти, на котором возникает первый сдвиг сравниваемых импульсов, что позволяет согласно (-2) и (3) уточнить фазу старт-импульса с точностью до дискрета TC/N. Дальнейшее уточнение фазы старт-импульса с точностью до дискрета Tc/2N происходит в результате анализа состояний триггера 42 для импульса на выходе (-O-D-ro элемента памяти.

Аналогично старт-импульсу осуществляется анализ фазы стоп-импуль са относительно СВЧ сигнала.

В результате одного цикла считывания в формирователе 9 фиксируется

а)измеренная преобразователем 12

л

длительность Т временного интервала равная целому числу периодов Тс

б)номера Д, и А дискретов Tc/2N,4 пронумерованных в пределах периода TC от 1 до 2N, с которыми совместились старт- и стоп-импульсы соответственно.

По формуле Т ( +

Л, ч То

2N

формирователь 9 восстанавливает требуемый интервал Т с точностью

± .

На этом один цикл считывания заканчивается, и формирователь 9 переходит к следующему циклу. Число . циклов считывания равно числу.записанных в элементе 13 интервалов времени. При попытке считать интервал времени, следующий за последним записанным в элементе 13, происходит переполнение преобразователя 12, с его выхода поступает сигнал пере

5

полнения, формирователь 9 фиксирует окончание всех циклов считывания.

На этом работа устройства заканчивается.

Техническая эффективность предлагаемого устройства определяется исключением половины элементов памяти и двукратным сокращением секционированной линии задержки, что обеспечивает уменьшение габаритов устройства, упрощение и большую технологичность при изготовлении.

Фор мула изобретения

Динамическое запоминающее устройство, содержащее источник СВЧ колебаний, выход которого соединен с информационным входом распределителя

0 мощности, блок записи, информационный вход, вход записи и вход стира- ния которого являются информационным входом, входом записи и входом стирания устройства соответственно, ли5 НИЛ задержки, вход которой соединен с первым выходом блока записи, блок считывания, первый выход которого соединен с первым входом блока сравнения и со стоп-входом преобразова0 теля время-код, формирователь управляющих сигналов, вход считывания которого является входом считывания устройства, компаратор, выход которого соединен с входом запрета фор5 мирователя управляющих сигналов, вход запуска которого соединен с выходом блока сравнения, второй вход блока сравнения соединен с, входом компаратора и с вторым выходом блока

0 считывания, адресные входы которого соединены с первым и вторым выходами формирователя управляющих сигналов, выход преобразователя время-код соединен с входом переполнения формиро5 вателя управляющих сигналов, выход которого соединен с входом блокировки преобразователя время-код, вход запуска преобразователя время-код соединен с вторым выходом блока счи0 тывания, первый, второй и третий элементы памяти, каждый из которых состоит из последовательно соединенных элементов задержки, усилителя, элемента ИЛИ, первого формирователя

55 импульсов, первого порогового элемента и источника опорного напряжения, причем в каждом элементе памяти вторые входы элементов ИЛИ соединены с выходами линий задерлски, заn

прещакнцие входы первых формирователей импульсов соединены с вторым вы ходом блока записи, синхронизирующие входы первых пороговых элементов соединены с первым, вторым и третьим выходами распределителя мощности, отличающееся тем, что, с целью упрощения устройства, в каждый элемент памяти введены второй формирователь импульсов, второй пороговый элемент и триггер, причем выходы триггеров соединены с входами элементов задержки и с информационными входами блока считывания, информационные входы вторых пороговых элементов соединены с четвертым, пятым и шестым выходами распределителя

6591А12

мощности соответственно, R-входы триггеров соединены с выходами вторых пороговых элементов, S-входы триггеров соединены с синхронизирующими входами первых пороговых элементов, входы опорных напряжений вторых пороговых элементов соединены с источниками опорного напряжения, входы управления Порогом срабатывания вторых пороговых элементов соединены : с выходами вторых формирователей импульсов, запрещающие входы вторых формирователей импульсов соединены с вторым выходом блока записи, информационные входы вторых формирователей импульсов соединены с выходами элементов ИЛИ.

10

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство | 1988 |

|

SU1596396A1 |

| Запоминающее устройство | 1988 |

|

SU1547032A1 |

| Аналого-динамическое запоминающее устройство | 1989 |

|

SU1674265A1 |

| Цифровой стробоскопический преобразователь повторяющихся электрических сигналов | 1986 |

|

SU1386913A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1305778A1 |

| Устройство дискретных задержек импульса | 1988 |

|

SU1587626A1 |

| Устройство дискретных задержек импульса | 1985 |

|

SU1330740A1 |

| Видеоконтроллер | 1990 |

|

SU1816326A3 |

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

| Автоматическое пороговое устройство | 1981 |

|

SU1012429A1 |

Изобретение относится к области вьгаислительной техники, а именно к запоминающим уст.ройствам, и может быть использовано в блоках памяти информационно-вычислительных и нн- формационно-измерительных систем. Цель изобретения - упрощение устройства - достигается введением в элементы памяти вторых формирователей импульсов, пороговых элементов и триггера. Запись импульсных потоков (Ш) осуществляется посредством блока записи и секционированной линии задержки. Хранение ИП происходит .на элементах памяти под воздействием синхронизирующих СВЧ колебаний снимаемых с СВЧ генератора через разветвитель мощности. При записи в элементы памяти фиксируется фаза фронта и спада импульсов, циркулирующих в контуре элемента памяти- элемент ИЛИ, формирователи, триггер элемент задержки, усилитель. 3 ил. S

К) k к. k k

Фаза синхронизации j

М)Гс , irc

| Малевич И.А | |||

| Методы и электрон- .ные системы анализа оптических процессов при их временном отображении Минск, БГУ, с.205-206 | |||

| Искусственный двухслойный мельничный жернов | 1921 |

|

SU217A1 |

Авторы

Даты

1989-03-15—Публикация

1987-06-08—Подача