Изобретение относится к импульсной технике и может быть использовано для запоминания случайных последовательностей импульсов и определения интервалов времени между ними при считывании.

Цель изобретения - упрощение устройства.

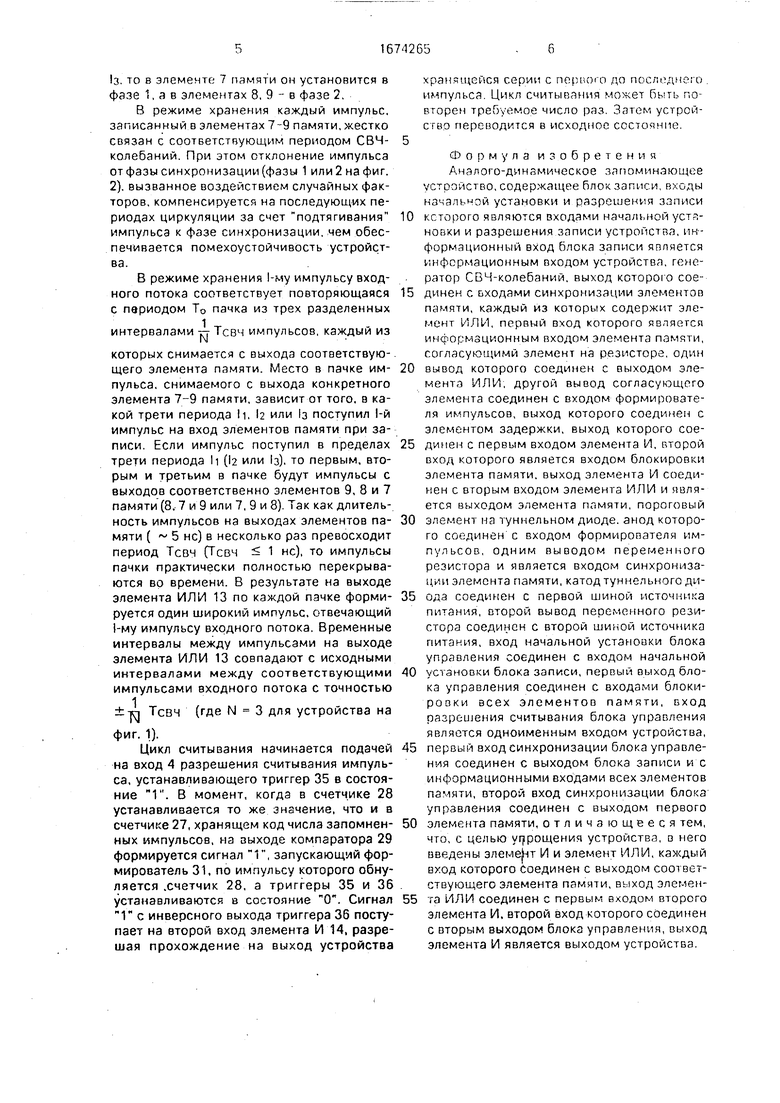

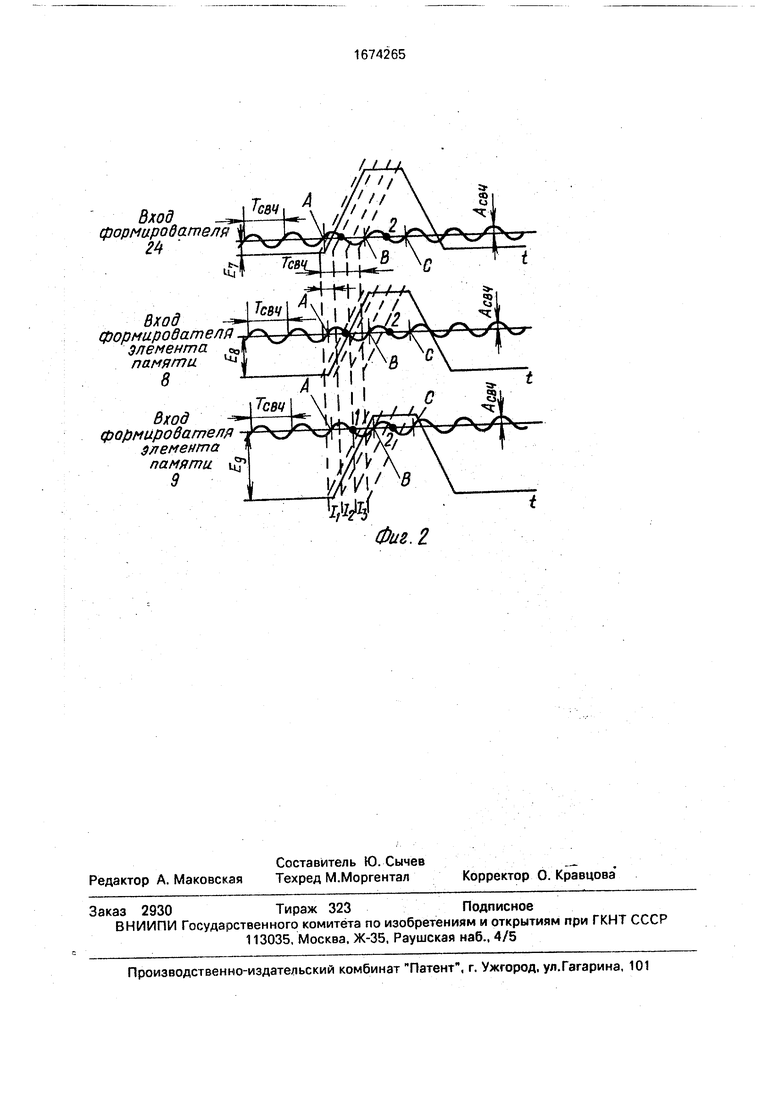

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма его работы.

Аналого-динэмическое запоминающее устройство содержит входы начальной установки 1, разрешения записи 2, информационный 3 и разрешения считывания 4, выход 5, блок 6 записи, элементы 7-9 памяти, генератор 10 СВЧ-колебаний, размножитель 11, блок 12 управления, элемент ИЛИ 13 и элемент И 14.

Блок 6 записи содержит элемент И 15, одновибратор 16, формирователь 17 импульсов, элемент ИЛИ 18 и RS-триггер 19.

Каждый из элементов 7-9 памяти содержит элемент ИЛИ 20, согласующий элемент на резисторе 21, пороговый элемент на туннельном диоде 22, подстроечный элемент на переменном резисторе 23, формирователь 24 импульсов, элемент 25 задержки и элемент И 26.

Блок 12 управления содержит счетчики 27, 28, цифровой компаратор 29. элемент 30 задержки, формирователь 31 импульса, элементы ИЛИ 32-33, RS-триггеры 34-36 и элементы И 37-39.

Устройство работает следующим образом.

Работа устройства начинается с приведением его в исходное состояние импульсом логической 1, поступающим на вход 1 начальной установки. По переднему фронту этого импульса происходит сброс в нулевое состояние триггера 19 в блоке 6 записи, а также триггеров 34-36 и счетчика 27 в блоке 12 управления. После появления импульса начальной установки на выходе элемента 30 задержки через время 1з, которое выбирается большим периода Т0 циркуляции импульсов в элементах 7-9 памяти, происходит сброс счетчика 28 в нулевое состояние и установка в 1 триггеров 34, 36. В результате сформированный на выходе триггера 34 импульс поступает с блока 12 управления на входы блокировки элементов 7-9 памяти, вызывая появление логического нуля на выходе элемента И 26 в каждом элементе памяти и срыв циркуляции в этих элементах записанных ранее импульсов.

Цикл записи потока импульсов в запоминающее устройство начинается с момента поступления на вход 2 разрешения записи короткого импульса, который устанавливает триггер 19 в состояние 1. После появления на информационном входе 3 первого из записываемых импульсов срабатывает одновибратор 16, который формирует

импульс длительностью, меньшей периода циркуляции Т0. по заднему фронту которого триггер 19 возвращается в нулевое состояние. За время нахождения триггера 19 в единичном состоянии импульсы, поступившие на вход 3. проходят через элемент И 15 и записываются в элементы 7-9 памяти, а их число запоминается на счетчике 27 в блоке 12 управления. Особенностью записи является то, что на синхронизирующие входы

элементов 7-9 памяти непрерывно подается синусоидальный СВЧ-сигнал высокой стабильности от генератора 10, который осуществляет модуляцию уровней порогов туннельных диодов 22 с периодом Тсвч и

амплитудой модуляции Асвч (фиг. 2). Исходные уровни порогов в элементах 7-9 памяти Е, ЕЗ и Eg устанавливаются с помощью переменных резисторов 23 так. чтобы в от сутствие СВЧ-модуляции при одновременном поступлении импульса на информационный вход элементов памяти момент переключения туннельного диода каждого последующего элемента памяти задерживался по отношению к предыдущему

на время Тсвч/N, где N - число элементов памяти (N 3, для устройства на фиг. 1). Периоды циркуляции импульсов в элементах 7-9 памяти выбираются равными и кратными периоду Тсвч:

Ту Те Тд Т0 п-Тсвч.

где п - целое число в диапазоне 10 -103. Компенсация различия задержек при срабатывании туннельных диодов достигается подстройкой длительности задержки в элементах 25 задержки в каждом из элементов 7-9 памяти. В результате взаимодействия циркулирующего в замкнутом контуре элемента памяти импульса с порогом туннельного диода, промодулированным

СВЧ-сигналом, происходит подтягивание импульса к одной из двух устойчивых фаз СВЧ-сигнала. На фиг. 2 это фазы 1 и 2. с которыми совмещается 1-й импульс входного потока, если он поступил на информационный вход элемента памяти в пределах периода АВ синхронизирующего сигнала. Если входной импульс во всех трех элементах памяти поступил в пределах трети (фиг. 2) периода И, то он установится в фазе 1 в

каждом из трех элементов 7-9 памяти, если в пределах трети периода 2. то в элементах 7, 8 памяти - в фазе 1, а в элементе 9 памяти - в фазе 2. И, наконец, если 1-й импульс поступил в пределах трети периода

l;i то в элемент 7 тымяти он установите н фале 1, я в элементах 8. 9 в фазе 2.

В режиме хранения каждый импульс, записанный в элементах 7 9 памяти,жестко связан с соответствующим периодом СВЧ- колебаний. При этом отклонение импульса от фазы синхронизации {фазы 1 или 2 на Фиг. 2), вызванное воздействием случайных факторов, компенсируется на последующи ; периодах циркуляции за смет подтягивания импульса к фазе синхронизации, чем обеспечивается помехоустойчивость устройства.

В режиме хранений l-му импульсу входного потока соответствует повторяющаяся с периодом Т0 пачка из трех разделенных

1 т

интервалами ут Тгич импульсов, каждый из N

которых снимается с выхода соответствующего элемента памяти. Место в пачке импульса, снимаемого с выхода конкретного элемента 7 9 памяти, зависит or того, п какой трети периода h, h или з поступил 1-й импульс на вход элементов памяти при записи. Если импульс поступил в пределах трети периода И (12 или 1з), то первым, вторым и третьим в пачке будут импульсы с выходов соответственно элементов 9, 8 и 7 памяти (8, 7 и 9 или 7, 9 и 8). Так как длительность импульсов на выходах элементов памяти ( 5 не) в несколько раз превосходит период Тсвч (Тсвч 1 не), то импульсы пачки практически полностью перекрываются во времени. В результате на выходе элемента ИЛИ 13 по каждой пччке формируется один широкий импульс, c-твечающий 1-му импульсу входного потока. Временные интервалы между импульсами на выходе элемента ИЛИ 13 совпадают с исходными интервалами между соответствующими импульсами входного потока с точностью

± тп Тсвч (где N 3 для устройства на

фиг. 1).

Цикл считывания начинается подачей на вход 4 разрешения считывания импульса, устанавливающего триггер 35 в состояние 1. В момент, когда в счетчике 28 устанавливается то же значение, что и в счетчике 27, хранящем код числа запомненных импульсов, на выходе компаратора 29 формируется сигнал 1 запускающий формирователь 31, по импульсу которого обнуляется .счетчик 28, а триггеры 35 и 36 устанавливаются в состояние О Сигнал 1 с инверсного выхода триггера 36 поступает на второй вход элемента И 14, разрешая прохождение на выход устройства

храчя цспся серии с леркою до гкч лгД К импульса Цикп считывания (чып. по торен треП/емое число раз Затем устройство переводится в исходите сгсточчцр

Формул а и о б р е 1 с и и я Л на лен о-динпмическое запоминающее V-ТГОИСТРО, содержаще блок, записи, fv-оды HavMt.MCHi установки и разрешения записи

которого шзлчются входами начат ной установки и разрешения записи устройства, информационный вход блока записи япляется информационным входом устройства, генератор СВЧ-колебании. ньпод которою сое

динен с входами синхронизации элементов памяти, каждый из которых содержит элемент ИЛИ, перпый вход которого является информационным входом элемента помят, согласующими элемент на резисторе, один

вывод которого соединен с выходом элемента ИЛИ. другой выоод согласующего элемента соединен с входом формирователя импульсов, выход которого соединен с элементом задержки, выход которого соедипен с перрым входом элемента И, второй вход которого является входом блокировки элемента памяти, выход элемента И соединен с вторым входом элемента ИЛИ и чвля- ется выходом элемента памяти, пороговый

элемент на туннельном диоде, анод которого соединен с входом фопмпропгпеля импульсов, одним выводом переменього резистора и является входом синхронизации элемента памяти, катод туннельного диод-ч соединен с первой шиной источника питания, второй вывод переменного резистора соединен с второй шиной источника питания, вход начальной установки блока управления соединен с входом начальной

установки блока записи, перпый выход блока управления соединен с входами блокировки всех э л е м е н т о в памяти, в х о д разрешения считывания блока управление является одноименным входом устройства,

первый вход синхронизации блока управления соединен с выходом Опока записи и с информационными входами всех элементов памяти, второй вход синхронизации блока управления соединен с выходом первого

элемента памяти, отличающееся тем, чго, с целью упрощения устройства, о пето введены элемент И и элемент ИЛИ, каждый вход которого Соединен с выходом соответствующего элемента ппмччи, в; ход элсменга ИЛИ соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом блока управления, иыход элемента И является выходом устройства.

it it //

il

I 1 f

x/

ww NS w/

Фиг. 2

it it //

il

о ЧУТ4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1988 |

|

SU1547032A1 |

| Динамическое запоминающее устройство | 1988 |

|

SU1596396A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1465914A1 |

| Устройство дискретных задержек импульса | 1988 |

|

SU1587626A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Устройство дискретных задержек импульса | 1985 |

|

SU1330740A1 |

| Динамическое запоминающее устройство | 1976 |

|

SU714501A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300544A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Энергонезависимое оперативное запоминающее устройство | 1981 |

|

SU978193A1 |

Изобретение относится к импульсной технике и может быть использовано для запоминания случайных последовательностей импульсов и определения интервалов времени между ними при считывании. Цель изобретения - упрощение устройства. Аналого-динамическое запоминающее устройство содержит входы 1 начальной установки, разрешения записи 2, информационный 3 и разрешения считывания 4, выход 5, блок записи 6, элементы памяти 7 - 9, генератор СВЧ - колебаний 10, размножитель 11, блок 12 управления, элемент ИЛИ 13, элементы И 14 и 15, одновибратор 16, формирователь импульсов 17, элемент ИЛИ 18, триггер 19, элемент ИЛИ 20, согласующий элемент на резисторе 21, пороговый элемент на туннельном диоде 22, подстроечный элемент на переменном резисторе 23, формирователь импульсов 24, элемент задержки 25 и элемент И 26, счетчики 27, 28, компаратор 29, элемент задержки 30, формирователь импульса 31, элементы ИЛИ 32, 33, триггеры 34 - 36 и элементы И 37 - 39 с соответствующими связями. 2 ил.

| Динамическое запоминающее устройство | 1977 |

|

SU708420A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-08-30—Публикация

1989-02-20—Подача