Изобретение относится к импульсной технике и может быть использовано для запоминания случайных последовательностей импульсов и определения интервалов времени между импульсами в запомненной серии импульсов при считывании.

Цель изобретения - упрощение запоминающего устройства.

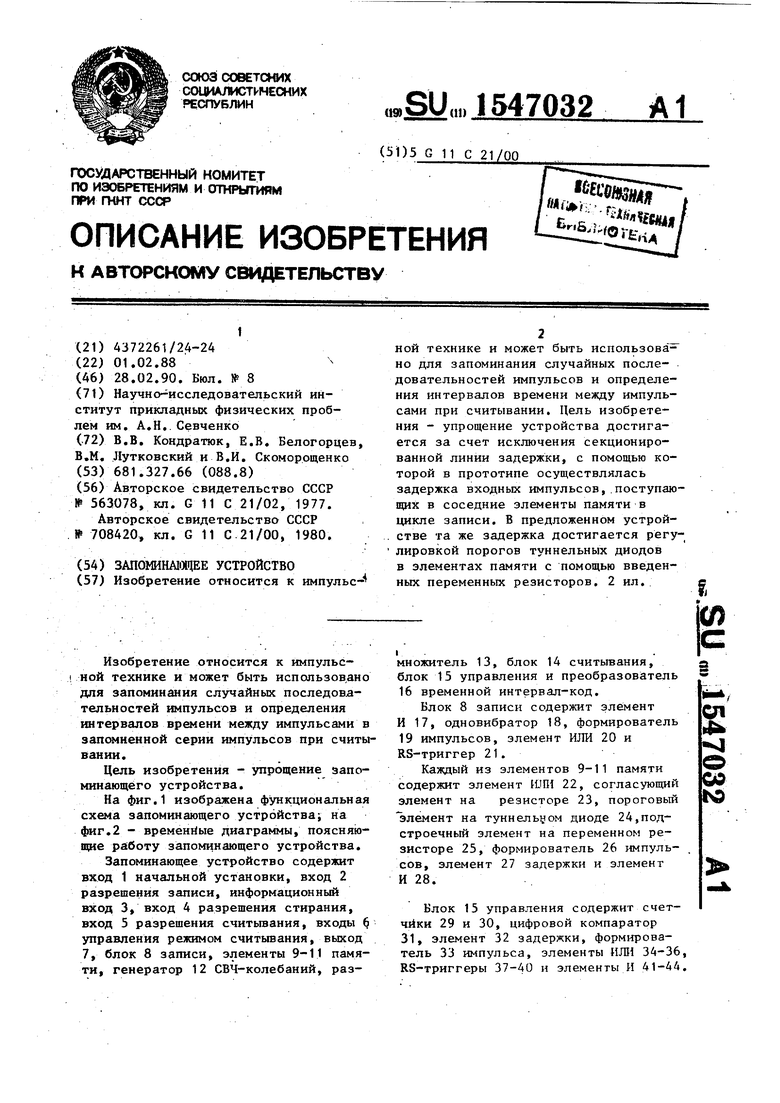

На фиг.1 изображена функциональная схема запоминающего устройства; на фиг.2 - временные диаграммы, поясняющие работу запоминающего устройства.

Запоминающее устройство содержит вход 1 начальной установки, вход 2 разрешения записи, информационный вход 3, вход 4 разрешения стирания, вход 5 разрешения считывания, входы (j управления режимом считывания, выход 7, блок 8 записи, элементы 9-11 памяти, генератор 12 СВЧ-колебаний, размножитель 13, блок 14 считывания,

блок 15 управления и преобразователь

16 временной интервал-код.

Блок 8 записи содержит элемент

И 17, одновибратор 18, формирователь 19 импульсов, элемент ИЛИ 20 и

RS-триггер 21.

Каждый из элементов 9-11 памяти

содержит элемент ИЛИ 22, согласующий элемент на резисторе 23, пороговый

элемент на туннельном диоде 24,под- строечный элемент на переменном резисторе 25, формирователь 26 импуль- . сов, элемент 27 задержки и элемент И 28.

Блок 15 управления содержит счетчики 29 и 30, цифровой компаратор 31, элемент 32 задержки, формирователь 33 импульса, элементы ИЛИ 34-36, RS-триггеры 37-40 и элементы И 41-44.

Клок 14 считывания содержит рас™ прсделитель 45 импульсов, мультиплексоры 46 и 47 и элементы II 48-50.

Устройство работает следующим об- разом.

Работа запоминающего устройства Начинается с приведения его в исходное состояние импульсом ло ической 1, поступающим на вход 1 начальной установки. По переднему фронту этого Импульса происходит сброс в нулевое состояние RS-триггера 21 в блоке 8 записи,, а также RS-триггеров 37-40 И счетчика 29 в блоке 15 управления. 11осле появления импульса начальной Установки на выходе элемента 32 задержки через время t3, которое выбирается большим периода Т0 циркуляции импульсов в элементах 9-11 памяти, происходит сброс счетчика 30 в нулевое состояние и установка в 1 RS-триггеров 38 и 40. В результате сформированный на выходе RS-триггера 38 импульс длительностью ty поступает из блока 15 управления на входы блокировки элементов 9-11 памяти, вызывая появление логического нуля на выходе элементов И 28 в каждом элементе памяти и срыв циркуляции в этих элементах записанных ранее импульсов.

Цикл записи потока импульсов в запоминающее устройство начинается с момента поступления на вход 2 разрешения записи короткого импульса, который устанавливает RS-триггер 21 в блоке 8 записи в состояние логической 1.

После появления на информационном входе 3 первого из записываемых импульсов срабатывает одновибратор 18, который формирует импульс длительностью, меньшей периода циркуляции Т0, по заднему фронту которого RS-триггер 21 возвращается в нулевое состояние. За время нахождения RS-триггера 21 в единичном состоянии импульсы, поступившие на информационный вход 3 устройства, проходят через элемент И 17 и записываются в элементы 9-11 памяти, а их число запоминается в счетчике 29 блока 15 управления. Особенностью записи является то, что на синхронизирующие входы элементов 9-11 памяти непрерывно подается синусоидальный СВЧ-сигнал вы сокой стабильности от генератора 12, который осуществляет модуляцию уровней порогов туннельных диодов 24 с

периодом Тсвч и амплитудой модуляции АС8Ч (фиг. 2). Исходные уровни порогов в элементах 9-11 памяти, равные Кэ, Г f(J и ЕЧ1 , устанавливаются с помощью переменных резисторов 25 так, чтобы в отсутствии СВЧ-модуля- ции при одновременном поступлении импульса на информационный вход эле-- ментов памяти момент переключения туннельного диода каждого последующего элемента памяти задерживался по отношению к предыдущему на время свч/, где N - число элементов памяти ( для запоминающего устройства, изображенного на фиг.1).Причем периоды циркуляции импульсов в элементах 9-11 памяти выбираются равными и кратными периоду СВЧ-колебания:

т

L 10

Т.

п-Т

сеч

где п - целое число в диапазоне Ю2 - 103 .

Компенсация различия задержек при срабатывании туннельных диодов достигается подстройкой длительности задержки в элементах 27 задержки в каждом из элементов памяти. При этом (так же как и в прототипе) в результате воздействия циркулирующего в замкнутом контуре элемента памяти импульса с промоделированным СВЧ-сигна- лом порогом туннельного диода происходит подтягивание импульса к одной из двух устойчивых точек. На фиг.2 это точки 1 или 2, в которые попадает 1-й импульс входного потока, если он поступил на информационный вход элемента памяти в пределах периода А-В синхронизации. Так, если входной импульс поступил в пре- f делах трети периода I,, то 1-й импульс во всех трех элементах памяти установится в точке 2, если в пределах трети периода 1 - то в точке 1 в элементах 9 и 10 памяти и в точке 2 элементе 11 памяти. И, наконец, если 1-й импульс поступил в пределах трети периода 1, то в элементе 9 памяти он установится в точке 1, а элементах 10 и 11 памяти - точке 2.

В режиме хранения записанная в элементах 9-11 памяти последовательность импульсов циркулирует так, что каждый импульс жестко связан с соответствующим периодом СВЧ-колебаний, При этом отклонение циркулирующего импульса от фазы синхронизации, вызванное воздействием случайных фак- торов, компенсируется на последующих периодах циркуляции за счет подтягивания импульса к фазе синхронизации,

чем обеспечивается помехоустойчивость устройства.

В режиме считывания определяются интервалы времени между импульсами, циркулирующими в элементах 9-11 памяти. По отличию измеряемого интервала в двух соседних элементах памяти на один такт синхронизации (или его отсутствию) определяется длительностью интервала с точностью до 1/N периода Т0 СВЧ-сигнала. Определение интервалов времени производится последовательно для серий импульсов, записанных в первый, второй

циклы считывания повторяются для следующих интервалов времени между импульсами записанной серии импульсол. Отличием предлагаемого запоминающего устройства от устройства-прототипа является исключение секционированной линии задержки, с помощью которой в прототипе осуществлялся

сдвиг на время T0/N для входных импульсов, поступающих в соседние элементы 9-11 памяти в цикле записи. В предлагаемом запоминающем устройстве тот же самый сдвиг задается регулировкой порогов туннельных диодов 24 с помощью переменных резисторов 25. Вместе с исключением громоздкой линии задержки, выполняемой из коаксиального кабеля, уменьшаются и искаже

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-динамическое запоминающее устройство | 1989 |

|

SU1674265A1 |

| Динамическое запоминающее устройство | 1988 |

|

SU1596396A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1465914A1 |

| Энергонезависимое оперативное запоминающее устройство | 1981 |

|

SU978193A1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| СЕЛЕКТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 1993 |

|

RU2072627C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Динамическое запоминающее устройство | 1976 |

|

SU714501A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство дискретных задержек импульса | 1988 |

|

SU1587626A1 |

Изобретение относится к импульсной технике и может быть использовано для запоминания случайных последовательностей импульсов и определения интервалов времени между импульсами при считывании. Цель изобретения - упрощение устройства - достигается за счет исключения секционированной линии задержки, с помощью которой в прототипе осуществлялась задержка входных импульсов, поступающих в соседние элементы памяти в цикле записи. В предложенном устройстве транзистора же задержка достигается регулировкой порогов туннельных диодов в элементах памяти с помощью введенных переменных резисторов. 1 ил.

и т.д. элементы памяти. Номер элемен- 20 ния импульсов входного потока в этой

та памяти задается подачей высокого уровня на соответствующий вход элемента И 48-50 в блоке 14 считывания. Номер 1-го интервала между 1-ым и (1+1)-ым импульсами задается подачей двоичного представления чисел 1 и 1+1 на адресные входы мультиплексоров 46 и 47. Перед каждым циклом считывания временного интервала производится установка распределителя 45 импульсов в исходное состояние подачей на R-вход импульса с входа 6. Цикл считывания начинается подачей на вход 5 разрешения считывания импульса, устанавливающего RS-триггер

39 в блоке 15 управления в состояние Hi п

после чего в момент прохожде40

45

ния последующего импульса записанной серии в счетчике 30 устанавливается то же самое значение, что и в счетчике 29, хранящем код числа импульсов в серии, что приводит к появлению логической 1 на выходе компаратора 31 кодов, запускающего формирователь 33 импульса. По этому импульсу счетчик 30 обнуляется, а RS-триггеры 40 и 39 устанавливаются в состояние О. Нулевой сигнал с RS-триггера 40 поступает в блок 14 считывания, разрешая прохождение с первого до послед-сл него импульса серии через один из элементов И 48-50 на вход распределителя 45 импульсов, причем первый импульс серии проходит на первый выход распределителя 45 импульсов, второй импульс - на второй выход и т.д. Преобразователь 16 временной интервал - код замеряет время между и (1-М)-ьм импульсами. Далее

55

5

0

5

0

5

л

5

линии задержки, свойственные устройству-прототипу.

Формула изобретения

Запоминающее устройство, содержащее блок записи, входы начальной установки и разрешения записи которого являются соответственно входами начальной установки и разрешения записи устройства, информационный вход блока записи является информационным входом устройства, генератор СВЧ-ко- лебаний, выход которого соединен с входом размножителя, выходы которого соединены с входами синхронизации элементов памяти, первый выходы которых подключены к соответствующим входам блока считывания, выходы которого соединены с соответствующими входами преобразователя временной интервал - код, выход которого является выходом устройства, входы задания режима блока считывания являются входами управления режимом считывания устройства, вход разрешения считывания блока считывания подключен к первому выходу блока управления, вход начальной установки которого соединен с входом начальной установки блока записи, а второй выход - с входами блокировки всех элементов памяти, входы разрешения стирания и считывания блока управления являются соответственно входами разрешения стирания и считывания устройства, первый н второй счетные входы блока управления подключены соответственно к выходу блока записи

и второму выходу первого элемента памяти, каждый элемент памяти содержит элемент ШШ, первый вход которого является информационным входом элемента памяти, согласующий элемент на резисторе, один вывод которого соединен с выходом элемента ИЛИ, другой вывод - с входом формирователя импульсов, выход которого является первым выходом элемента памяти и подключен к входу элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого является входом блокировки элемен- та памяти, а выход подключен к второму входу элемента ИЛИ и является вторым выходом элемента памяти, поро

говый элемент на туннельном диоде, катод которого подключен к отрицательной шине источника питания, а анод - к входу формирователя импульсов и является входом синхронизации элемента памяти, отличающееся тем, что, с целью упрощения устройства, в каждый элемент памяти введен подстроечный элемент на переменном резисторе, один вывод которого подключен- к аноду туннельного диода, другой вывод - к положительной шине источника питания, и информационные входы всех элементов памяти подключены к выходу блока записи. I

-V4r ) V

то памяти 9.

t-uuимпульс модного потока

/ / / / /// / /

/7/11

Туннельный C8V к v ////1 sg

йиод Мыснен-и U t/fl// J , Ж

ffv -T

Туннельный диод элемента, памяти Ю

Туннельной диод элемента памяти 11

Составитель Я. Дикарев Редактор А. Ревин Техред М.Ходакич Корректор

Заказ 83

Тираж 483

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

t-uuимпульс модного потока

sg

Ж

7

t-ыи импульс

Входного потека .-р

Подписное

| Авторское свидетельство СССР № 563078, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU708420A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-02-28—Публикация

1988-02-01—Подача