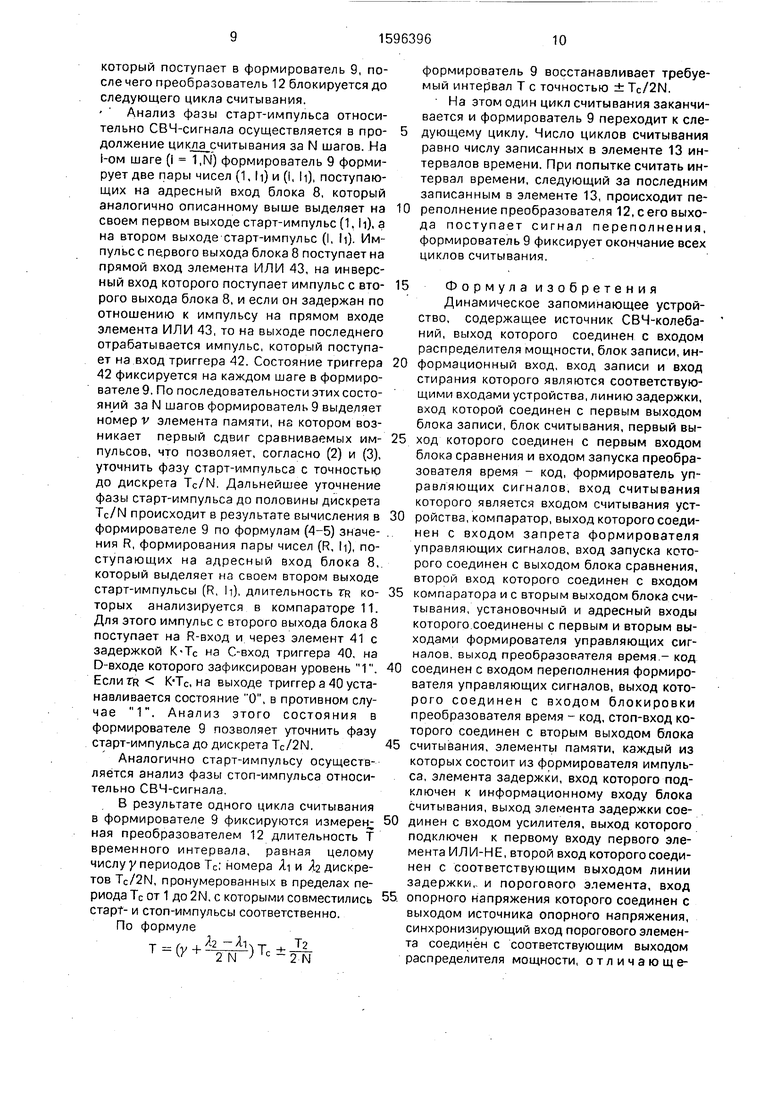

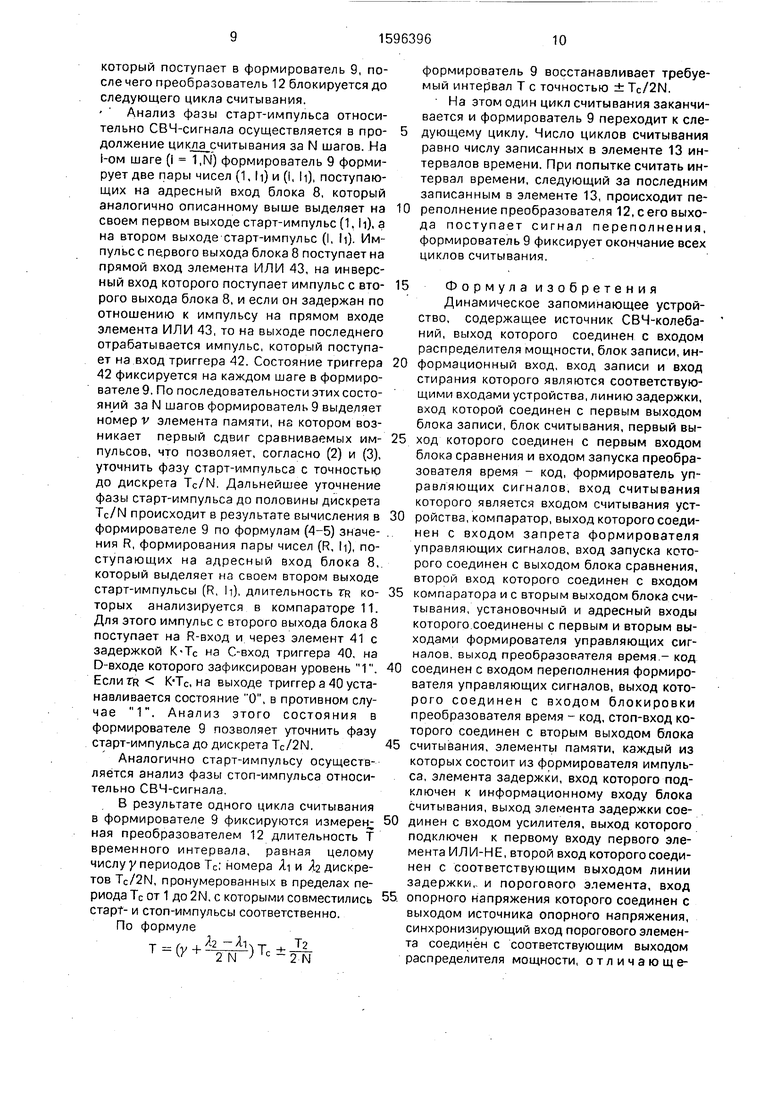

дом стирания блока 1, информационным входом которого является вход формирователя 37, управляющий вход которого соединен с выходом одновибратора 38, а выход является первым выходом блока 1, вторым выходом которого является выход одновибратора 39. Первый вход блока 8 считывания соединен с первым входом элемента И 26, выход которого соединен с входом одновибратора 27, выход которого соединен с еторым входом элемента И 26 и с являющимся входом схемы 29 селекции первым входом элемента И 30, второй вход которого подключен к выходу триггера 31, S-вход которо,го является устайовочным входом блока 8, а R-вход объединен с выходом элемента И 30, который является выходом Схемы 29 селекции и подключен к входу одновибратора 28, выход которого соединен с управляющим входом селектора 32 и 33, установочные входы которых подключены к аналогичному входу блока 8. Первый, второй и третий входы, а также адресные входы и вход управления мультиплексора 34 являются соответственно первым, вторым и третьим информационными, а также адресными и управляющими входами селектора 32. Выход мультиплексора 34 подсоединен к входу схемы 36 селекции и одновременно к счетному входу счетчика 35, S-и р-входы которого соединены соответственно с установочным и адресным входами селектора 32, а выход подключен к установочному входу схемы 36 селекции, выход которой является выходом селектора 32 и первым выходом блока 8, вторым выходом которого является выход селектора 33. Первый, второй, третий и адресные входы селектора 32 объединены с аналогичными входами селектора 33 и подключены соответственно к первому, второму, третьему и адресным входам блока 8 считывания. Входом компаратора 11 является R-вход триггера 40, который соединен через элемент 41 задержки с его С-входом, а выход триггера 40 является выходом компаратора 11. Первый вход блока 10 сравнения соединен с прямым входом элемента И 43, инверсный вход которого соединен с вторым входом блока 10, а выход элемента И 43 подключен к входу триггера 42, выход которого является выходом блока 10 сравнения. Первый полюс резистора 19 и туннельного диода 20 являются соответственно входом и входом опорного напряжения порогового элемента 18, а их вторые полюсы объединены и являются одновременно выходом и синхронизирующим входом элемента 18, последний из которых является также синхронизирующим входом элемента 13 памяти. Выход источника 21

опорного напряжения подключен к входу опорного напряжения порогового элемента 18, выход которого соединен с входом формирователя 22, выход которого является выходом элемента 13 памяти и через элемент 23 задержки подключен к входу усилителя 24, выход которого соединен с первым входом элемента ИЛИ-НЕ 16, второй вход которого подключен к соответствующему

0 выходу секционированной линии 5 задержки, а выход соединен с первым входом элемента ИЛИ-НЕ 17, выход которого соединен с входом порогового элемента 18, а второй вход объединен с третьим входом элемента

5 ИЛИ-НЕ 16 и подключен к второму выходу блока 1 записи.

Аналогично организованы элементы 14 и 15 памяти. Первый выход блока 1 подключен к входу секционированной линии 5 задержки. Выход источника 6 СВЧ-колебаний соединен с входом распределителя 7 мощности, выходы которого соединены с синхронизирующими входами соответствующих элементов 13, 14 и 15 памяти, выходы которых подключены соответственно к первому, второму и третьему входам блока 8, первый выход которого подключен к первому входу блока 10 и входу запуска преобразователя 12. а второй выход соединен с вторым входом

0 бяока 10, входом компаратора 11 и стоп-входом преобразователя 12. Установочный и адресный входы блока 8 подключены к аналогичным выходам формирователя 9 управляющих сигналов, вход считывания которого соединен с шиной 25, а выход соединен с входом блокировки преобразователя 12. Выходы компаратора 11 и блока 10 сравнения подключены соответственно к первому и второму входам формирователя 9 управляющих

0 сигналов, третий вход которого соединен с выходом преобразователя 12 время - код.

Пороговый элемент 18 вьтолнен в виде формирующего устройства на туннельном диоде с одним устойчивым состоянием.

5 Устройство работает следующим образом,

В исходное состояние оно приводится по сигналу с входа 4, которым запускается одновибратор 39. Импульс одновибратора

0 39 с длительностью, превышающей период То циркуляции элементов 13, 14 и 15, блокирует контур циркуляции, состоящий из элементов ИЛИ-НЕ 16 и 17, порогового элемента 18, формирователя 22. элемента

5 23 задержки и усилителя 24. На выходах элементов 13, 14 и 15 устанавливается логический О. В отсутствие импульсов на выходе элемента 13 одновибратор 27 находится в УСТОЙС1ИВОМ состоянии с логическим уровнем 1 на выходе. На выходе одновибратоpa 28 установлен логический О, что блокирует информационные входы селекторов 32 и 33. В исходном состоянии входной поток, поступающий с входа 2 в блок 1, блокирован формирователем 37. На вход опорного напряжения элемента 18 поступает напряжение источника 21, которое устанавливает порог срабатывания туннельного диода 20. С выходов распределителя 7 на синхронизирующие входы элементов 13, 14 и 15 синфазно поступает СВЧ-сигнал с периодом То, который модулирует уровень порога элемента 18 и аналогичные пороговые уровни элементов 14 и 15 памяти.

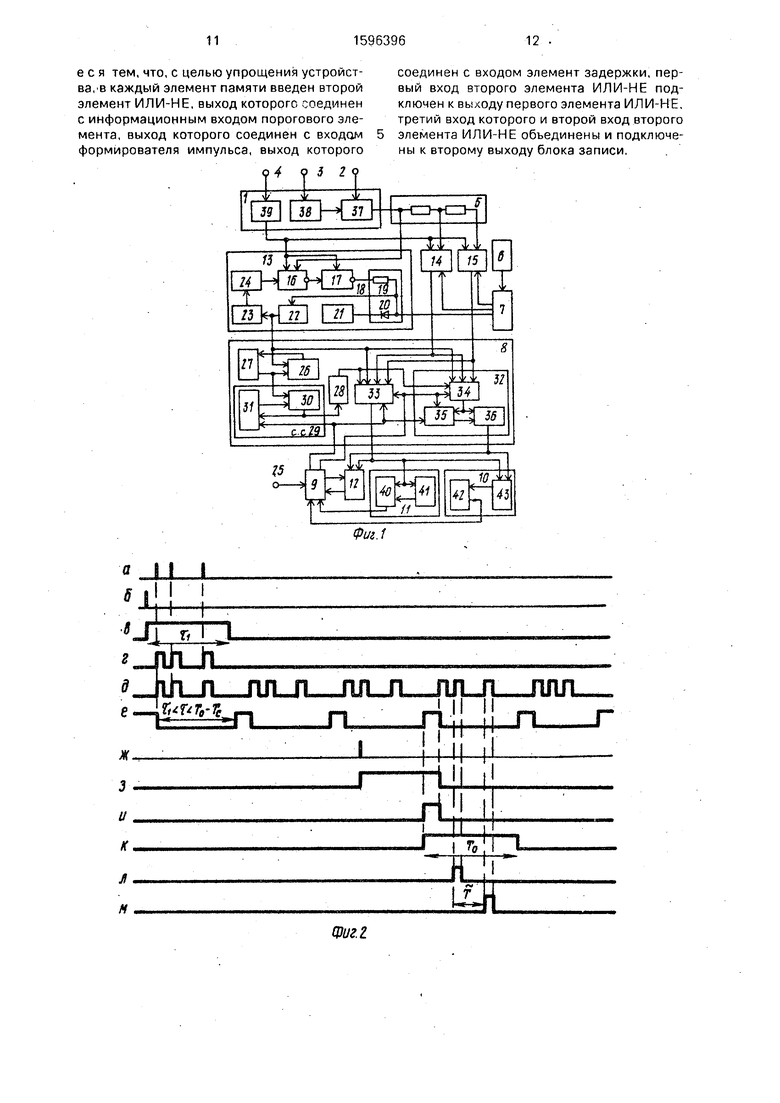

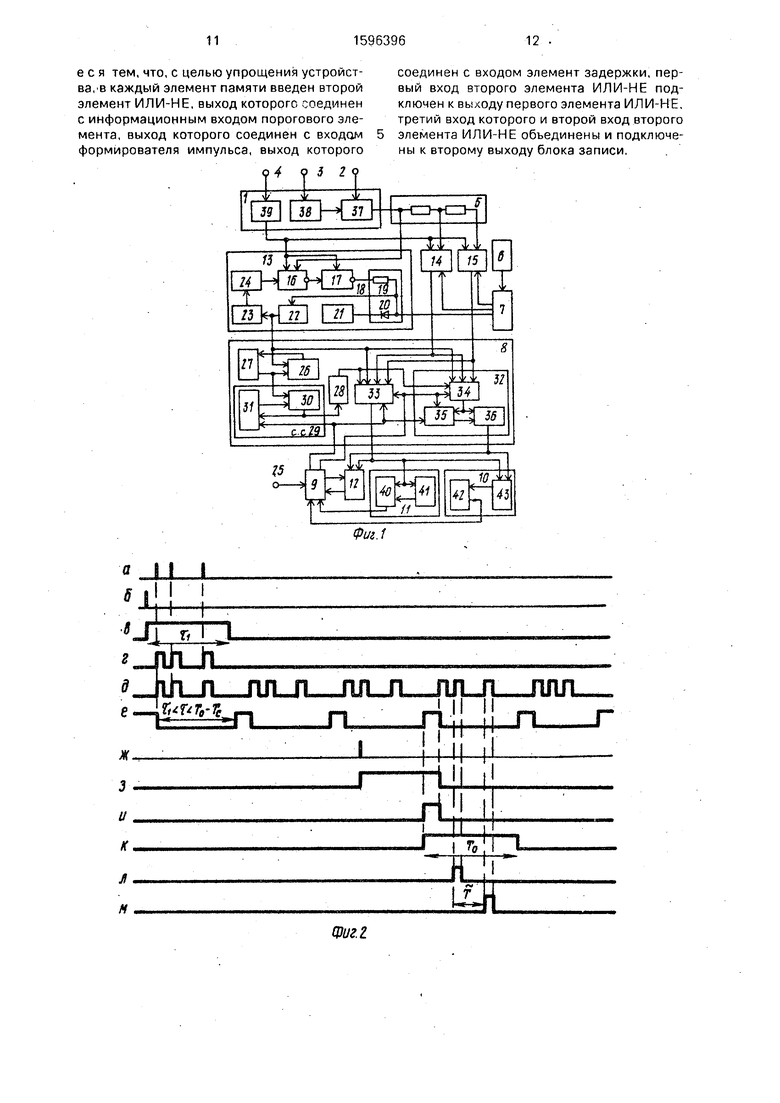

Запись в элементы 13-15 потока импульсов с входа 2 (фиг. 2а) осуществляется по сигналу, который подается на вход 3 (фиг. 26) и запускает одновибратор 38, выходной сигнал которого (фиг. 2в) открывает на время п То - Тс формирователь 37. В результате на первом выходе блока 1 появляется сформированный формирователь 37 информационный поток стандартных импульсов (фиг. 2г) длительности

(К-Ь Tjrrn) Тс при четном N

tkпри нечетном N

К -Тс

где N - количество элементов памяти (для устройства на фиг. 1 N 3);

К- наименьшее из чисел 1, 2,..., обеспечиваемое быстродействием формирователя 37...

Эти импульсы Г1оступают на вход секционированной линии 5 задержки, которая состоит из (N-1) одинаковых элементов с задержкой на каждом элементе Tc/N. С первого выхода линии 5 задержки импульсы поступают на второй вход элемента ИЛИНЕ 16 и записываются в контур циркуляции элемента 13 памяти. Аналогично происходит запись задержанных импульсных последовательностей в контуры циркуляции элементов 14 и 15. Первый записанный импульс с выхода элемента 13 (фиг. 2д) через открытый элемент И 26 запускает одновибратор 27 (фиг. 2е), который закрывает элемент И 26 до возвращения на выход элемента 13 первого записанного импульса, который вновь запускает одновибратор 27, и процесс повторяется (фиг. Зе).

Хранение потока импульсов в элементе 13 осуществляется в результате его непрерывного обращения в контуре циркуляции с периодом То пТс,.где п - кратность синхронизации элемента 13. В стационарном режиме хранения длительность импульсов, в потоке кратна Тс/2. Это достигается тем, что пороговый элемент 18 работает в режиме триггера Шмидта с устойчивым состоянием на тунЯельной ветви вольт-амперной характеристики диода 20. Переключение порогового элемента 18 г риводит к синхронизации фронта и спада каждого импульса потока с фиксированной в пределах периода Тс фазой СВЧ-сигнала (фазой синхронизации). Так как фронт переключает элемент 18 из состояния О в 1, а спад - из состо0 яния 1 в О, то фазы синхронизации для каждого из этих переключений сдвинуты на , Тс/2. Следовательно, длительность импульсов, циркулирующих в элементах памяти 13-15, равна целому числу полупериодов

5 СВЧ-сигнала. Интервалы между импульсами равны целому числу периодов Тс. Так как каждый из импульсов в элементе 13 сфазирован с синхронизирующим СВЧ-сигналом, то это ведет к деформации на выходе элемента 13 длительностей временных интервалов, сформированных на первом выходе блока 1. Для повышения точности устройства на этапе записи формируется, а затем хранится в элементах памяти 13-15 позиционный код, который содержит информацию о фазе СВЧ-сигнала, отвечающей моменту поступления на выход блока 1 каждого импульса в потоке. Это позволяет при считывании уточнить фазу прихода каждого

0 импульса в пределах периода Тс СВЧ-сигнала и провести коррекцию длительности интервалов, считываемых с выхода элемента 13.

Режим формирования устройством no-i

5 зиционного кода.

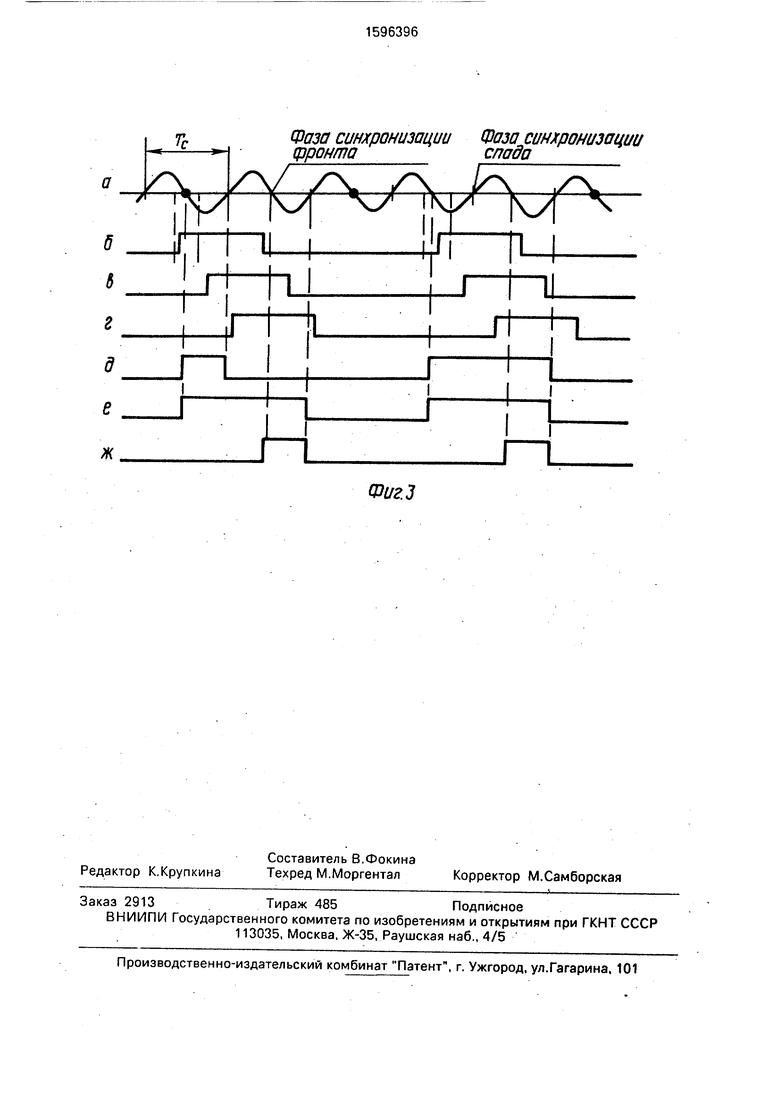

Без ограничения общности под. периодом Тс можно понимать временной интервал между ближайшими точками перехода СВЧ-синусоиды через ноль (фиг. За), в которых ее первые производные положительны. Записываемый импульс потока поступает на вход элемента 13 (фиг. 36) и далее последовательно через рремя Tc/N на входы элементов 14 (фиг. Зв) и 15 (фиг. Зг). Для

5 устройства на фиг. 1 N 3. Если фронт импульса на входе элемента 13 совпадает во времени с сегментом Ij некоторого периода Тс СВЧ-сигнала, где

,N, (2)

то с этим периодом совпадают фронты импульсов, поступающих на элементы памяти с номерами I 1,N+ 1-j и получаемых в результате размножения записываемого импульса линией 5 задержки (отсчет элементов памяти следует начинать с элемента, подключенного к первому выходу секционированной линии 5 задежки). Импульсы на

входах элементов памяти с номерами i N + 2-j,N совмещаются уже со следующим периодом СВЧ-сигнала (фиг. Зг). Происходит запись каждого из импульсов в соответствующий элемент памяти.

Вследствие синхронизации на пороговом элементе 18 фронты импульсов в элементах памяти с номерами 1,N+1 оказываются жестко сфазированными с фазой синхронизации одного и того же периода СВЧ-сигнала (фиг. Зд,е) и в режиме хранения синфазно повторяются на выходах этих элементов памяти. Синфазно, но со сдвигами на период Тс повторяются фронты иг пульсов на выходах элементов памяти с номерами N +2 -,. Зж). Если импульсы на выходах элементов памяти с номерами от 1 до N синфазны, то считаем, что сдвиг происходит на выходе фиктивного (N+1)-ro элемента памяти. Номер v N + 2-j элемента, на котором происходит описанный сдвиг, может служить кодом для номера J сегмента Ij. Связь v и j даетсяформулой

j N + 2 -v.v 2,N +1 , (3) что позволяет по номеру v уточнить в пределах периода Тс до дискрета Tc/N фазу исходного импульса, поступившего на вход элемента 13.

Дополнительное уточнение фазы записанного импульса с точностью до дискрета Tc/2N достигается за счет анализа длительностигк импульса позиционного кода на выходе R-ro элемента прамяти, где

V4- .1 +у

(4)

R V- 1у+ 1 I

для четных N и

,+ ,N,

V |N4:1, n,.

для нечетных N. При этом, если TR (К- )Тс,

то фройт импульса на входе элемента 13 памяти совмещается с первой половиной сегмента ij, найденного по формуле (3), если

TR (К + 2 )с. то - с второй половиной этого

сегмента.

Аналогично формируется позиционный код для каждого импульса, поступающего с выхода блока записи.

Восстановление длительности интервалов входного потока по записанной в элементах памяти информации состоит в

выделении и преобразовании интервалов времени в соответствии с алгоритмом считывания, ваеденным в формирователь 9. Это осуществляется с помощью .блока 8 считывания, формирователя 9, преобразователя 12, компаратора 11 и блока 10 сравнения. По сигналу с входа 25 запускается алгоритм считывания, организованный в виде циклов считывания интервалов времени.

0 Любой импульс, хранимый в элементах памяти 13-15, однозначно определяется парой чисел (I, I), где i - номер элемента памяти, в котором он записан, а I - его порядковый номер в этом элементе по отношению к опорному импульсу, формируемому на выходе схемы 29 селекции.

Цикл считывания начинается с формирования в формирователе 9 двух пар чисел (1, И) и (1, 2) .которые поступают на адрес0 ный вход блока 8 и определяют соответственно старт- и стоп-импульсы,. ограничивающие выделяемый интервал из потока, хранимого в элементе памяти 13. Значение I 1 поступает на адресный вход

5 мультиплексора 34, а значение И - на D-вход счетчика 35. Аналогично распределяются значения I 1 и 12 в селекторе 33. Далее формирователь 9 формирует на управляющем входе преобразователя 12 сигнал разблокировки, а

0 также импульс (фиг. 2ж), который подводится к установочному входу блока 8, воздействует на триггер 31 (фиг. 2з), открывающий, в свою очередь, элемент И 30. Импульсом одновибратора 27 элемент И 30 закрывается,

5 и на выходе схемы 29 селекции формируется опорный импульс (фиг. 2и), привязанный к началу циркуляции в элементе 13 памяти. Этим импульсом запускается одновибратор 28, управляющий сигнал которого длительностью То (фиг. 2к) поступает на управляющие входы селекторов 32 и 33, Старт-импульс, отвечающий значениям (1, li), выделяется на выходе селектора 32 (фиг. 2л) в течение действия импульса одно5 вибратора 28.

Аналогично выделяется стоп-импульс на выходе селектора 33 (фиг. 2м).

Селектор 32 работает следующим образом. На адресном входе мультиплексора 34

0 установлен код 1, а в счетчике 35 по импульсу с установочного входа блока 8 записано значение I, По сигналу одновибратора 28 временной поток 1-го элемента памяти с выхода мультиплексора 34 поступает на счетчик 35

5 и схему 36 селекции. При досчете до единицы счетчик 35 устанавливает схему 36 селекции, на выходе которой выделяется импульс с номером I. Временной интервал Т между выделенными старт- и стоп-импульсами преобразуется преобразователем 12 в код.

который поступает в формирователь 9, послечего преобразователь 12 блокируется до следующего цикла считывания. Анализ фазы старт-импульса относительно СВЧ-сигнала осуществляется в продолжение цикла считывания за N шагов. На i-OM щаге (1 1,N) формирователь 9 формирует две пары чисел (1, И) и (I, И), поступающих на адресный вход блока 8, который аналогично описанному выше выделяет на своем первом выходе старт-импульс (1, Н), а на втором выходе старт-импульс (I, li). Импульс с первого выхода блока 8 поступает на прямой вход элемента ИЛИ 43, на инверсный вход которого поступает импульс с второго выхода блока 8, и если он задержан по отношению к импульсу на прямом входе элемента ИЛИ 43, то на выходе последнего отрабатывается импульс, который поступает на вход триггера 42. Состояние триггера 42 фиксируется на каждом шаге в формирователе 9. По последовательности этих состоян ий за N шагов формирователь 9 выделяет номера элемента памяти, из котором возникает первый сдвиг сравниваемых импульсов, что позволяет, согласно (2) и (3), уточнить фазу старт-импульса с точностью до дискрета Tc/N. Дальнейшее уточнение фазы старт-импульса до половины дискрета TC/N происходит в результате вычисления в формирователе 9 по формулам (4-5) значения R, формирования пары чисел (R, li), поступающих на адресный вход блока 8,. который выделяет на своем втором выходе старт-импульсы (R, И), длительность TR которых анализируется в компараторе 11. Для этого импульс с второго выхода блока 8 поступает на R-вход и через элемент 41 с задержкой К-Тс на С-вход триггера 40, на D-входе которого зафиксирован уровень 1. Если TR КТс, на выходе триггер а 40 устанавливается состояние О, в противном случае 1. Анализ этого состояния в формирователе 9 позволяет уточнить фазу старт-импульса до дискрета Tc/2N.

Аналогично старт-импульсу осуществляется анализ фазы стоп-импульса относительно СВЧ-сигнала.

В результате одного цикла считывания в формирователе 9 фиксируются измерен,; ная преобразователем 12 длительность Т временного интервала, равная целому числу у периодов Тс; номера AI и Д2 дискретов Tc/2N, пронумерованных в пределах периода Тс от 1 до 2N, с которыми совместились старт- и стоп-импульсы соответственно.

По формуле

А2 Т2

Ич-г

Т-(у +

-) 1с ±

2 N

2N

формирователь 9 восстанавливает требуемый интервал Т с точностью ± Tc/2N.

На этом один цикл считывания заканчивается и формирователь 9 переходит к следующему циклу. Число циклов считывания равно числу записанных в элементе 13 интервалов времени. При попытке считать интервал времени, следующий за последним записанным в элементе 13, происходит переполнение преобразователя 12, с его выхода поступает сигнал переполнения, формирователь 9 фиксирует окончание всех циклов считывания.

5 Формула изобретения

Динамическое запоминающее устройство, содержащее источник СВЧ-колебаний, выход которого соединен с входом распределителя мощности, блок записи, информационный вход, вход записи и вход стирания которого являются соответствующими входами устройства, линию задержки, вход которой соединен с первым выходом блока записи, блок считывания, первый выход которого соединен с первым входом блока сравнения и входом запуска преобразователя время - код, формирователь управляющих сигналов, вход считывания которого является входом считывания устройства, компаратор, выход которого соединен с входом запрета формирователя управляющих сигналов, вход запуска которого соединен с выходом блока сравнения, второй вход которого соединен с входом

5 компаратора и с вторым выходом блока считывания, установочный и адресный входы которого.соединены с первым и вторым выходами формирователя управляющих сигналов, выход преобразователя время.- код

0 соединен с входом переполнения формирователя управляющих сигналов, выход которого соединен с входом блокировки преобразователя время - код, стоп-вход которого соединен с вторым выходом блока

5 считывания, элементы памяти, каждый из которых состоит из формирователя импульса, элемента задержки, вход которого подключен к информационному входу блока считывания, выход элемента задержки соединен с входом усилителя, выход которого подключен к первому входу первого элемента ИЛИ-НЕ, второй вход которого соединен с соответствующим выходом линии задержки,- и порогового элемента, вход

5. опорного напряжения которого соединен с выходом источника опорного напряжения, синхронизирующий вход порогового элемента соединён с соответствующим выходом распределителя мощности, отличающее с я тем, что, с целью упрощения устройства,В каждый элемент памяти введен второй элемент ИЛИ-НЕ, выход которого соединен с информационным входом порогового элемента, выход которого соединен с входам формирователя импульса, выход которого

соединен с входом элемент задержки, первый вход второго элемента ИЛИ-НЕ подключен к выходу первого элемента ИЛИ-НЕ, третий вход которого и второй вход второго элемента ИЛИ-НЕ объединены и подключены к второму выходу блока записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство | 1987 |

|

SU1465914A1 |

| Запоминающее устройство | 1988 |

|

SU1547032A1 |

| Цифровой стробоскопический преобразователь повторяющихся электрических сигналов | 1986 |

|

SU1386913A1 |

| Запоминающее устройство | 1978 |

|

SU743037A1 |

| Устройство для регистрации динамических процессов | 1989 |

|

SU1702358A1 |

| Устройство дискретных задержек импульса | 1988 |

|

SU1587626A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| РАДИОСТАНЦИЯ | 2010 |

|

RU2484583C2 |

| РАДИОСТАНЦИЯ | 2010 |

|

RU2465727C2 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

Изобретение относится к вычислительной технике и позволяет упростить устройство записи и хранения импульсных потоков /ИП/. Цель изобретения - упрощение устройства. Запись ИП осуществляется посредством блока записи и секционированной линии задержки. Хранение ИП происходит в блоке идентичных динамических элементов памяти /ЭП/ под воздействием синхронизирующего СВЧ-колебания, подаваемого на ЭП с СВЧ-генератора. При записи в блок ЭП синхронизируется фаза фронта и спада каждого импульса в ИП. Анализ хранимого ИП производится блоком считывания, преобразователем время-код, блоком сравнения и компаратором. 3 ил.

иI Фаза синхронизации Фронта

Фиг.З Фаза синхронизации спада

| Малевич И.А | |||

| Методы и электронные системы анализа оптических процессов | |||

| Минск: Изд | |||

| БГУ, 1981 | |||

| с | |||

| Искусственный двухслойный мельничный жернов | 1921 |

|

SU217A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1990-09-30—Публикация

1988-09-26—Подача