(5) ПАРАМЕТРИЧЕСКИЙ ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Параметрический импульсный стабилизатор постоянного напряжения | 1982 |

|

SU1035593A2 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1324016A2 |

| Импульсный параметрический стабилизатор постоянного напряжения | 1983 |

|

SU1141390A1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1984 |

|

SU1159006A1 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1559333A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Стабилизирующий преобразователь постоянного напряжения | 1985 |

|

SU1285449A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Высоковольтный стабилизированный источник напряжения постоянного тока | 1985 |

|

SU1309211A1 |

| Стабилизированный преобразователь постоянного напряжения (его варианты) | 1982 |

|

SU1117617A1 |

1

Изобретение относится к промышленности средств связи и может быть использовано при построении высокостабильных вторичных источников питания телевизионных и других импульсных синхронизируемых устройств.

Известен стабильный источник постоянного напряжения, содержащий ключевой транзистор, LCD-фильтр и управляющую схему, содержащую триггер, управляющий с помощью сброса и установки включением-выключением тронзистора, генератор, устанавливающий .режим триггера в каждый определенный период, и усилитель ошибки, переключающий триггер, когда напряжение делителя выходного напряжения превышает опорное напряжение и JНедостатками этого источника напряжения являются невысокая.стабильность выходного напряжения при изменении нагрузки, большая величина пульсаций выходного напряжения с частотой первичной сети, выбросы выходного напряжения при импульсном изменении нагрузки или при включении источника питания. Указанные недостатки обусловлены тем, что си1- нал обратной связи, управляющий через делитель выходного напряжения и усилитель ошибки моментом переключения триггера, а следовательно, и выходным напряжением, снимается с выхода LCD-фильтра, обладающего боль 0шой инерционностью.

Наиболее близким техническим решением к предложенному является параметрический импульсный стабилизатор постоянного напряжения, содержа15щий последовательно соединенные и включенные в силовую шину регулирующий (ключевой) транзистор и дроссель LCD-фильтра, конденсатор которого соединен с выходами для подключения

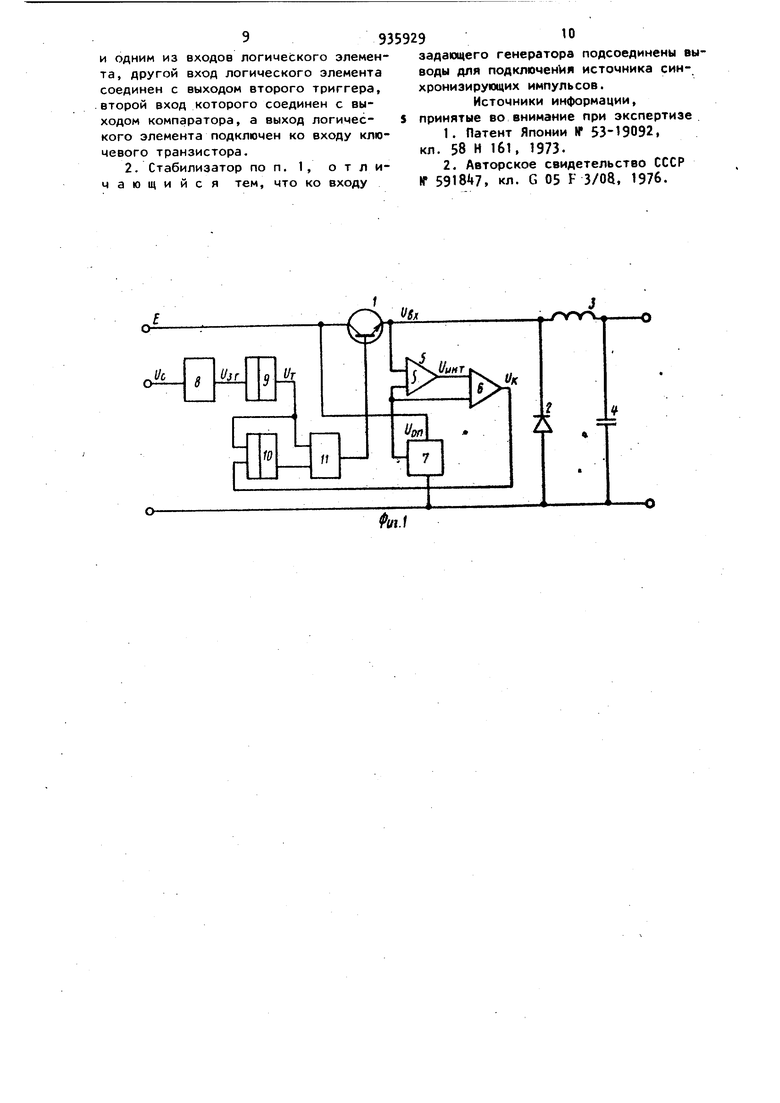

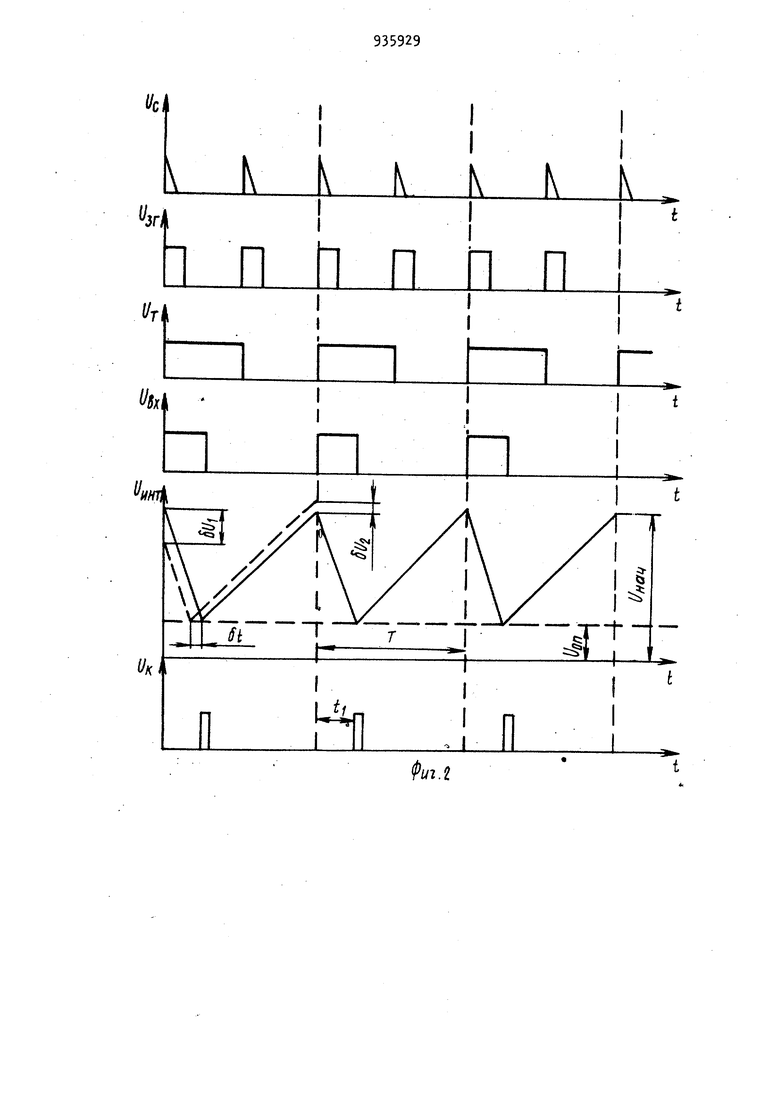

20 нагрузки., и управляющий узел. Один вход которого соединен с общей точкой регулирующего транзистора и дросселя LCD-фильтра, другой вход - с истомником опорного напряжения, а выхо подключен ко входу ключевого транзис тора. Управляющий узел выполнен в виде соединенных последовательно интегрирующего преобразователя и релей ного элемента, причем интегрирующий преобразователь подключен ко входу управляющего у.зла, а релейный элемент - к его выходу. Релейный элемент, имеющий два порога срабатывания, включает или выключает ключевой транзистор при достижении выходным напряжением интегратора одного из порогов 2. Недостатками этого стабилизатора являются большой вес и габариты и вы сокий уровень излучаемых помех. Боль шой вес и габариты обусловлены тем, что рабочая частота стабилизатора при изменении входного напряжения меняется в широких пределах, как в сторону увеличения, так и в сторону уменьшения частоты, поскольку при из менении входного напряжения изменяется скорость нарастания и спада напряжения .на выходе интегратора, что при постоянных порогах срабатывания релейного элемента, приводит к значи тельным изменениям частоты. Поэтому размеры и вес LCD-фильтра, в основном определяющие габариты и с стабилизатора и рассчитанные на наинизшую частоту, значительны. В связи с широким изменением частоты устранить воздействие широкого спектра помех на питаемую аппаратуру практически невозможно. Целью изобретения является умень шение габаритов и веса стабилизатора и уменьшения излучаемых помех. Поставленная цель достигается тем, что в параметрический импульсный стабилизатор постоянного наг)ряжения, содержащий последовательно со единенные и включенные в силовую шину ключевой транзистор и дроссель LCD-фильтра, конденсатор которого со единен с выходами для подключения на груЗки, интегратор, один вход которо го соединен с общей точкой ключевого транзистора и дросселя LCD-фильтра, другой вход - с источником опорного напряжения, введены компаратор, зада ющий генератор, два триггера и логический элемент, причем один вход ком паратора соединен с источником опорн го напряжения, другой вход - с выходом интегратора, выход задающего генератора соединен со входом первого триггера, выход которого соединен со входом второго триггера и.одним из входов логического элемента, другой вход логического элемента соединен с выходом второго триггера, второй вход которого соединен с выходом компаратора, а выход логического элемента подключен ко входу ключевого транзистора. Задающий генератор может быть синхронизирован внешними импульсами, устанавливающими основную гармонику в спектре излучения. На фиг. 1 изображена структурная схема параметрического импульсного стабилизатора постоянного напряжения; на фиг. 2 - диаграммы работы устройства, когда выходное напряжение стабилизатора меньше половины входного напряжения; на фиг. 3 диаграммы напряжений, когда выходное напряжение больше половины входного напряжения. Параметрический импульсный стабилизатор постоянного напряжения( фиг. Ij содержит последовательно соединенные и включенные в силовую шину ключевой транзистор 1 и сглаживающий LCDфильтр, состоящий из диода 2, дросселя 3 и соединенного с выводами для подключения к нагрузке конденсатора Ц. Общая точка ключевого транзистора . и дросселя соединена с инверсным входом интегратора 5, выход которого соединен с одним из входов компаратора 6. Другой вход компаратора соединен с прямым входом интегратора и источником опорного напряжения 7Задающий генератор 8, определяющий рабочую частоту стабилизатора, соединен со счетным входом первого триггера 9 выход которого подключен к счетному входу второго триггера 10 и одному из входов логического элеMcufa 11. Другой вход логического элемента подключен к выходу второго триггера, определяющего скважность импульсов на выходе интегратора. Вход сброса второго триггера соединен с выходом компаратора. Счетные выходы триггеров являются динамическими, т. е. триггера изменяю-т. свое состбяние только в моменты перепада потенциала на этих входах. Вход сброса . второго триггера - статический, т.е. триггер срабатывает при наличии напряжения определенного уровня на этом входе. Вход логического элемента, выделяющего одинаковые состояния триггеров, соединен со входом ключевого транзистора. Стабилизатор работает следующим образом. Импульсы синхронизации Ue (фиг. 2 и 3) подаются на вход задающего гене ратора 8, с выхода которого импульсы Ujr с частотой 2 f раб, где f раб рабочая частота, подаются на счетный вход первого триггера 9- Импульсы с выхода первого триггера U чистотой раб и скважностью, равном двум, по даются на счетный вход второго три|- гера 10 и логический элемент 11. С приходом очередного импульса на счет ный вход второго триггера 10, на выходе логического элемента 11 появляется первое устойчивое состояние, воздействующее на ключевой транзисто 1. Напряжение с выхода ключевого транзистора подается на вход ратора 5 и вход LCD-фильтра. В процессе интегрирования разности напряжений на входе интегратора Ugj и опорного Uon напряжение на выходе ин тегратора UKHT через некоторое время t достигает значения опорного напряжения UOP, что вызывает срабатывание компаратора 6 и возвращение второго триггера 10 в первоначальное состояние. При этом на выходе логического элемента 11 появляется второ устойчивое состояние. Далее процесс идет по описанной схеме. Напряжение на выходе интегратора 5 изменяется со временем следующим образом: . UUHT(t) и

U...y(t) - напряжение на выходе ин тегратора;

и. - напряжение на выходе пОЧ

интегратора в нaчafльныи

момент времени;

постоянная времени тегрирования;

5 напряжение на входе интегратора;

и напряжение опорного исОПточника;

t - время.

режиме стабилизации доЛжно выяться условие стационарности прое интегрирования, т. е. напряжена выходе интегратора в начальcTUa

(6) Ж

45

где cf Uj. - абсолютное значение отклонения напряжения на выходе интегратора в момент времени t Т; - абсолютное значение отклонения напряжения на выходе интегратора в момент времени t 0.

Это условие выполняется, как вид-но из фиг. 2, только тогда, когда крутизна изменения выходного напряжения интегратора за время О -t ный момент каждого периода t О должно быть равно напряжению в конце периода, при t Т, где Т - длительность периода, и равно некоторому установившемуся начальному напряжению и.нт(О) и,„ЛТ) и„«. Подставляя в (1) значения времени t Т и учитывая соотношение (2), получаем чЬ ,оп СЗ) Напряжение на выходе LCD-фильтра при условии непрерывности тока через дроссель фильтра, равно среднему значению напряжения на его входе . Т и (t)dt Подставляя значение интеграла () получаем ВЫХ ОП Таким образом, выходное напряжение практически не зависит от входного напряжения, уровня сравнения компаратора, постояннс й времени интегрирования, рабочей частоты, температуры, и равно опорному напряжению. Для выполнения условия (2) необходимо, чтобы отклонение напряжения на выходе интегратора от стационарной величины в конце периода по абсолютной величине не превышало бы значения возмущения, вызывающего это отклонение, в начале периода (фиг. -2) т.е. больше, чем за время , что соответствует следующему условию При невыполнении условия (7) небольшое отклонение выходного напряжения интегратора от установившегося значения в начале периода, вызывает в конце периода отклонение, большее по абсолютной величине, чем начальное, которое, в свою очередь, вызывает еще большее отклонение в конце следующего периода, в результате чего в стабилизаторе возникают автоколебания на частотах ниже рабочей час тоты. Выполнение условия (7) достига ется тем, что импульсы с выхода первого триггера, скважность которых равна двум, ограничивают длительност времени t на уровне половины периода. Для того, чтобы максимальное выход ное напряжение при выполнении уелоВИЯ (7) было меньше половины мини мального входного напряжения, в качест ве логического элемента используется элемент совпадения 2И,поскольку в этом случае ключевой транзистор открыт в течение времени О - t, а 3aKpiJh- в течение времени t - Т. При этом, как следует из фиг, 2, напряжение на выходе интегратора больше или равно опорному напряжению. Поэтому KOMnapa тор подключен прямым входом i источнику опорного напряжения, а инверсным входом - к выходу интегратора. Для того, чтобы минимальное выходное напряжение при выполнении условия(1} было больше половины максимального ВХОДНОГО напряжения, в качестве логического элемента используется элемент совпадения с отрицанием 2И-НК, поскольку в. этом случае ключевой гра зистор в течение времени О - .. заТ, от а в течение времени t крыт. При этом, как видно из фиг. напряжение на выходе интегратора меньше или равно опорному напряжению, Поэтому компаратор в этом случае подключен прямым входом к интегратору, а инверсным входом к источнику опорно го напряжения. Постоянство рабочей частоты стабилизатора позволяет уменьшить размеры и вес LCD-фильтра в раза и более при коэффициенте стабилизации несколь ко тысяч и высоких динамических по3, казателях по входному напряжению. Учитывая, что размеры и вес LCD-фильтра составляют до 50-60% от общего веса и габаритов стабилизатора, в случае выполнения последнего на дискретной элементной базе, и до 80% - в случае использования гибридно-пленочной технологии, общий вес и габариты предлагаемого стабилизатора уменьшаются в среднем в 1,5-2 раза. Стабильность рабочей частоты, определяемая стабильностью задающего генератора, и возможность работы с внешней синхронизацией позволяют применять стабилизатор.во вторичных источниках питания телевизионных устройств, что улучшает качество изображения за счет подавления инвериантного спектра излучения, а также и в других импульсных синхронизирующих устройствах. Кроме того, ограничение длительности импульсов повышает надежность и уменьшает выбросы в моменты включения ивыключения стабилизатора. Уменьшение размеров и веса LCDфильтра происходит в основном за счет уменьшения числа конденсаторов фильтра, в качестве которых в настоящее время применяются остродефицитные дорогостоящие конденсаторы с объемно-пористым танталовым анодом. Таким образом, применение пр)ейлагаемого стабилизатора уменьшает и себестоимость вторичных источников питания. Формула изобретения 1. Параметрический импульсный стабилизатор постоянного напряжения, содержащий последовательно соединенные и включенные в силовую шину ключевой транзистор и дроссель LCD-фильтра, конденсатор которого соединен с выводами для подключения нагрузки, интегратор, один вход которого соединен с общей точкой 1 лючевого транзистора и дросселя LCD-фильтра, другой вход - с источником опорного напря жения, о т л и ч а ю щ и и с я тем, что, с целью уменьшения габаритов и веса стабилизатора и уменьшения излучаемых помех, в негр введены компаратор, задающий генератор, два триггера и логический элемент, причем один вход компаратора соединен с источником опорного напряжения, другой вход - с выходом интегратора, выход задающего генератора соединен со входом первого триггера, выход которого соединен со входом второго триггера

и одним из входов логического элемента, другой вход логического элемента соединен с выходом второго триггера, .второй вход которого соединен с выходом компаратора, а выход логического элемента подключен ко входу ключевого транзистора.

задающего генератора подсоединены выводы для подключенУ1Я источника синхронизирующих импульсов.

Источники информации, принятые во внимание при экспертизе

п n

n п

Авторы

Даты

1982-06-15—Публикация

1980-10-08—Подача