4

ISD

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный детектор | 1986 |

|

SU1367130A1 |

| Устройство для измерения девиации частоты | 1985 |

|

SU1298676A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1709266A2 |

| Измеритель амплитудно-частотных и временных характеристик | 1989 |

|

SU1705767A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для кодирования сигналов частотных датчиков | 1987 |

|

SU1564728A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьппе- ние точности детектирования. Детектор содержит формирователь 1 коротких импульсов, формирователь 2 управляющих импульсов, счетчики 3, 8, 12 и 13, блок памяти 4, ЦАП 5, фильтр 6 низких частот, опорный г-р 7, регистр 9, блок сравнения 10, эл-т И 11 и делитель 14 частоты с переменным коэф. деления. Цель достигается введением счетчика 13.и делителя 14, с помощью которых производится самонастройка детектора на диапазон частот входного сигнала при максимально возможной точности детектирования. Кроме того, в детекторе производится линейное нормирование выходного сигнала за счет обеспечения автоматической подстройки частоты опорного г-ра 7 под диапазон девиации входного частотно- модулированного сигнала, позволяющей устранить зависимость амплитуды выходного сигнала детектора от диапазона девиации входного сигнала. Дана ил. выполнения формирователя 1, 3 ил.

9U9,f

Изобретение относится к радиотехнике, предназначено для использования в системах демодуляции частотно-модулированного и частотно-мани- пулированного сигнала и является усовершенствованием изобретения по авт.ев, № 1367130,

Цель изобретения - повышение точности детектирования цифрового час- тотного детектора.

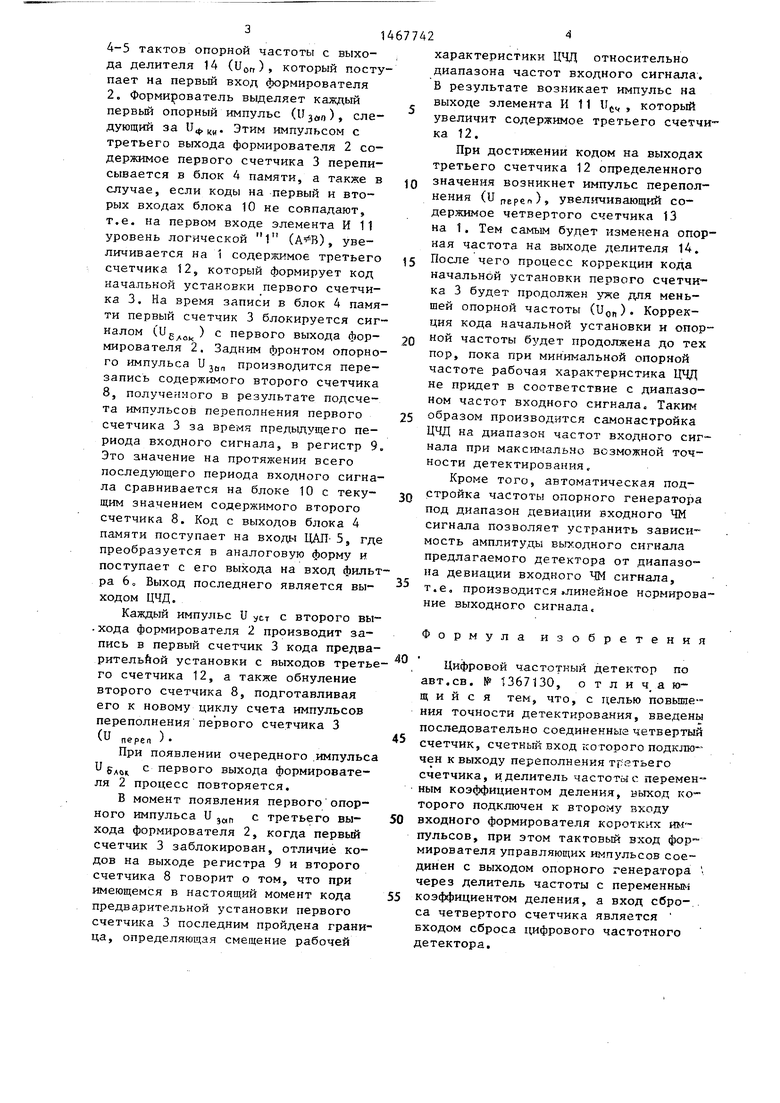

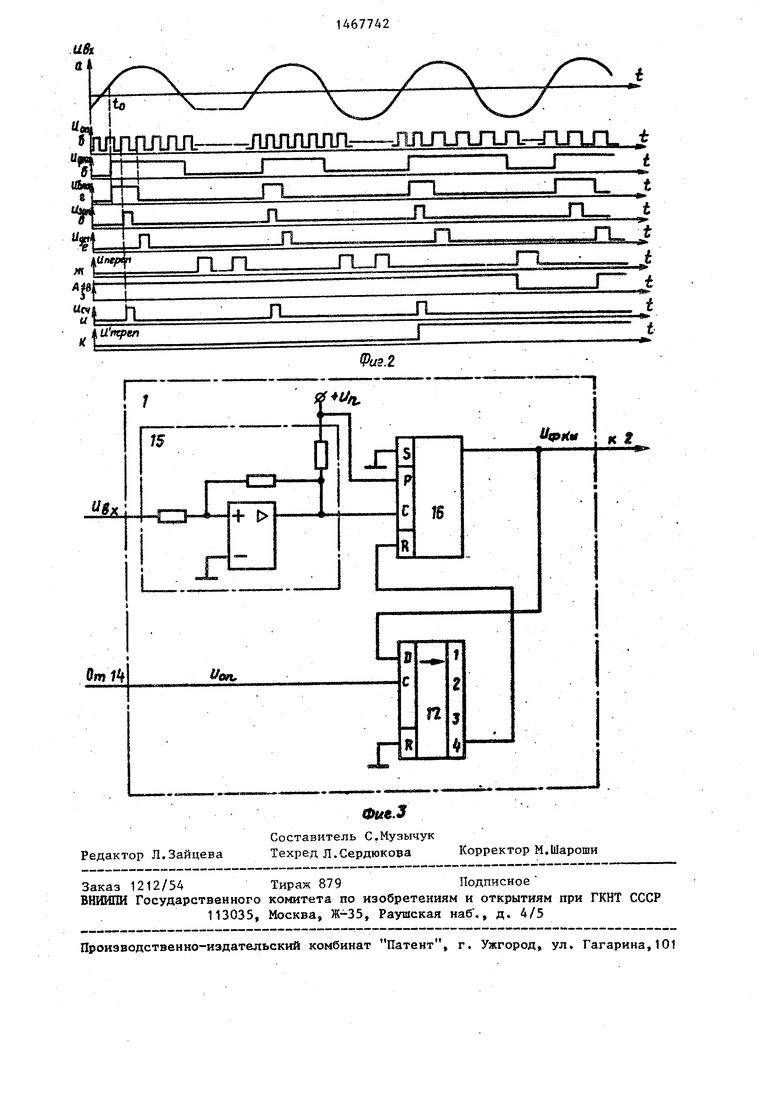

На фиг. 1 приведена структурная схема цифрового частотного детектора j на фиг. 2 - временные .диаграммы поясняющие его работу; на фиг. 3 - пример реализации формирователя коротких импульсов.

Цифровой частотный детектор содержит входной формирователь 1 коротких импульсов, формирователь 2 управляющих импульсов, первый счетчик 3, блок 4 памяти, цифроаналого- вый преобразователь (ЦАП) 5; фильтр

6низких частот, опорный 7 генератор, второй счетчик 8, регистр 9, блок 10 сравнения, элемент И 11, третий счетчик 12, четвертый счетчик

13, делитель 14 частоты с переменным коэффициентом деления„

Формирователь 1 коротких импуль- сов содержит компаратор 15, D-триг- гер 16 и регистр 17 сдвига.

Цифровой частотный детектор (ЦЧД) работает следующим образом.

В исходном состоянии, когда входной сигнал ЦЧД отсутствует, на выходе формирователя 1 устанавливается уровень логического О, который устанавливает уровень логического нуля на всех трех выходах формирователя 2,

Содержимое первого счетчика 3 цикличес ки изменяется под воздействием импульсов опорной частоты на его счетном входе, поступающем с выхода делителя 14, но поскольку сигналы записи в блок 4 памяти с третьего выхода формирователя 2 отсутствуют, то код на выходе блока 4 памяти остается неизменным и равным одному из значения в диапазоне от О до 2 -1 (где m - разрядность первого счетчика 3). Этот код с выхода блока 4 памяти поступает на входы ЦАП-5 и с выхода ЦА11 5 напряжение, соответствующее входному коду, че- рез фильтр 6 поступает на выход ЦЧД, Сигналы с выхода опорного генератора

7поступают на счетный вход делите

Q

5

0

5

О

0 5

5

0

ля 14, который преобразует их в соответствии с кодом коэффициента деления на входах установки коэффициента деления в импульсы опорной частоты соответствующего периода. Сигналы опорной частоты с выхода делителя 14 поступают также на второй вход формирователя 2. Содержимое второго счетчика 8 циклически изменяется под воздействием импульсов переполнение первого счетчика 3 и подается на зходы регистра 9 и первые входы блока 10. Поскольку пульсы записи в регистр 9 с третьего выхода формирователя 2 отсутствуют, то код на вторых входах блока 10, приходящий с выходов регистра 9, остается неизменным и равным одному из значений в диапазоне от О до 2 -1 (где k - разрядность второго счетчика 8), Выходной сигнал блока 10, равный уровню логической единицы за исключением момента, когда содержимое второго счетчика 8 становится равным коду на выходе регистра 9, подается на первый вход элемента И 11, но не влияет на его выход, где установлен уровень логического нуля, так как на втором входе этого элемента отсутствует сигнал с Третьего выхода формирователя 2. Код с выходов третьего счетчика 12, для которого сигнал на выходе элемента И 11 является счетным, остается неизменным и равным одному из значений в диапазоне от О до (разрядности счетчиков 3 и 12 равны).

Так как импульсы переполнения третьего счетчика 12, являющиеся L счетными дпя четвертого счетчика 13, отсутствуют, то на выходах четвертого счетчика 13 устанавливается произвольный код в диапазоне от О до 2 -1 (где 1 - разрядность четвертого счетчика 13). Этот код определяет частоту опорных импульсов на выходе делителя 14.

После подачи сигнала Сброс на вход сброса четвертого счетчика 13 на его выходах устанавливается код минимально возможного коэффициента деления делителя 14 и ЦЧД подготавливается к работе.

При превышении входным сигналом (Ugj) заранее установленного порога (момент времени t, фиг. 3) на выходе формирователя 1 будет сформирован импульс UcjKu длительностью

4-5 тактов опорной частоты с выхода делителя 14 (Uor,) , который поступает на первый вход формирователя 2, Формирователь выделяет каждый первый опорный импульс (U „), следующий за ифк„. Этим импульсом с третьего выхода формирователя 2 содержимое первого счетчика 3 переписывается в блок 4 памяти, а также в случае, если коды на первый и вторых входах блока 10 не совпадают, т.е. на первом входе элемента И 11 уровень логической 1 (), увеличивается на I содержимое третьего счетчика 12, который формирует код начальной установки первого счетчика 3. На время запис и в блок 4 памяти первый счетчик 3 блокируется сигналом (Ug) с первого выхода формирователя 2. Задним фронтом опорного импульса Ujt, производится перезапись содержимого второго счетчика 8, полученного в результате подсчета импульсов переполнения первого счетчика 3 за время предыдущего периода входного сигнала, в регистр 9 Это значение на протяжении всего последующего периода входного сигнала сравнивается на блоке 10 с текущим значением содержимого второго счетчика 8, Код с выходов блока 4 памяти поступает на входы ДАЛ- 5, где преобразуется в аналоговую форму и поступает с его выхода на вход фильтра 6 „ Выход последнего является выходом цчд.

Каждый импульс U уст с второго вы- хода формирователя 2 производит запись в первый счетчик 3 кода предва- рительйой установки с выходов третьего счетчика 12, а также обнуление второго счетчика 8, подготавливая его к новому циклу счета импульсов переполнения первого счетчика 3 U переп )

При появлении очередного .импульса блок с первого выхода формирователя 2 процесс повторяется.

В момент появления первого опорного импульса и з„п с третьего вы- хода формирователя 2, когда первый счетчик 3 заблокирован, отличие кодов на выходе регистра 9 и второго счетчика 8 говорит о том, что при имеющемся в настоящий момент кода предварительной установки первого счетчика 3 последним пройдена граница, определяющая смещение рабочей

4

o

5

0

5

0

характеристики ЦЧД относительно диапазона частот входного сигнала. В результате возникает импульс на выходе элемента И 11 U(, , который увеличит содержимое третьего счетчика 12.

При достижении кодом на выходах третьего счетчика 12 определенного значения возникнет импульс переполнения (и переп), увеличивающий содержимое четвертого счетчика 13 на 1. Тем самым будет изменена опорная частота на выходе делителя 14. После чего процесс коррекции кода начальной установки первого счетчика 3 будет продолжен уже для меньшей опорной частоты (UQ). Коррекция кода начальной установки и опорной частоты будет продолжена до тех пор, пока при минш- альной опорной частоте рабочая характеристика ЦЧД не придет в соответствие с диапазоном частот входного сигнала. Таким образом производится самонастройка ЦЧД на диапазон частот входного сигнала при максимально возможной точности детектирования.

Кроме того, автоматическая подстройка частоты опорного генератора под диапазон девиации входного ЧМ сигнала позволяет устранить зависимость амплитуды выходного сигнала предлагаемого детектора от диапазона девиации входного ЧМ сигнала, т.е, производится .линейное нормирование выходного сигнала.

Формула из

о б р е т а

н и я

5

Цифровой частотный детектор по авт.св. № 1367130, о т л и ч, а ю- щ и и с я тем, что, с целью повышения точности детектирования, введены последовательно соединенные четвертый счетчик, счетный вход которого подключен к выходу переполнения третьего счетчика, и делитель частоты с переменным коэффициентом деления, выход которого подключен к второму входу входного формирователя коротких импульсов, при этом тактовый вход формирователя управляющих импульсов соединен с выходом опорного генератора . через делитель частоты с переменньич коэффициентом деления, а вход сбро-,. са четвертого счетчика является входом сброса цифрового частотного детектора.

Г7

| Цифровой частотный детектор | 1986 |

|

SU1367130A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-03-23—Публикация

1987-07-22—Подача