&0

С7:

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный детектор | 1987 |

|

SU1467742A2 |

| Цифровой частотный детектор | 1991 |

|

SU1827709A1 |

| Цифровой частотно-фазовый дискриминатор | 1982 |

|

SU1027798A1 |

| Цифровой частотно-фазовый дискриминатор | 1984 |

|

SU1256139A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Цифровой частотный детектор | 1983 |

|

SU1193765A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2000 |

|

RU2169988C1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1185561A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

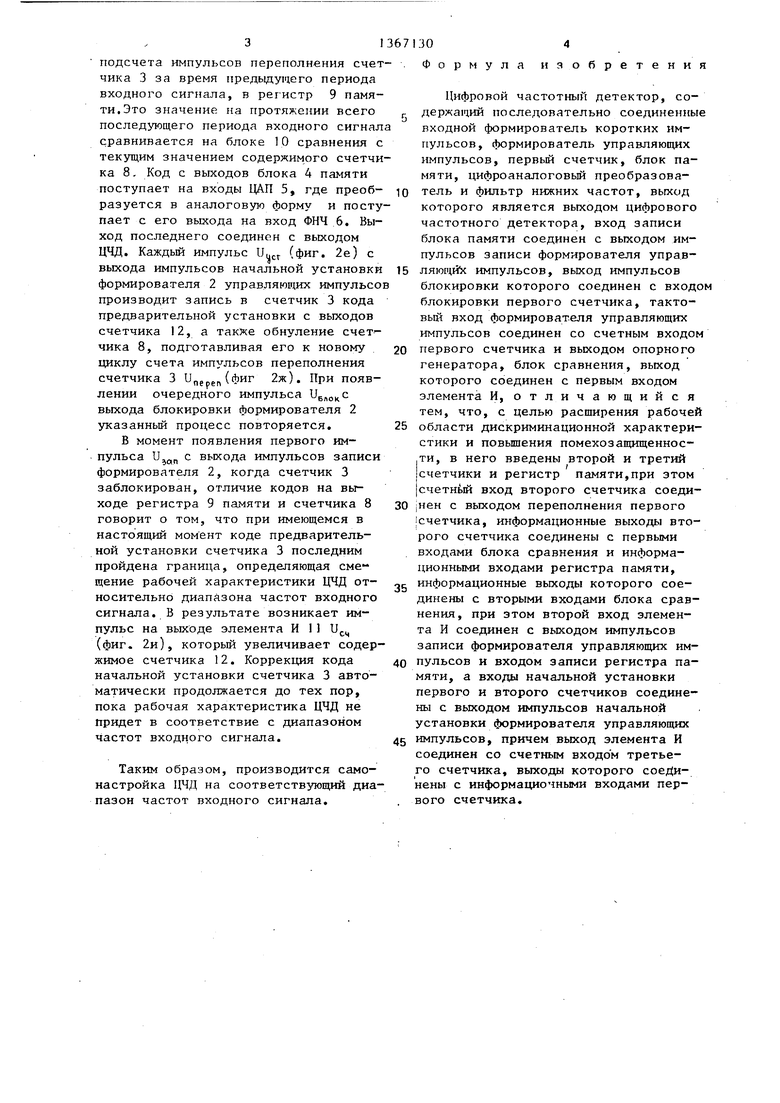

Изобретение относится к радиотехнике. Цель изобретения - расширение рабочей области дискриминационной характеристики и повьшение помехозащищенности. Цифровой частотный детектор (ЦЧД) содержит входной формирователь 1 коротких импульсов, формирователь 2 управляющих импульсов, счетчик 3, блок 4 памяти, ЦАП 5, фильтр 6 нижних частот, опорный генератор 7, блок 10 сравнения, элемент И 11. Введены два счетчика 8, 12 и регистр 9 памяти. Содержимое счетчика 8 циклически изменяется под воздействием импульсов переполнения счетчика 3 и подается на информационные входы регистра 9 памяти и первые входы блока 10. Отличие кодов на выходах регистра 9 памяти и счетчика 8 говорит о том, что при имеющемся в настоящий момент коде предварительной установки счетчика 3 последним пройдена граница, определяющая смещение рабочей х-ки ЦЧД относительно диапазона частот входного сигнала. В результате воз- . никнет импульс на выходе элемента И 11, который увеличит содержимое счетчика 12. Коррекция кода начальной установки счетчика 3 будет автоматически продолжена до тех пор, пока рабочая х-ка ЦЧД не придет в соответствие с диапазоном частот входного сигнала. 2 ил. с

(риг1

1

Изобретение относится к радиотехпике и предназначено для использования в системах демодуляции частотно- модулированных и частотно-манипулиро ванных сигналов.

Цель изобретения - расвшрение рабочей области дискриминационной характеристики и повьйче ние помехозащищенности.

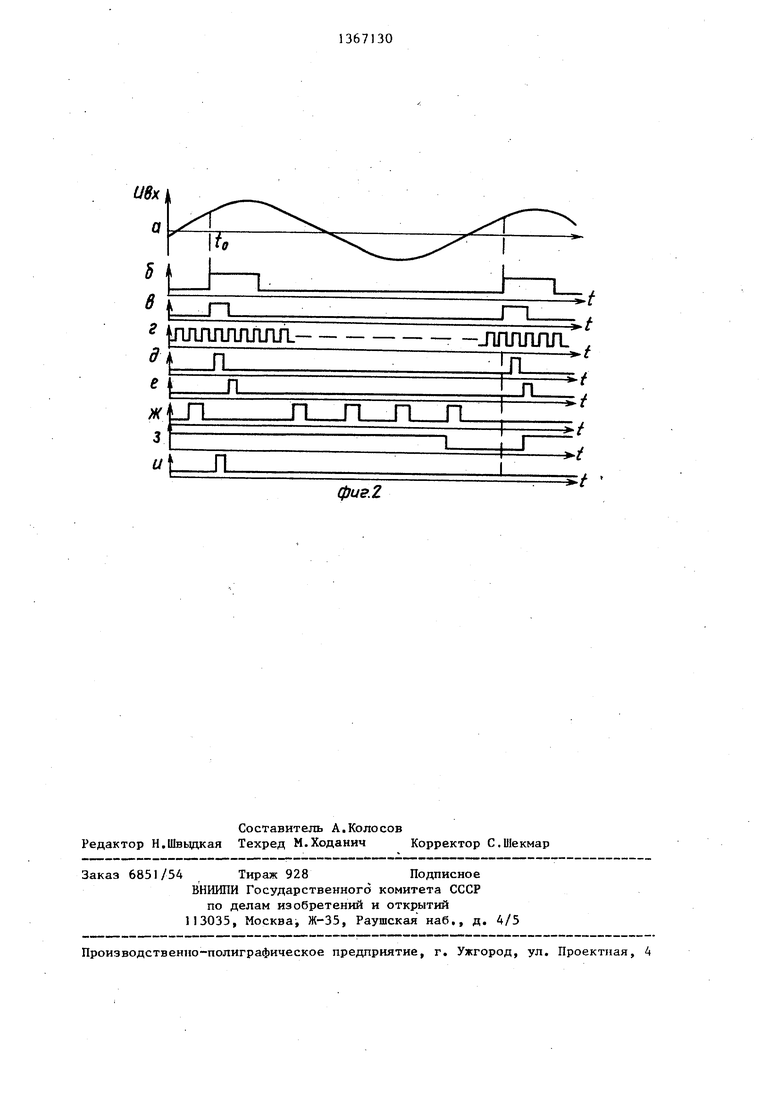

На фиг.1 приведена структурная электрическая схема цифрового частотного детектора; на фиг.2 - временные диаграммы, поясняющие его работу.

Цифровой частотньй детектор со- держит входной формирователь 1 коротких импульсов, формирователь 2 управляющих импульсов, первый счетчик 3, блок 4 , цифроаналого- вьй преобразователь (ЦА11) 5, фильтр 6 нижних частот (ФНЧ), опорный генератор 7j второй счетчик 8., регистр 9 памяти, блок 10 сравнения, элемент И 11, третий счетчик 12.

Устройство работает следующим об- разом.

В исходном состоянии, когда входной сигнал цифрового частотного детектора (ЦЧЛ) отсутствует, на выходе формирователя 1 коротких импуль- сов устанавливается уровень ло1 кчес- кого нуля, который устанавливает уровни логического нуля на всех трех выходах формирователя 2 управляющих импульсов.

Содержимое счетчика 3 циклически изменяется под воздействием импульсов опорной частоты на его счетном входе, поступающих с выхода опорного генератора 7, но поскольку сигна лы записи в блок 4 памяти с выхода импульсов записи формирователя 2 отсутствуют, то код.на выходе блока 4 памя.ти остается неизменным и рав- ным одному из значений в диапазоне 0-(2 - 1), где m - разрядность счетчика 3. Этот код с выхода блока 4 памяти поступает на входы ЦАП 5 и с выхода НАЛ 5 в напряжение, соответствующее входному коду, через ФНЧ 6 поступает на выход ЦЧД.

Сигналы опорной частоты с выхода опорного генератора 7 поступают также на тактовый вход формирователя 2 Содержимое счетчика 8 циклически из- меняется под воздействием импульсов переполнения счетчика 3 и подается на информационные входы регистра 9 памяти и первые входы блока 10 срав

02

нения. Поскольку импульсы записи в регистр 9 памяти с выхода импульсов записи формирователя 2 управляющих импульсов отсутствуют, то код на вторых входах блока 10 сравнения, приходящий с информационных выходов регистра 9 памяти,остается неизменным и равным одному из значений в диапазоне О - (2 -1), где к - раз- рядность счетчика 8. Выходной сигнал блока 10 сравнения равен уровню логической единицы за исключением момента, когда содержимое счетчика 8 становится равным коду на выходе регистра 9 памяти и подается на первый вход элемента И 11,но не влияет на его выход, где установлен уровень логического нуля,, так как на втором входе этого элемента отсутствуют импульсы записи .с выхода формирователя 2 управляющих импульсов. Код с выходов счетчика 12, для которого сигналы на выходе элемента И 11 являются счетными, остается неизменным и равным одному из значений в диапазоне О - (2 - 1), разрядности счетчиков 3 и 12 равны. При превыпении входным сигналом Ug (фиг.2а) заранее установленного порога (момент времени t, фиг. 2а) на выходе входного формирователя формируется импульс и„(фиг. 26) длительностью, превьшающей четыре такта частоты опорного генератора 7 и,, (фиг. 2г), которьм поступает на первый вход формирователя 2 управляющих импульсов. Формирователь 2 управляющих импульсов выделяет каждый первый опорный импул1 с и,(фиг. 2д), следующий за и .. Этим импульсом с вькода имЧ И „

пульсов записи формирователя Z управляющих импульсов содержимое счетчика 3 переписывается в блок 4 памяти, а также в случае, если коды на первых и вторых входах блока 10 сравнения не совпадают, т.е. на первом входе элемента И 11 уровень логической единицы (фиг. 2з), увеличивается на единицу содержимое счетчика 12, который формирует код начальной установки счетчика 3. На время записи в блок 4 памяти счетчик 3 блокируется сигналом Ug (фиг.,2в) с первого выхода формирователя 2 управляющих импульсов. Задним фронтом опорного импульса U, (фиг. 2д) производится перезапись содерж ймого счетчика 8, полученного в результате

подсчета импульсов переполнения счет чика 3 за время предыдутцего периода входного сигнала, в регистр 9 памяти. Это значение на протяжении всего

последующего периода входного сигнал

сравнивается на блоке 10 сравнения с текущим значением содержимого счетчика 8. Код с выходов блока 4 памяти поступает на входы ЦАП 5, где преоб- разуется в аналоговую форму и поступает с его выхода на вход ФНЧ 6. Выход последнего соединен с выходом ЦЧД. Каждьй импульс и,. (фиг. 2е) с выхода импульсов начальной установки формирователя 2 управляющих импульсо производит запись в счетчик 3 кода предварительной установки с выходов счетчика 12, а такхе обнуление счетчика 8, подготавливая его к новому циклу счета импульсов переполнения счетчика 3 U (фиг 2ж). При появлении очередного импульса выхода блокировки формирователя 2 указанный процесс повторяется,

В момент появления первого импульса с выхода импульсов записи формирователя 2, когда счетчик 3 заблокирован, отличие кодов на выходе регистра 9 памяти и счетчика 8 говорит о том, что при имеющемся в настоящий момент коде предварительной установки счетчика 3 последним пройдена граница, определяющая смещение рабочей характеристики ЦЧД от- иосительно диапазона частот входного сигнала. В результате возникает импульс на выходе элемента И 1 1 И (фиг. 2и), который увеличивает содержимое счетчика 12. Коррекция кода начальной установки счетчика 3 автоматически продолжается до тех пор, пока рабочая характеристика ЦЧД не придет в соответствие с диапазоном частот входного сигнала.

Таким образом, производится самонастройка ЦЧД на соответствующий диапазон частот входного сигнала.

Формула изобретени

Цифровой частотный детектор, содержащий последовательно соединенны входной формирователь коротких импульсов, формирователь управляющих импульсов, первый счетчик, блок памяти, цифроаналоговьй преобразователь и фильтр нижних частот, выход которого является выходом цифрового частотного детектора, вход записи блока памяти соединен с выходом импульсов записи формирователя управ- ляющи с импульсов, выход импульсов блокировки которого соединен с вход блокировки первого счетчика, тактовый вход формирователя управляющих импульсов соединен со счетным входо первого счетчика и выходом опорного генератора, блок сравнения, выход которого соединен с первым входом элемента И, отличающийся тем, что, с целью расщирения рабоче области дискриминационной характеристики и повьшения помехозащищенности, в него введены второй и третий счетчики и регистр памяти,при этом счетньй вход второго счетчика соеди |нен с выходом переполнения первого счетчика, информационные выходы второго счетчика соединены с первыми входами блока сравнения и информационными входами регистра памяти, информационные выходы которого соединены с вторыми входами блока сравнения, при этом второй вход элемента И соединен с выходом импульсов записи формирователя управляющих импульсов и входом записи регистра памяти, а входы начальной установки первого и второго счетчиков соединены с выходом импульсов начальной установки формирователя управляющих импульсов, причем выход элемента И соединен со счетным входом третьего счетчика, выходы которого соединены с информационными входами первого счетчика.

ивх

а

ti

1ГШЛЛЯПЯШ1J1

фиг.2

-лллпла.

t

In

| Частотный детектор | 1982 |

|

SU1119161A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-01-15—Публикация

1986-07-09—Подача