4 Oi О5

Изобретение относится к электросвязи и может быть использовано в системах передачи данных.

Цель изобретения - повышение объема передаваемой информации путем увеличения скорости адаптации компенсирующего сигнала.

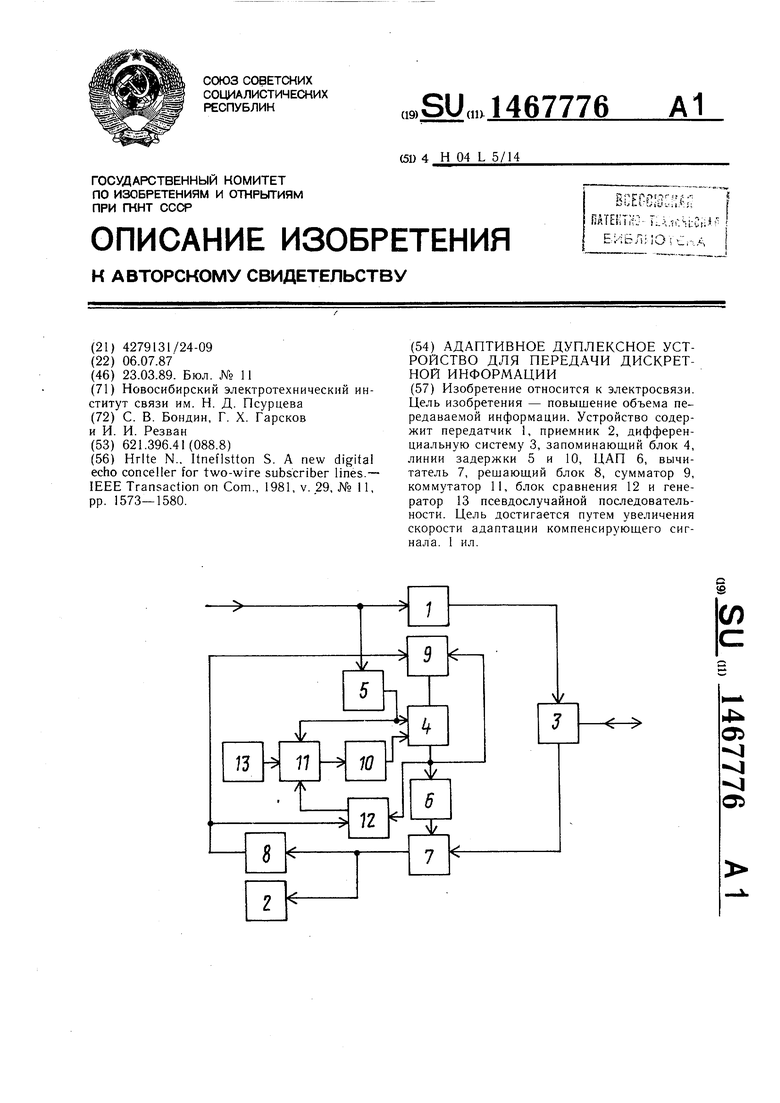

На чертеже изображена структурная электрическая схема предложенного устройства.

Адаптивное дуплексное устройство для передачи дискретной информации содержит передатчик 1, приемник 2, дифференциальную систему 3, запоминающий блок 4, первую линию 5 задержки, цифроаналоговый преобразователь 6, вычитатель 7, решающий блок 8, сумматор 9/ вторую линию 10 задержки, коммутатор 11, блок 12 сравнения и генератор 13 псевдослучайной последовательности.

Устройство работает следующим образом.

Передаваемая двоичная последовательность, подвергнутая скремблированию, подается на вход передатчика 1,. в котором преобразуется к виду, удобному для передачи по двухпроводной линии (кодируется, модулируется и т. д.). Поскольку предварительная дифференциальная система 3 может обеспечить подавление передаваемого сигнала на 10-20 дБ, часть передаваемого сигнала поступает на вход приемника 2, где превышает уровень принимаемого сигнала, который затухает в линии на 30-40 дБ на 20-30 дБ. При предположении, что импульсная реакция дифференциальной системы 3 обладает конечной длительностью (N тактовых интервалов), передаваемый сигнал на входе приемника 2 будет функцией только Л последних переданных символов. Так как принимаемый сигнал цифровой, компенсация передаваемого сигнала требуется только в отсчетные моменты времени. Для этого из запоминающего блока 4 по адресу, определяемому последними N переданными символами, извлекается отсчет компенсирующего сигнала, который вычитается в вычитателе 7 из сигнала на входе приемника 2. Заполнение запоминающего блока (т. е. накопление информации о величине компенсирующего сигнала) осуществляется следующим образом по знаковому алгоритму:

/j.fi / -+A5Jgrt/;-,(1)

где /, - оценка ошибки на г-м шаге; Д - величина шага адаптации; л, - сигнал на выходе вычитателя 7, причем

ri Si+ni+li-f:,

(2)

где S,- - принимаемый сигнал; Л; - аддитивный шум.

Знак ошибки компенсации определяется в решающем блоке 8, с выхода которого на первый вход сумматора 9 подается ЬД. На

второй вход сумматора 9 подается содержимое запоминающего блока 4 по адресу, определяемому последними N переданными символами, которое после изменения (добавления ЬА) записывается по этому же адресу.

Заполнение запоминающего блока 4 осуществляется в два этапа следующим образом. На первом этапе производится грубая настройка. На величину сигнала собственного передатчика 1 на входе приемника 2 наиболее сильное влияние оказывает последний переданный yV-й символ. Поскольку дифференциальная система 3 обладает импульсной реакцией длиной Л тактовых интер5 валов, каждый из N ранее переданных символов также оказывает влияние на величину мешающего сигнала на входе приемника 2. Причем влияние (N-К)-го символа больше влияния (jV-L)-ro при К меньше L. На первом этапе настройки компенсируется влия0 ние yV-/VI последних переданных символов, оказывающих наиболее существенный вклад в величину отсчета передаваемого сигнала на входе приемника. Для этого линия 10 задержки с отводами, формирующая адрес,

5 делается двухсекционной. На первую линию 5 задержки, которая формирует N-NI разрядный адрес А, подается двоичный сигнал с источника информации (не показан). Адрес А с выхода линии 5 задержки подается на N-N старших адресных входов

0 запоминающего блока 4. Пока комбинация передаваемых символов, определяющая адрес Л 1, не меняется (т. е. пока не проходит следующий передаваемый символ), на jVl младших разрядов адресных входов подаются все возможные комбинации (2 ) адре5 са Л2 с второй линии 10 задержки, которые образуются путем подачи на линию 10 задержки двоичных символов с генератора 13 псевдослучайной последовательности длиной ( - 1) через коммутатор 11. Таким образом величина ±Д, подаваемая с решающего

блока 8 на сумматор 9, записывается в ячеек памяти запоминающего блока 4, определяемых комбинацией адресов /41 и А2. При смене адреса /41 описанная процедура адаптации повторяется. Так как появление с всех адресов равновероятно, процесс предварительной настройки считается законченным, если знак числа, записанного в запоминающем блоке 4 на предыдущем шаге, не совпадает со знаком ошибки ±Д на выходе решающего блока 8 хотя бы по одному адре0 су. Для этого на первый вход блока 12 сравнения подается сигнал со знакового разряда выхода запоминающего блока 4, а на второй вход - сигнал знака ошибки с выхода решающего блока 8. При несовпадении знаков с выхода блока 12 сравнения по- 5 дается управляющий сигнал на управляющий третий вход коммутатора 11, который отключает от второй линии 10 задержки сигнал с генератора 13 псевдослучайной последовательности и подключает выход линии 5 задержки. После этого начинается второй этап настройки компенсации, который заключается в том, что осуществляется индивидуальная настройка по каждому из 2 адресов запоминающего блока 5. При этом учитывается влияние оставщихся Л/1 отсчетов им- .пульсной реакции, поскольку каждый возможный адрес определяется последними N переданными символами.

Формула изобретения

Адаптивное дуплексное устройство для передачи дискретной информации, содержащее передатчик, выход которого соединен со входом дифференциальной системы, выход которой соединен с первым входом вычи- тателя, выход которого подключен к входу приемника и к входу рещающего блока, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом запоминающего блока, выход ко0

5

0

торого соединен с вторым входом сумматора и с входом цифроаналогового преобразователя, выход которого подключен к второму входу вычитателя, при этом вход передатчика подключен к входу первой линии задержки, выход которой соединен со вторым входом запоминающего блока, отличающееся тем, что, с целью повыщения -объема передаваемой информации путем увеличения скорости адаптации компенсирующего сигнала, введены блок сравнения, коммутатор, вторая линия задержки и генератор псевдослучайной последовательности, выход которого соединен с первым входом коммутатора, выход которого подключен к входу второй линии задержки, выход которой подключен к третьему входу запоминающего блока, второй вход которого соединен с вторым входом коммутатора, третий вход которого подключен к выходу блока сравнения, первый вход которого подключен к выходу запоминающего блока, а выход решающего блока соединен с вторым входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дуплексной передачи сигналов | 1988 |

|

SU1570014A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ПОМОЩЬЮ ШУМОПОДОБНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2362273C2 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2117392C1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ OFDM-СИГНАЛОВ С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ | 2010 |

|

RU2423002C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2116699C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение объема передаваемой информации. Устройство содержит передатчик 1, приемник 2, дифференциальную систему 3, запоминающий блок 4, линии задержки 5 и 10, ЦАП 6, вычи- татель 7, решающий блок 8, сумматор 9, коммутатор 11, блок сравнения 12 и генератор 13 псевдослучайной последовательности. Цель достигается путем увеличения скорости адаптации компенсирующего сигнала. 1 ил.

| НгИе N. | |||

| Itneflstton S | |||

| А new digital echo conceller for two-wire subscriber lines.- IEEE Transaction on Com., 1981, v | |||

| Солесос | 1922 |

|

SU29A1 |

| Двухванная плавильная печь с поворотной фурмой | 1924 |

|

SU1573A1 |

Авторы

Даты

1989-03-23—Публикация

1987-07-06—Подача