О1

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное дуплексное устройство для передачи дискретной информации | 1987 |

|

SU1467776A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| РАДИОЛИНИЯ ДИСТАНЦИОННОГО УПРАВЛЕНИЯ | 1991 |

|

RU2013866C1 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2116699C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| СПОСОБ АДАПТИВНОГО КВАЗИКОГЕРЕНТНОГО МНОГОЛУЧЕВОГО ПРИЕМА В ПРЯМОМ КАНАЛЕ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1999 |

|

RU2178955C2 |

| УСТРОЙСТВО СВЯЗИ | 1999 |

|

RU2185033C2 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2117392C1 |

| СПОСОБ И УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ЭЛЕКТРОСЕТЯМ | 2001 |

|

RU2216854C2 |

Изобретение относится к электросвязи и может найти применение в системах передачи цифровой информации. Целью изобретения является увеличение дальности связи за счет повышения степени подавления сигнала собственного передатчика на входе приемника. Для достижения поставленной цели введены задающий генератор 9, генератор 10 псевдослучайной последовательности, первый коммутатор 7, второй коммутатор 8, формирующий фильтр 5 и сумматор 6. После определенного числа итераций в блоке памяти накапливается информация о величине корректирующего сигнала для всех возможных комбинаций передаваемых сигналов. 2 ил.

Фиг.1

Изобретение относится к электросвязи и может найти применение в системах передачи цифровой информации.

Цель изобретения - увеличение даль ности связи за счет повышения степени подавления сигнала собственного передатчика на входе приемника„

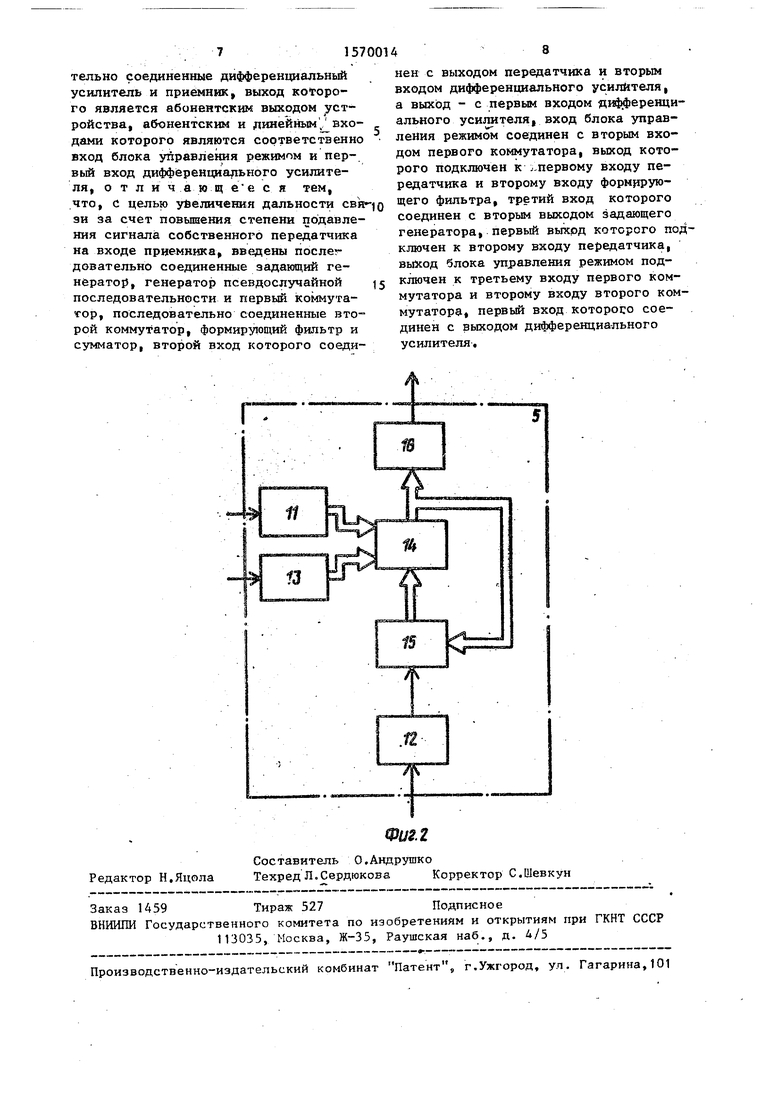

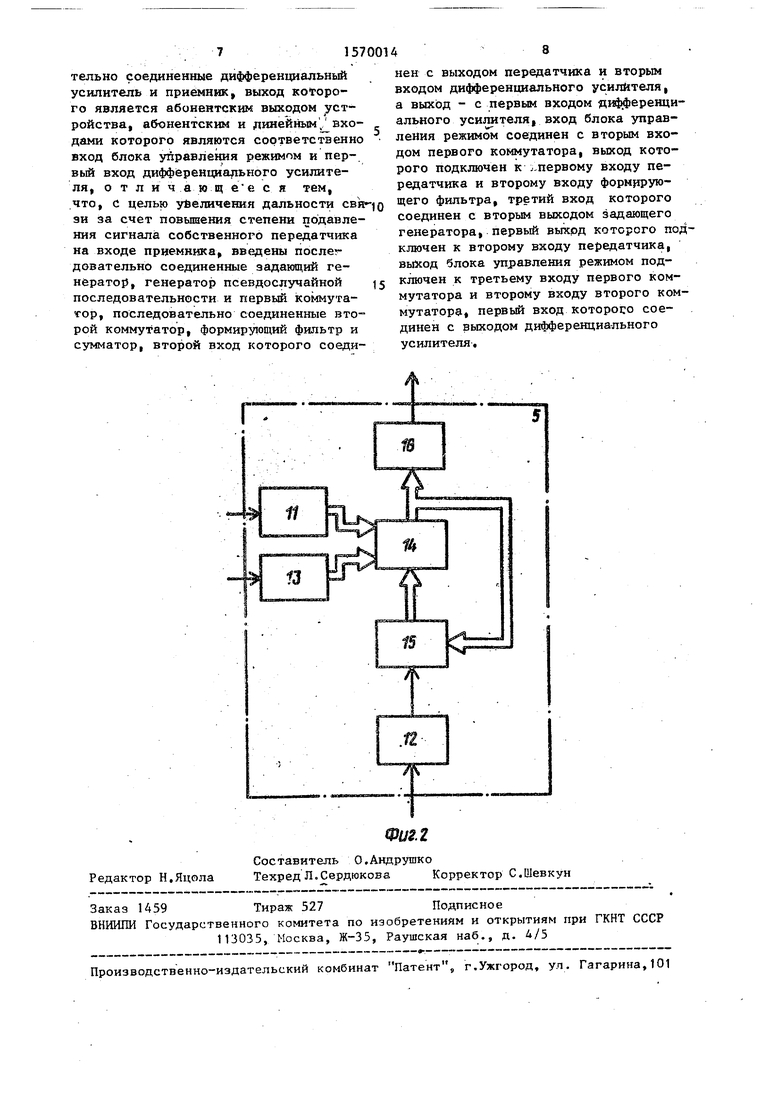

На фиг.1 изображена структурно- м электрическая схема устройства; на фиг,2 - структурно-электрическая схема формирующего фильтра.

Устройство содержит передатчик 1, приемник 2, дифференциальный усилитель 3, блок 4 управления режимом, формирующий фильтр 5, сумматор б,- первый коммутатор 7, второй коммутатор 8, задающий генератор 9 и генератор 10 псевдослучайной последовательности, причем формирующий фильтр 5 содер жит регистр сдвига 11, блок 12 решения, счетчик 13, блок 13 памяти, сумматор 15 и цифро-аналоговый преобразователь 16„

Устройство для дуплексной переда- чи сигналов работает следующим образом.

Имеется два режима работы устройства: режим настройки и режим передачи-приема, устанавливаемые блоком 4 управления режимом Режим настройки устанавливается при поступлении из источника цифровой информации служебной посылки, которая дешифрируется блоком 4 управления режимом и на его выходе появляется сигнал, который подается на третий вход первого коммутатора 7 и на второй вход второго коммутатора 8. При этом первый коммутатор 7 соединяет выход генератора 10 псевдослучайной последовательности с первым входом передатчика 1, а второй коммутатор 8 соединяет выход дифференциального усили

теля 3 с первым входом формирующего фильтра 5. Поскольку линия связи, подключенная к выходу сумматора 6, обладает реактивным входным сопротивлением, до начала настройки устройства сргналы на выходе передатчика 1 и на выходе сумматора б отличаются по амплитуде, фазе и форме друг от друга, причем амплитуда каждого из отсчетов передаваемого сигнала на выходе сумматора 6 определяется с сверткой отсчетов импульсной реакции сумматора 6 нагруженного на реактивное сопротивление линии и отсчетов выходного сигнала передатчика 1. При

допущении, что импульсная реакция конечной длительности N тактовых интервалов, йа амплитуду каждого из отсчетов передаваемого сигнала Ь . на выходе сумматора 6 оказывают влияние только N последних переданных символов. Таким образомс

-,-ЬАМ.

(5)

5 д

5

Q

5

5

0

5

где h. - отсчеты импульсной реакции. а. - отсчеты выходного сигнала передатчика,10

Для того, чтобы полностью подавить передаваемый сигнал на входе приемника 2 с помощью дифференциального усилителя 3 необходимо, чтобы сигналы на выходах передатчика 1 и сумматора 6 были одинаковы,, Таким образом настройка устройства заключается в таком изменении параметров формирующе - го фильтра 5, чтобы синтезированный им из передаваемой последовательности сигнал, складываясь в сумматоре 6 с выходным сигналом передатчика 1, пред- искажал его, компенсируя влияние реактивности линии связи. Поэтому после настройки формирующего фильтра 5 сигналы на выходе передатчика 1 и сумматора 6 оказываются равны.

Для настройки формирующего фильтра 5 используется псевдослучайная последовательность длиной 2N-1 символов, которая с выхода генератора 10 псевдослучайной последовательности через первый коммутатор 7 поступает на входы передатчика 1 и формирующего фильтра 5. Пока формирующий фильтр 5 не настроен, сигналы на первом и втором входах дифференциального усилителя 3 отличаются по амплитуде, форме и фазе. При этом сигнал на выходе дифференциального усилителя 3 пропорционален разности сигналов на его входахс Этот сигнал через второй коммутатор 8 поступает на первый вход формирующего фильтра 5 и изменяет его характеристики таким образом, чтобы уменьшить величину разностного сигнала на выходе дифференциального усилителя 3„

Режим настройки завершается при поступлении на вход блока 4 управления режимом кода конец настройки с выхода источника цифровой информации При этом сигнал с выхода блока управления режимом 4 поступает на третий вход первого коммутатора 7, который i

отключает выход Генератора 0 псевдослучайной последовательности от входа передатчика 1 и второго входа формирующего фильтра 5 и подключает к входу передатчика S выход источника цифровой информации, а также на второй вход второго коммутатора 8, который отключает выход дифференциального усилителя 3 от первого входа формирующего фильтра 5. После этого устанавливается режим передачи-приема. В течении сеанса связи параметры формирующего фильтра 5 остаются неизменными .

Формирующий фильтр 5 работает следующим образом. Поскольку, как указывалось, амплитуда отсчета передаваемого сигнала на выходе сумматора 6 однозначно определяется комбинацией N последних переданных символов, для его коррекции достаточно извлечь из блока 14 памяти по адресу, определяемому последними N переданными символами величину отсчета корректирующего сигнала, преобразовать в цифро- аналоговом преобразователе 16 в аналоговый вид и сложить в сумматоре 6 с отсчетом выходного сигнала передатчика 1. Так как амплитуда выходного сигнала сумматора 6 может изменяться на длительности одного тактового интервала, его коррекцию необходимо осуществлять п раз за тактовый интервал через промежуток времени t, причем по теореме Котельникова At Ј

- Fg, где F g- верхняя граничная

частота спектра передаваемого сигнала

Поэтому в устройстве формирование адреса, по которому хранится величина отсчета корректирующего сигнала, производится следующим образом. N старших разрядов адресных входов блока 14 памяти соединены с выходами последовательного регистра 11 сдви га, в котором хранится N последних переданных символов, М младших разрядов адрес..ых входов блока 14 памяти

50

соединены с выходами счетчика 13, на вход которого подается регулярная последовательность частотой nfт, fT - тактовая частота, со второго выхода задающего генератора 9, Поэтому на выходах счетчика 13 последователь- 55 но двоичное число от 1 до п. Сдвиг двоичной информцции по последователь- . ному регистру 11 сдвига производится с тактовой частотой fT. Следовательно,

за время, пока нд выходах регистра i1 сдвига остается очередная комбинация переданных символов, на выходах счетчика 13 последовательно появляются все возможные числа от 0 до п. Таким образом, двоичное число на адресных входах блока I4 памяти в каждый момент времени определяет адрес одного из п отсчетов корректирующего сигнала на длительности последнего переданного символа

Настройка формирующего фильтра 5 осуществляется адаптивно по знаково- му алгоритму адаптации

1 (6)

0

л

еА

е

где ё.

+ л sign г. ,

1-М

- оценка ошибки (разности) напряжений на выходе передатчика 1 и 0 сумматора 6 на i-м шаге;

Л - величина шага адаптации.„ г. - сигнал на выходе дифференциального усилителя 3, причем

25

г. е. е.

+ i

(7)

0

где п.- аддитивный шум.

Знак ошибки определяется в блоке 12 решения, ка вход которого подается сигнал с выхода дифференциального

Q усилителя 3. С выхода блока 12 реше ния на первый вход сумматора 15 подается ± & (обычно & - единица младшего разряда корректирующего числа, записанного в блоке 14 памяти). На второй вход сумматора 15 подается содержимое данной ячейки блока 14 памя- ти, которое после изменения добавления ±).записывается в эту же ячейку.

Q Таким образом, после операционного числа итераций, в блоке 14 памяти накапливается информация о величине корректирующего сигнала пля всех воз-- можных N-разрядных комбинаций переда5 ваекых сигнала.

В режиме передачи-приема второй коммутатор 8 по команде блока 4 управления режимом отключает вход блока 1 2 решения от выхода дифференциального усилителя 3 и в течение сеанса связи содержимое блока i4 памяти не изменяется - он работает только на считывание.

Формула изобретения

Устройство для дуплексной передачи сигналов, содержащее передатчик, блок управления режимом, последовательно соединенные дифференциальный усилитель и приемник, выход которого является абонентским выходом устройства, абонентским и линейным вхо- дами которого являются соответственно вход блока управления режимом и первый вход дифференциального усилителя, отличающееся тем, что, с целью увеличения дальности СВЯэй за счет повышения степени подавления сигнала собственного передатчика на входе приемника, введены последовательно соединенные задающий генератор, генератор псевдослучайной последовательности и первый коммутатор, последовательно соединенные второй коммутатор, формирующий фильтр и сумматор, второй вход которого соединен с выходом передатчика и вторым входом дифференциального усилителя, а выход - с первым входом дифференциального усилителя вход блока управления режимом соединен с вторым входом первого коммутатора, выход которого подключен к , первому входу передатчика и второму входу формирующего фильтра, третий вход которого соединен с вторым выходом задающего генератора, первый выхрд которого под ключей к второму входу передатчика, выход блока управления режимом подключен к третьему входу первого коммутатора и второму входу второго коммутатора, первый вход которого соединен с выходом дифференциального усилителя.

| Авторское свидетельство СССР 1282346, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-20—Подача