Известны быстродействующие параллельные преобразователи кода Баркера в двоичный код, построенные на феррит-транзисторных элементах.

В предлагаемом преобразователе для упрощения устройства использована ключевая схема импульсного типа, подключающая нужный подразряд в зависимости от значения предшествующего младшего разряда.

Для выполнения логической операции «НЕ в верхней ячейке ключа подразряда А каждого разряда введена обмотка для принудительной записи двоичной единицы за такт до приема кода Баркера на преобразователь и дополнительная обмотка считывания импульсом кода предществующего младшего разряда. Для увеличения быстродействия преобразователя операция подразрядного преобразования кода осуществляется путем подключения основных обмоток считывания ферриттранзисторных ячеек каждого разряда к выходам соответствующих блокинг-генераторов активной линии задержки.

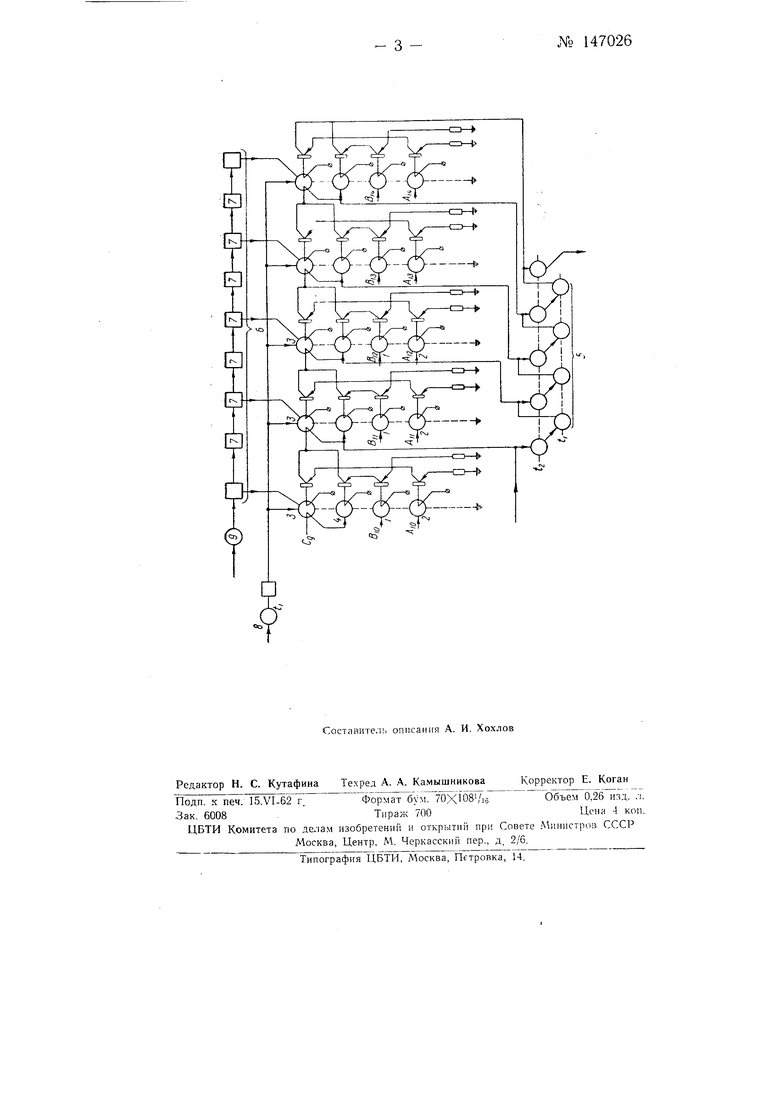

На чертеже приведена принципиальная схема описываемого преобразователя.

Для преобразования в двоичный код предлагаемый преобразователь переключает подразряды кода Баркера таким образом, чтобы выполнялась последовательность следующих элементарных логических операций: Cn- Bn-{- Cп- An Cn

где Cj - перенос или значение предществующего младщего разряда в двоичном коде; С,- - инверсия переноса; Л,-; S, - информация, поступающая на соответствующие входы преобразователя.

9)0 Сю

CjoOii-4-C

№ 147026- 2 Принцип действия преобразователя рассматривается на примере работы элементов одного разряда.

Код Баркера поступает на препбразователь параллельно в яченкн } и 2 каждого разряда. За такт до приема кода Баркера в дополнительные обмотки записи верхних ячеек 3 ключевых схем записывается двоичная «1. В момент записи кода Баркера на ячейки преобразователя импульс кода предшествующего младшего разряда Сд спишет (по дополнительной обмотке .считывания) «1 с ячейки 3 на ячейку 4. Поэтому в момент считывания тактом /ю срабатывает ключевая схема на ячейках 4 и У, т. е двоичный код разряда будет представлен значением BIO.

Согласно выражению (I) имеем

1.5,0 + 0.10 Cir,

т. е. Cio io.

Очевидно, что при значении двоичный код разряда будет представлен подразрядом А

(9.Б,о-4-/., т. е. Cio io.

Результат преобразования Сю переписывается в верхнюю ячейку 3 следуюш.его разряда и выдается на регистр 5.

Преобразование кода в последующих старших разрядах происходит аналогично.

Преобразователь использует для считывания такты (), которые вырабатываются блокинг-генераторами 6 активной линии задержки (7 - эмиттерные повторители). Благодаря высокой частоте следования тактов достигается высокое быстродействие преобразователя.

Управляющие сигналы на входы 8 я 9 поступают с программирующего устройства. Полученный двоичный код записывается параллельно в выходной регистр, построенный по двухтактной системе. Двоичный код выдается с регистра последовательно, начиная со старшего разряда.

Описываемый преобразователь может быть использован, например, в качестве устройства ввода в специализированной электронной машине.

Предмет изобретения

1.Быстродействующий параллельный преобразователь кода Баркера в двоичный код, построенный на феррит-транзисторных элементах, отличающийся тем, что, с целью упрощения устройства, в нем использована ключевая схема импульсного типа, подключающая нужный подразряд в зависимости от значения предшествующего младшего разряда.

2.Быстродействующий параллельЕ1ый преобразователь по п. 1, отличающийся тем, что, с целью выполнения Логической операции «НЕ, в верхней ячейке ключа подразряда А каждого разряда введена обмотка для принудительной записи двоичной единицы за такт до приема кода Баркера на преобразователь и дополнительная обмотка считывания импульсом кода предп ествующего младшего разряда.

3.Быстродействующий параллельный преобразователь по п. 1, отличающийся те.м, что, с целью увеличения быстродействия преобразователя, операция поразрядного преобразования кода осуществляется путем подключения основных обмоток считывания ферриттранзисторных ячеек каждого разряда к выходам соответствующих блокинг-генераторов активной линии задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА БАРКЕРА В ДВОИЧНЫЙ КОД | 1967 |

|

SU196446A1 |

| ВСГ.СОЮЗНАЯПМиЬЙО-ТШН'-'ЕСНАе БИБЛИОТЕКА | 1971 |

|

SU298075A1 |

| Устройство для преобразования параллельного -кода в последовательный двоичный код | 1974 |

|

SU523407A1 |

| Дешифратор | 1974 |

|

SU572922A1 |

| ОДНОТАКТНЬШ РЕГИСТР СДВИГА | 1970 |

|

SU265943A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА БАРКЕРА В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 1969 |

|

SU249762A1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1968 |

|

SU210489A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU702530A1 |

| СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU268008A1 |

Авторы

Даты

1962-01-01—Публикация

1960-03-07—Подача