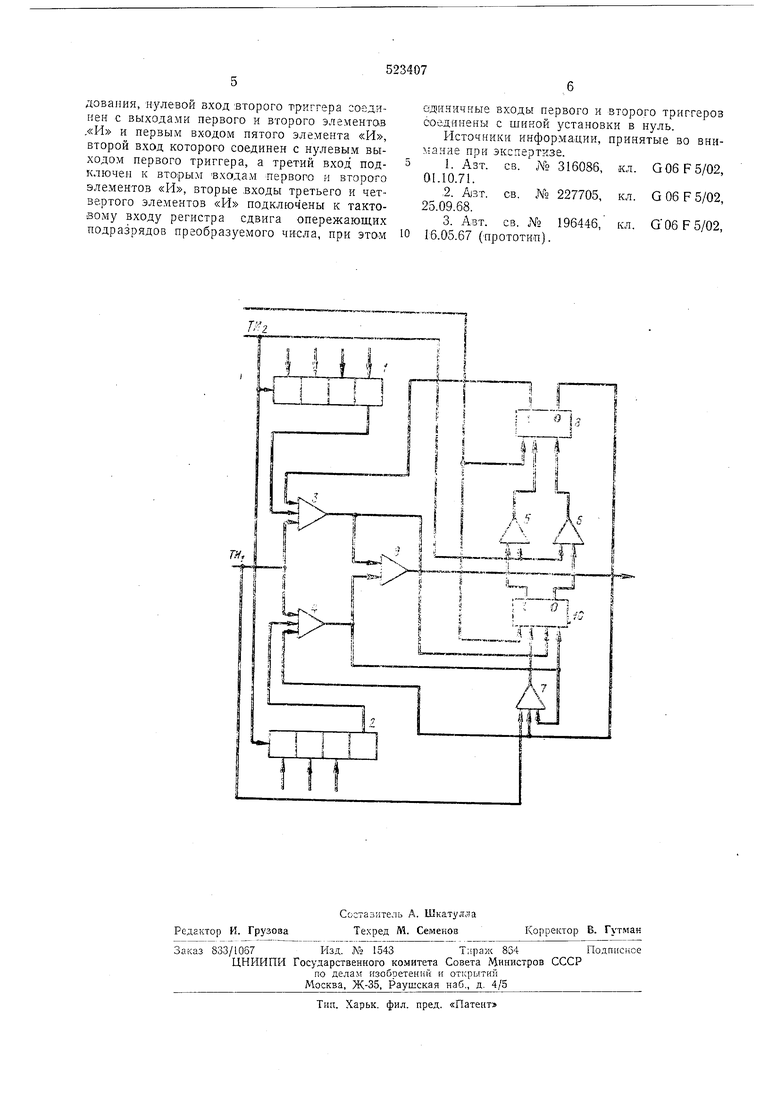

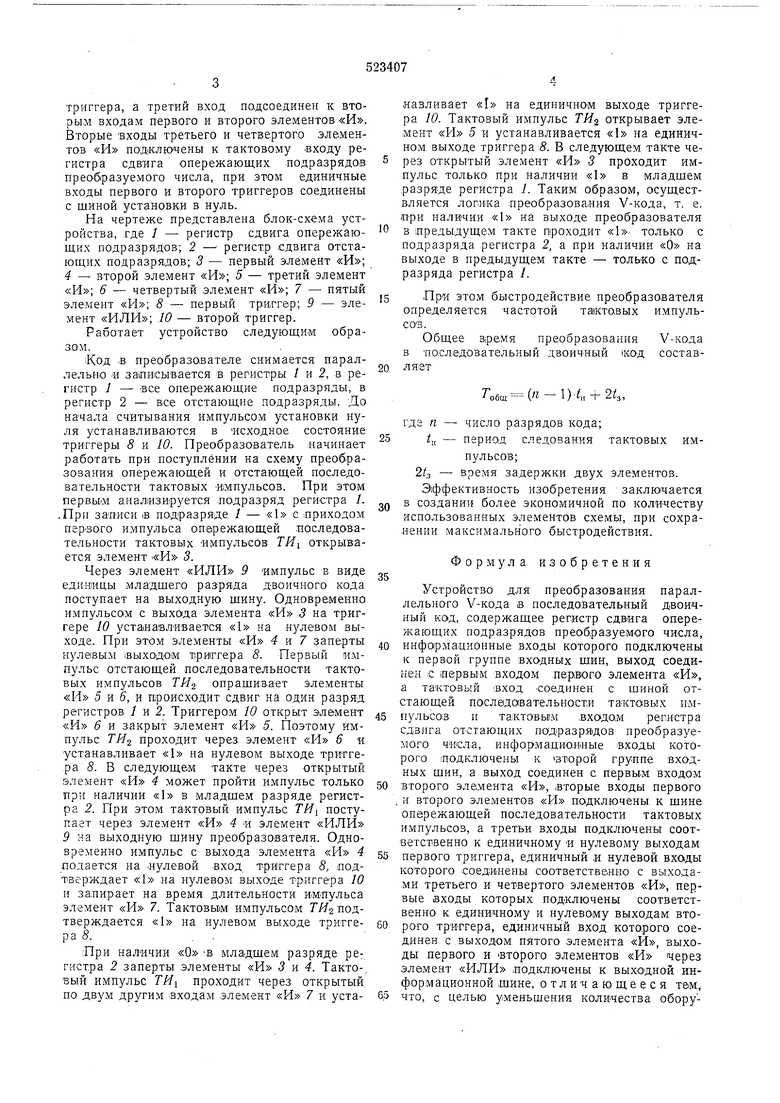

триггера, а третий вход подсоединен к вторым входам первого и второго элементов «И. Вторые ВХОДЫ третьего и четвертого элементов «И под1ключены к тактовому входу регистра сдвига опережающих подразрядов преобразуемого числа, при этом единичные входы первого и второго триггеров соединены с шиной установки в нуль. На чертеже представлена блок-схема устройства, где 1 - регистр сдвига опережающих подразрядов; 2 - регистр сдвига отстающих подразрядов; 3 - первый элемент 4 - второй элемент 5 - третий элемент 6 - четвертый элемент 7 - пятый элемент 8 - первый триггер; 9 - элемент 10 - второй триггер. Работает устройство следующим образом. :Код в преобразователе снимается параллельно И записывается в регистры 7 и 2, в регистр 1 - все опережающие подраз ряды, в регистр 2 - Bice отстающие подразряды. До начала считывания импульсом установки нуля устанавливаются в исходное состояние триггеры 8 и 10. Преобразователь ;начинает работать при поступлении на схему преобразования опережающей и отстающей последовательности тактовых «мпульсов. При этом первЫМ анализируется подразряд регистра 1. .При заПиси iB подразряде / - «1 с лриходом пер-вого импульса опережающей последовательности тактовых импульсов ТИ открывается элемент «И 3. Через элемент «ИЛИ 9 импульс в виде едивицы младшего разряда двоичного кода поступает на выходную щину. Одновременно импульсам с выхода элемента «И 3 на триггере 10 устанавливается «1 на нулевом выходе. При этом элементы «И 4 и 7 заперты нулевым 1ВЫХОД10М преггера 8. Первый импульс отстающей последовательности тактовых импульсов Г//2 опрашивает элементы «И 5 и &, и п:роисходит сдвиг на один разряд регистров / и 2. Триггером 10 открыт элемент 6 и закрыт элемент «И 5. Поэтому импульс ТИ2 проходит через элемент «И 6 устанавливает «1 на нулевом выходе триггера S. В следующем такте через открытый элемент «И 4 может пройти импульс только при наличии «1 в .младшем разряде регистра 2. При этом тактовый импульс ТИ поступает через элемент «И 4 и элемент «ИЛИ 9 на выходную шину преобразователя. Одновременно импульс с выхода элемента «И 4 полается на «улевой вход триггера 5, подтверждает «1 на нулевом выходе триггера 10 и запирает на время длительности импульса элемент «И 7. Тактовым импульсом ГЯ2 подтверждается «1 на нулевом выходе триггера 5.. , При наличии «О В младшем разряде ре: гистра 2 заперты элементы «И Л и 4. Такто-, вый импульс ТИ проходит через открытый по двум другим входам элемент «И 7 и устанавлйвает «I на единичном выходе триггера 10. ТактО|Вый импульс ТИ открывает элемент «И 5 и устанавливается «1 на единичном выходе триггера 8. В следующем такте через открытый элемент «И 3 проходит импульс только при наличии «1 в младшем разряде регистра /. Таким образом, осуществляется логика преобразования V-кода, т. е. ори наличии «1 на выходе преобразователя в предыдущем такте проходит «1. только с подразряда регистра 2, а при наличии «О на выходе в предыдущем такте - только с подразряда регистра /. При этом быстродействие преобразователя определяется частотой тактовых импульОбщее время преобразования V-кода в -паследовательный двоичный 1код составляет7общ(«-- l)-if,,-i-2/3, число разрядов кода; период следования тактовых импульсов;время задержки двух элементов. Эффективность изобретения заключается в создании более экономичной по количеству использованных элементов схемы, при сохранении максимального быстродействия. Формула изобретения Устройство для преобразования параллельного V-кода в последовательный двоичный кад, содержащее регистр сдвига опережающих подразрядов преобразуемого числа, инфар.мационные входы которого подключены к первой группе входных шин, выход соединел с первым входом первого элемента «И, а тактовый 1вход соединен с шиной отстающей послвдавательности та ктовых имПУЛЬСОВ и тактовым входом регистра сдвига отстающих подразрядов преобразуемого числ.а, инфор.мациовные входы которого Подключены к второй группе входных шин, а выход соединен с первым входом второго эле.мента «И, вторые входы первого и второго элементов «И подключены к шине опережающей последовательности тактовых импульсов, а третьи входы подключены соответственно к единичному и нулевому выходам первого триггера, единичный и нулевой входы которого соединены соответственно с выходами третьего и четвертого элементов «И, первые входы которых подключены соответственно к единичному и нулевому выходам второго триггера, единичный вход которого соединен с выходом пятого элемента «И, выходы первого и Второго элементов «И через элемент «ИЛИ подключены к выходной информационной шине, отличающееся тем. что, с целью уменьшения количества оборудовапия, нулевой вход второго триггера соединен с выходами первого и второго элементов ,«И и первым входо1м пятого элемента «И, второй вход которого соединен с нулевым выходом первого триггера, а третий вход подключен к вто)рым входам первого и второго элементов «И, вторые .входы третьего и четвертого элементов «И подключены к тактовому входу регистра сдвига опережающих подразрядов преобразуемого числа, при это-м

одияичные входы первого и второго триггеров соединены с шиной установки в нуль.

Источники информации, принятые во внимание при экспертизе.

1. Азт. св. № 316086, кл. G06F5/02, 01.10.71.

2.Азт. св. 227705, кл. G 06 F 5/02, 25.09.68.

3.Авт. св. № 196446, кл. G06 F 5/02, 16.05.67 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА БАРКЕРА В ДВОИЧНЫЙ КОД | 1967 |

|

SU196446A1 |

| Оптоэлектронный преобразователь перемещения в код | 1981 |

|

SU1005133A1 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1968 |

|

SU217712A1 |

| Преобразователь напряжения в код | 1980 |

|

SU924853A2 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

Авторы

Даты

1976-07-30—Публикация

1974-09-24—Подача