Сумматор может быть использован в вычислительных устройствах и машинах на ферриттранзисторных ячейках различных типов.

Известны сумматоры параллельного действия на феррит-транзисторных ячейках, действие которых основано на компенсационном или разновременном способе гашения информации (запрета).

Недостаток известных схем заключается в том, что и компенсационный и разновременный режимы запрета (гашения) сушественно отличаются от типового режима работы ферриттранзисторной ячейки «запись - считывание. Это приводит к усложнению схем и снижает надежность работы сумматоров.

Предлагаемый сумматор отличается от известных тем, что в нем шины первого и второго слагаемых подключены, соответственно, ко входам записи первой ячейки и второй и третьей ячеек и соединены со входами, первой схемы «ИЛИ, выход которой связан со входом записи четвертой ячейки и со входом считывания седьмой ячейки. Выход первой ячейки соединен со входом считывания третьей и со входом второй схемы «ИЛИ, на второй вход которой подключен выход второй ячейки. Выход второй схемы «ИЛИ соединен со входом записи седьмой ячейки, выходы третьей и четвертой ячеек подключены ко входам третьей схемы «ИЛИ, выход которой соединен со входом считывания восьмой ячейки. Шина переноса из младшего разряда соединена со входом считывания четвертой и входом записи пятой ячейки, выходы пятой и шестой

ячеек подключены ко входам четвертой схемы «ИЛР, выход которой соединен со входом записи девятой и входом считывания десятой ячейки. Выход седьмой ячейки соединен со входом считывания шестой, а выход девятой

соединен со входом записи десятой.

Это дает возможность повысить надел ;ность и упростить схему сулшатора.

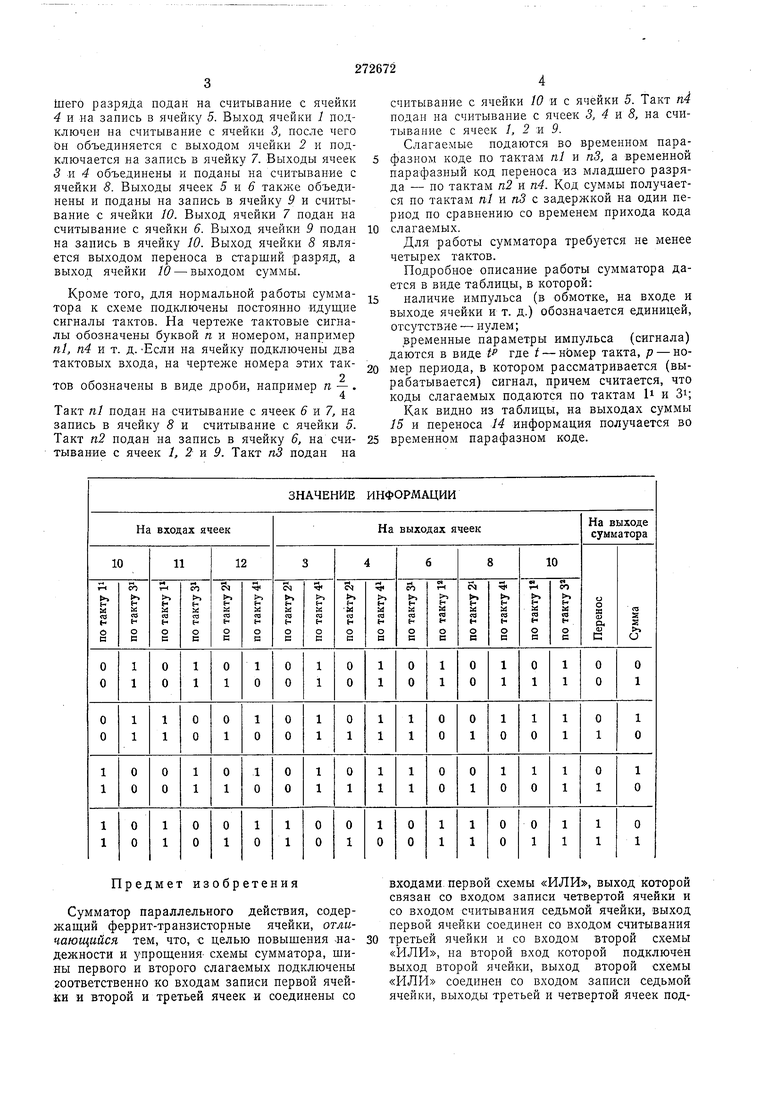

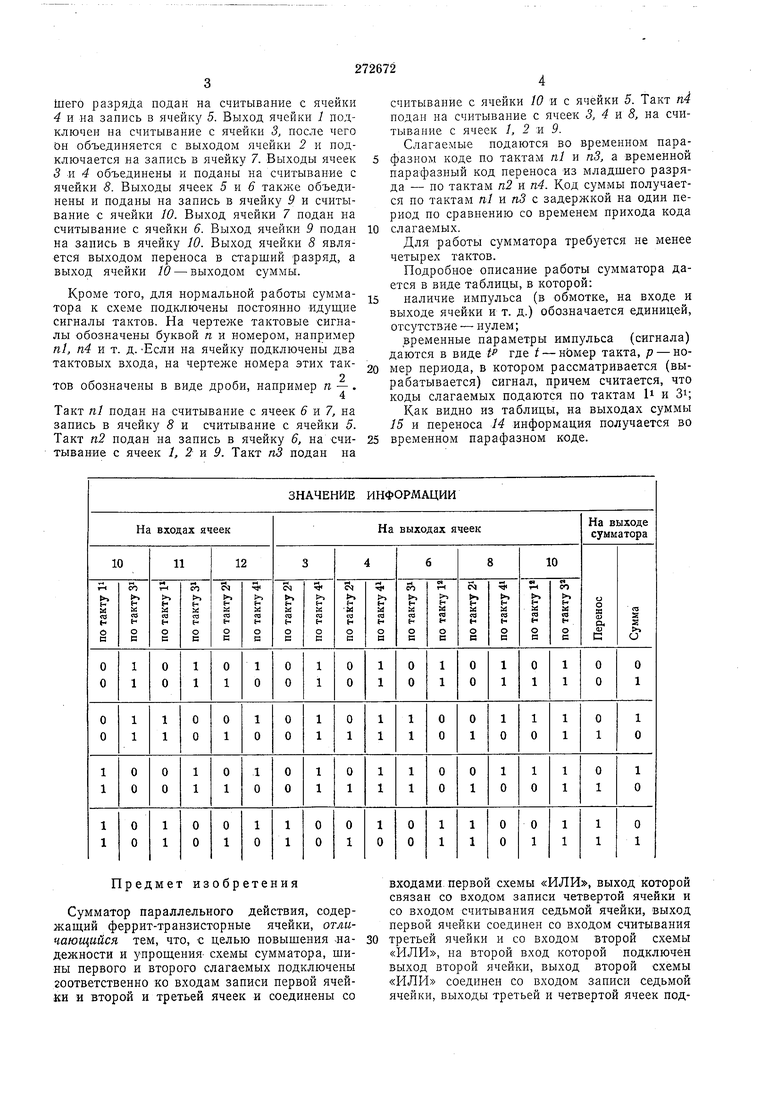

В сумматоре используется временной парафазный код.

Схема устройства приведена на чертеже.

Сум: 1атор на феррит-транзисторных ячейках /-10 имеет три входа (два входа слагаемых 11 м 12 -л в.ход 13 переноса из младшего разряда) и два выхода (переиос в старший

разряд 14 и выход суммы 15).

Ячейки /, 2, 5 и Р предназначены для задержки информации на один такт, ячейки 3, 4, 7 и 10 - для конъюнкций, а ячейки 6 8- для восстановления взаимоннверсного значения рабочих тактов.

Входы слагаемых 11 и 12 подключены на запись в ячейку / и ячейки 2 и 3, соответственно, после чего они объединяются и их дизъюнкцня подается на запись в ячейку 4 и счиШего разряда подан на считывание с ячейки 4 и на занись в ячейку 5. Выход ячейки 1 подключен на считывание с ячейки 3, после чего Он объединяется с выходом ячейки 2 и подключается на запись в ячейку 7. Выходы ячеек 3 и 4 объединены и поданы на считывание с ячейки 8. Выходы ячеек 5 w. 6 объединены и поданы на запись в ячейку 9 и считывание с ячейки 10. Выход ячейки 7 подан на считывание с ячейки 6. Выход ячейки 9 подан на запись в ячейку 10. Выход ячейки 5 является выходом переноса в старший разряд, а выход ячейки 10 - выходом суммы. Кроме того, для нормальной работы сумматора к схеме подключены постоянно идущие сигналы тактов. На чертеже тактовые сигпалы обозначены буквой п и номером, например п1, п4 и т. д. Если на ячейку подключены два тактовых входа, на чертеже номера этих тактов обозначены в виде дроби, например п - , Такт п1 подан на считывание с ячеек б и 7, на запись в ячейку 8 и считывание с ячейки 5. Такт п2 подан на запись в ячейку 6, на считывание с ячеек /, 2 и 9. Такт пЗ подан на считывание с ячейки 10 и с ячейки 5. Такт п4 подан на считывание с ячеек 3, 4 i 8, на считывание с ячеек 1, 2 и 9. Слагаемые подаются во временном парафазном коде по тактам п1 и пЗ, а временной парафазиый код переноса из младшего разряда - по тактам п2 и п4. Код суммы получается по тактам п1 и пЗ с задержкой на один период по сравнению со временем прихода кода слагаемых. Для работы сумматора требуется не менее четырех тактов. Подробное описание работы сумматора дается в виде таблицы, в которой: наличие импульса (в обмотке, на входе и выходе ячейки и т. д.) обозначается единицей, отсутствие - нулем; временные параметры импульса (сигнала) даются в виде tP где t - нЬмер такта, р - номер периода, в котором рассматривается (вырабатывается) сигнал, причем считается, что коды слагаемых подаются по тактам U и ЗЧ Как видно из таблицы, на выходах суммы 15 и переноса 14 информация получается во временном парафазном коде.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU268008A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1973 |

|

SU409220A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Однотактный одноразрядный сумматор на феррит-транзисторных ячейках | 1959 |

|

SU126662A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ НА ФЕРРИТ-ТРАНЗИСТОРНЫХЯЧЕЙКАХ | 1967 |

|

SU203320A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

Предмет изобретения

Сумматор параллельного действия, содержащий феррит-транзисторные ячейки, отличающийся тем, что, с целью повышения -надежности и упрощения- схемы сумматора, щины первого и второго слагаемых подключены гоответственно ко входам записи первой ячейки и второй и третьей ячеек и соединены со

входами первой схемы «ИЛИ, выход которой связан со входом записи четвертой ячейки и со входом считывания седьмой ячейки, выход первой ячейки соединен со входом считывания третьей ячейки и со входом второй схемы «ИЛИ, на второй вход которой подключен выход второй ячейки, выход второй схемы «ИЛИ соединен со входом записи седьмой ячейки, выходы третьей и четвертой ячеек поД ючёны ко входам третьей схемы «ИЛИ, ход которой соединен со входом считываэ восьмой ячейки, шина переноса цз младго разряда соединена со входом считывания вертой и входом записи пятой ячейки, вы1,ы пятой и шестой ячеек подключены ко

X

(перенос)

15 (сумма) входам четвертой схемы «ИЛИ, выход которой соединен со входом записи девятой и входом считывания десятой ячейки, выход седьмой ячейки соединен со входом считывания шестой, а выход девятой соединен со входом записи десятой.

Даты

1970-01-01—Публикация