которого соединен с первым информационньт входом регистра сжатых выходных сигналов, группа выходов которого соединена со второй группой входов блока сравнения и с группой входов су матора по модулю два, первая и вторая группы вых.одов регистра команд соединены соответственно с группой входов.постоянной памяти сжатых данных и с группой входов блока элементов И разрешения и второй групцой информационных входов коммутатора точек, информационный вход устройства соединен с третьим входом блока управления, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, деся тый, одинна,ццатый выходы которого :соединены соответственно с управляющим входом регистра команд, с управляющим входом регистра начальных условий, с управляющим входом коммутатора точек, с управляющим входом блока предварительного анализа, со входом постоянной памяти сжатых данных, с управляющим входом регистра сжатых эталонных сигналов, с управляющим входом регистра сжатых выходных сигналов, с первым и вторым входами блока воспроизведения теста, четвертый вход блока управления соединен с выходом кнопки Пуск, группа выходов коммутатора точек и группа выходов регистра начальных условий образуют контрольную группу выходов устройства третья группа информационных входов коммутатора точек является контрольНой группой входов устройства, причем блок управления содержит два распределителя импульса, генератор импульсов, три триггера, дешифратор, |три элемента И,пять элементов ИЛИ, причем выход генератора импульсов соединен с первыми входами первого и второго элементов И, второй вход и выход первого элемента И соединены соответственно с прямым выходом первого триггера и со входом первого распределителя импульсов, первый - пятый выходы которого соединены соответственно с первыми входами первого четвертого элементов ИЛИ и с шестым выходом блока управления, единичный вход первого триггера соединен с четвертым входом блока управления и нулевым входом третьего триггера, единичный вход и инверсный выход которого соединены соответственно со вторым входом блока управления и с первым входом третьего элемента И,

выход которого соединен с единичным входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, выход которого соединен со входом второго распределителя импульсов, первый - одиннадцатый выходы которого соединены соответственно со вторыми входами первого, второго и третьего элементов ИЛИ, с четвертым выходом блока управления, с первым входом пятого элемента ИЛИ, с восьмым выходом блока управления, со вторыми входами четвертого и пятого элементов ИЛИ, с десятым, одиннадцатым и девятым выходами блока управления, второй вх третьего элемента И соединен с первы входом блока управления и с нулевым входом первого триггера, нулевой вход второго триггера соединен через дещифратор с третьим входом блока управления, вьгходы первого - пятого элементов ИЛИ соединены соответственн с первым,вторым,третьим,седьмым и пятым выходами блока управления, приче блок предварительного анализа содержит регистр, семь счетчиков, три схемы сравнения, делитель частоты, сумматор, узел управления, узел измерения, четыре группы элементов И, группу элементов И-НЕ, три группы элементов ИЛИ, элемент НЕ, два элемента И, три элемента ИЛИ, причем группа выходов регистра соединена с группами информационных входов первого - четвертого счетчиков и с первой группой входов первой схемы сравнения выход которой соединен с первым входом узла управления и с первым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с суммирующим входом пятого счетчика, группа выходов которого соединена с первыми входами соответствующих элемен тов ИЛИ первой группы, с первой группой входов второй схемы сравнения и с первой группой входов третьей схемы сравнения, выход которой соединен с первыми входами элементов И первой группы, вьгходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с первой группой информационных выходов блока предварительного анализа, группа выходов третьего счетчика соединена соответственно с первой группой входов узла управления и с группой информационных входов делителя

частоты, выход которого соединен с суммирующим входом шестого счетчика, группа выходов которого соединена со второй группой входов узла управления, с первыми входами соответствующих элементов И-НЕ группы и первыми входами элементов И второй группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ третьей группы, выходы элементов И-НЕ группы соединены со вторыми входами соответствующих элементов ИЛИ третьей группы, выходы которых соединены с группой входов- сумматора, группа выходов которого соединена с группой информационных входов седьмого счетчика, группа выходов которого соединена с первыми входами соответствующих элементов И третьей группы, со вторыми входами соответствующих элементов ИЛИ первой группы и со второй группой входов второй схемы сравнения, выход которой соединен со вторыми входами элементов И третьей группы, выходы которых соединены со вторыми входами соответствующих элементов ИЛИ второй группы, группа выходов второго счетчика соединена с третьими входами соответствующих элементов ИЛИ второй группы и со второй группой входов первой схемы сравнения, группа выходов первого счетчика соединена со вторыми входами соответствующих элементов И первой группы и со второй группой входов третьей схемы сравнения, вы|ходы элементов ИЛИ первой группы соединены с первыми входами соответству кндих элементов И четвертой группы, выходы которых соединены со второй группой информационных выходов блока предварительного элемента, вход узла измерения соединен со вторым контроль1ным входом блока- предварительного анализа, вход-выход узла измерения |соеданены с первым входом первого |элемента И и через элемент НЕ с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого элемента И и со вторым входом узла управления, выход первого элемента ИЛИ соединен с вычитающим входом четвертого счетчика, выход переноса которого соединен с третьим входом узла управления и третьим управляющим выходом блока предварительного анализа, выход переноса третьего счетчика соединен.с четвертым входом узла управления, выход переноса первого счетчика соединен с пятым входом узла управления, выход переноса шестого счетчика соединен с шестым входом узла управления, управляющий вход блока предварительногь анализа соединен с седьмым входом узла управления, группа информационных входов регистра является группой информационных входов блока предварительного анализа, первый контрольный вход блока предварительного анализа соединен с первым входом первого элемента И, первый - восемнадцатый выходы узла управления соединены соответственно с первым управляющим выходом блока предварительного анализа, со вторым управляющим выходом блока предварительного анализа и вторым входом первого элемента И, со входами разрешения записи третьего и четвертого счетчиков, с суммирую- , гщм входом третьего счетчика, со разрешения записи первого счетчика, первым входом второго элемента ИЛИ и вторым входом первого элемента ИЛИ, с вычитающим входом первого счетчика и третьими входами элементов И первой группы, с вычитающим входом третьего счетчика, со вто рыми входами элементов И второй , со вторыми входами элементов ИНЕ группы, со входом разрешения записи седьмого счетчика, с вычитающим входом седьмого счетчика, со входом разрешения записи регистра, со входом разрешения записи второго счетчика и вторым входом второго эле мента ИЛИ, с суммирующим входом второго счетчика, с вычитающим входом шестого счетчика и суммирующим входой седьмого счетчика и третьими входами элементов И третьей группы, со вторым входом второго элемента И, с управляющим входом делителя частоты, со вторыми входами элементов И четвертой группы и четвертым управляющим выходом блока предварительного анализа.

2, Устройство по п. 1, отличающееся тем, что узел управления блока предварительного анализа содержит регистр сдвига, четьфе распределителя импульсов, два дешифратора, десять триггеров, семнадцать элементов И, пять элементов ИЛИ, два генератора импульсов, причем выход первого генератора импульсов соединен с первыми входами первого, второго.

трьтьегс.) н чс I icpTiifo элементов И, выход Я1(рого генератора импульсов соединен с синхронизирующим входом первого триггера и первыми входами пятого - девятого элементов И, второй вход и выход пятого элемента И соединены соответственно с прямым выходом второго триггера и со входом первого распределителя импульсов, первьгй, второй, третий, четвертый выходы которого соединены соответственно с первым входом первого элемента ИЛИ, с первым входом второго элемента ИЛИ, с единичным входом третьего триггера, с нулевым входом второго триггера и первым входом третьего элемента ИЛИ, выход которого соединен с единичным входом четвертого триггера, выход которого соединен со вторым входом шестого элемента И, выход которого соединен со входом второго распределителя импульсов, первый и второй выходы которого соединены соответственно с пятым выходом узла и с единичным входом пятого триггера, выход которого соединен со вторым входом второго элемента И, выход которого соединен :С шестым выходом узла, первый вход десятого элемента И соединен со вторым входом блока, первым входом четвертого элемента ИЛИ, информационным входом первого триггера, первым входом одиннадцатого элемента И и еди:ничньм входом швстого триггера, прямой выход которого соединен со вторы входом седьмого элемента И, выход которого соединен со входом третьего .распределителя, первый, второй, третий, четвертый, пятый, шестой, седьмой выходы которого соединены соотвественно с семнадцатым выходом узла и вторым входом второго элемента ИЛИ с единичным входом седьмого триггера с первыми входами двенадцатого и тринадцатого элементов И, с десятым выходом узла, с единичным входом восьмого триггера, с первым входом четырнадцатого элемента И, с первым входом патнадцатого элемента И, выход KOTOрого соединен со вторым входом третьего элемента ИЛИ, нулевым вход ом шее то(Го триггера и первым входом пятого элемента ИЛИ, выход которого соединен с восемнадцатым выходом узла, нулевой вход восьмого триггера соединен о шестым входом уэла, а прямой выход со вторым входом третьего элемента И выход которого соединен с пятнадца1

тым выходом узла, нулевой вход седьмого триггера соединен с четвертым входом узла, а прямой выход - со втог рым входом четвертого элемента И, выход которого соединен с седьмым выходом узла, нулевой вход третьего триггера соединен через первый дешифратор с первой группой входов узла, а прямой выход - со вторьм входом первого элемента И, выход которого соединен с четвертым выходом узла, вторые входы четырнадцатого и пятнадцатого элементов И соединены через второй дешифратор со второй группой входов узла, выход четьфнадцатого элемента И соединен с одиннадцатым выходом узла, второй вход четвертого элемента ИЖ соединен с третьим входом узла, третьим входом второго элемента ИЛИ и входом регистра сдвига, первый выход которого соединен с первым входом шестнадцатого элемента И, шестнадцатым выходом узла и вторым входом десятого элемента И, второй выход - с первым входом семнадцатого элемента И, вторьм входом одиннадцатого элемента И и первым выходом узла, а третий выход - со вторым выходом узла, второй вход семнадцатого элемента И соединен с седьмым входом узла и вторым входом шестнадцатого элемента И, а выход - с единичным входом девятого триггера, прямой выход которого соединен со вторым входом восьмого элемента И, выход которого соединен со входом четвертого распределителя импульсов, первый и второй выходы которого соединены со ответственно с тринадцатым выходом узла и со вторым входом первого элемента ИЛИ,а третий выход - с нулевым входом девятого триггера и единичным входом десятого триггера,нулевой вход и прямой выход которого соединены соответственно с первым входом узла и со вторым входом девятого элемента И, выход которого соединен с четырнадцатым выходом узла, прямой выход первого триггера соединен со вторьм входом двенадцатого элемента И, выход которого соединен с восьмым выходом узла, инверсный выход первого триггера соединен с третьим входом четырнадцатого элемента И и вторым входом тринадцатого элемента И, выход которого соединен с девятым выходом узла, нулевой вход пятого триггера соединен с пятым входом узла, выход шестнадцатого элемента И соединен с единичным входом второго триггера, выход десятого элемента И соединен со вторым входом пятого элемента ИЛИ, .выход второго элемента ИЛИ соединен с третьим выходом узла, выход первого элемента ИЛИ соединен с двенадцатым выходом узла, выход четвертого элемента ИЛИ соединен с нулевым входом четвертого триггера, выход одиннадцатого элемента И соединен с третьим входом пятого элемента ИЛИ. 3. Устройство по п, 1, отличающееся тем, что узел измерения блока предварительного аналиэа содержит эталонный резистор, операционный усилитель, двуханодный стабилитрон и источник опорного напряжения, причем выход источника опорного напряжения соединен через эталонный резистор с первым выводом дву анодного стабилитрона, со входом узла и с инвертирующим входом операционного усилителя, выход которого соединен со вторым вьтодом двуханодного стабилитрона и со входом-выходо узла. А. Устройствб по п. 1, отлич ющееся тем, что блок воспроизведения теста содержит два регистра сумматор по модулю два, два счетчика распределитель импульсов, два триггера, группу элементов И, два элемента И, три элемента ИЖ и генератор импульсов, причем выход генератора импульсов соединен с первым входом первого элемента И, выход ко торого соединен с вычитаннцим входом первого счетчика, управляющими входа ми первого и второго регистров, информационный вход второго регистра 51 соединен с выходом сумматора по модулю два, первый вход которого соединен с вькодом первого регистра, группа информационных входов которого соединена с третьей группой входов блока, первый вход второгоэлемента И соединен с .первым входом блока, а выход - со входами разрешения записи первого регистра, второго счетчика и первого счетчика, выход переноса которого соединен с нулевым входом первого триггера, тактовым входом распределителя импульсов, установочным входом второго регистра и вычитающим входом второго счетчика, выход переноса которого соединен с установочным входом распределителя импульсов и единичным входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, группа вьгходов второго регистра соединена со вторым входом сумматора по модулю два и первыми входами соответствующих элементов И группы, вторые входы которых подключены к соответствующим выходам распределителя импульсов, а выходы K соответствующим группам входов первого, второго и третьего элементов ИЛИ, выходы которьк соединены соответственно с первым, вторым и третьий выходами блока, нулевой вход второго триггера соединен со вторым входом блока и единичным входом первого триггера, прямой выход которого соединен со вторым входом первого элемента И, группы информационных входов первого и второго счетчиков соединены соответственно с первой и второй группами входов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля электрических цепей | 1983 |

|

SU1112322A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля полупроводниковых приборов | 1989 |

|

SU1705783A1 |

1. УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ПОИСКА ДЕФЕКТОВ В ЛОГИЧЕСКИХ БЛОКАХ, содержащее блок памяти, блок выбора адреса, дискриминатор выходных сигналов, блок сравнения, и блок управления, первый и второй выходы которого соединены соответственно со входом блока выбора адреса и управляюпщм входом блока памяти, информационный и адресный входы которого соединены соответственно с информационным входом устройства и выходом блока выбора адреса, отличающееся тем, что, с целью расширения области применения устройства, в него введены регистр команд, постоянная память сжатых данных, коммутатор точек, регистр начальных условий, регистр сжатых эталонных сигналов, регистр сжатых выходных сигналов, сумматор по модулю два, блок воспроизведения, теста, блок элементов И разрешения кнопка Пуск и блок предварительного анализа, причем первый, второй, третий, четвертый управляющие выход блока предварительного анализа соединены соответственно с первым и вторым информационными входами коммутатора точек, с первым входом блока управления, со вторым входом блока управления и синхровходом блока памяти, первая, вторая и третья группы выходов которого соединены соответственно с группами информационных входов регистра начальных условий, регистра команд и блока предварительного анализа, первая и вторая группы информационных выходов которого соединены соответственно с первыми группами информационных входов коммутатора точек и блока памяти, вторая группа информационных входов которого соеди(Л нена с группой выходов блока элементов И разрешения, первый вход которого соединен с выходом блока сравнения, первая группа входов которого о соединена с группой выходов регистра сжатых эталонных сигналов, группа информационных входов которого соединена с первой группой выходов постоянной памяти сжатых данных, вторая, 00 4 третья и четвертая группы выходов которого соединены соответственно с СЛ первой, второй и третьей группами входов блока воспроизведения теста, первый, второй и третий выходы которого соединены соответственно с третьим, четвертым и пятым информационными входами коммутатора точек, первьй, второй и третий выходы которого соединены соответственно с первым и вторым контрольными входами блока предваритепьного анализа и со входом дискриминатора вькодных сигналов, выход которого соединен со входом сумматора по модулю два, выход

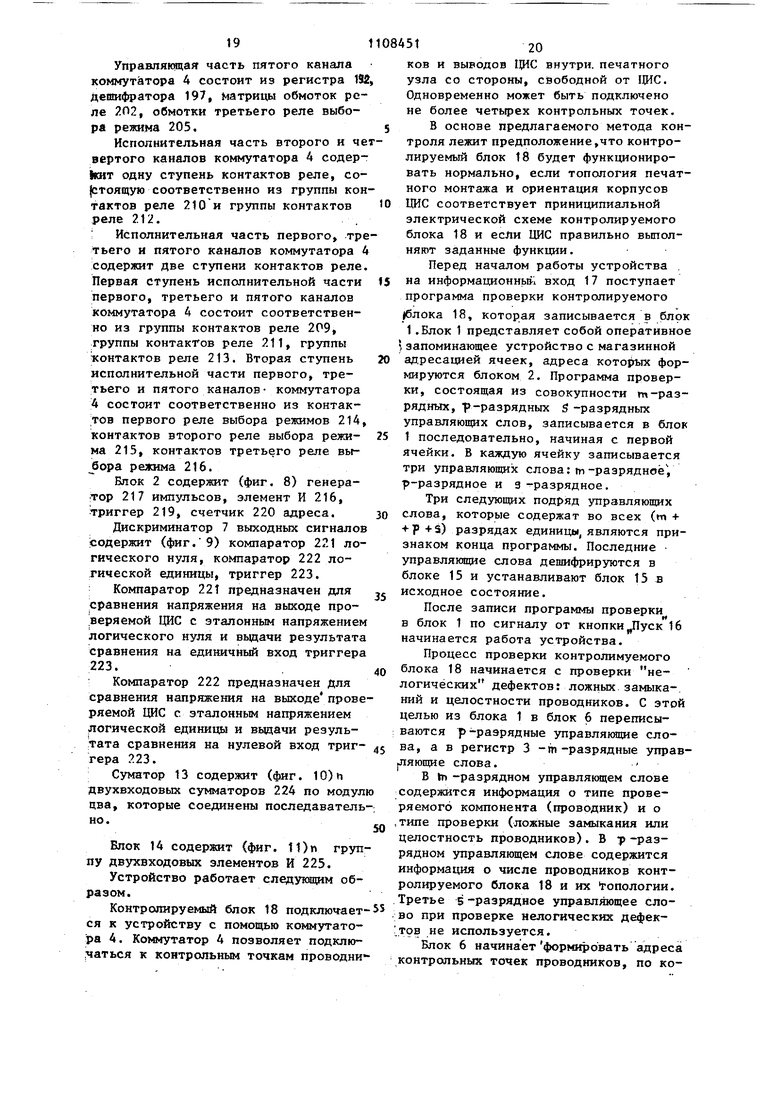

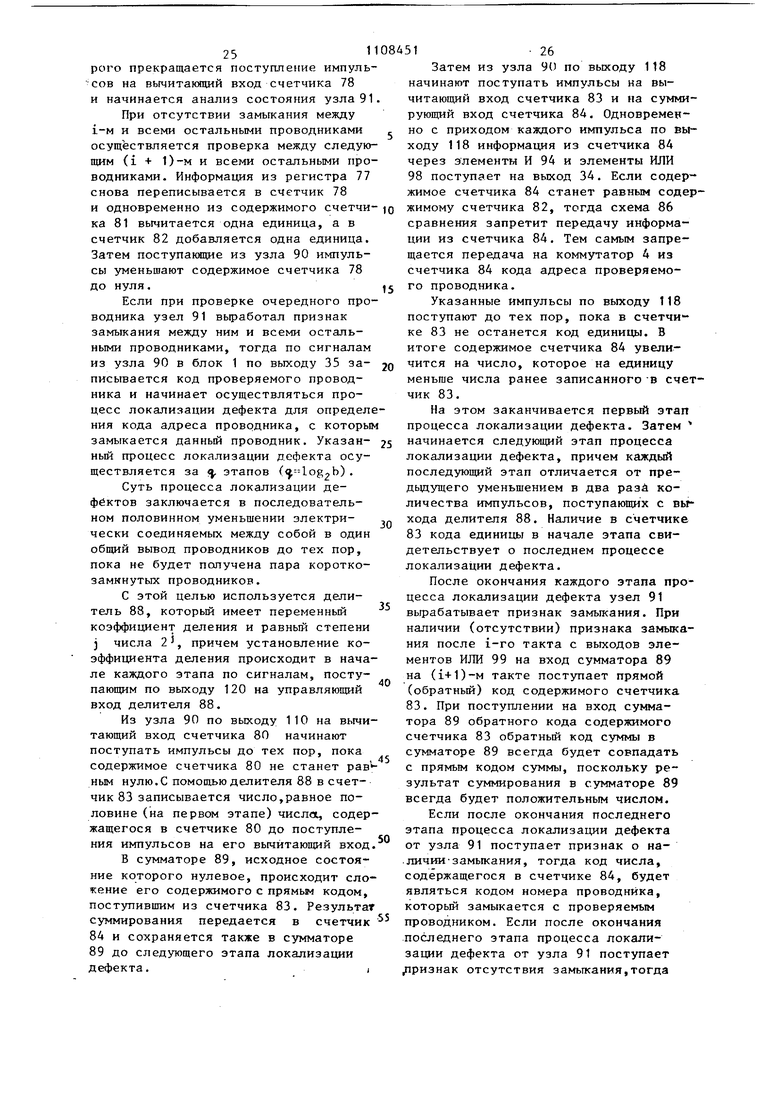

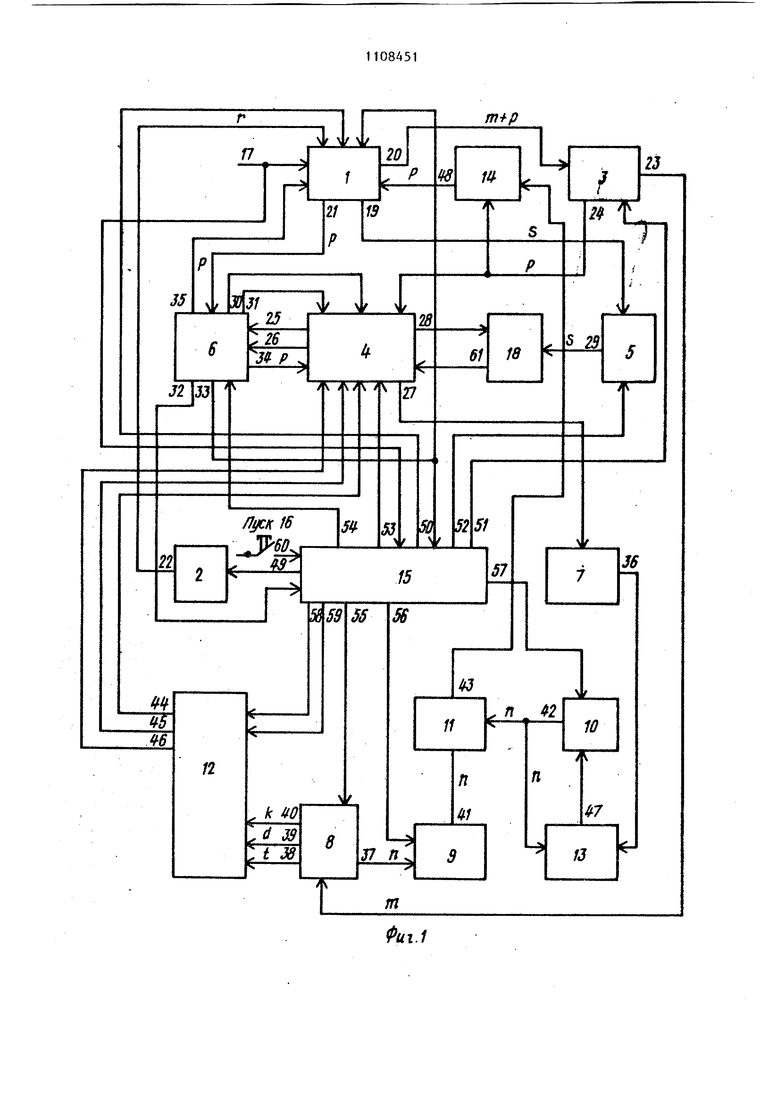

Изобретение относится к вычислитель ной технике и может быть использовано для производственной проверки после сборки печатных узлов, содержащих цифровые интегральные схемы (ЦИС). Известны устройства для тестового контроля логических блоков, которые содержат эталонный блок, схемы сравнения, коммутатор, регистр контролируемых параметров, блок формирования временной задержки, блок индикации и вывода, блок управления и блок ввода D j. Недостаток этих устройств состоит в ограниченной области их применения. Наиболее близким к предлагаемому является устройство для автоматического контроля цифровых объектов, содержащее генератор тестов блок формирования входных сигналов, эталонный блок, дискриминатор выходных сигналов, блок сравнения, блокблокировки, счетчик тактов, блок управления, бло памяти, блок ввода, блок .выбора адре са, причем первый, второй, третий и четвертый выходы блока управления соединены соответственно со входом генератора тестов, с первым входом блока формирования входных сигналов с первым входом блока блокировки, со входом счетчика тактов, первый выход генератора тестов соединен со вт рым входом блока формирования входны сигналов, третий вход которого соединен с первым выходом блока блокировки, выход блока формирования вход ных сигналов соединен со входом эталонного блока и с выходом устройства вход устройства соединен со входом дискриминатора выходных сигналов, вы ход которого соединен с первым входом блока сравнения, второй и третий входы которого соединены соответственно с выходом эталонного блока, со вторым выходом блока блокировки, выход блока сравнения соединен со входом блока управления, пятый и шестой выходы которого соединены соответственно с первьм входом блока выбора адреса и с первым входом блок памяти, первый, второй и третий выходы которого соединены соответствен но со вторым входом блока выбора адреса, со вторым входом генератора тестов, со вторым входом блока блокировки, выход блока ввода соединен со вторым входом блока памяти, выход счетчика тактов соединен с третьим входом блока выбора адреса, выход которого соединен с третьим входом блока памяти 2. Недост ком этого устройства, вопервых,является ограниченная область применения, поскольку проверка контролируемого объекта производится в номинальном режиме и наличие некоторых типов неисправностей, например дефектов шин питания ЦИС, приводит к повреждению ЦИС при подаче н них номинального напряжения питания Второй недостаток известных устройств состоит в низкой глубине поиска дефектов, вследствие чего невозможно установить дефект с точностью до корпуса ЦИС. Третий недостаток известных устройств состоит в их низкой надежности, поскольку наличие эталонного блока порождает проблемы, связанные с его аттестацией и сохранностью. необходимостью внесения в него изменений и т.д. Целью изобретения является расширение области применения устройства, путем обеспечения нераэрушающего характера проверки контролируемого блока, увеличения глубины поиска дефектов и уменьшения емкости памяти устройства. Поставленная цель достигается тем, что в устройство, содержащее блок памяти, блок выбора адреса, дискриминатору выходных сигналов, блок сравнения и блок управления, первый и второй выходы которого соединены со ответственно со входом блока выбора адреса и управляющим входом блока памяти, информационный и адресный входы которого соединены соответственно с информационным входом устройства и выходом блока выбора адреса, введены регистр команд, постоянная память сжатых данных, коммутатор точек, регистр начальных условий, регистр сжатых эталонных сигналов, регистр сжатых выходных сигналов, сумматор по модулю два, блок воспроизведения теста, блок элементов И разрешения, кнопка Пуск и блок предварительного анализа, причем первый, второй, третий, четвертьй управляющие выходы блока предварительного анализа соединены соответственно с первым и вторым информационными входами коммутатора точек, с первым входом блока управления, со вторым входом блока управления и синхров7 :одом блока памяти, первая, вторая и третья группы выходов которого соединены соответственно с группами информационных входов регистра начальных условий, регистра команд и блока предварительного анализа, первая и вторая группы информационных выходов которого соединены соответственно с первыми группами информационных входов коммутатора точек и блока памяти, вторая группа информационных входов которого соединена с группой выходов блока элементов И разрешения, первый вход которого соединен с выходом блока сравнения, первая группа входов которого соединена с группой выходов регистра сжатых эталонных си г налов, группа информационных входов которого соединена с первой группой выходов постоянной памяти сжатых данных, вторая, третья и четвертая группы выходов которого соединены соответственно с первой, второй и третьей группами входов блока воспроизведения теста, первый, второй и третий вмхс-ДЫ которого соединены соответственно с третьим, четвертым н пятым информационными входами коммутатора точек, первый, второй и третий выходы которого соединены соответственно с первым и вторым контрольными входами блока предварительного анализа и со входом дискриминатора выходных сигналов, выход которого соединен со входом сумматора по модулю два, выход которого соединен с первым информацион ным входом регистра сжатых выходных сигналов, группа выходов которого соединена со второй группой входов блока сравнения и с группой входов сумматора по модулю два, первая и вторая группы выходов регистра коман соединены соответственно с группой ВХОДОВпостоянного запоминающего уст ройства сжатых данных и с группой вх дов блока элементов И разрешения и второй группой информационных входов коммутатора точек, информационный вход устройства соединен с третьим входом блока управления, третий, чет вертьй, пятый, шестой, седьмой, вось мой, девятый, десятый, одиннадцатый выходы которого соединены соответственно с управляющим входом регистр команд, с управляющим входом регистр начальных условий, с управляющим вхо дом коммутатора точек, с управляющим входом блока предварительного анализа, со входом постоянной памяти сжатых данных, с управляющим входом регистра сжатых эталонных сигналов, с управляющим входом регистра 1сжатьк выходных сигналов, с первым и вторым входами блока воспроизведения теста, четвертый вход блока упра ления соединен с выходом кнопки Пуск, группа выходов коммутатора точек и группа выходов регистра начальных условий образуют контрольную группу выходов устройства, третья группа информационных входов коммутатора точек является контрольной группой входов устройства, причем блок управления содержит три триггер два распределителя импульсов, дешифратор, три элемента И, пять элементов ИЛИ и генератор импульсов, причем выход генератора импульсов соеди нен с первыми входами первого и второго элементов И, второй вход и вьжо 1 316 первого элемента И соединены соответственно с прямым выходом первого триггера и со входом первого распределителя импульсов, первый - пятый выходы которого соединены соответственно с первыми входами первого четвертого элементов ИЛИц с шестым выходом блока управления, единичный вход первого триггера соединен с четвертым входом блока управления и нулевым входом третьего триггера, единичный вход и инверсный выход которого соединены соответственно со вторым входом блока управления и с первым входом третьего элемента И, выход которого сорялмеи с единичным входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, выход которого соединен .со входом второго распределителя импульсов, первый - одиннадцатый выходы которого соединены соответственно со вторыми входами первого, второго и третьего элементов ИЛИ, с четвертым выходом блока управления, с первым входом пятого элемента ИЛИ, с восьмым выходом блока управления, со вторыми входами четвертого и пятого элементов ИЛИ, с десятым, одиннадцатым и девятым выходами блока управления, второй вход третьего элемента И соединен с первым входом блока управления и с нулевым входом первого триггера, нулевой вход второго триггера соединен через дешифратор с третьим входом блока управления, выходы первого - пятого элементов ИЛИ соединены соответственно с первым, вторым, третьим, седьмым и пятым выходами блока управления, причем блок предварительного анализа содержит регистр, семь счетчиков, три схемы сравнения, делитель частоты, сумматор, узел управления, узел измерения,четыре группы элементов И, группу элементов И-НЕ, три группы элементов ИЛИ, элемент НЕ, два элемента И, три элемента ИЛИ, причем группа выходов регистра соединена с группами информационных входов первого - четвертого счетчиков и с первой группой входов первой схемы сравнения, выход которой соединен с первым входом узла управления и с первым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с суммирующим входом пятого счетчика,группа выходов которого соединена с первыми входами соответствующих элементов ИЛИ первой группы, с первой группой входов второй схемы сравнения и с первой группой входов третье схемы сравнения, выход которой соединен с первыми входами элементов И первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с первой груп пой информациойных вькодов блока пре варительного анализа, группа выходов третьего счетчика соединена соответственно с первой группой входов узла управления и с группой информационны входов делителя частоты, выход кото рого соединен с суммирующим входом шестого счетчика, группа выходов которого соединена со второй группой входов узла управления, с первыми входами соответствующих элементов И-НЕ группы и. первыми входами элемен тов И второй группы, выходы которых соединены с первыми входами соотвеаствующих элементов ИЛИ третьей группы, вькоды элементов И-НЕ группы coe динены со вторыми входами соответствующих элементов ИЛИ третьей группы, выходы которых соединены с группой входов сумматора, группа выходов которого соединена с группой информационных входов седьмого счетчика, группа выходов которого соединена с первыми входами соответствующих элементов И третьей группы, со вторыми входами соответствующих элементов ИЛИ первой группы и со второй группой входов второй схемы сравнения, выход которой соединен со вторыми входами элементов И третьей группы, выходы которых соединены со вторыми входами соответствующих элементов ИЛИ второй группы, группа выходо второго счетчика соединена с третьими входами соответствующих элементов. ИЛИ второй группы и со второй грзшпой входой первой схемы сравнения, группа выходов первого счетчика соединена со вторыми входами соответствующих элементов И первой группы и со второй группой входов третьей схемы сравнения, выходы элементов ИЛИ первой группы соединены с первыми входами соответствующих элементов И четвертой группы, выходы ко :торых соединены со второй группой информационных выходов блока предварительного анализа, вход узла измерения соединен со вторым контрольным входом блока предварительного 1 51 8 анализа, вход-выход узла измерения соединены с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого элемента И и со вторым входом узла управления, выход первого элемента ИЛИ соединен с вьгчитающим входом четвертого счетчика, выход переноса которого соединен с третьим входом узла управления и третьим управляющим выходом блока предварительного анализа, выход переноса третьего счетчика соединен с четвертым входом узла управления, выход переноса первого счетчика соединен с пятым входом узла управления, выход переноса шестого счетчика соединен с шестым входом узла управления, управляющий вход блока предварительного анализа соединен с седьмым входом узла управления группа информационных входов регистра является группой информационных входов блока предварительного анализа, первый контрольный вход блока предварительного анализа соединен с первым входом первого элемента И, первый-восемнадцатый выходы узла управления соединены соответственно с первым управляющим выходом блока предварительного анализа, со вторым управляющим выходом блока предварительного анализа и вторым входом первого элемента И, со входами разрешения записи третьего и четвертого счетчиков, с с -ммирующим входом третьего счетчика, со входом разрешения записи первого счетчика, первым входом второго элемента ИЛИ и вторым входом первого элемента ИЛИ, с вычитающим входом первого счетчика и третьими входами элементов И первой группы, с вычитающим входом третьего счетчика, со вторыми входами элементов И второй группы, со вторыми входами элементов И-НЕ группы, со входом разрешения записи седьмого счетчика, с вычитающим входом седьмого счетчика, со входом разрешения записи регистра, со входом разрешения записи второго счетчика и вторым входом второго элемента ИЛИ, с суммирукяцим входом второго счетчика, с вычитающим входом шестого счетчика, и суммируннцим входом седьмого счетчика и третьими входами элементов И третьей группы, со вторым входом второго элемента И, с управляюпщм входом делителя частоты, со вторыми входами элементов И четвертой группы и четвертым управляющим выходом блока предварительного анализа. Узел управления блока предварительного анализа содержит регистр сдвига, четыре распределителя импул сов, два дешифратора, десять тригге |РОВ, семнадцать элементов И, пять элементов ИЛИ, два генератора импульсов, причем выход первого генератора импульсов соединен с первыми входами первого, второго, третьего, и четвертого элементов И, выход ВТО рого генератора импульсов соединен с синхронизирующим входом первого триггера и первыми входами пятого девятого элементов И, второй вход и выход пятого элемента И соединены соответственно с прякп;1м выходом второго триггера и со входом первого распределителя импульсов, первый, второй, третий, четвертый выходы которого соединены соответственно с первым входом первого элемента ИЛИ, с первым входом второго элемента ИЛИ с единичным входом третьего триггера с нулевым входом второго триггера, и первым входом третьего элемента ИЛИ, выход которого соединен с едини ным входом четвертого триггера, выход которого соединен со вторым входом шестого элемента И, выход которого соединен со входом второго распределителя импульсов, первый и второй выходы которого соединены соответственно с пятым выходом узла и с единичным входом пятого триггера, выход которого соединен со вторым входом второго элемента И, выход которого соединен с шестым выходом узл первый вход десятого элемента И соединен со вторым входом блока, первым входом четвертого элемента ИЛИ, информационным входом первого триггера первым входом одиннадцатого элемента И и единичным входом шестого триггер прямой выход которого соединен со вт рым входом седьмого элемента И, выхо которого соединен со входом третьего распределителя импульсов, первый, вт рой, третий, четвертый, пятый, шестой, седьмой выходы которого соедине ны соответственно с семнадцатым выходом узла и вторым входом второго элемента И.ПИ, с единичным входом сед мого триггера, с первыми входами две надцатого и тринадцатого элементов И, с десятым выходом узла, с единичным входом восьмого триггера, с первым входом четырнадцатого элемента И, с первым входом пятнадцатого элемена И, выход которого соединен со втоым входом третьего элемента ИШТ, нулевым входом шестого триггера и первым входом пятого элемента 1ШИ, выход которого соединен с восеменадцатым выходом узла, нулевой вход восьмого триггера соединен с шестым входом узла, а прямой выход - со вторым входом третьего элемента И, выход которого соединен со пятнадцатым выходом узла,нулевой вход седьмого триггера соединено четвертым входом узла, а прямой выход - со вторым входом четвертого элемента И, выход которого соединен с седьмым выходом узла, нулевой вход третьего триггера соединен через первый дешифратор с первой группой входов узла, а прямой выход - со вторым входом первого элемента И, выход которого соединен с четвертым выходом узла, вторые входь( четырнадцатого и пятнадцатого элементов И соединены через второй дешифратор со второй группой входов узла, выход четьфнадцатого элемента И соединен с одиннадцатым выходом узла, второй вход четвертого элемента ИЛИ соединен с третьим входом узла, третьим входом второго элемента ИЛИ и входом регистра сдвига, первый выход которого соединен с первым входом шестнадцатого элемента И, шестнадцатым выходом узла и вторым входом десятого элемента И, второй выход с первым входом семнадцатого элемента И, вторым входом одиннадцатого элемента И и первым выходом узла, а третий выход - со вторым выходом узла, второй вход семнадцатого элемента И соединен с седьмым входом узла и вторым входом шестнадцатого элемента И, а выход - с единичным входом девятого триггера, прямой выход которого соединен со вторым входом восьмого элемента И, выход которого соединен со входом четвертого распределителя импульсов, первый и второй выходы которого соединены соответственно с тринадцатым выходом узла и со вторым входом первого элемента ИЛИ, а третий выход - с нулевым входом девятого триггера и единичным входом десятого триггера, нулевой вход и прямой выход которого соединены соответственно с первым входом узла и со вторым входом девятого элемента И, выход которого соединен с четырнадцатым выходом узла, прямой выход первого триггера соединен со вторым входом двенадцатого элемента И, выход которого соединен с восьмым выходом узла, инверсный « вькод первого триггера соединен с третьим входом четырнадцатого элемен та И и вторым входом тринадцатого элемента И, выход которого соединен г девятым выходом узла, нулевой вход плтого триггера соединен с пятым вхо дом узла, выход шестнадцатого элемен та И соединен с единичным входом второго триггера, выход десятого элемента И соединен со вторым входом пятого элемента ИЛИ, выход второго элемента ИЛИ соединен с третьим выходом узла, выход первого элемента ИЛИ сое динен с двенадцатым выходом узла, вы ход четвертого элемента ИЛИ соединен с нулевым входом четвертого триггера вьйсод одиннадцатого элемента И соединен с третьим входом пятого элемен та ИЛИ. Узел измерения блока предваритель ного анализа содержит эталонный рези стор, операционный усилитель, двуханодный стабилитрон и источник опорного напряжения, причем выход источника опорного напряжения соединен че рез эталонный резистор с первым выводом двуханодного стабилитрона, со входом узла и с инвертирующим входом операционного усилителя, выход которого соединен со вторым выводом двух анодного стабилитрона и со входомвыходом узла. Блок воспроизведения теста содерж два регистра, сумматор по модулю два два счетчика, распределитель импульсов, два триггера, группу элементов И, два элемента И, три элемента ИЛИ и генератор импульсов, причем выход генератор импульсов соединен с первым входом первого элемента И, выход которого соединен с вычитающим входом первого счетчика, управляющими входами первого и второго регистров, информационный вход второго регистра соединен с выходом сумматора по модулю два, первый вход которого соединен с выходом первого регистра, группа информационных входов которого соединена с третьей группой входов блока, первый вход 1 5112 второго элемента И соединен с первым входом блока, а выход - со входами разрешения записи первого регистра, второго счетчика и первого счетчика, выход переноса которого соединен с нулевым входом первого триггера, тактовым входом распределителя импульсов, установочным входом второго регистра и вычитающим входом второго счетчика, выход переноса которого соединен с установочным входом распределителя импульсов и единичным входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, группа выходов второго регистра соединена со вторым входом сумматора по модулю два и первыми входами соответствующих элементов И группы, вторые входы которых подключены к соответствующим выходам распределителя импульсов, а выходы к соответствующим группам входов первого, второго и третьего элементов ИЛИ,выходы которых соединены соответственно с первым,вторьми третьим выходами блока, нулевой вход второго триггера соединен со вторым входом блока и единичным входом первого триггера, прямой выход которого соединен со вторым входом первого элемента И, группы информационных входов первого и второго счетчиков соединены соответственно с первой и второй группами входов блока. На фиг. 1 представлена блок-схема предлагаемого устройства-, на фиг. 2 схема блока управления; на фиг. 3-11 представлены функциональные схемы блока предварительного анализа, узла управления блока предварительного анализа, узла измерения блока предварительного анализа, блока воспроизведения теста, коммутатора точек, блока выбора адреса, дискриминатора выходных сигналов, сумматора по модулю два, блока элементов И разрешения. Устройство содержит (фиг. 1) блок 1 памяти, блок 2 выбора адреса, регистр 3 команд, коммутатор 4 точек, регистр 5 начальных условий, блок 6 предварительного анализа, дискриминатор 7 выходных сигналов, постояннун память (ПЗУ) 8 сжатых данных, регистр 9 сжатых эталонных сигналов, регистр 10 сжатых выходных сигналов, блок 11 сравнения, блок 12 воспроизведения теста, сумматор 13 по модулю два, блок 14 разрешения, блок 15

управления, кнопку информационный вход 17 устройства, контролируемый блок 18, а также следующие соединения: первую 19, вторую 20 и третью 21 группы информационных выходов блока 1, выход 22 блока 2, первую группу выходов 23 регистра 3, вторую группу выходов 24 регистра 3, первый вьпсод 25, второй выход 26, третий выход 27 и группу выходов 28 коммутатора 4 точек, группу выходов 29 регистра 5, первый 30, второй 31, третий 32 и четвертый 33 управляющие выходы блока 6, первую 34 и вторую 35 группы информационных выходов блока 6, выход 36 дискриминатора 7 выходных сигналов, первую группу выходов 37 ПЗУ 8, вторую группу выходов 38 ПЗУ 8, третью группу выходов 39 ПЗУ 8, четвертую группу выходов 40 ПЗУ 8, группу выходов 41 регистра 9, группу выходов 42 регистра 10, выход 43 блока 11, первый выход 44, второй выход 45 и третий выход 46 блока 12, выход 47 сумматора 13, группу выходов 48 блока 14, первый выход 49, второй выход 50, третий выход 51, четвертый выход 52, пятый выход 53, шестой выход 54, седьмой выход 55, восьмой выход 56, девятый выход 57, десятый выход 58 и одиннадцатый выход 59 блока 15, выход 60 кнопки ус к 16, группа выходов 61 контролируемого блока 18. Группа выходов 28 и 29 образуют контрольную группу выходов устройства.

Блок 2 предназначен для формирования адреса, по которому в блоке 1 записана программа проверки в течение одного цикла работы устройства.

Регистр 3 предназначен для хранения информации о программе проверки в течение одного цикла работы устройства.

Коммутатор 4 точек предназначен для подключения контрольных точек контролируемого блока 18 в течение одного цикла работы устройства. При проверке нелогических дефектов коммутатор 4 подключает одновременно две контрольные точки контролируемого блока 18. При проверке логических элементов контролируемого блока 18 коммутатор 4 подключает одновременно не более трех входов и одного выхода проверяемой ЦИС.

Регистр 5 предназначен для хранения логических констант начальных

условий при проверке ЦИС контролируемого блока 18.

Блок 6 предназначен для проверки в микрорежиме нелогических дефектов контролируемого блока 18.

Дискриминатор 7 выходНьпс сигналов предназначен для анализа выходнь потенциалов контролируемого блока 18 на соответствие их потенциалам логических значений 1 и О.

ПЗУ 8 предназначено для хранения сжатых входных и сжатых эталонных сигналов отдельных логических элементов.

Регистр 9 предназначен для хранения сжатых эталонных сигналов в течение времени проверки одной ЦИС контролируемого блока 18.

Регистр 10 и сумматор 13 предназначены для сжатия сигналов, поступающих в процессе проверки с выходов ЦИС контролируемого блока 18.

Блок 11 предназначен для обнаружения логического неравенства сжатых выходных и сжатых эталонных сигналов

Блок 12 предназначен для формирования тестовьк сигналов из сжатых входных сигналов.

Блок 14 элементов И разрешения предназначен для подачи кода адреса подключенных входов и выхода проверяемой ЦИС из регистра 3 в блок 1 при наличии сигнала разрешения от блока 11.

Блок 15 обеспечивает проверку контролируемого блока 18 согласно программе, содержащейся в блоке 1.

Контролируемый блок 18 представляет собой печатный узел, содержащий корпуса ЦИС, соединенных печатными проводниками. В корпусе ЦИС со держится один или несколько элементов, вьтолняющих функции хранения, логической обработки и преобразования информации.

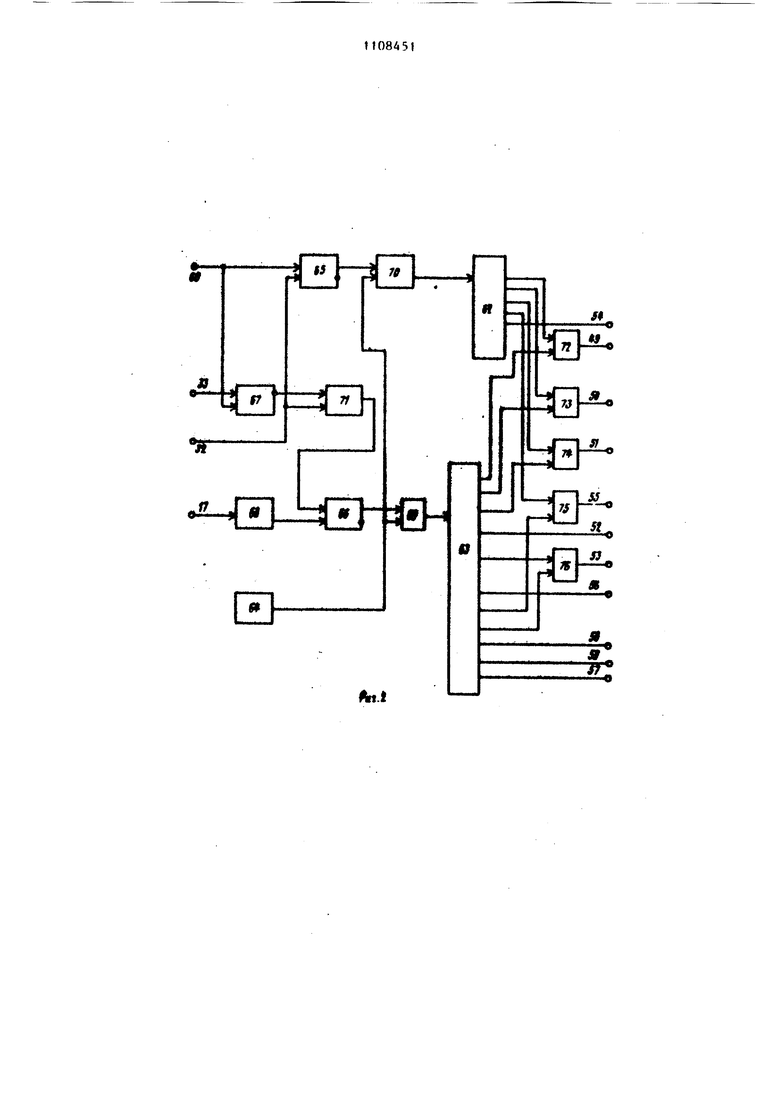

Блок 15 содержит Сфиг. 2) распределители 62 и 63 импульсов, генератор 64 импульсов, триггеры 65-67, дешифратор 68, второй, первый и третий элементы И 69-71, элементы ИЛИ 72-76.

Распределитель 62 импульсов пред назначен для формирования управляющих сигналов для управления блоками устройства во время проверки нелогических дефектов контролируемого блока 18.

Распределитель 63 импульсов предназначен для формирования управляющих сигналов для управления блоками устройства во время проверки логических дефектов контролируемого блока 18.

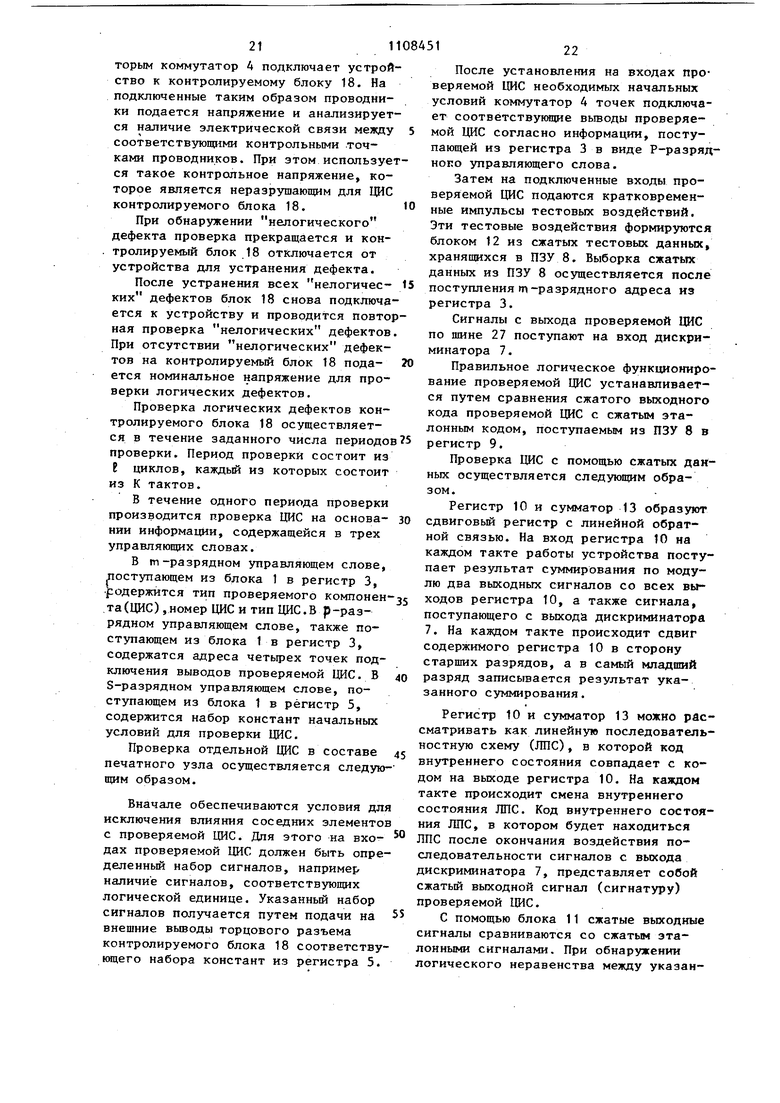

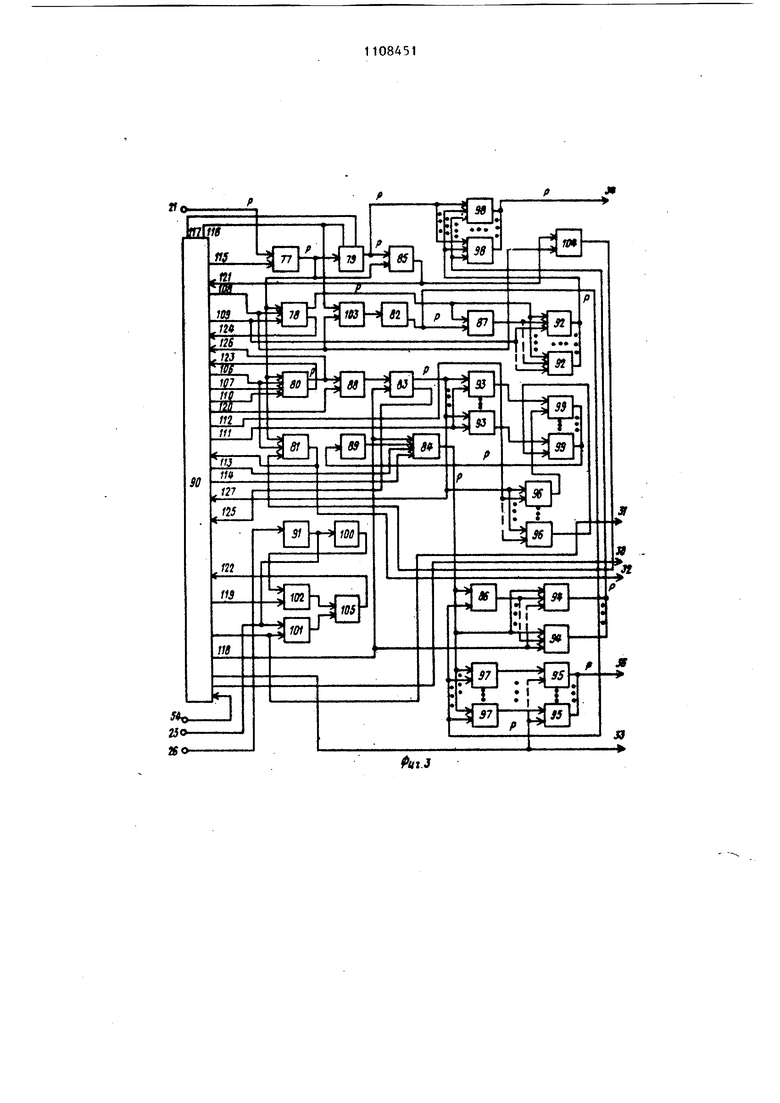

Елок 6 содержит (фиг. 3) регистр 77, счетчики 78-84, схемы 85-87 сравнения, делитель 88 частоты, сумматор 89, узел 90 управления, узел 91 измерения, элементы И 92-95 групп, элементы И-НЕ 96 группы, элементы Ш1И 97-99 групп,-, элемент НЕ 100, элементы И 101-102, второй, первый и третий элементы ИЛИ 103-105, третий семнадцатый выходы 106-120 узла 90, первый, второй, четвертьй, пятый и шестой входы 121-125 узла 90, первую группу входов 126 уэла 90, вторую группу входов 127 уэла 90.

Регистр 77 предназначен для хранения двоичного кода числа печатных проводников контролируемого блока 18.

Счетчик 78 предназначен для образования последовательностей двоичных кодов адресов всех проводников при проверке ложных замыканий проводников.

Счетчик 82 предназначен для образования двоичного кода адреса проверяемого проводника при проверке ложных замыканий и целостности проводников.

Схема 87 сравнения предназначена для выработки сигнала разрешения подачи на группу выходов 35 всех кодов адресов, формируемых счетчиков 78, за исключением кода адреса проверяемого проводника, при проверке, ложных замыканий проводников.

Счетчик 80 предназначен для образования последовательностей двоичных кодов адресов всех проводников для локализации ложных замыканий проводников.

Делитель 88 частоты предназначен для деления частоты импульсов, поступающих с выхода счетчика 80,по заданному коэффициенту деления.

Счетчик 83 предназначен для получения двоичного кода числа импульсов, поступакшщх с выхода делителя 88

Сумматор 89 предназначен для получения суммы его содержимого с прямым или обратным кодом содержимого счетчика 83.

Счетчик 79 предназначен для образования последовательностей двоичных

кодов адресов при проверке целостности проводников.

Схема 85 сравнения предназначена для формирования сигнала при равенстве кодов адресов в регистре 77 и в счетчике 79.

Узел 91 измерений предназначен для выработки признака замыкания пары проводников при проверке ложных замыканий и целостности проводников.

Счетчик 81 предназначен для формирования признаков окончания проверки ложных замыканий и целостности проводников.

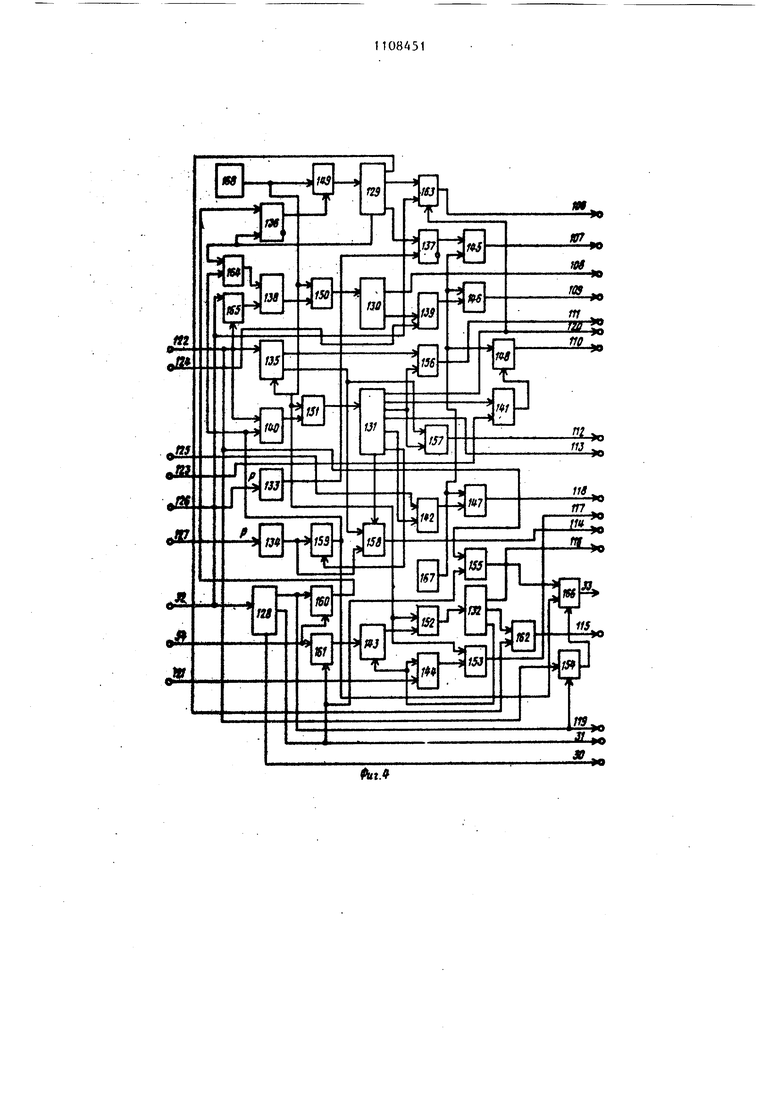

Узел 90 управления предназначен для формирования управляющих сигналов, обеспечивающих функционирование блока 6 согласно заданному алгоритму, и содержит (фиг. 4) регистр 128 сдвига, распределители 129-132 импульсов, дешифратор 133-134, триггеры 135-144, элементы И 145-161, элементы ИЛИ 162-166, генераторы 167168 импульсов.

Распределитель 130 импульсов является кольцевым распределителем им-пульсов и служит для формирования управляющих сигналов, необходимых для осуществления проверки ложных замыканий проводников контролируемого блока 18.

Распределитель 131 импульсов является кольцевым распределителем импульсов и служит для формирования управляющих сигналов, необходимых для осуществления процесса локализации ложных замыканий проводников контролируемого блока 18.

Распределитель 132 импульсов служит для формирования управляющих сигналов, необходимых для проверки целостности проводников контролируемого блока 18.

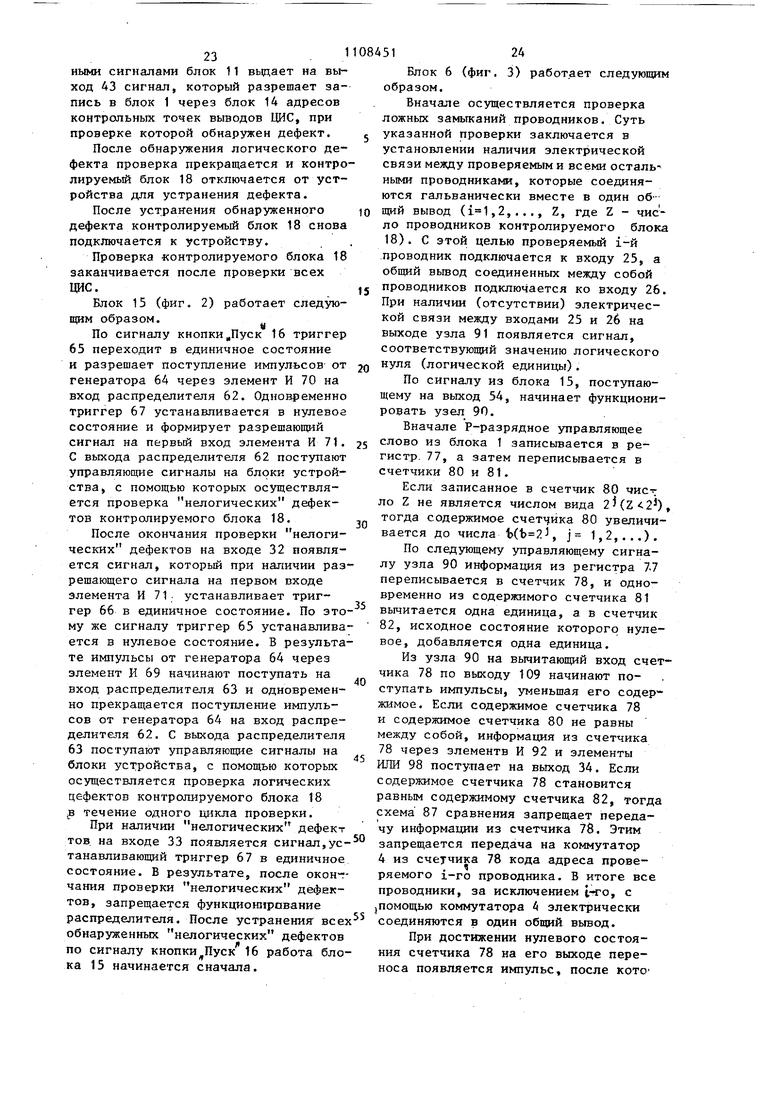

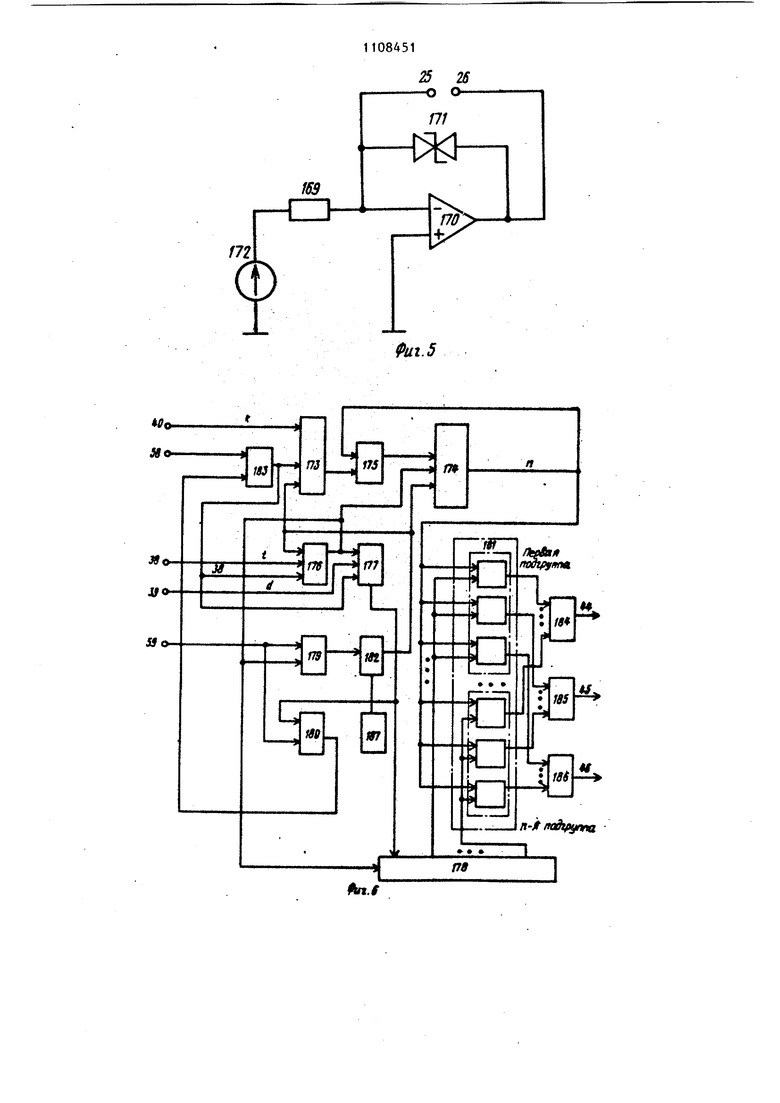

Узел 91 содержит (фиг. 5) эталоннь Й .резистор 169, операционный усилитель 170, двуханодный стабилитрон 171, источник 172 опорного напряжения.

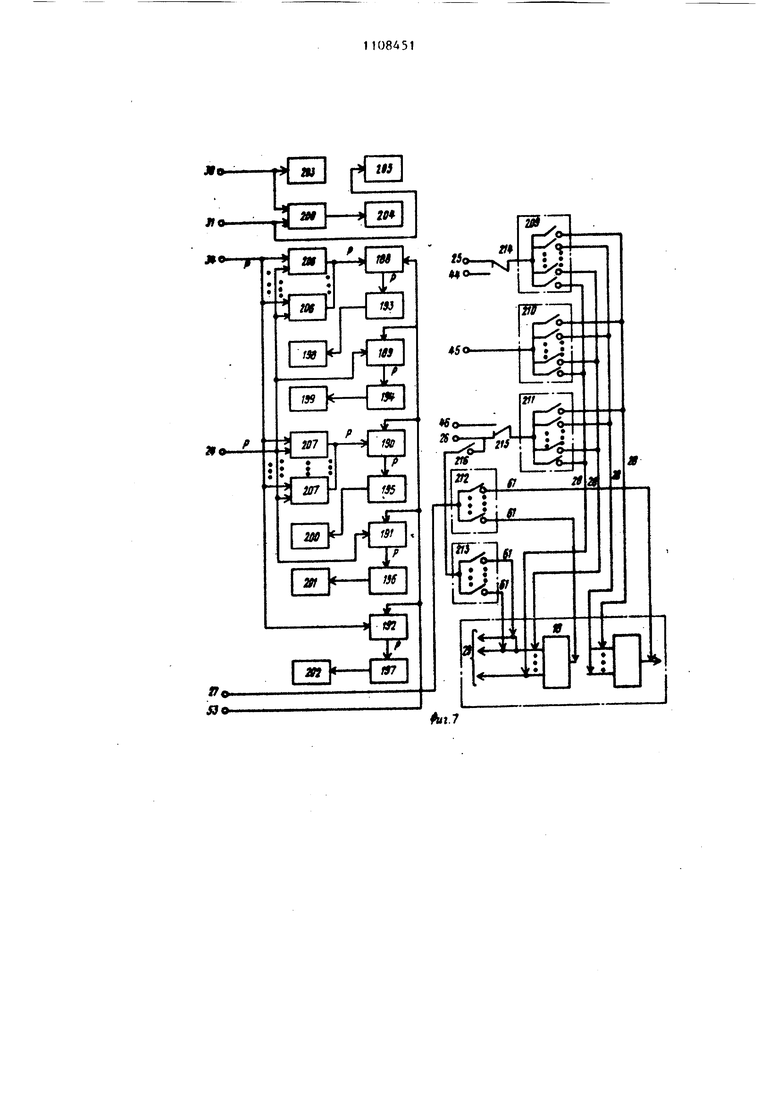

Блок 12 содержит (фиг. 6) регистры 173-174, сумматор 175 по модулю два, счетчики 176-177, распределитель 178 импульсов, триггеры 179-180, группу элементов И 181, элементы И 182-183, элементы ИЛИ 184-186, генератор 187 импульсов.

Регистр 173 является кольцевым сдвиговым регистром и предназначен для хранения одного сжатого входного вектора в течение одного периода

проверки логических дефектов контролируемого блока 18.

Сумматор 175 предназначен для выполнения операции поразрядного сложения (п + 1)-разрядного кода, причем п -разрядный код поступает с г -разрядного регистра 174 и одноразрядный код поступает со старшего разряда регистра 173.,

Регистр 174 и сумматор 1 75 предназначены для получения п-разрядных тестовых наборов из сжатого входного вектора, хранящегося в регистре 173.

Счетчик 176 предназначен для подсчета числа тактов проверки ЦИС контролируемого блока 18.

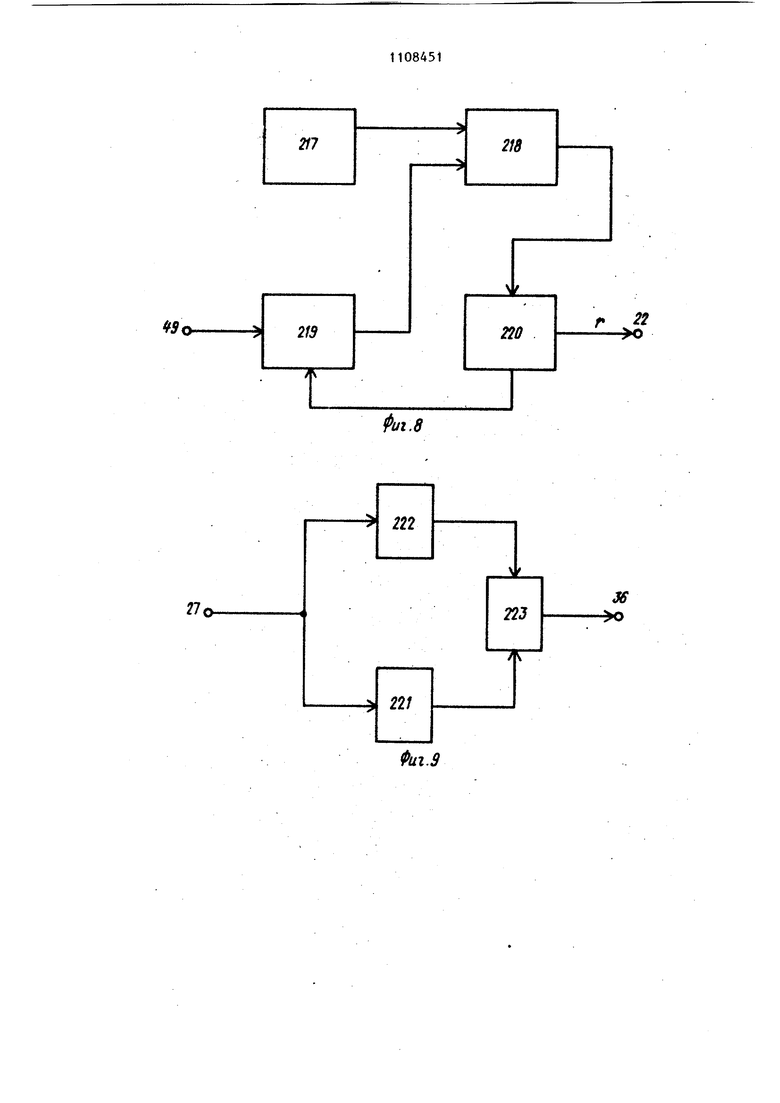

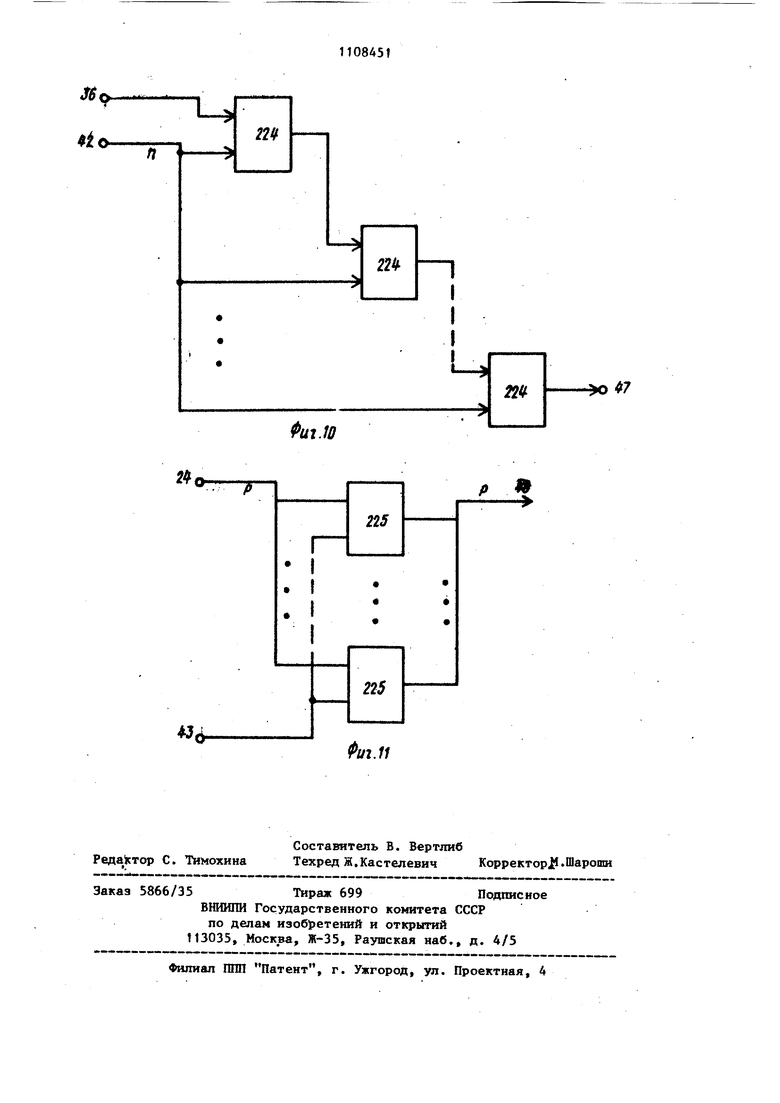

Счетчик 177 предназначен для подсчета числа циклов проверки ЦИС контролируемого блока 18. Распределитель 178 импульсов пред-20 жиме назначен для вьфаботки импульсов, ко торые разрешают передачу информации от одной из l(Z -) групп выходов регистра 174 на выходы блока 12. Коммутатор 4 точек содержит (фиг. 7) регистры 188-192, дешифраторы 193-197, матрицы обмоток реле 198-202, обмотку первого реле выбор режима 203, обмотку второго реле вы бора режима 204, обмотку третьего реле выбора режима 205,группы элемен тов ИЛИ 206-207, элемент ИЛИ 208, группы контактов реле 209-213, контакты 214 первого реле выбора режима, кон такты 215 второго реле выбора режима, контакты 216 третьего реле выбора режима. Регистр 188 и регистр 190 предна значен для запоминания адреса контрольной точки проводника в режимах контроля ложных замыканий и целостности проводников или адреса контрольной точки входа ЦИС в режиме проверки логических дефектов на инте вал времени подключения соответствую щей контрольной точки. Регистр 189 предназначен для запо минания адреса контрольной точки вхо да ЦИС в режиме проверки логических дефектов на интервал времени подключения соответствующей контрольной точки. Регистр 191 предназначен для запоминания адреса контрольной точки выхода ЦИС в режиме проверки логических дефектов на интервал времени подключения соответствующей контрольной точки.

Регистр 192 предназначен для запо-минания адреса контрольной точки проводника в режиме целостности проводников на интервал времени подключения соответствующей контрольной точки.

Дешифраторы 193-197 предназначены для выбора одной обмотки реле соответственно в матрицах обмоток реле 198-202.I,

Матрицы обмоток реле 198-202 предна значены для включения одного реле соответственно в группах контактов реле 209-213.

Коммутатор 4 точек состоит из пяти каналов, каждый из которых содержит управляющую и исполнительную части.

Первый и третий каналы коммутатора 4 предназначены для подключения к контрольным точкам входов ЦИС в репроверки логических дефектов или .для подключения к контрольным точкам проводников в режиме контроля ложных замыканий проводников контролируемого блока 18. Второй канал коммутатора 4 предназначен для подключения к контрольHbw точкам входов ЦИС контролируемого блока 18. Четвертый канал коммутатора 4 предназначен для подключения к контрольным точкам выходов ЦИС контролируемого блока 18. Пятый канал коммутатора 4 предназначен для подключения к контрольным точкам проводников в режиме контроля целостности проводников контролируемого блока 18. Управляющая часть первого канала коммутатора 4 состоит из группы элементов ИЛИ 206, регистра 188, дешифратора 193, матрицы обмоток реле 198, обмотки первого реле выбора режима 203. Управляющая часть второго канала ком утатора 4 состоит из регистра 189, дешифратора 194, матрицы обмоток реле 199. Управляющая часть третьего канала коммутатора 4 состоит из группы элементов ИЛИ 207, регистра 190, дешифратора 195, матрицы обмоток реле ОГ, обмотки второго реле выбора режима 204, элемента ИЛИ 208. Управляющая часть четвертого канала коммутатора 4 состоитиз регистра 191, дешифратора 196, матрицы обмоток реле 201 . Управляяэщая часть пятого канала коммутатора 4 состоит из регистра 192 дешифратора 197, матрицы обмоток роле 202, обмотки третьего реле выборе режима 205. Исполнительная часть второго и че вертого каналов коммутатора 4 содер|гит одну ступень контактов реле, со{стоящую соответственно из группы кон тактов реле 210 и группы контактов реле 212.. ; Исполнительная часть первого тре тьего и пятого каналов коммутатора 4 содержит две ступени контактов реле. Первая ступень исполнительной части первого, третьего и пятого каналов коммутатора 4 состоит соответственно из группы контактов реле 209, группы контактов реле 211, группы контактов реле 213. Вторая ступень исполнительной части первого, третьего и пятого каналов коммутатора 4 состоит соответственно из контактов первого реле выбора режимов 214, контактов второго реле выбора режима 215, контактов третьего реле режима 216. Блок 2 содержит (фиг. 8) генератор 217 импульсов, элемент И 216, триггер 219, счетчик 220 адреса. Дискриминатор 7 выходных сигналов содержит (фиг.9) компаратор 221 логического нуля, компаратор 222 логической единиг№1 триггер 223. Компаратор 22t предназначен для сравнения напряжения на выходе проверяемой ЦИС с эталонным напряжением логического нуля и вьщачи результата сравнения на единичный вход триггера 223. Компаратор 222 предназначен для сравнения напряжения на выходе прове ряемой ЦИС с эталонным напряжением логической единицы и вьщачи результата сравнения на нулевой вход триггера 223. Суматор 13 содержит (фиг. 10)и двухвходовых сумматоров 224 по модул цва, которые соединены последаватель °Блок 14 содержит (фиг. 11)п груп пу двухвходовых элементов И 225. Устройство работает следукщим образом. Контролируемый блок 18 подключ-ает ся к устройству с помощью коммутатоjpa 4. Коммутатор 4 позволяет подклю.;чаться к контрольным точкам проводни 5120 ков и выводов 1ЩС внутри, печатного узла со стороны, свободной от ЦИС. Одновременно может быть подключено не более четьфех контрольных точек. В основе предлагаемого метода контроля лежит предположение,что контролируемый блок 18 будет функционировать нормально, если топология печатного монтажа и ориентация корпусов ЦИС соответствует приниципиальной электрической схеме контролируемого блока 18 и если ЦИС правильно вьшолнягот заданные функции. Перед началом работы устройства , на информационньв- вход 17 поступает программа проверки контролируемого (блока 18, которая записывается в блок 1 .Блок 1 представляет собой оперативное запоминающее устройство с магазинной ад,ресацией ячеек, адреса которых формируются блоком 2. Программа проверки, состоящая из совокупности m-разрядных, Р-разрядных S -разрядных управляющих слов, записывается в блок 1 последовательно, начиная с первой ячейки. В каждую ячейку записывается три управляющих слова: m-разрядное, -разрядное и з -разрядное, Три следующих подряд управляющих слова, которые содержат во всех (т + +3) разрядах единицы, являются признаком конца программы. Последние управляклцие слова дешифрируются в блоке 15 и устанавливают блок 15 в исходное состояние. После записи программы проверки в блок 1 по сигналу от кнопки Пуск 16 начинается работа устройства. Процесс проверки контролимуемого блока 18 начинается с проверки нелогичёских дефектов: ложных замыка-. НИИ и целостности проводников. С этой цепью из блока 1 в блок 6 переписываются р-разрядные управляющие слова, а в регистр 3 -т -разрядные управ Ляющие слова. В In -разрядном управляющем слове содержится информация о типе проверяемого компонента (проводник) и о типе проверки (ложные замыкания или целостность проводников). В р -разрядном управляющем слове содержится информация о числе проводников контролируемого блока 18 и их топологии. Третье 5-разрядное управляющее слово при проверке нелогических дефектов не используется. Блок 6 начинаетформ фовать адреса контрольных точек проводников, по которым коммутатор 4 подключает устройство к контролируемому блоку 18, На подключенные таким образом проводники подается напряжение и анализируется наличие электрической связи между соответствующими контрольными точками проводников. При этом используется такое контрольное напряжение, которое является неразрушающим для ЦИС контролируемого блока 18.

При обнаружении нелогического дефекта проверка прекращается и контролируемый блок 18 отключается от устройства для устранения дефекта.

нелогичес- 15

После устранения всех .11

ких дефектов блок 1В снова подключается к устройству и проводится повто дефектов ная проверка

нелогических

t нелогических дефекПри отсутствии тов на контролируемый блок 18 подается номинальное напряжение для проверки логических дефектов.

Проверка логических дефектов контролируемого блока 18 осуществляется в течение заданного числа периодо проверки. Период проверки состоит из Е циклов, каждый из которых состоит из К тактов.

В течение одного периода проверки производится проверка ЦИС на основаНИИ информации, содержащейся в трех управляющих словах.

В m-разрядном управляющем слове, поступающем из блока 1 в регистр 3, родержится тип проверяемого компонен та(ЦИС),номер ЦИС и тип ЦИС. В р-разрядном управляющем слове, также поступающем из блока 1 в регистр 3, содержатся адреса четырех точек подключения выводов проверяемой ЦИС. В S-разрядном управляющем слове, поступающем из блока 1 в регистр 5, содержится набор констант начальных условий для проверки ЦИС.

Проверка отдельной ЦИС в составе печатного узла осуществляется следующим образом.

Вначале обеспечиваются условия дл исключения влияния соседних элементо с проверяемой ЦИС. Дпя этого на входах проверяемой ЦИС должен быть определенный набор сигналов, например наличие сигналов, соответствующих логической единице. Указанный набор сигналов получается путем подачи на внешние выводы торцового разъема контролируемого блока 18 соответствующего набора констант из регистра 5.

После установления на входах проверяемой ЦИС необходимых начальных условий коммутатор 4 точек подключает соответствуюпие вьтоды проверяемой ЦИС согласно информации, поступающей из регистра 3 в виде Р-разрядноко управляющего слова.

Затем на подключенные входы проверяемой ЦИС подаются кратковременные импульсы тестовых воздействий. Эти тестовые воздействия формируются блоком 12 из сжатых тестовых данных, хранящихся в ПЗУ 8. Выборка сжатых данных из ПЗУ 8 осуществляется после поступления л-разрядного адреса из регистра 3.

Сигналы с выхода проверяемой ЦИС по шине 27 поступают на вход дискриминатора 7.

Правильное логическое функционирование проверяемой ЦИС устанавливается путем сравнения сжатого выходного кода проверяемой ЦИС с сжатым эталонным кодом, поступаемым из ПЗУ 8 в регистр 9.

Проверка ЦИС с помощью сжатых данных осуществляется следующим образом.

Регистр 10 и сумматор 13 образуют сдвиговьй регистр с линейной обратной связью. На вход регистра 10 на каждом такте работы устройства поступает результат суммирования по модулю два выходных сигналов со всех выходов регистра 10, а также сигнала, поступающего с выхода дискриминатора 7. На каждом такте происходит сдвиг содержимого регистра 10 в сторону старших разрядов, а в самый младший разряд записывается результат указанного суммирования.

Регистр 10 и сумматор 13 можно рассматривать как линейную последователькостную схему (ЛПС), в которой код внутреннего состояния совпадает с кодом на выходе регистра 10. На каждом такте происходит смена внутреннего состояния ЛПС. Код внутреннего состояния ЛПС, в котором будет находиться ЛПС после окончания воздействия последовательности сигналов с выхода дискриминатора 7, представляет собой сжатый выходной сигнал (сигнатуру) проверяемой ЦИС.

С помощью блока 11 сжатые выходные сигналы сравниваются со сжатым эталонными сигналами. При обнаружении логического неравенства между указан1ными сигналами блок 11 вьиает на выход 43 сигнал, который разрешает запись в блок 1 через блок 14 адресов контрольных точек выводов ЦИС, при проверке которой обнаружен дефект. После обнаружения логического дефекта проверка прекращается и контро лируемый блок 18 отключается от устройства для устранения дефекта. После устранения обнаруженного дефекта контролируемый блок 18 снова подключается к устройству. Проверка контролируемого блока 18 заканчивается после проверки всех ЦИС. Блок 15 (фиг. 2) работает следующим образом. По сигналу кнопки,Пуск 16 триггер 65 переходит в единичное состояние и разрешает поступление импульсов от генератора 64 через элемент И 70 на вход распределителя 62. Одновременно триггер 67 устанавливается в нулевое состояние и формирует разрешающий сигнал на первый вход элемента И 71. С выхода распределителя 62 поступают управляющие сигналы на блоки устройства, с помощью которых осуществляется проверка нелогических дефектов контролируемого блока 18. После окончания проверки нелогических дефектов на входе 32 появляется сигнал, который при наличии раз решающего сигнала на первом входе элемента И 71- устанавливает триггер 66 в единичное состояние. По это му же сигналу триггер 65 устанавлива ется в нулевое состояние. В результа те импульсы от генератора 64 через элемент И 69 начинают поступать на вход распределителя 63 и одновременно прекращается поступление импульсов от генератора 64 на вход распределителя 62. С выхода распределителя 63 поступают управляющие сигналы на блоки устройства, с помощью которых осуществляется проверка логических дефектов контролируемого блока 18 в течение одного цикла проверки. При наличии нелогических дефект тов на входе 33 появляется сигнал,ус танавливающий триггер 67 в единичное состояние. В результате, после окон-г чания проверки нелогических дефектов, запрещается функционирование распределителя. После устранения всех обнаруженньк нелогических дефектов по сигналу кнопки Пуск 16 работа блока 15 начинается сначала. 5124 Блок 6 (фиг. 3) работает следующим образом. Вначале осуществляется проверка ложных замыканий проводников. Суть указанной проверки заключается в установлении наличия электрической связи между проверяемым и всеми осталь ными проводниками, которые соединяются гальванически вместе в один обпр й вывод (,2,..., Z, где Z - число проводников контролируемого блока 18). С этой целью проверяемый i-й проводник подключается к входу 25, а общий вывод соединенных между собой проводников подключается ко входу 26. При наличии (отсутствии) электрической связи между входами 25 и 2б на выходе узла 91 появляется сигнал, соответствующий значению логического нуля (логической единицы). По сигналу из блока 15, поступающему на выход 54, начинает функционировать узел 90. Вначале Р-разрядное управляющее слово из блока 1 записывается в регистр. 77, а затем переписьгеается в счетчики 80 и 81. Если записанное в счетчик 80 число Z не является числом вида 2() тогда содержимое счет- ика. 80 увеличивается до числа Ь(, j 1,2,...). По следующему управляющему сигналу узла 90 информация из регистра 77 переписывается в счетчик 78, и одновременно из содержимого счетчика 81 вычитается одна единица, а в счетчик 82, исходное состояние которого нулевое, добавляется одна единица. Из узла 90 на вычитающий вход счетчика 78 по выходу 109 начинают поступать импульсы, уменьшая его содержимое. Если содержимое счетчика 78 и содержимое счетчика 80 не равны между собой, информация из счетчика 78 через элементв И 92 и элементы ИЛИ 98 поступает на выход 34. Если содержимое счетчика 78 становится равным содержимому счетчика 82, тогда схема 87 сравнения запрещает передачу информации из счетчика 78. Этим запрещается передача на коммутатор 4 из счетчика 78 кода адреса проверяемого i-ro проводника. В итоге все проводники, за исключением i-rro, с помощью коммутатора 4 электрически соединяются в один общий вывод, При достижении нулевого состояния счетчика 78 на его выходе переноса появляется импульс, после кото 251 рого прекращается поступление импульсов на вычитакяций вход счетчика 78 и начинается анализ состояния узла 91 При отсутствии замыкания между i-M и всеми остальными проводниками осуществляется проверка между следующим ( + 1)-м и всеми остальными проводниками. Информация из регистра 77 снова переписывается в счетчик 78 и одновременно из содержимого счетчика 81 вычитается одна единица, а в счетчик 82 добавляется одна единица. Затем поступакнцие из узла 90 импульсы уменьшают содержимое счетчика 78 до нуля. Если при проверке очередного проводника узел 91 выработал признак замыкания между ним и всеми остальными проводниками, тогда по сигналам из узла 90 в блок 1 по выходу 35 записывается код проверяемого проводника и начинает осуществляться процесс локализации дефекта для определе ния кода адреса проводника, с которым замыкается данный проводник. Указанный процесс локализации дефекта осуществляется за . этапов (log2b) . Суть процесса локализации дефектов заключается в последовательном половинном уменьшении электрически соединяемых между собой в один общий вывод проводников до тех пор, пока не будет получена пара короткозамкнутых проводников. С этой целью используется делитель 88, который имеет переменный коэффициент деления и равный степени j числа 2, причем установление коэффициента деления происходит в начале каждого этапа по сигналам, поступающим по выходу 120 на управляющий вход делителя 88. Из узла 90 по выходу 110 на вычитающий вход счетчика 80 начинают поступать импульсы до тех пор, пока содержимое счетчика 80 не станет рав ным нулю.С помощью делителя 88 в счетчик 83 записывается число,равное половине (на первом этапе) число, содер жащегося в счетчике 80 до поступления импульсов на его вычитающий вход В сумматоре 89, исходное состояние которого нулевое, происходит слокение его содержимого с прямьм кодом, поступившим из счетчика 83. Результат суммирования передается в счетчик 84 и сохраняется также в сумматоре 89 до следующего этапа локализации дефекта,i 51 Затем из узла 90 по вькоду 118 начинают поступать импульсы на вычитающий вход счетчика 83 и на суммирующий вход счетчика 84. Одновременно с приходом каждого импульса по выходу 118 информация из счетчика 84 через элементы И 94 и элементы ИЛИ 98 поступает на выход 34. Если содержимое счетчика 84 станет равным содержимому счетчика 82, тогда схема 86 сравнения запретит передачу информации из счетчика 84. Тем самым запрещается передача на коммутатор 4 из счетчика 84 кода адреса проверяемого проводника. Указанные импульсы по выходу 118 поступают до тех пор, пока в счетчике 83 не останется код единицы. В итоге содержимое счетчика 84 увеличится на число, которое на единицу меньше числа ранее записанного В счетчик 83. На этом заканчивается первый этап процесса локализации дефекта. Затем начинается следующий этап процесса локализации дефекта, причем каждый последующий этап отличается от предьщущего уменьшением в два рази количества импульсов, поступающих с вьгхода делителя 88. Наличие в счетчике 83 кода единицы в начале этапа свидетельствует о последнем процессе локализации дефекта. После окончания каждого этапа процесса локализации дефекта узел 91 вырабатывает признак замыкания. При наличии (отсутствии) признака замыкания после i-ro такта с вьпсодов элементов ИЛИ 99 на вход сумматора 89 на (i+1)-M такте поступает прямой (обратный) код содержимого счетчика 83. При поступлении на вход сумматора 89 обратного кода содержимого счетчика 83 обратный код суммы в сумматоре 89 всегда будет совпадать с прямым кодом суммы, поскольку результат суммирования в сумматоре 89 всегда будет положительным числом. Если после окончания последнего этапа процесса локализахщи дефекта от узла 91 поступает признак о наличин-замыкания, тогда код числа, содержащегося в счетчике 84, будет являться кодом номера проводника, который замыкается с проверяемым проводником. Если после окончания последнего этапа процесса локализации дефекта от узла 91 поступает 1ризнак отсутствия замыкания,тогда код числа, которое на единицу меньше числа в счетчике 84, будет являться кодом номера проводника, иоторый замыкается с проверяемым проводником В последнем случае для получения окон чательного результата на вычитающий вход счетчика 84 по выходу 114 посту пает один импульс коррекции. Затем на выходе 33 появляется импульс, по которому в блок 1 записывается код номера проводника, который замыкается проверяемьм проводником Проверка ложных замыканий проводников заканчивается при достижении нулевого состояния в счетчике 81, о чем свидетельствует появление импуль са на выходе 32. Затем начинается проверка целостности проводников. Суть указанной проверки заключается в установлении электрической связи между одной произвольно выбран ной контрольной точкой проводника, называемой узловой, со всеми остальными контрольными точками данного проводника,которые называются топологическими точками данного проводника С этой целью узловая точка i-ro про водника подключается к входу 25 блока 6,а очередная топологическая точка этого проводника подключается к входу 26. Адреса узловых и топологических точек формируются следующим образом. Для первого проводника адрес узловой точки совпадает с номером проводника, т.е. равен единице, а топологические точки будут иметь адреса от (Z + t) до (Z f) (где f - число топологических точек первого проводника) . Дпя последукнцих проводников адреса контрольных точек формируются аналогичным образом, причем адрес узловой точки совпадает с номе ром проводника, а адрес первой топологической точки (i + 1)-го проводника на единицу больше адреса послед ней топологической точки i-ro провод Перед началом проверки целостности проводников информация из регист ра 77 снова переписьгоается в счетчик 81. При проверке целостности первого проводника в регистр 77 заносится адрес последней топологической точки первого проводника, а в счетчик 79 число узловых точек проводников контролируемого блока 18. Одновременно на суммирующий вход счетчика 82 (исходное состояние нулевое) поступает один импульс. Из узла 90 по выходу 117 на суммирующий вход счетчика 79 начинают поступать импульсы. Информация из счетчика 79 через элементы ИЛИ 98 поступает на выход 34. При равенстве содержимого регистра 77 и счетчика 79 схема 85 сравнения вырабатывает признак, по которому из счетчика 81 вычитается одна единица и прекращается подача импульсов на суммирующий вход счетчика 79. Далее анализируется состояние узла 91. При отсутствии дефекта целостности проводника в регистр 77 заносится адрес последней топологической точки второго проводника и начинается проверка целостности второго проводника. Аналогичным образом проверяются все остальные проводники. Проверка целостности проводников заканчивается при достижении нулевого состояния счетчика 81. При обнаружении дефекта целостности проводника его код из счетчика 82 через элемент ИЛИ 97 и элемент И 95 записьшается в блок 1. С помощью элемента И 101, элемента И 102, элемента ИЛИ 105 и элемента НЕ 100 формируется признак наличия нелогического дефекта следующим образом. В режиме проверки ложных замыканий проводников значение логической 1 (логического нуля) на выходе элемента И 102 свидетельствует о наличии (отсутствии) ложного замыкания. В режиме проверки целостности проводников значение логической 1 (логического нуля) на выходе элемента И 101 свидетельствует о наличии (отсутствии) дефекта целостности проводника. Узел 90 (фиг. А) работает следующим образом, В исходном состоянии регистр 129 находится в состоянии, соответствующем режиму ложных замыканий проводников (значение логической единицы только на .выходе 119). В исходном состоянии триггеры 135144 находятся в нулевых состояниях. По сигналу, поступающему по входу 54, триггер 136 устанавливается в единичное состояние, разрешая поступление импульсов от генератора 168 на вход распределителя 129. Сигналы с первого и со второго выходов распред&ггителя 129 приводят к появлению сигналов соответственно на выходах 115 и 106. Сигнал с третьего выхода распределителя 129 переводит в единичное состояние триггер 137, которьй разрешает поступление импульсов от генератора 167 на выход 107. Частота следования импульсов от генератора 167 в Z раз больше час;тоты следования импульсов от генератора 168. При поступлении на вход дешифратора 133 числа вида 2 на его выход формируется сигнал, которьш устанавливает триггер 137 в нулевое состояние. В итоге запрещается поступление импульсов на выход 107. Сигнал с четвертого выхода распре делителя 129 устанавливает в нулевое состояние триггер 136 и в единичное состояние - триггер 138. В итоге запрещается поступление импульсов от генератора 168 на вход распределителя 129 и разрешается поступление импульсов от генератора 168 иа вход распределителя 130. Сигнал со второго выхода распреде лителя 130 переводит в единичное состояние триггер 139, который разрешает поступление импульсов от генера тора 167 на выход 109. При появлении сигнала на выходе 124 триггер 139 переходит в нулевое состояние и запрещает поступление импульсов на вход 109 В промежутке времени между исчезновением сигнала на втором выходе и появлением сигнала на первом выходе распределителя 130 на входе 122 появляется признак наличия ложного замыкания, который вырабатывается узлом 91. При отсутствии ложного замыкания распределитель 130 продолжает работать в кольцевом режиме. При наличии признака ложного замыкания появляется сигнал на входе 122, который переводит триггер 135 и триггер 140 в единичное состояние, а триггер 138 - в нулевое состояние В итоге запрещается поступление импульсов от генератора 168 на вход распределителя 130 и разрешается по- 5S

ступление импульсов от генератора 168 на вход распределителя 131. Одновременно появляется сигнал на выходе