у

Фиг.1

Vх

у

Изобретение относится к электронной технике и может быть использовано при создании БИС запоминающих устройств.

Цель изобретения - расширение области применения элемента памяти за счет возможности хранения аналоговой информации.

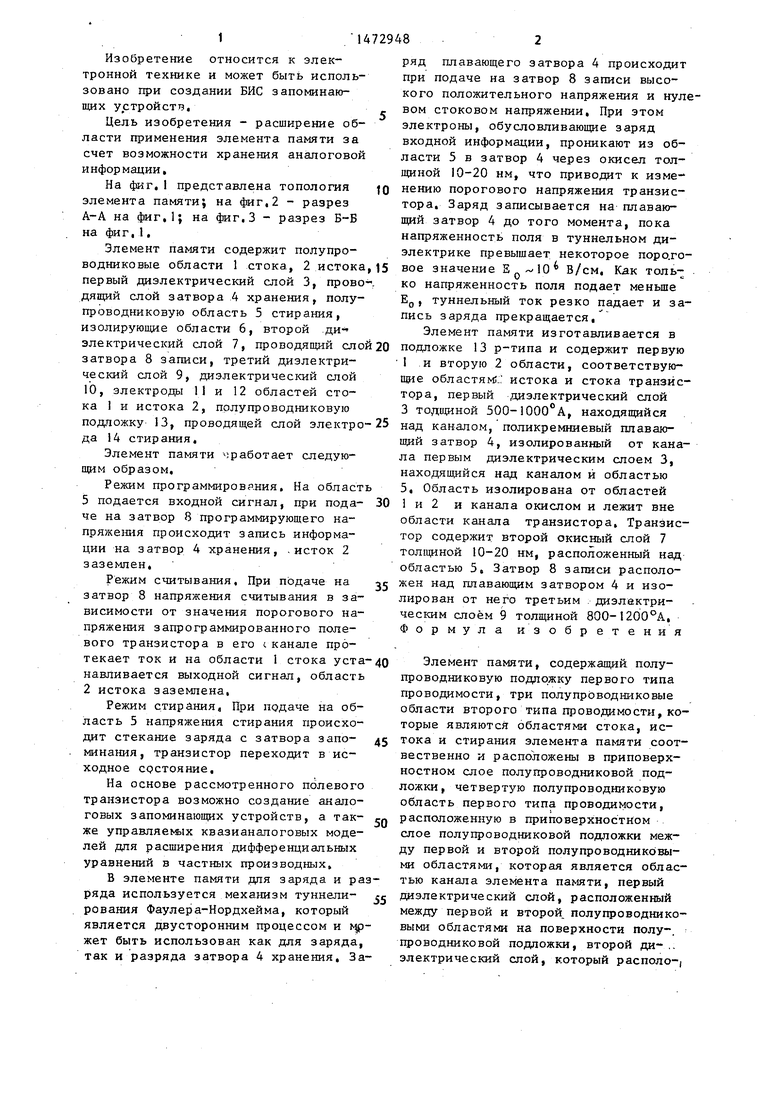

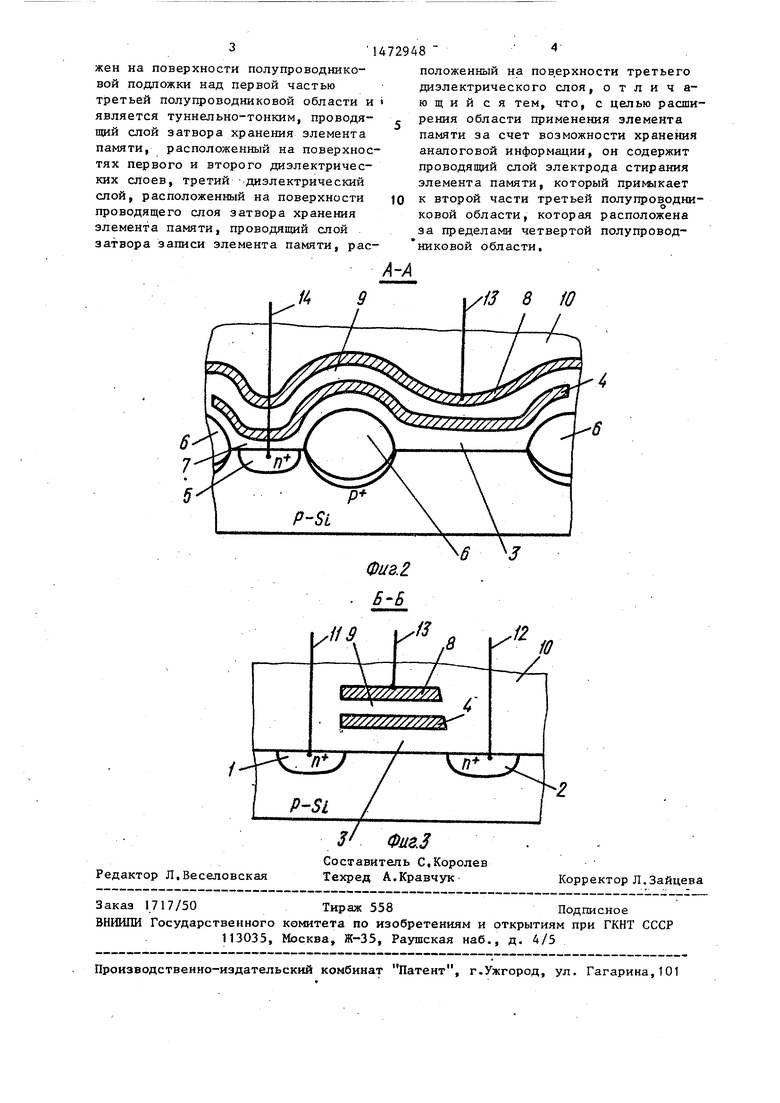

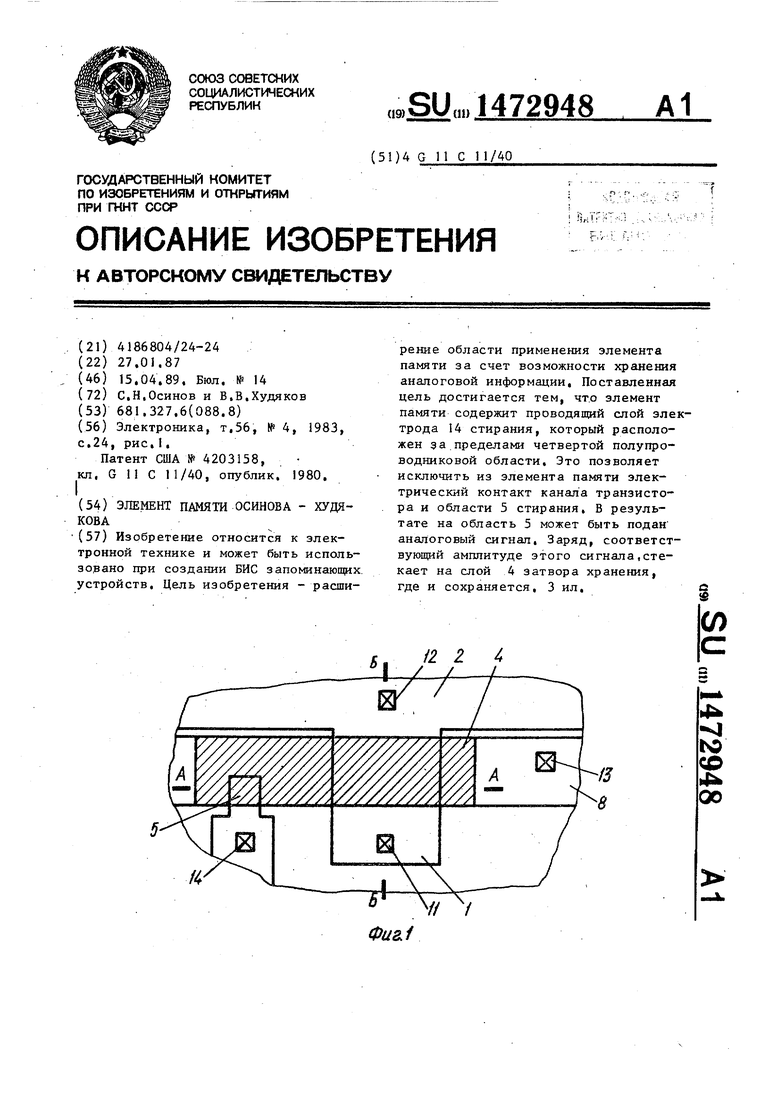

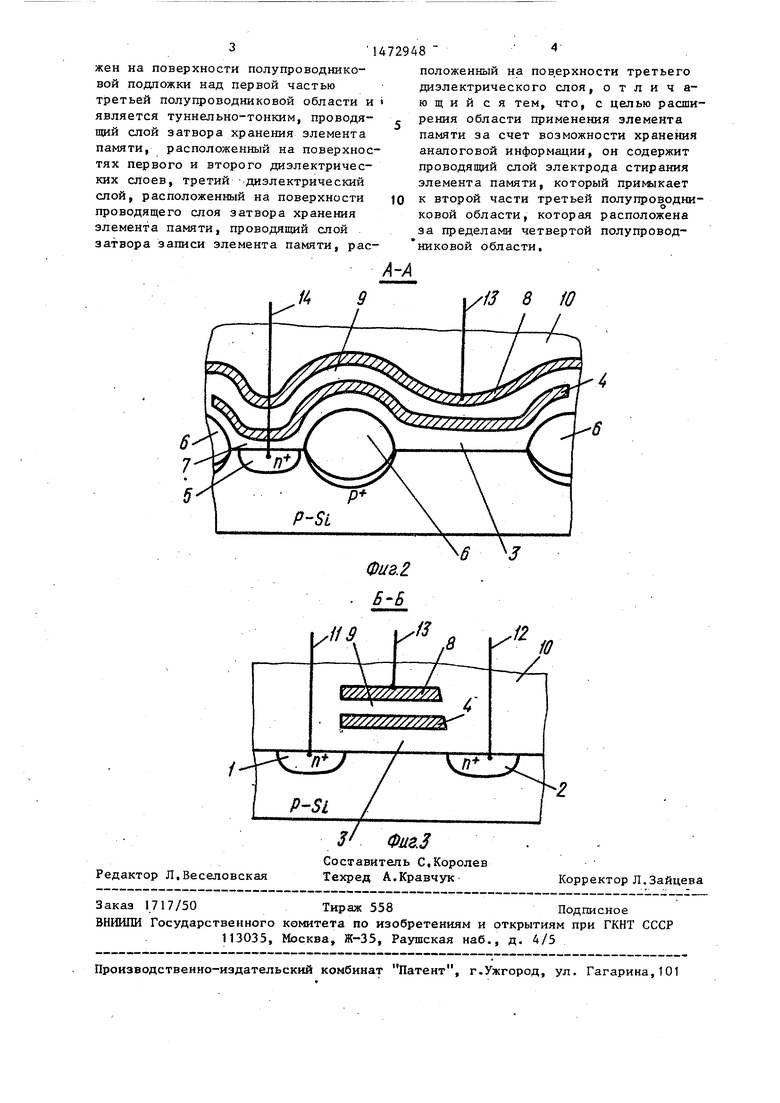

На фиг. 1 представлена топология элемента памяти; на фиг,2 - разрез А-А на фиг,1; на фиг.З - разрез Б-Б на фи г, 1,

Элемент памяти содержит полупро

ряд плавающего затвора 4 происходит при подаче на затвор 8 записи высокого положительного напряжения и нулевом стоковом напряжении. При этом электроны, обусловливающие заряд входной информации, проникают из области 5 в затвор 4 через окисел толщиной 10-20 нм, что приводит к изменению порогового напряжения транзистора. Заряд записывается на плавающий затвор 4 до того момента, пока напряженность поля в туннельном диэлектрике превышает некоторое поро.го

| название | год | авторы | номер документа |

|---|---|---|---|

| ФЛЭШ ЭЛЕМЕНТ ПАМЯТИ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2015 |

|

RU2584728C1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1982 |

|

SU1135354A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| ФЛЭШ ЭЛЕМЕНТ ПАМЯТИ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2368037C1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

| Элемент памяти | 1980 |

|

SU881860A1 |

| ФЛЭШ ЭЛЕМЕНТ ПАМЯТИ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2357324C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1989 |

|

RU1604054C |

| Элемент памяти | 1986 |

|

SU1361629A1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 1996 |

|

RU2111556C1 |

Изобретение относится к электронной технике и может быть использовано при создании БИС запоминающих устройств. Цель изобретения - расширение области применения элемента памяти за счет возможности хранения аналоговой информации. Поставленная цель достигается тем, что элемент памяти содержит проводящий слой электрода 14 стирания, который расположен за пределами четвертой полупроводниковой области. Это позволяет исключить из элемента памяти электрический контакт канала транзистора и области 5 стирания. В результате на область 5 может быть подан аналоговый сигнал. Заряд , соответствующий амплитуде этого сигнала, стекает на слой 4 затвора хранения, где и сохраняется. 3 ил.

водниковые области 1 стока, 2 истока, 15 вое значение В/см, Как толь- первый диэлектрический слой 3, прово-1. дящий слой затвора 4 хранения, полупроводниковую область 5 стирания, изолирующие области 6, второй ди- электрический слой 7, проводящий слой 20 подложке 13 р-типа и содержит первую

ко напряженность поля подает меньше Е0, туннельный ток резко падает и запись заряда прекращается,

Элемент памяти изготавливается в

1 и вторую 2 области, соответствующие областям;. истока и стока транзисзатвора 8 записи, третий диэлектрический слой 9, диэлектрический слой 10, электроды 11 и 12 областей стока 1 и истока 2, полупроводниковую

подложку 13, проводящей слой электро-25 над каналом, поликремниевый плаваю- да 14 стирания,щий затвор 4, изолированный от канатора, первый диэлектрический слой 3 толщиной 500-1000°А, находящийся

Элемент памяти сработает следующим образом.

Режим программирования. На область 5 подается входной сигнал, при пода- че на затвор 8 программирующего напряжения происходит запись информации на затвор 4 хранения, -исток 2 заземлен,

Режим считывания, При подаче на затвор 8 напряжения считывания в зависимости от значения порогового напряжения запрограммированного полевого транзистора в его канале протекает ток и на области 1 стока устанавливается выходной сигнал, область 2 истока заземлена,

Режим стирания, При подаче на область 5 напряжения стирания происходит стекание заряда с затвора запо- минания, транзистор переходит в исходное состояние.

На основе рассмотренного полевого транзистора возможно создание аналоговых запоминающих устройств, а также управляемых квазианалоговых моделей для расширения дифференциальных уравнений в частных производных,

В элементе памяти для заряда и раряда используется механизм туннели- рования Фаулера-Нордхейма, который является двусторонним процессом и мр жет быть использован как для заряда, так и разряда затвора 4 хранения, За

вое значение В/см, Как толь- подложке 13 р-типа и содержит первую

ко напряженность поля подает меньше Е0, туннельный ток резко падает и запись заряда прекращается,

Элемент памяти изготавливается в

1 и вторую 2 области, соответствующие областям;. истока и стока транзис над каналом, поликремниевый плаваю- щий затвор 4, изолированный от кан

тора, первый диэлектрический слой 3 толщиной 500-1000°А, находящийся

ла первым диэлектрическим слоем 3, находящийся над каналом и областью 5, Область изолирована от областей 1 и 2 и канала окислом и лежит вне области канала транзистора. Транзистор содержит второй окисный слой 7 толщиной 10-20 нм, расположенный над областью 5, Затвор 8 записи расположен над плавающим затвором 4 и изолирован от него третьим диэлектрическим слоем 9 толщиной 800-1200°А, Формула изобретения

Элемент памяти, содержащий полупроводниковую подложку первого типа проводимости, три полупроводниковые области второго типа проводимости, которые являются областями стока, истока и стирания элемента памяти соот- вественно и расположены в приповерхностном слое полупроводниковой подложки, четвертую полупроводниковую область первого типа проводимости, расположенную в приповерхностном слое полупроводниковой подложки между первой и второй полупроводниковыми областями, которая является областью канала элемента памяти, первый диэлектрический слой, расположенный между первой и второй, полупроводниковыми областями на поверхности полу-. проводниковой подложки, второй ди- .. электрический слой, который располо-)

J Фо&З

| Электроника, т.56, № 4, 1983, с.24, рис,1 | |||

| Патент США 4203158, кл, G 11 С 11/40, опублик | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1989-04-15—Публикация

1987-01-27—Подача